Capacitor Voltage Balancing of a Grid-Tied, Cascaded Multilevel Converter with Binary Asymmetric Voltage Levels Using an Optimal One-Step-Ahead Switching-State Combination Approach †

Abstract

:1. Introduction

Research Contribution and Scope

2. Asymmetric Cascaded Multilevel Converter Basics

2.1. Switching-States

2.2. Nearest-Level Control

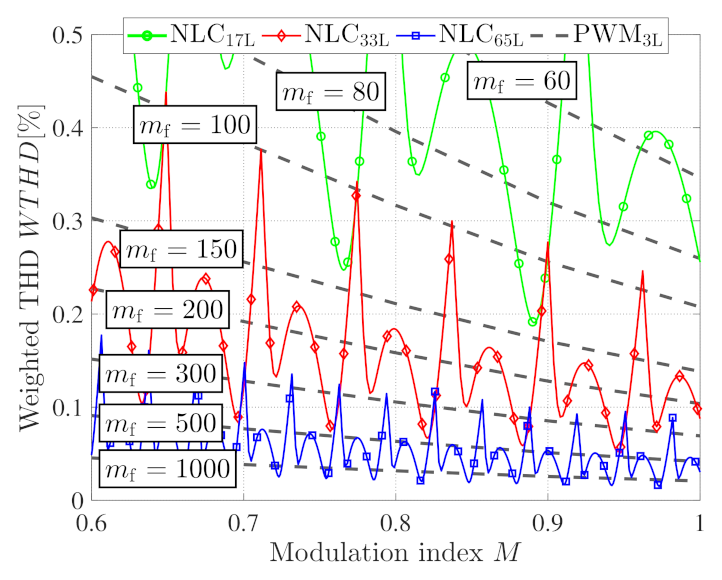

3. Weighted Total Harmonic Distortion of Higher Level NLC Waveform in Comparison to Three-Level PWM

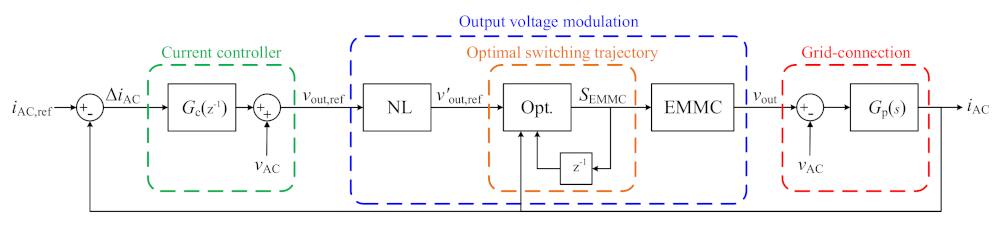

4. Current Control and Voltage Balancing of the Asymmetric Cascaded Multilevel Converter

4.1. Current Control Using a Proportional-Resonant Controller

4.2. Capacitor Voltage Balancing Using a One-Time-Step Model Predictive Control Approach

4.3. Sensorless Capacitor Voltage Balancing Using a Dynamic Programming Approach

5. Stability of the Sensorless, Dynamic Programming Approach

6. Measurements

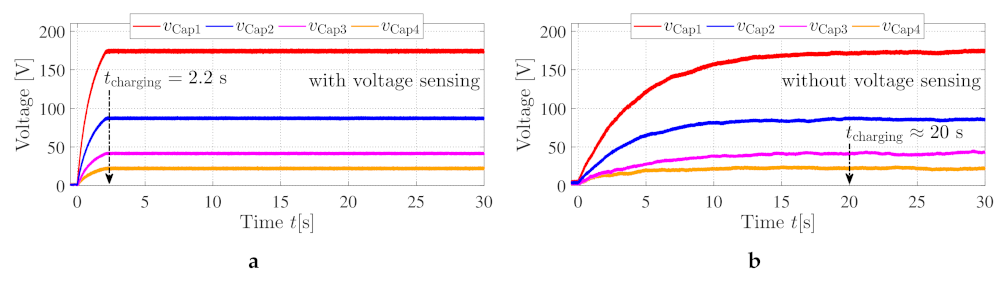

6.1. Capacitor Precharging

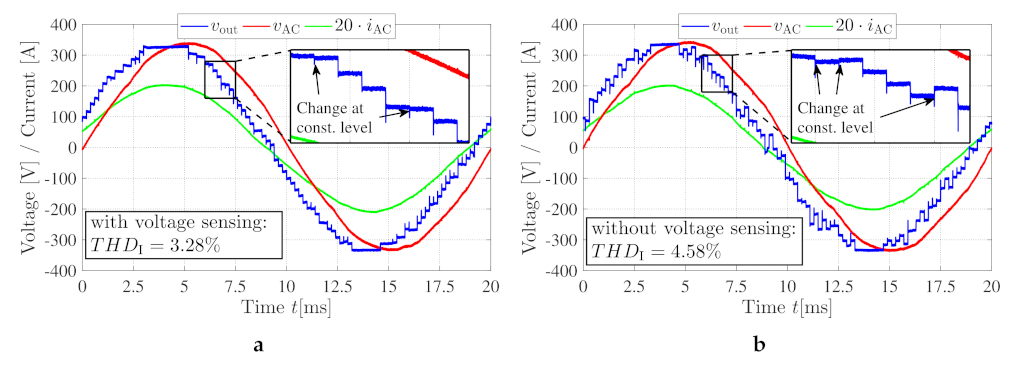

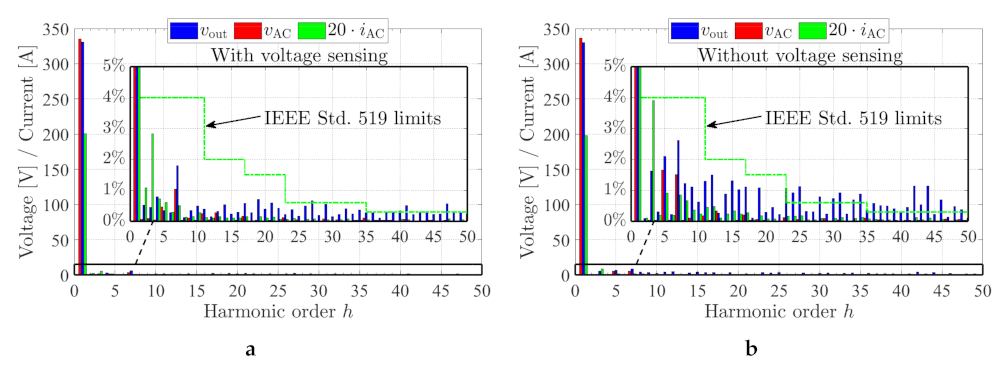

6.2. Operation in Grid-Feeding Mode

7. Conclusions

Author Contributions

Funding

Conflicts of Interest

References

- Lesnicar, A.; Marquardt, R. An innovative modular multilevel converter topology suitable for a wide power range. In Proceedings of the 2003 IEEE Bologna Power Tech Conference Proceedings, Bologna, Italy, 23–26 June 2003; Volume 3, p. 6. [Google Scholar]

- Behrouzian, E.; Bongiorno, M. Investigation of Negative-Sequence Injection Capability of Cascaded H-Bridge Converters in Star and Delta Configuration. IEEE Trans. Power Electron. 2017, 32, 1675–1683. [Google Scholar] [CrossRef]

- Tolbert, L.M.; Peng, F.Z.; Habetler, T.G. Multilevel converters for large electric drives. IEEE Trans. Ind. Appl. 1999, 35, 36–44. [Google Scholar] [CrossRef] [Green Version]

- Corzine, K.; Familiant, Y. A new cascaded multilevel H-bridge drive. IEEE Trans. Power Electron. 2002, 17, 125–131. [Google Scholar] [CrossRef]

- Ma, M.; Hu, L.; Chen, A.; He, X. Reconfiguration of Carrier-Based Modulation Strategy for Fault Tolerant Multilevel Inverters. IEEE Trans. Power Electron. 2007, 22, 2050–2060. [Google Scholar] [CrossRef]

- Kersten, A.; Oberdieck, K.; Bubert, A.; Neubert, M.; Grunditz, E.; Thiringer, T.; De Doncker, R.W. Fault Detection and Localization for Limp Home Functionality of Three-Level NPC Inverters with Connected Neutral Point for Electric Vehicles. IEEE Trans. Transp. Electrif. 2019, 5, 416–432. [Google Scholar] [CrossRef]

- Kersten, A.; Oberdieck, K.; Gossmann, J.; Bubert, A.; Loewenherz, R.; Neubert, M.; Thiringer, T.; De Doncker, R. Measuring and Separating Conducted Three-Wire Emissions from a Fault-Tolerant, NPC Propulsion Inverter with a Split-Battery using Hardware Separators based on HF Transformers. IEEE Trans. Power Electron. 2020, 36, 378–390. [Google Scholar] [CrossRef]

- Zhang, H.; Yang, L.; Wang, S.; Puukko, J. Common-Mode EMI Noise Modeling and Reduction With Balance Technique for Three-Level Neutral Point Clamped Topology. IEEE Trans. Ind. Electron. 2017, 64, 7563–7573. [Google Scholar] [CrossRef]

- Chang, F.; Ilina, O.; Lienkamp, M.; Voss, L. Improving the Overall Efficiency of Automotive Inverters Using a Multilevel Converter Composed of Low Voltage Si mosfets. IEEE Trans. Power Electron. 2019, 34, 3586–3602. [Google Scholar] [CrossRef]

- Kersten, A.; Grunditz, E.; Thiringer, T. Efficiency of Active Three-Level and Five-Level NPC Inverters Compared to a Two-Level Inverter in a Vehicle. In Proceedings of the 2018 20th European Conference on Power Electronics and Applications (EPE’18 ECCE Europe), Riga, Latvia, 17–21 September 2018; pp. P.1–P.9. [Google Scholar]

- Kersten, A.; Kuder, M.; Grunditz, E.; Geng, Z.; Wikner, E.; Thiringer, T.; Weyh, T.; Eckerle, R. Inverter and Battery Drive Cycle Efficiency Comparisons of CHB and MMSP Traction Inverters for Electric Vehicles. In Proceedings of the 2019 21st European Conference on Power Electronics and Applications (EPE ’19 ECCE Europe), Genova, Italy, 3–5 September 2019; pp. P.1–P.12. [Google Scholar] [CrossRef]

- Zhang, Y.; Adam, G.P.; Lim, T.C.; Finney, S.J.; Williams, B.W. Hybrid Multilevel Converter: Capacitor Voltage Balancing Limits and its Extension. IEEE Trans. Ind. Inform. 2013, 9, 2063–2073. [Google Scholar] [CrossRef]

- Holmes, D.G.; Lipo, T.A. Pulse Width Modulation for Power Converters: Principles and Practice; John Wiley & Sons: Hoboken, NJ, USA, 2003; Volume 18. [Google Scholar]

- Ruderman, A.; Schlosberg, S. A hybrid asymmetric cascaded multilevel inverter comprising high resolution and symmetric low resolution parts. In Proceedings of the 2008 IEEE 25th Convention of Electrical and Electronics Engineers in Israel, Eilat, Israel, 3–5 December 2008; pp. 21–25. [Google Scholar] [CrossRef]

- Thielemans, S.; Ruderman, A.; Reznikov, B.; Melkebeek, J. Improved Natural Balancing With Modified Phase-Shifted PWM for Single-Leg Five-Level Flying-Capacitor Converters. IEEE Trans. Power Electron. 2012, 27, 1658–1667. [Google Scholar] [CrossRef] [Green Version]

- Ruderman, A.; Reznikov, B.; Thielemans, S. Four-level H-bridge flying capacitor converter voltage balance dynamics analysis. In Proceedings of the 2009 35th Annual Conference of IEEE Industrial Electronics, Porto, Portugal, 3–5 November 2009; pp. 498–503. [Google Scholar] [CrossRef]

- Mariethoz, S. Systematic Design of High-Performance Hybrid Cascaded Multilevel Inverters With Active Voltage Balance and Minimum Switching Losses. IEEE Trans. Power Electron. 2013, 28, 3100–3113. [Google Scholar] [CrossRef]

- Mademlis, G.; Liu, Y.; Saadat, N. Combined voltage balancing techniques of the DC link in five-level medium voltage NPC back-to-back converters for offshore renewable generation. In Proceedings of the 2017 19th European Conference on Power Electronics and Applications (EPE’17 ECCE Europe), Warsaw, Poland, 11–14 September 2017; pp. P.1–P.10. [Google Scholar]

- He, L.; Sun, J.; Lin, Z.; Cheng, B. Capacitor-Voltage Self-Balance Multilevel Inverter with Unequal Amplitude Carrier-Based APODPWM. IEEE Trans. Power Electron. 2021, 36, 14002–14013. [Google Scholar] [CrossRef]

- Wheeler, P.W.; Empringham, L.; Gerry, D. Improved output waveform quality for multi-level H-bridge chain converters using unequal cell voltages. In Proceedings of the 2000 Eighth International Conference on Power Electronics and Variable Speed Drives (IEE Conf. Publ. No. 475), London, UK, 18–19 September 2000; pp. 536–540. [Google Scholar]

- Babaei, E.; Hosseini, S.H. Charge balance control methods for asymmetrical cascade multilevel converters. In Proceedings of the 2007 International Conference on Electrical Machines and Systems (ICEMS), Seoul, Korea, 8–11 October 2007; pp. 74–79. [Google Scholar]

- Veenstra, M.; Rufer, A. Control of a hybrid asymmetric multilevel inverter for competitive medium-voltage industrial drives. IEEE Trans. Ind. Appl. 2005, 41, 655–664. [Google Scholar] [CrossRef]

- Fuentes, C.D.; Rojas, C.A.; Renaudineau, H.; Kouro, S.; Perez, M.A.; Meynard, T. Experimental Validation of a Single DC Bus Cascaded H-Bridge Multilevel Inverter for Multistring Photovoltaic Systems. IEEE Trans. Ind. Electron. 2017, 64, 930–934. [Google Scholar] [CrossRef]

- Monteiro, A.P.; Jacobina, C.B.; Méllo, J.P.R.A.; de Freitas, N.B.; Matias, R.R. Capacitor Voltage Balancing for Single-Phase Asymmetric Cascaded H-Bridge Inverters. IEEE Trans. Ind. Appl. 2020, 56, 5129–5141. [Google Scholar] [CrossRef]

- Zambra, D.A.B.; Rech, C.; Pinheiro, J.R. Comparison of Neutral-Point-Clamped, Symmetrical, and Hybrid Asymmetrical Multilevel Inverters. IEEE Trans. Ind. Electron. 2010, 57, 2297–2306. [Google Scholar] [CrossRef]

- Mariethoz, S. Design and Control of High-Performance Modular Hybrid Asymmetrical Cascade Multilevel Inverters. IEEE Trans. Ind. Appl. 2014, 50, 4018–4027. [Google Scholar] [CrossRef]

- Kuder, M.; Kersten, A.; Bergmann, L.; Eckerle, R.; Helling, F.; Weyh, T. Exponential Modular Multilevel Converter for Low Voltage Applications. In Proceedings of the 2019 21st European Conference on Power Electronics and Applications (EPE ’19 ECCE Europe), Genova, Italy, 3–5 September 2019; pp. P.1–P.11. [Google Scholar] [CrossRef]

- Zygmanowski, M.; Michalak, J.; Grzesik, B. DC-link voltage balancing method for a hybrid asymmetric multilevel converter. In Proceedings of the 2013 15th European Conference on Power Electronics and Applications (EPE), Lille, France, 2–6 September 2013; pp. 1–10. [Google Scholar] [CrossRef]

- Vasu, R.; Chattopadhyay, S.K.; Chakraborty, C. Asymmetric Cascaded H-Bridge Multilevel Inverter With Single DC Source per Phase. IEEE Trans. Ind. Electron. 2020, 67, 5398–5409. [Google Scholar] [CrossRef]

- Ziaeinejad, S.; Sangsefidi, Y.; Mehrizi-Sani, A. A Generalized Switching Strategy and Capacitor Sizing Algorithm for Granular Multilevel Converters. IEEE Trans. Ind. Electron. 2018, 65, 4443–4453. [Google Scholar] [CrossRef]

- Moeini, A.; Wang, S. A DC Link Sensor-Less Voltage Balancing Technique for Cascaded H-Bridge Multilevel Converters with Asymmetric Selective Harmonic Current Mitigation-PWM. IEEE Trans. Power Electron. 2018, 33, 7571–7581. [Google Scholar] [CrossRef]

- Vahedi, H.; Al-Haddad, K. Single-DC-source five-level CHB inverter with sensor-less voltage balancing. In Proceedings of the IECON 2015—-41st Annual Conference of the IEEE Industrial Electronics Society, Yokohama, Japan, 9–12 November 2015. [Google Scholar] [CrossRef]

- Vahedi, H.; Labbé, P.; Al-Haddad, K. Sensor-Less Five-Level Packed U-Cell (PUC5) Inverter Operating in Stand-Alone and Grid-Connected Modes. IEEE Trans. Ind. Inform. 2016, 12, 361–370. [Google Scholar] [CrossRef]

- Kersten, A.; Kuder, M.; Marques-Lopez, J.L.; Schwitzgebel, F.; Thiringer, T.; Marquardt, R.; Weyh, T.; Eckerle, R. Sensorless Capacitor Voltage Balancing of a Grid-Tied, Single-Phase Hybrid Multilevel Converter with Asymmetric Capacitor Voltages using Dynamic Programming. In Proceedings of the IECON 2020 the 46th Annual Conference of the IEEE Industrial Electronics Society, Singapore, 18–21 October 2020; pp. 4288–4293. [Google Scholar] [CrossRef]

- Haghbin, S.; Thiringer, T.; Alatalo, M.; Karlsson, R. An LCL filter with an active compensation for a fast charger station. In Proceedings of the 2017 IEEE International Conference on Environment and Electrical Engineering and 2017 IEEE Industrial and Commercial Power Systems Europe (EEEIC/I CPS Europe), Milan, Italy, 6–9 June 2017; pp. 1–5. [Google Scholar]

- Liserre, M.; Blaabjerg, F.; Hansen, S. Design and control of an LCL-filter-based three-phase active rectifier. IEEE Trans. Ind. Appl. 2005, 41, 1281–1291. [Google Scholar] [CrossRef]

- IEEE. IEEE Guide for Smart Grid Interoperability of Energy Technology and Information Technology Operation with the Electric Power System (EPS), End-Use Applications, and Loads; IEEE Std 519-2014 (Revision of IEEE Std 519-1992); IEEE: Piscataway, NJ, USA, 2014; pp. 1–126. [CrossRef]

- Lee, C.T.; Hsu, C.W.; Cheng, P.T. A Low-Voltage Ride-Through Technique for Grid-Connected Converters of Distributed Energy Resources. IEEE Trans. Ind. Appl. 2011, 47, 1821–1832. [Google Scholar] [CrossRef]

- Ciobotaru, M.; Teodorescu, R.; Blaabjerg, F. A new single-phase PLL structure based on second order generalized integrator. In Proceedings of the 2006 37th IEEE Power Electronics Specialists Conference, Jeju, Korea, 18–22 June 2006; pp. 1–6. [Google Scholar] [CrossRef]

- Cha, H.; Vu, T.K.; Kim, J.E. Design and control of Proportional-Resonant controller based Photovoltaic power conditioning system. In Proceedings of the 2009 IEEE Energy Conversion Congress and Exposition, San Jose, CA, USA, 20–24 September 2009; pp. 2198–2205. [Google Scholar]

- Richter, S.A.; De Doncker, R.W. Digital proportional-resonant (PR) control with anti-windup applied to a voltage-source inverter. In Proceedings of the 2011 14th European Conference on Power Electronics and Applications, Birmingham, UK, 30 August–1 September 2011; pp. 1–10. [Google Scholar]

- Harnefors, L. Control of Variable-Speed Drives; Applied Signal Processing and Control, Department of Electronics, Mälardalen University: Västerås, Sweden, 2002. [Google Scholar]

- Sharifabadi, K.; Harnefors, L.; Nee, H.P.; Norrga, S.; Teodorescu, R. Design, Control, and Application of Modular Multilevel Converters for HVDC Transmission Systems; John Wiley & Sons: Hoboken, NJ, USA, 2016. [Google Scholar]

- Kim, S.K.; Park, C.R.; Lee, Y.I. One-step ahead model predictive controller of three-phase inverter for uninterruptible power supply applications. In Proceedings of the 2014 IEEE Applied Power Electronics Conference and Exposition-APEC 2014, Fort Worth, TX, USA, 16–20 March 2014; pp. 2735–2740. [Google Scholar] [CrossRef]

- Benzaquen, J.; Fateh, F.; Shadmand, M.B.; Mirafzal, B. One-Step-Ahead Adaptive Control Scheme for Active Rectifiers in Wild Frequency Applications. In Proceedings of the 2019 IEEE Applied Power Electronics Conference and Exposition (APEC), Anaheim, CA, USA, 17–21 March 2019; pp. 588–593. [Google Scholar] [CrossRef]

- Karamanakos, P.; Liegmann, E.; Geyer, T.; Kennel, R. Model Predictive Control of Power Electronic Systems: Methods, Results, and Challenges. IEEE Open J. Ind. Appl. 2020, 1, 95–114. [Google Scholar] [CrossRef]

- Kermani, M. Transient voltage and frequency stability of an isolated microgrid based on energy storage systems. In Proceedings of the 2016 IEEE 16th International Conference on Environment and Electrical Engineering (EEEIC), Florence, Italy, 7–10 June 2016; pp. 1–5. [Google Scholar] [CrossRef]

- LaSalle, J. The extent of asymptotic stability. Proc. Natl. Acad. Sci. USA 1960, 46, 363. [Google Scholar] [CrossRef] [Green Version]

- Chen, F.C.; Khalil, H.K. Adaptive control of nonlinear systems using neural networks. Int. J. Control 1992, 55, 1299–1317. [Google Scholar] [CrossRef]

- Imperix Ltd. PEN8018-NPC Building Block. Available online: https://cdn.imperix.com/wp-content/uploads/document/PEN8018.pdf (accessed on 29 September 2020).

- Imperix Ltd. PEH2015-Full Bridge Building Block. Available online: https://cdn.imperix.com/wp-content/uploads/document/PEH2015.pdf (accessed on 29 September 2020).

- Imperix Ltd. B-Box RCP-RAPID Prototyping Controller. Available online: https://cdn.imperix.com/wp-content/uploads/document/B-Box_Datasheet.pdf (accessed on 12 November 2020).

- IEEE. IEEE Recommended Practice and Requirements for Harmonic Control in Electric Power Systems; IEEE Std 519-2014 (Revision of IEEE Std 519-1992); IEEE: Piscataway, NJ, USA, 2014; pp. 1–29. [Google Scholar] [CrossRef]

- Marzoughi, A.; Imaneini, H. An optimal selective harmonic mitigation for cascaded H-bridge converters. In Proceedings of the 2012 11th International Conference on Environment and Electrical Engineering, Venice, Italy, 18–25 May 2012; pp. 752–757. [Google Scholar] [CrossRef]

- Kersten, A.; Kuder, M.; Singer, A.; Han, W.; Thiringer, T.; Weyh, T.; Eckerle, R. Elimination/Mitigation of Output Voltage Harmonics for Multilevel Converters Operated at Fundamental Switching Frequency using Matlab’s Genetic Algorithm Optimization. In Proceedings of the 2020 22nd European Conference on Power Electronics and Applications (EPE’20 ECCE Europe), Lyon, France, 7–11 September 2020; pp. 1–12. [Google Scholar] [CrossRef]

- Du, Z.; Tolbert, L.M.; Ozpineci, B.; Chiasson, J.N. Fundamental Frequency Switching Strategies of a Seven-Level Hybrid Cascaded H-Bridge Multilevel Inverter. IEEE Trans. Power Electron. 2009, 24, 25–33. [Google Scholar] [CrossRef] [Green Version]

| 1 | −1 | −1 | −1 | −1 |

| 0 | 1 | −1 | −1 | −1 |

| 0 | 0 | 1 | −1 | −1 |

| 0 | 0 | 0 | 1 | −1 |

| 0 | 0 | 0 | 0 | 1 |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2022 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Kuder, M.; Kersten, A.; Marques-Lopez, J.-L.; Estaller, J.; Buberger, J.; Schwitzgebel, F.; Thiringer, T.; Lesnicar, A.; Marquardt, R.; Weyh, T.; et al. Capacitor Voltage Balancing of a Grid-Tied, Cascaded Multilevel Converter with Binary Asymmetric Voltage Levels Using an Optimal One-Step-Ahead Switching-State Combination Approach. Energies 2022, 15, 575. https://doi.org/10.3390/en15020575

Kuder M, Kersten A, Marques-Lopez J-L, Estaller J, Buberger J, Schwitzgebel F, Thiringer T, Lesnicar A, Marquardt R, Weyh T, et al. Capacitor Voltage Balancing of a Grid-Tied, Cascaded Multilevel Converter with Binary Asymmetric Voltage Levels Using an Optimal One-Step-Ahead Switching-State Combination Approach. Energies. 2022; 15(2):575. https://doi.org/10.3390/en15020575

Chicago/Turabian StyleKuder, Manuel, Anton Kersten, Jose-Luis Marques-Lopez, Julian Estaller, Johannes Buberger, Florian Schwitzgebel, Torbjörn Thiringer, Anton Lesnicar, Rainer Marquardt, Thomas Weyh, and et al. 2022. "Capacitor Voltage Balancing of a Grid-Tied, Cascaded Multilevel Converter with Binary Asymmetric Voltage Levels Using an Optimal One-Step-Ahead Switching-State Combination Approach" Energies 15, no. 2: 575. https://doi.org/10.3390/en15020575