Current Modulation of a Heterojunction Structure by an Ultra-Thin Graphene Base Electrode

Abstract

:1. Introduction

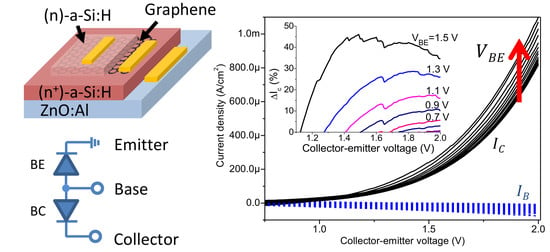

2. Materials and Methods

3. Results and Discussion

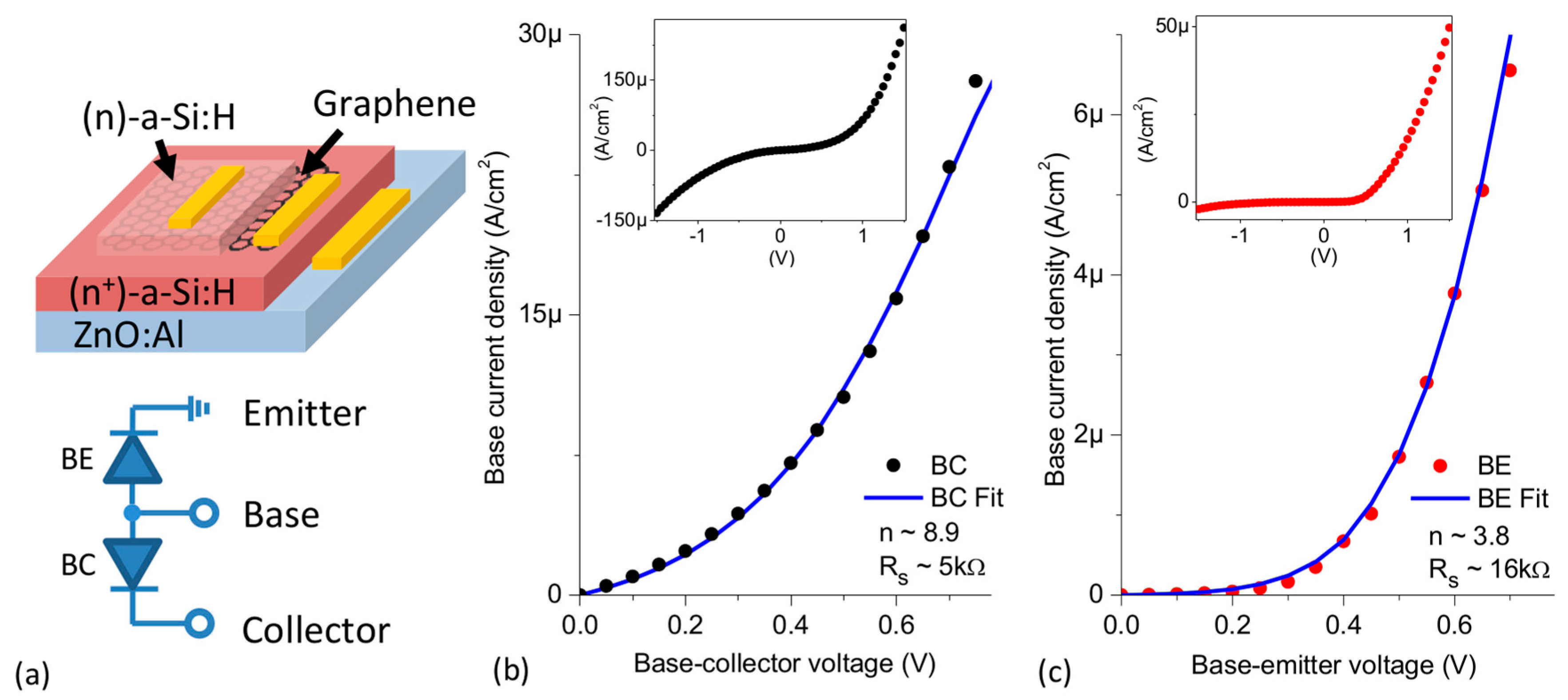

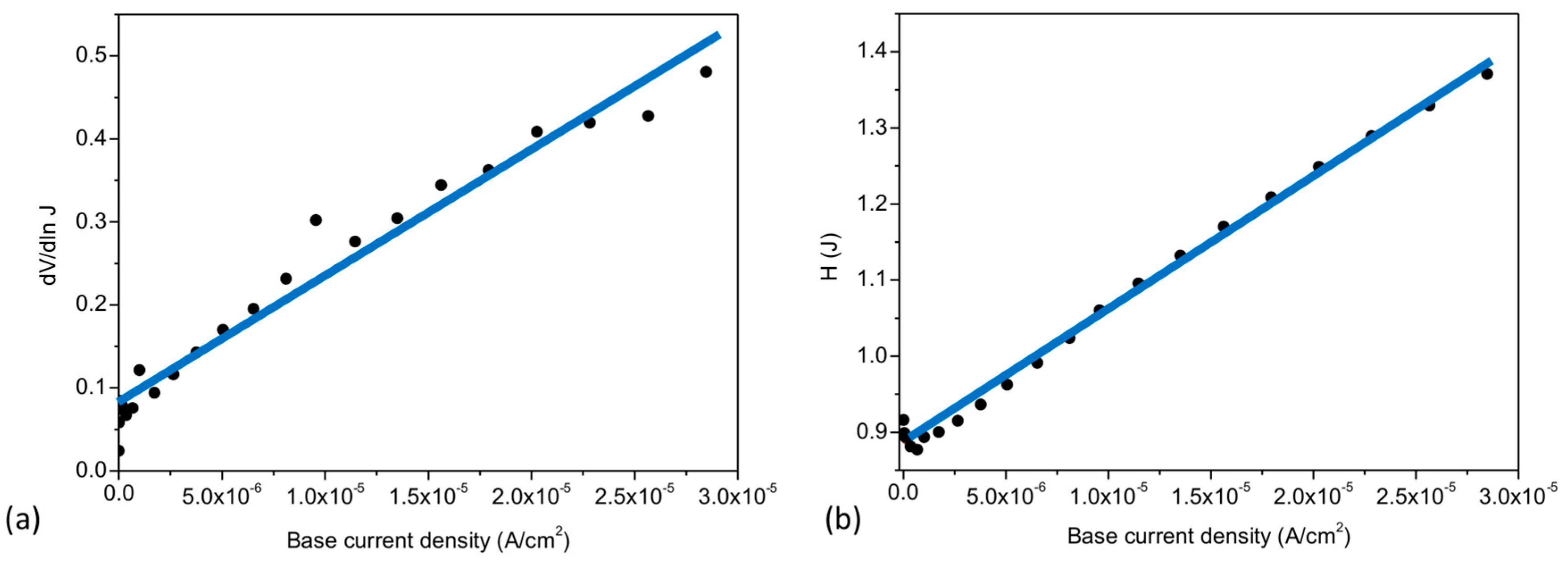

3.1. Diode Characterization

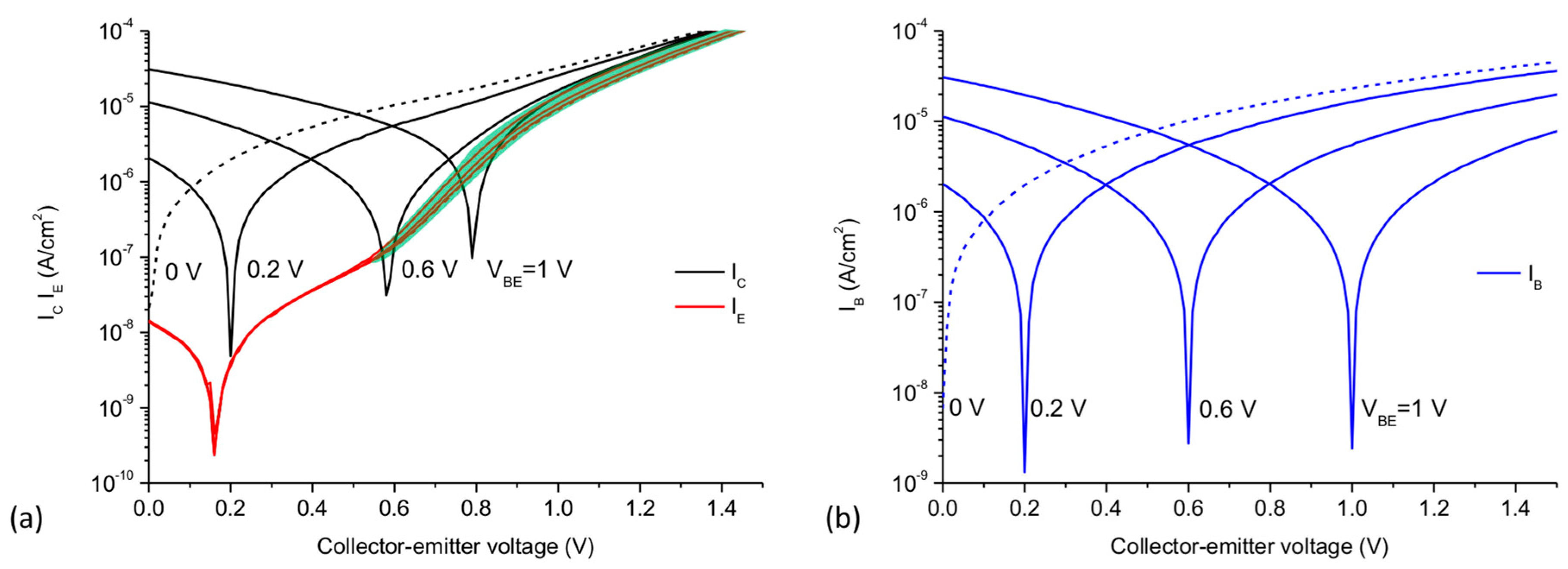

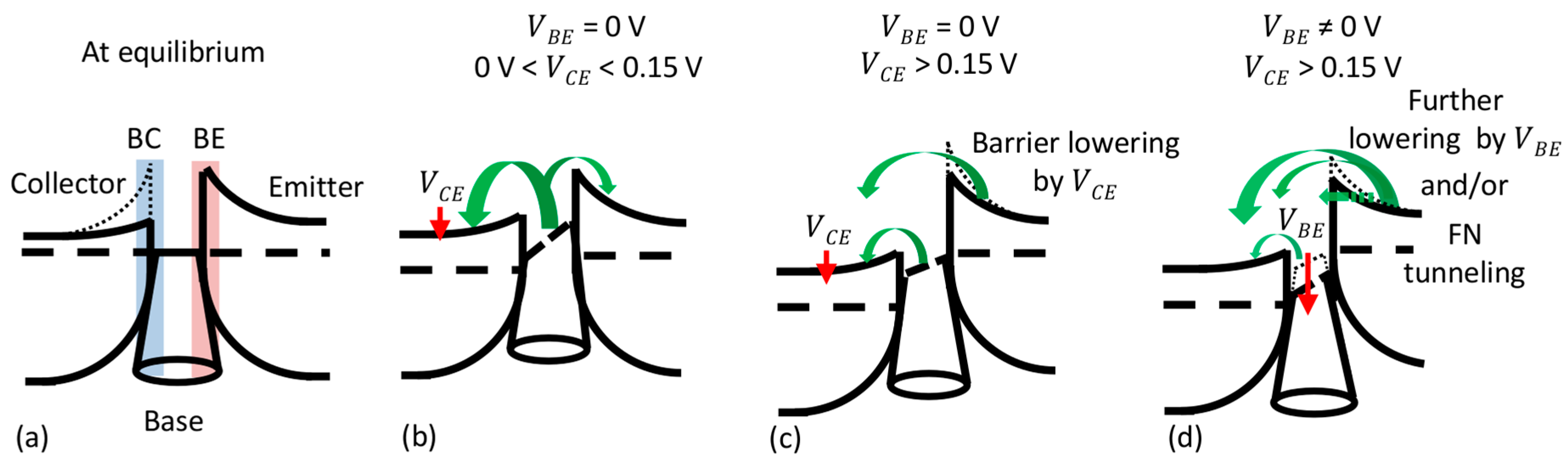

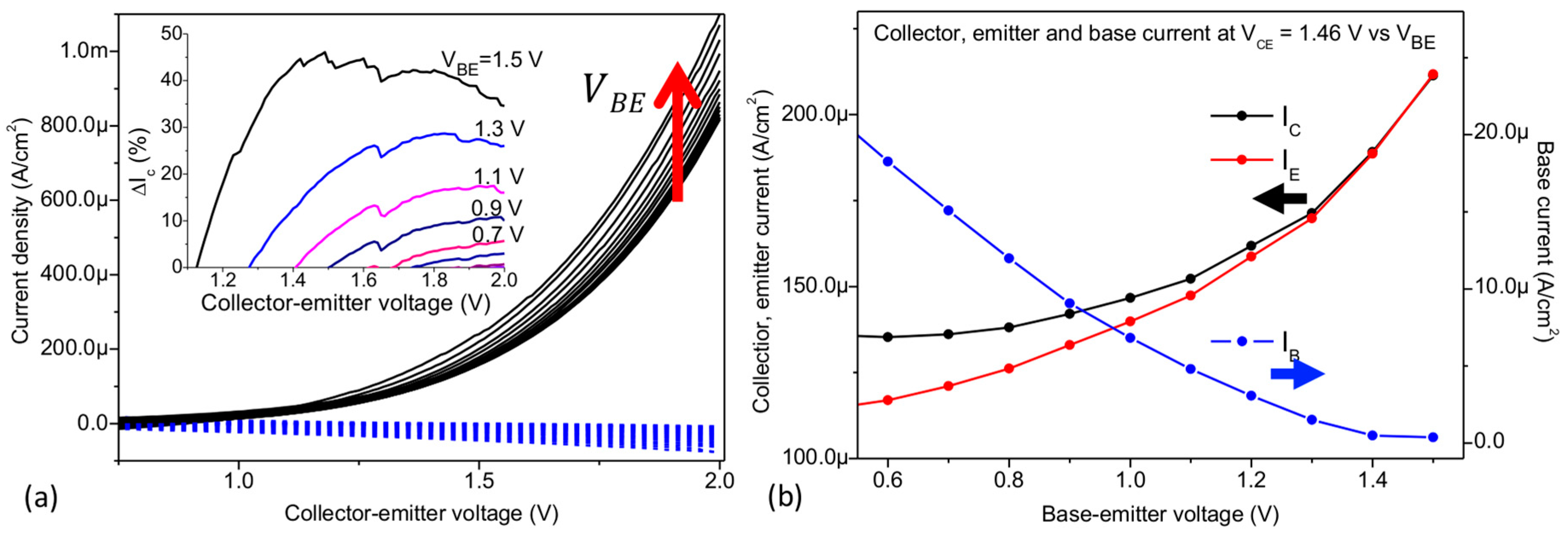

3.2. Three-Terminal Characterization

4. Conclusions

Acknowledgments

Author Contributions

Conflicts of Interest

References

- Mehr, W.; Dabrowski, J.; Scheytt, J.C.; Lippert, G.; Xie, Y.H.; Lemme, M.C.; Ostling, M.; Lupina, G. Vertical graphene base transistor. IEEE Electron Device Lett. 2012, 33, 691. [Google Scholar] [CrossRef]

- Vaziri, S.; Lupina, G.; Henkel, C.; Smith, A.D.; Östling, M.; Dabrowski, J.; Mehr, W.; Lemme, M.C. A graphene-based hot electron transistor. Nano Lett. 2013, 13, 1435–1439. [Google Scholar] [CrossRef] [PubMed]

- Zeng, C.; Song, E.B.; Wang, M.; Lee, S.; Torres, C.M.; Tang, J.; Weiller, B.H.; Wang, K.L. Vertical graphene-base hot-electron transistor. Nano Lett. 2013, 13, 2370–2375. [Google Scholar] [CrossRef] [PubMed]

- Di Lecce, V.; Grassi, R.; Gnudi, A.; Gnani, E.; Reggiani, S.; Baccarani, G. Graphene-base heterojunction transistor: An attractive device for Terahertz operation. IEEE Trans. Electron Devices 2013, 60, 4263–4268. [Google Scholar] [CrossRef]

- Bae, S.; Kim, H.; Lee, Y.; Xu, X.; Park, J.; Kim, K.; Kim, H.; Ahn, J.; Hong, B.; Lijima, S. Roll-to-roll production of 30-inch graphene films for transparent electrodes. Nat. Nanotechnol. 2010, 5, 574–578. [Google Scholar] [CrossRef] [PubMed]

- Wong, W.S.; Salleo, A. Flexible Electronics: Materials and Applications; Springer Science & Business Media: New York, NJ, USA, 2009; ISBN 978-0-387-74362-2. [Google Scholar]

- Zhou, L.; Jung, S.; Brandon, E.; Jackson, T.N. Flexible substrate micro-crystalline silicon and gated amorphous silicon strain sensors. IEEE Trans. Electron Devices 2006, 53, 380–385. [Google Scholar] [CrossRef]

- Di Bartolomeo, A. Graphene Schottky diodes: An experimental review of the rectifying graphene/semiconductor heterojunction. Phys. Rep. 2016, 606, 1–58. [Google Scholar] [CrossRef]

- Gluba, M.A.; Amkreutz, D.; Troppenz, G.V.; Rappich, J.; Nickel, N.H. Embedded graphene for large-area silicon-based devices. Appl. Phys. Lett. 2013, 103, 1–5. [Google Scholar] [CrossRef]

- Arezki, H.; Boutchich, M.; Alamarguy, D.; Madouri, A.; Alvarez, J.; Cabarrocas, P.; Kleider, J.; Yao, F.; Lee, Y.H. Electronic properties of embedded graphene: doped amorphous silicon/CVD graphene heterostructures. J. Phys. Condens. Matter 2016, 28, 404001. [Google Scholar] [CrossRef] [PubMed]

- Lupina, G.; Strobel, C.; Dabrowski, J.; Lippert, G.; Kitzmann, J.; Krause, H.M.; Wenger, C.; Lukosius, M.; Wolff, A.; Albert, M.; et al. Plasma-enhanced chemical vapor deposition of amorphous Si on graphene. Appl. Phys. Lett. 2016, 108, 193105. [Google Scholar] [CrossRef]

- Heintze, M.; Zedlitz, R. New diagnostic aspects of high rate a-Si:H deposition in a VHF plasma. J. Non-Cryst. Solids 1996, 198, 1038–1041. [Google Scholar] [CrossRef]

- Strobel, C.; Chavarin, C.A.; Kitzmann, J.; Lupina, G.; Wenger, C.; Albert, M.; Bartha, J.W. Towards high frequency heterojunction transistors: Electrical characterization of N-doped amorphous silicon-graphene diodes. J. Appl. Phys. 2017, 121, 245302. [Google Scholar] [CrossRef]

- Strobel, C.; Zimmermann, T.; Albert, M.; Bartha, J.W.; Kuske, J. Productivity potential of an inline deposition system for amorphous and microcrystalline silicon solar cells. Sol. Energy Mater Sol. Cells 2009, 93, 1598–1607, doi 101016/jsolmat200904023. [Google Scholar] [CrossRef]

- Goto, H.; Nagase, Y.; Takada, T.; Tahara, A.; Momma, Y. Analysis of highly doped collector transistors by using two-dimensional process/device simulation and its application of ECL circuits. IEEE Trans. Electron Devices 1991, 38, 1840–1844. [Google Scholar] [CrossRef]

- Yang, H.; Heo, J.; Park, S.; Song, H.J.; Seo, D.H.; Buyn, K.; Kim, P.; Yoo, I.; Chung, H.; Kim, K. Graphene barristor, a triode device with a gate-controlled Schottky barrier. Science 2012, 336, 1140–1143. [Google Scholar] [CrossRef] [PubMed]

- Di Bartolomeo, A.; Luongo, G.; Giubileo, F.; Funicello, N.; Niu, G.; Schroeder, T.; Lisker, M.; Lupina, G. Hybrid graphene/silicon Schottkly photodiode with intrinsic gating effect. 2D Materials 2017, 4, 025075. [Google Scholar] [CrossRef]

- Di Bartolomeo, A.; Giubileo, F.; Romeo, F.; Sabatino, P.; Carapella, G.; Iemmo, L.; Schroeder, T.; Lupina, G. Graphene field effect transistors with niobium contacts and asymmetric transfer characteristics. Nanotechnology 2015, 26, 475202. [Google Scholar] [CrossRef] [PubMed]

- Singh, A.; Uddin, M.A.; Sudarshan, T.; Koley, G. Tunable reverse-biased graphene/silicon heterojunction Schottky diode sensor. Small 2014, 10, 15551565. [Google Scholar] [CrossRef] [PubMed]

- Lin, Y.-J.; Lin, J.-H. Annealing effect on Schottky barrier inhomogeneity of graphene/n-type Si Schottky diodes. Appl. Surf. Sci. 2014, 311, 224–229. [Google Scholar] [CrossRef]

- Chen, C.-C.; Aykol, M.; Chang, C.-C.; Levi, A.F.; Cronin, S.B. Graphene-silicon Schottky diodes. Nano Lett. 2011, 11, 1863–1867. [Google Scholar] [CrossRef] [PubMed]

- Kishore, R.; Hotz, C.; Naseem, H.; Brown, W.D. Aluminum-induced crystallization of amorphous silicon (α-Si:H) at 150°C. Electrochem. Solid State Lett. 2001, 4, G14–G16. [Google Scholar] [CrossRef]

- Cheung, S.K.; Cheung, N.W. Extraction of Schottky diode parameters from forward current-voltage characteristics. Appl. Phys. Lett. 1986, 49, 85–87. [Google Scholar] [CrossRef]

- Di Bartolomeo, A.; Giubileo, F.; Luongo, G.; Iemmo, L.; Martucciello, N.; Niu, G.; Fraschke, M.; Skibitzki, O.; Schroeder, T.; Lupina, G. Tunable Schottky barrier and high responsivity in graphene/Si-nanotip optoelectronic device. 2D Materials 2017, 4, 015024. [Google Scholar] [CrossRef]

- Lupina, G.; Kitzmann, J.; Costina, I.; Lukosius, M.; Wenger, C.; Wolff, A.; Vaziri, S.; Ostling, M.; Pasternak, I.; Krajewska, A.; et al. Residual metallic contamination of transferred chemical vapor deposited graphene. ACS Nano 2015, 9, 4776. [Google Scholar] [CrossRef] [PubMed]

- Hong, C.M.; Wagner, S. Inkjet printed copper source/drain metallization for amorphous silicon thin-film transistors. IEEE Electron Device Lett. 2000, 21, 384–386. [Google Scholar] [CrossRef]

- Alle, D.R.; Clark, L.T.; Vogt, B.D.; Shringarpure, R.; Venugopal, S.M.; Uppili, S.G.; Kaftanoglu, K.; Shivalingaiah, H.; Li, Z.P.; Ravindra, J.J.; et al. Circuit-level impact of a-Si:H thin-film-transistor degradation effects. IEEE Trans. Electron Devices 2009, 56, 1166–1176. [Google Scholar] [CrossRef]

- Sah, C. Fundamentals of Solid State Electronics; World Scientific Publishing: Singapore, 1991; ISBN 978-981-02-0637-6. [Google Scholar]

- Ray, S.; Mukhopadhyay, S.; Jana, T.; Carius, R. Transition from amorphous to microcrystalline Si:H: effects of substrate temperature and hydrogen dilution. J. Non-Cryst. Solids 2002, 299, 761–766. [Google Scholar] [CrossRef]

- Goto, M.; Toyoda, H.; Kitagawa, M.; Hirao, T.; Sugai, H. Low temperature growth of amorphous and polycrystalline silicon films from a modified inductively coupled plasma. Jpn. J. Appl. Phys. 1997, 36, 3714. [Google Scholar] [CrossRef]

- Chavarin, C.A.; Sagade, A.A.; Neumaier, D.; Bacher, G.; Mertin, W. On the origin of contact resistances in graphene devices fabricated by optical lithography. Appl. Phys. A 2016, 122, 58. [Google Scholar] [CrossRef]

- An, Y.; Behnam, A.; Pop, E.; Bosman, G.; Ural, A. Forward-bias diode parameters, electronic noise, and photoresponse of graphene/silicon Schottky junctions with an interfacial native oxide layer. J. Appl. Phys. 2015, 118, 114307. [Google Scholar] [CrossRef]

- Song, Y.; Li, X.; Mackin, C.; Zhang, X.; Fang, W.; Palacios, T.; Zhu, H.; Kong, J. Role of interfacial oxide in high-efficiency graphene–silicon Schottky barrier solar cells. Nano Lett. 2015, 15, 2104–2110. [Google Scholar] [CrossRef] [PubMed]

- Lee, N.J.; Yoo, J.W.; Choi, Y.J.; Kang, C.J.; Jeon, D.Y.; Kim, D.C.; Seo, S.; Chung, H.J. The interlayer screening effect of graphene sheets investigated by Kelvin probe force microscopy. Appl. Phys. Lett. 2009, 95, 222107. [Google Scholar] [CrossRef]

- Yu, Y.-J.; Zhao, Y.; Ryu, S.; Brus, L.E.; Kim, K.S.; Kim, P. Tuning the graphene work function by electric field effect. Nano Lett. 2009, 9, 3430–3434. [Google Scholar] [CrossRef] [PubMed]

- Chien, F.-C. A Review on Conduction Mechanisms in Dielectric Films. Adv. Mater. Sci. Eng. 2014, 578168. [Google Scholar] [CrossRef]

- Mouafo, L.D.N.; Godel, F.; Froehlicher, G.; Berciaud, S.; Doudin, B.; Venkata Kamalakar, M.; Dayen, J.-F. Tuning contact transport mechanisms in bilayer MoSe2 transistors up to Fowler–Nordheim regime. 2D Materials 2016, 4. [Google Scholar] [CrossRef]

- Mews, M.; Liebhaber, M.; Rech, B.; Korte, L. Valence band alignment and hole transport in amorphous/crystalline silicon heterojunction solar cells. Appl. Phys. Lett. 2015, 107, 013902. [Google Scholar] [CrossRef] [Green Version]

- Lee, J.-H.; Lee, E.K.; Joo, W.-J.; Jang, Y.; Kim, B.-S.; Lim, J.Y.; Choi, S.-H.; Ahn, S.J.; Ahn, J.R.; Park, M.-H.; et al. Wafer-Scale Growth of Single-crystal monolayer graphene on reusable hydrogen-terminated germanium. Science 2014, 344, 286–289. [Google Scholar] [CrossRef] [PubMed]

- Oostinga, J.B.; Heersche, H.B.; Liu, X.; Morpurgo, A.F.; Vandersypen, L.M. Gate-induced insulating state in bilayer graphene devices. Nat. Mater. 2008, 7, 151–157. [Google Scholar] [CrossRef] [PubMed]

- Jariwala, D.; Marks, T.J.; Hersam, M.C. Mixed-dimensional van der Waals heterostructures. Nat. Mater. 2017, 16, 170–181. [Google Scholar] [CrossRef] [PubMed]

- Di Bartolomeo, A.; Genovese, L.; Giubileo, F.; Iemmo, L.; Luongo, G.; Foller, T.; Schleberger, M. Hysteresis in the transfer characteristics of MoS2 transistors. 2D Materials 2017, 5. [Google Scholar] [CrossRef]

© 2018 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Alvarado Chavarin, C.; Strobel, C.; Kitzmann, J.; Di Bartolomeo, A.; Lukosius, M.; Albert, M.; Bartha, J.W.; Wenger, C. Current Modulation of a Heterojunction Structure by an Ultra-Thin Graphene Base Electrode. Materials 2018, 11, 345. https://doi.org/10.3390/ma11030345

Alvarado Chavarin C, Strobel C, Kitzmann J, Di Bartolomeo A, Lukosius M, Albert M, Bartha JW, Wenger C. Current Modulation of a Heterojunction Structure by an Ultra-Thin Graphene Base Electrode. Materials. 2018; 11(3):345. https://doi.org/10.3390/ma11030345

Chicago/Turabian StyleAlvarado Chavarin, Carlos, Carsten Strobel, Julia Kitzmann, Antonio Di Bartolomeo, Mindaugas Lukosius, Matthias Albert, Johann Wolfgang Bartha, and Christian Wenger. 2018. "Current Modulation of a Heterojunction Structure by an Ultra-Thin Graphene Base Electrode" Materials 11, no. 3: 345. https://doi.org/10.3390/ma11030345

APA StyleAlvarado Chavarin, C., Strobel, C., Kitzmann, J., Di Bartolomeo, A., Lukosius, M., Albert, M., Bartha, J. W., & Wenger, C. (2018). Current Modulation of a Heterojunction Structure by an Ultra-Thin Graphene Base Electrode. Materials, 11(3), 345. https://doi.org/10.3390/ma11030345