High On-Current Ge-Channel Heterojunction Tunnel Field-Effect Transistor Using Direct Band-to-Band Tunneling

Abstract

:1. Introduction

2. Result and Discussion

3. Summary

Author Contributions

Funding

Conflicts of Interest

References

- The International Technology Roadmap for Semiconductors. Available online: http://www.itrs.net/ (accessed on 24 November 2018).

- Lundstrom, M. Device physics at the scaling limit: What matters? In Proceedings of the International Electron Device Meeting (IEDM), Washington, DC, USA, 8–10 December 2003; pp. 789–792. [Google Scholar]

- Frank, D.J.; Robert, R.J.; Nowak, E.; Solomon, P.M.; Taur, Y.; Wong, H.-S.P. Device scaling limits of Si MOSFETs and their application dependencies. Proc. IEEE 2001, 89, 259–288. [Google Scholar] [CrossRef]

- Cheung, K.P. On the 60 mV/dec @300 K Limit for MOSFET Subthreshold Swing. In Proceedings of the Symposium VLSI-TSA Technology Systems and Applications, Hsin Chu, Taiwan, 26–28 April 2010; pp. 72–73. [Google Scholar]

- Li, K.-S.; Chen, P.-G.; Lai, T.-Y.; Lin, C.-H.; Cheng, C.-C.; Chen, C.-C.; Wei, Y.-J.; Hou, Y.-F.; Liao, M.-H.; Lee, M.-H.; et al. Sub-60mV-Swing Negative-Capacitance FinFET without Hysteresis. In Proceedings of the International Electron Device Meeting (IEDM), Washington, DC, USA, 7–9 December 2015; pp. 620–623. [Google Scholar]

- Lin, C.-I.; Khan, A.I.; Salahuddin, S.; Hu, C. Effects of the variation of ferroelectric properties on negative capacitance FET characteristics. IEEE Trans. Electron. Devices 2016, 63, 2197–2199. [Google Scholar] [CrossRef]

- McGuire, F.A.; Cheng, Z.; Price, K.; Franklin, A.D. Sub-60 mV/decade switching in 2D negative capacitance field-effect transistors with integrated ferroelectric polymer. Appl. Phys. Lett. 2016, 109, 093101. [Google Scholar] [CrossRef] [Green Version]

- Huang, Q.; Huang, R.; Pan, Y.; Tan, S.; Wang, Y. Resistive-Gate Field-Effect Transistor: A Novel Steep-Slope Device Based on a Metal—Insulator—Metal—Oxide Gate Stack. IEEE Electron Device Lett. 2014, 35, 877–879. [Google Scholar] [CrossRef]

- Kam, H.; Lee, D.T.; Howe, R.T.; King, T.-J. A new nano-electro-mechanical field effect transistor (NEMFET) design for low-power electronics. In Proceedings of the International Electron Device Meeting (IEDM), Washington, DC, USA, 5–7 December 2005; pp. 463–466. [Google Scholar]

- Abele, N.; Fritschi, N.; Boucart, K.; Casset, F.; Ancey, P.; Ionescu, A.M. Suspended-gate MOSFET: Bringing new MEMS functionality into solid-state MOS transistor. In Proceedings of the International Electron Device Meeting (IEDM), Washington, DC, USA, 5–7 December 2005; pp. 1075–1077. [Google Scholar]

- Padilla, A.; Yeung, C.W.; Shin, C.; Hu, C.; Liu, T.-J.K. Feedback FET: A novel transistor exhibiting steep switching behavior at low bias voltages. In Proceedings of the International Electron Device Meeting (IEDM), San Francisco, CA, USA, 15–17 December 2008; pp. 171–174. [Google Scholar]

- Hwang, S.; Kim, H.; Kwon, D.W.; Lee, J.-H.; Park, B.-G. Si1-xGex positive feedback field-effect transistor with steep subthreshold swing for low-voltage operation. J. Semicond. Technol. Sci. 2017, 17, 216–222. [Google Scholar] [CrossRef]

- Choi, W.Y.; Song, J.Y.; Lee, J.D.; Park, Y.J.; Park, B.-G. 100-nm n-/p-channel I-MOS using a novel self-aligned structure. IEEE Electron Device Lett. 2005, 26, 261–263. [Google Scholar] [CrossRef]

- Ramaswamy, S.; Kumar, M.J. Junction-less impact ionization MOS: Proposal and investigation. IEEE Trans. Electron Devices 2014, 61, 4295–4298. [Google Scholar] [CrossRef]

- Ionescu, A.M.; Riel, H. Tunnel field-effect transistors as energy-efficient electronic switches. Nature 2011, 479, 329–337. [Google Scholar] [CrossRef]

- Choi, W.Y.; Park, B.-G.; Lee, J.D.; Liu, T.-J.K. Tunneling field-effect transistors (TFETs) with subthreshold swing (SS) less than 60 mV/dec. IEEE Electron Device Lett. 2007, 28, 743–745. [Google Scholar] [CrossRef]

- Kim, S.W.; Kim, J.H.; Liu, T.-J.K.; Choi, W.Y.; Park, B.-G. Demonstration of L-shaped tunnel field-effect transistors. IEEE Trans. Electron Devices 2016, 63, 1774–1778. [Google Scholar] [CrossRef]

- Lee, R.; Kwon, D.W.; Kim, S.; Kim, D.H.; Park, B.-G. Investigation of feasibility of tunneling field effect transistor (TFET) as highly sensitive and multi-sensing biosensors. J. Semicond. Technol. Sci. 2017, 17, 141–146. [Google Scholar] [CrossRef]

- Mayer, F.; Le Royer, C.; Damlencourt, J.F.; Romanjek, K.; Andrieu, F.; Tabone, F.C.; Previtali, B.; Deleonibus, S. Impact of SOI, Si1−xGexOI and GeOI substrates on CMOS compatible Tunnel FET performance. In Proceedings of the International Electron Device Meeting (IEDM), San Francisco, CA, USA, 15–17 December 2008; pp. 163–166. [Google Scholar]

- Gandhi, R.; Chen, Z.; Singh, N.; Banerjee, K.; Lee, S. CMOS-compatible vertical-silicon-nanowire gate-all-around ptype tunneling FETs with ≤50-mV/decade subthreshold swing. IEEE Electron Device Lett. 2011, 32, 1504–1506. [Google Scholar] [CrossRef]

- Kim, S.H.; Kam, H.; Hu, C.; Liu, T.-J.K. Germanium-source tunnel field effect transistors with record high ION/IOFF. In Proceedings of the International Conference on VLSI Technology, Kyoto, Japan, 15–18 June 2009; pp. 178–179. [Google Scholar]

- Nayfeh, O.M.; Chleirigh, C.N.; Hennessy, J.; Gomez, L.; Hoyt, J.L.; Antoniadis, D.A. Design of tunneling field-effect transistors using strained-silicon/strained-germanium type-II staggered heterojunctions. IEEE Electron Device Lett. 2008, 29, 1074–1077. [Google Scholar] [CrossRef]

- Han, G.; Guo, P.; Yang, Y.; Zhan, C.; Zhou, Q.; Yeo, Y.-C. Silicon-based tunneling field-effect transistor with elevated germanium source formed on (110) silicon substrate. Appl. Phys. Lett. 2011, 98, 153502. [Google Scholar] [CrossRef]

- Kim, M.; Wakabayashi, Y.; Nakane, R.; Yokoyama, M.; Takenaka, M.; Takagi, S. High Ion/Ioff Ge-source ultrathin body strained-SOI tunnel FETs. In Proceedings of the International Electron Device Meeting (IEDM), San Francisco, CA, USA, 15–17 December 2014; pp. 331–334. [Google Scholar]

- Takagi, S.; Kim, M.; Noguchi, M.; Ji, S.-M.; Nishi, K.; Takenaka, M. III-V and Ge/strained SOI tunnel FET technologies for low power LSIs. In Proceedings of the International Conference on VLSI Technology, Kyoto, Japan, 16–19 June 2015; pp. 22–23. [Google Scholar]

- Krishnamohan, T.; Kim, D.; Raghunathan, S.; Saraswat, K. Double-gate strained-Ge heterostructure tunneling FET (TFET) with record high drive currents and <60 mV/dec subthreshold slope. In Proceedings of the International Electron Device Meeting (IEDM), San Francisco, CA, USA, 15–17 December 2008; pp. 1–3. [Google Scholar]

- Michielis, L.D.; Lattanzio, L.; Ionescu, A.M. Understanding the superlinear onset of tunnel-FET output characteristics. IEEE Electron Device Lett. 2012, 33, 1523–1525. [Google Scholar] [CrossRef]

- Toh, E.-H.; Wang, G.H.; Samudra, G.; Yeo, Y.-C. Device physics and design of double-gate tunneling field-effect transistor by silicon film thickness optimization. Appl. Phys. Lett. 2007, 90, 263507. [Google Scholar] [CrossRef]

- Synopsys, Inc. Sentaurus Device User Guide; Synopsys, Inc.: Mountain View, CA, USA, 2015. [Google Scholar]

- Kao, K.-H.; Verhulst, A.S.; Vandenberghe, W.G.; Sorée, B.; Groeseneken, G.; Meyer, K.D. Direct and indirect band-to-band tunneling in germanium-based TFETs. IEEE Trans. Electron Devices 2011, 59, 292–301. [Google Scholar] [CrossRef]

- Vandenberghe, W.; Soree, B.; Magnus, W.; Fischetti, M.V. Generalized phonon-assisted Zener tunneling in indirect semiconductors with non-uniform electric fields: A rigorous approach. J. Appl. Phys. 2011, 109, 124503. [Google Scholar] [CrossRef] [Green Version]

- Van de Put, M. Band-to-band tunneling in III-V semiconductor heterostructures. In Proceedings of the Eurocon 2013, Zagreb, Croatia, 1–4 July 2013; pp. 2134–2139. [Google Scholar]

- Verreck, D.; Van de Put, M.; Soree, B.; Verhulst, A.S.; Magnus, W.; Vandenberghe, W.; Collaert, N.; Thean, A.; Groeseneken, G. Quantum mechanical solver for confined heterostructure tunnel field-effect transistors. J. Appl. Phys. 2014, 115, 053706. [Google Scholar] [CrossRef]

- Takagi, S.; Kim, M.; Noguchi, M.; Nishi, K.; Takenaka, M. Tunneling FET device technologies using III-V and Ge materials. In Proceedings of the Berkeley Symposiums on Energy Efficient Electronic Systems (E3S), Berkeley, CA, USA, 1–2 October 2015; pp. 1–2. [Google Scholar]

- Kim, S.W.; Choi, W.Y. Hump effects of germanium/silicon heterojunction tunnel field-effect transistors. IEEE Trans. Electron Devices 2016, 63, 2583–2588. [Google Scholar] [CrossRef]

- Pan, J.; Woo, C.; Yang, C.-Y.; Bhandary, U.; Guggila, S.; Krishna, N.; Chung, H.; Hui, A.; Yu, B.; Xiang, Q.; et al. Replacement metal-gate NMOSFETs with ALD TaN/EP-Cu, PVD Ta, and PVD TaN electrode. IEEE Electron Device Lett. 2003, 24, 304–305. [Google Scholar] [CrossRef]

- Vincent, B.; Damlencourt, J.F.; Morand, Y.; Pouydebasque, A.; Le Royer, C.; Clavelier, L.; Dechoux, N.; Rivallin, P.; Nguyen, T.; Cristoloveanu, S.; et al. The Ge condensation technique: A solution for planar SOI/GeOI co-integration for advanced CMOS technologies? Mater. Sci. Semicond. Process. 2008, 11, 205–213. [Google Scholar] [CrossRef]

| Case | Source (p-type 1020 cm−3) | Channel (Undoped) | Drain (n-type 1018 cm−3) |

|---|---|---|---|

| Case1 | Si | Si | Si |

| Case2 | Ge | Ge | Ge |

| Case3 | Ge | Si | Ge |

| Case4 | Si | Ge | Si |

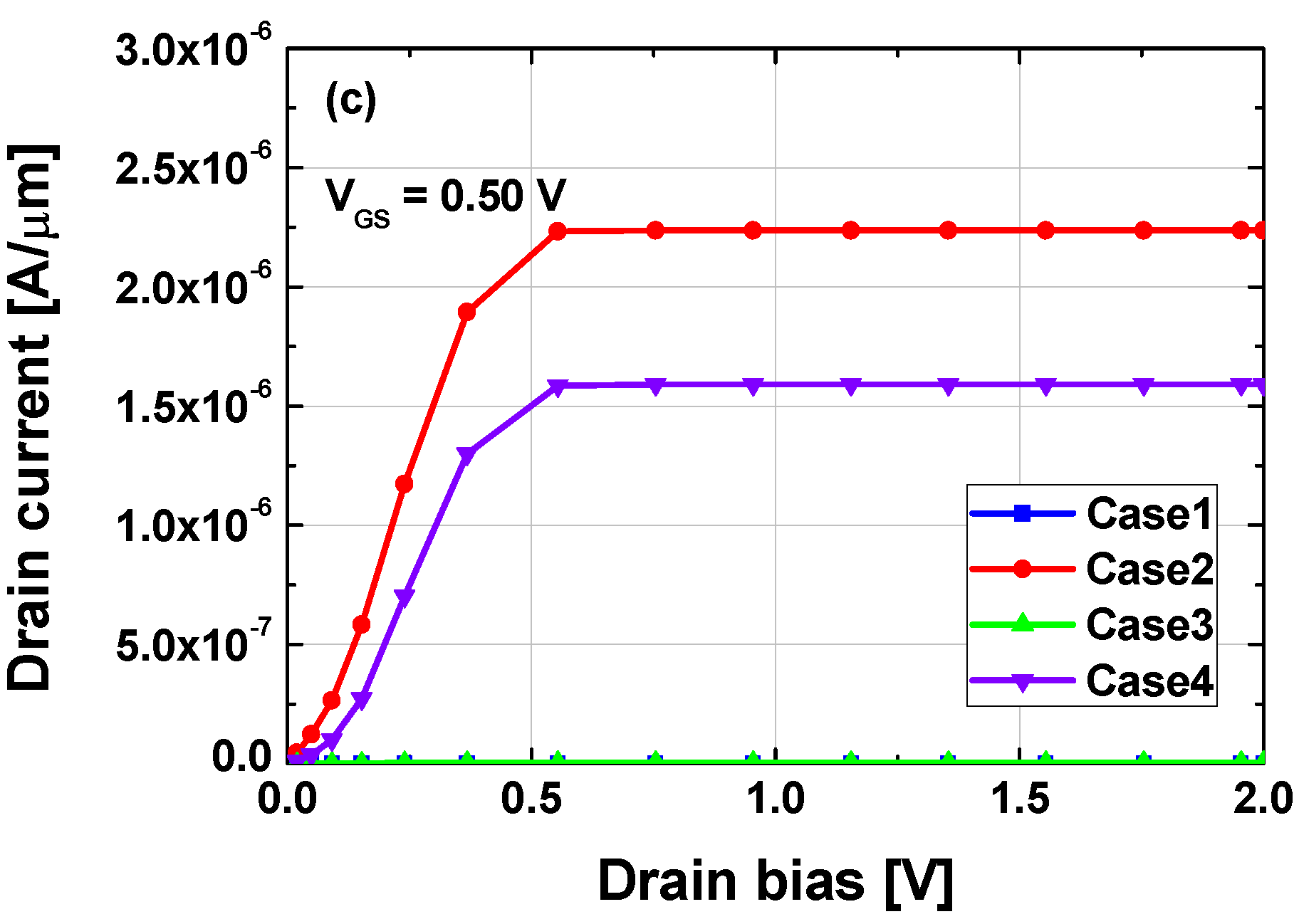

| Case | Subthreshold Swing (SS) [mV/dec] | Ion [μA/μm] | Ioff [pA/μm] | Ion/Ioff |

|---|---|---|---|---|

| Case1 | 40.5 | 0.1 | 0.001 | 1.0 × 108 |

| Case2 | 45.3 | 294.5 | 0.666 | 4.4 × 108 |

| Case3 | 68.4 | 1.5 | 0.602 | 2.5 × 106 |

| Case4 | 35.8 | 115.1 | 0.095 | 1.2 × 109 |

© 2019 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Kim, G.; Lee, J.; Kim, J.H.; Kim, S. High On-Current Ge-Channel Heterojunction Tunnel Field-Effect Transistor Using Direct Band-to-Band Tunneling. Micromachines 2019, 10, 77. https://doi.org/10.3390/mi10020077

Kim G, Lee J, Kim JH, Kim S. High On-Current Ge-Channel Heterojunction Tunnel Field-Effect Transistor Using Direct Band-to-Band Tunneling. Micromachines. 2019; 10(2):77. https://doi.org/10.3390/mi10020077

Chicago/Turabian StyleKim, Garam, Jaehong Lee, Jang Hyun Kim, and Sangwan Kim. 2019. "High On-Current Ge-Channel Heterojunction Tunnel Field-Effect Transistor Using Direct Band-to-Band Tunneling" Micromachines 10, no. 2: 77. https://doi.org/10.3390/mi10020077