A CMOS-Thyristor Based Temperature Sensor with +0.37 °C/−0.32 °C Inaccuracy

Abstract

:1. Introduction

2. Proposed CMOS Thyristor Based VCO

2.1. Basics of CMOS Thyristor Based Delay Cell

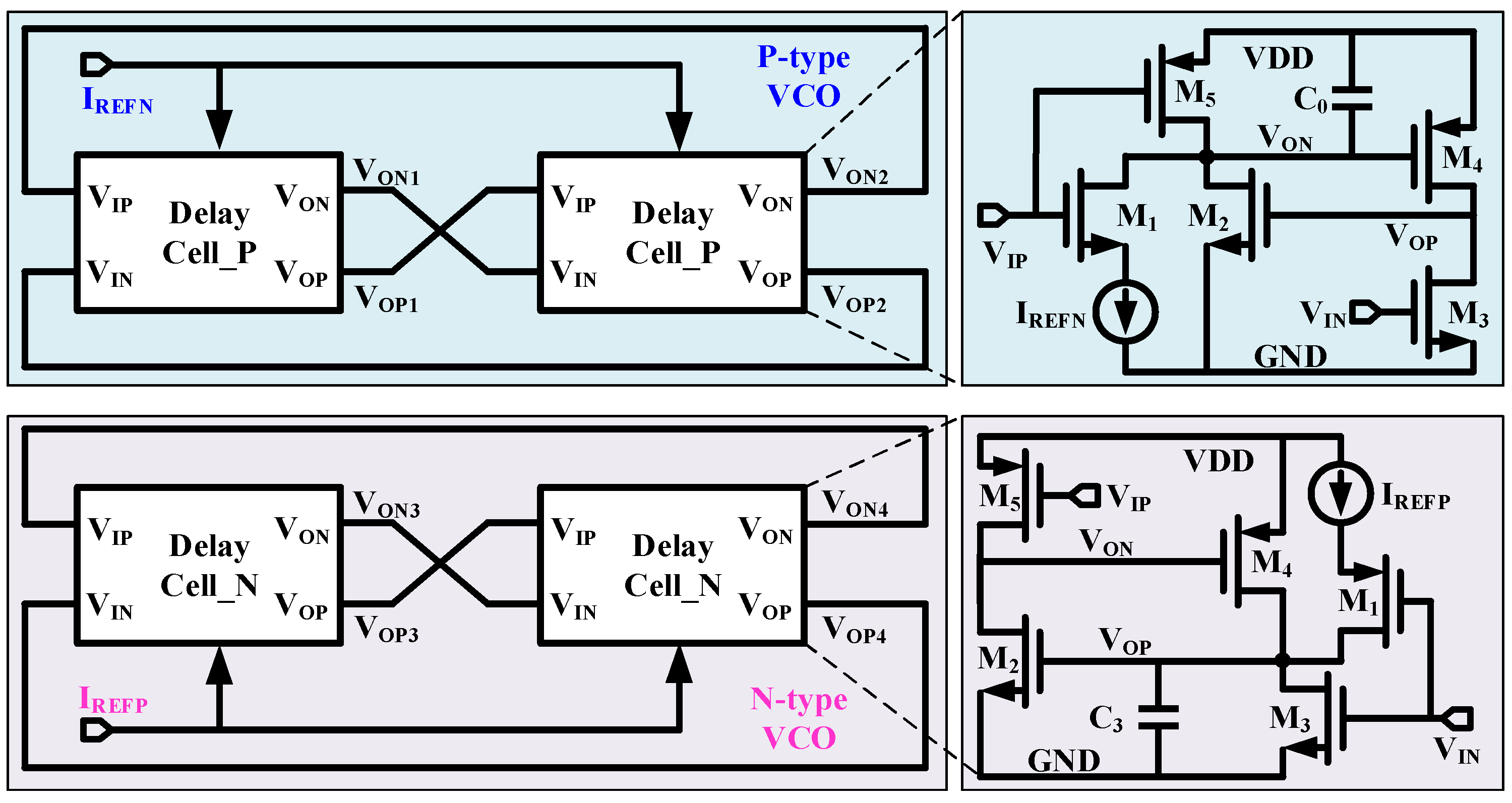

2.2. Proposed CMOS Thyristor Based VCO

3. Temperature Sensor Architecture

4. Circuit Implementation

4.1. Delay Cell

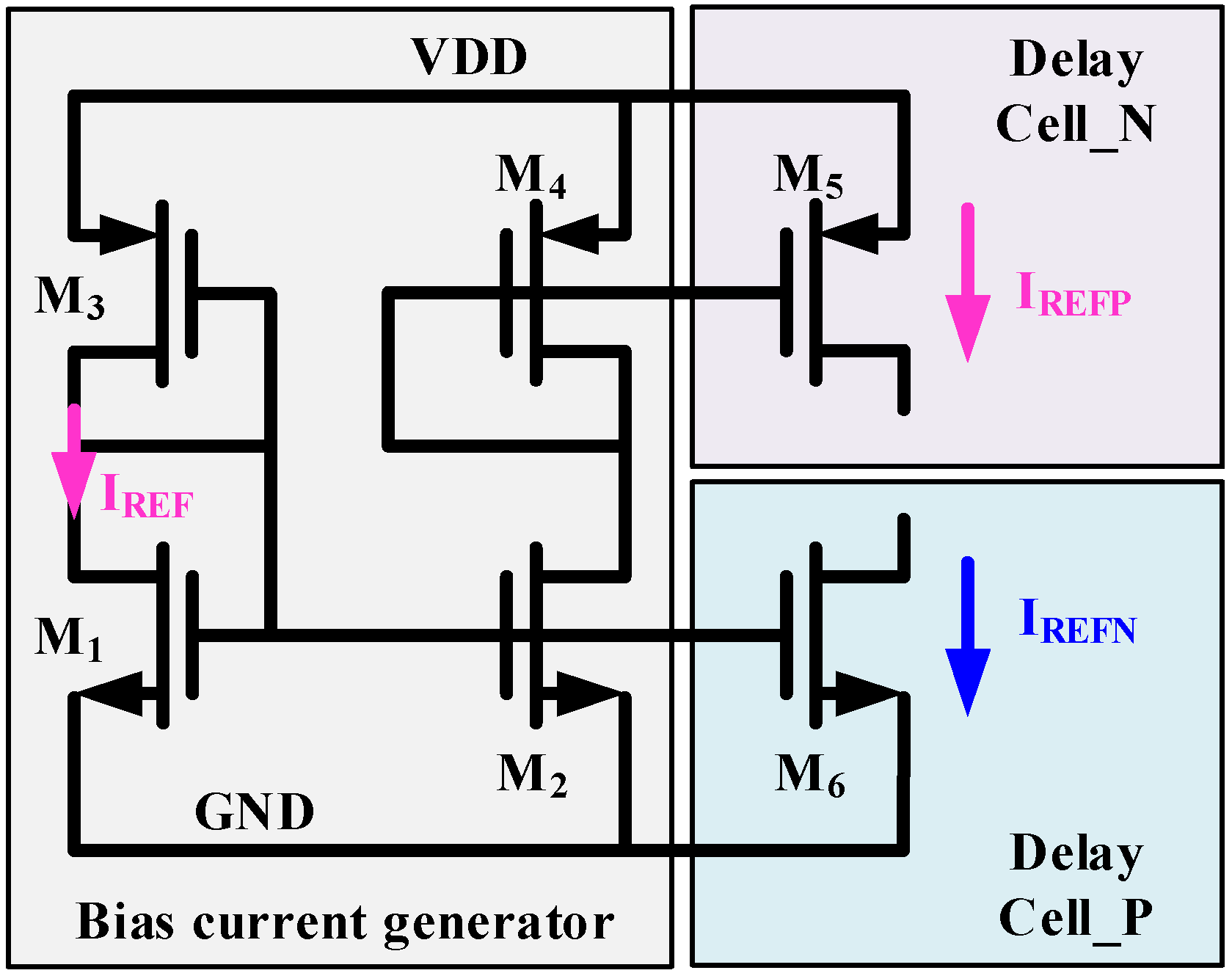

4.2. Bias Current Generator

4.3. Quasi-Static D-Flip Flop

5. Simulation Results

5.1. VCO Simulation

5.2. Temperature Sensor Simulation

6. Conclusions

Author Contributions

Funding

Conflicts of Interest

References

- Floyd, M.; Allen-Ware, M.; Rajamani, K.; Brock, B.; Lefurgy, C.; Drake, A.J.; Pesantez, L.; Gloekler, T.; Tierno, J.A.; Bose, P.; et al. Introducing the adaptive energy management features of the Power7 chip. IEEE Micro 2011, 31, 60–75. [Google Scholar] [CrossRef]

- Oshita, T.; Shor, J.; Duarte, D.E.; Kornfeld, A.; Zilberman, D. Compact BJT-based thermal sensor for processor applications in a 14 nm tri-gate CMOS process. IEEE J. Solid State Circuits 2015, 50, 799–807. [Google Scholar] [CrossRef]

- Shim, D.; Jeong, H.; Lee, H.; Rhee, C.; Jeong, D.K.; Kim, S. A process-variation-tolerant on-chip CMOS thermometer for auto temperature compensated self-refresh of low-power mobile DRAM. IEEE J. Solid State Circuits 2013, 48, 2550–2557. [Google Scholar] [CrossRef]

- Ha, S.; Akinin, A.; Park, J.; Kim, C.; Wang, H.; Maier, C.; Cauwenberghs, G.; Mercier, P.P. A 16-channel wireless neural interfacing SoC with RF-powered energy-replenishing adiabatic stimulation. In Proceedings of the 2015 Symposium on VLSI Circuits (VLSI Circuits), Kyoto, Japan, 17–19 June 2015; pp. C106–C107. [Google Scholar]

- Wang, H.; Mercier, P.P. A 51 pW reference-free capacitive discharging oscillator architecture operating at 2.8 Hz. In Proceedings of the 2015 IEEE Custom Integrated Circuits Conference (CICC), San Jose, CA, USA, 28–30 September 2015; pp. 1–4. [Google Scholar]

- Pertijs, M.A.P.; Makinwa, K.A.A.; Huijsing, J.H. ACMOS smart temperature sensor with a inaccuracy of C from to 125 C. IEEE J. Solid State Circuits 2005, 40, 2805–2815. [Google Scholar] [CrossRef]

- Aita, A.L.; Pertijs, M.A.P.; Makinwa, K.A.A.; Huijsing, J.H. A CMOS smart temperature sensor with a batch-calibrated inaccuracy of C from C to 130 C. In Proceedings of the 2009 IEEE International Solid-State Circuits Conference-Digest of Technical Papers, San Francisco, CA, USA, 8–12 February 2009; pp. 342–343. [Google Scholar]

- Sebastiano, F.; Breems, L.J.; Makinwa, K.A.A.; Drago, S.; Leenaerts, D.M.W.; Nauta, B. A 1.2-V 10-μW NPN-based temperature sensor in 65-nm CMOS with an inaccuracy of 0.2 °C from 70° C to 125 °C. IEEE J. Solid State Circuits 2010, 45, 2591–2601. [Google Scholar] [CrossRef] [Green Version]

- Pan, S.; Gürleyük, Ç.; Pimenta, M.F.; Makinwa, K.A.A. A 0.12 mm2 Wien-Bridge Temperature Sensor with 0.1 °C (3σ) Inaccuracy from −40 °C to 180 °C. In Proceedings of the 2019 IEEE International Solid-State Circuits Conference-Digest of Technical Papers, San Francisco, CA, USA, 17–21 February 2019; pp. 184–186. [Google Scholar]

- Pan, S.; Makinwa, K.A.A. A Wheatstone Bridge Temperature Sensor with a Resolution FoM of 20fJ.K2. In Proceedings of the 2019 IEEE International Solid-State Circuits Conference-Digest of Technical Papers, San Francisco, CA, USA, 17–21 February 2019; pp. 186–188. [Google Scholar]

- Yang, K.; Dong, Q.; Jung, W.; Zhang, Y.; Choi, M.; Blaauw, D.; Sylvester, D. A 0.6 nJ −0.22/+0.19 °C Inaccuracy Temperature Sensor Using Exponential Subthreshold Oscillation Dependence. In Proceedings of the 2017 IEEE International Solid-State Circuits Conference-Digest of Technical Papers, San Francisco, CA, USA, 5–9 February 2017; pp. 160–162. [Google Scholar]

- Jeong, S.; Foo, Z.; Lee, Y.; Sim, J.Y.; Blaauw, D.; Sylvester, D. A fully-integrated 71 nW CMOS temperature sensor for low power wireless sensor nodes. IEEE J. Solid State Circuits 2014, 49, 1682–1693. [Google Scholar] [CrossRef]

- Anand, T.; Makinwa, K.A.A.; Hanumolu, P.K. A VCO Based Highly Digital Temperature Sensor with 0.034 °C/mV Supply Sensitivity. IEEE J. Solid-State Circuits 2016, 51, 2651–2663. [Google Scholar] [CrossRef]

- Lin, Y.S.; Sylvester, D.; Blaauw, D. An Ultra Low Power 1 V, 220 nW Temperature Sensor for Passive Wireless Applications. In Proceedings of the 2008 IEEE Custom Integrated Circuits Conference(CICC), San Jose, CA, USA, 21–24 September 2008; pp. 507–510. [Google Scholar]

- Kim, C.K.; Kong, B.S.; Lee, C.G.; Jun, Y.H. CMOS Temperature Sensor with Ring Oscillator for Mobile DRAM Self-refresh Control. In Proceedings of the 2008 IEEE International Symposium on Circuits and Systems, Seattle, WA, USA, 18–21 May 2008; pp. 3094–3097. [Google Scholar]

- Hwang, S.; Koo, J.; Kim, K.; Lee, H.; Kim, C. A 0.008 mm2 500 μW 469 kS/s Frequency-to-Digital Converter Based CMOS Temperature Sensor with Process Variation Compensation. IEEE Trans. Circuits Syst. I Reg. Pap. 2013, 60, 2241–2248. [Google Scholar] [CrossRef]

- Kim, G.; Kim, M.K.; Chang, B.S.; Kim, W. A low-voltage, low-power CMOS delay element. IEEE J. Solid State Circuits 1996, 31, 966–971. [Google Scholar]

- Saft, B.; Schäfer, E.; Jäger, A.; Rolapp, A.; Hennig, E. An Improved Low-Power CMOS Thyristor-Based Micro-to-Millisecond Delay Element. In Proceedings of the ESSCIRC 2014—40th European Solid State Circuits Conference (ESSCIRC), Venice Lido, Italy, 22–26 September 2014; pp. 123–126. [Google Scholar]

- Tsividis, Y.P. Operation and Modeling of the MOS Transistor; McGraw-Hill: New York, NY, USA, 1987. [Google Scholar]

- Wang, H.; Mercier, P.P. A 3.4-pW 0.4-V 469.3 ppm/°C Five-Transistor Current Reference Generator. IEEE Solid State Circuits Lett. 2018, 1, 122–125. [Google Scholar] [CrossRef]

- Xin, H.; Andraud, M.; Baltus, P.; Cantatore, E.; Harpe, P. A 174 pW–488.3 nW 1 S/s–100 kS/s all-dynamic resistive temperature sensor with speed/resolution/resistance adaptability. IEEE Solid State Circuits Lett. 2018, 1, 70–73. [Google Scholar] [CrossRef]

| [13] | [12] | [11] | [21] | This Work * | |

|---|---|---|---|---|---|

| Technology [nm] | 65 | 180 | 180 | 65 | 130 |

| Area [mm2] | 0.004 | 0.09 | 0.22 | 0.06 | 0.06 |

| Supply Voltage [V] | 0.85–1.05 | 1.2 | 1.2 | 1 | 1 |

| External Clock | NO | NO | NO | YES | NO |

| Temperature Range [°C] | 0–100 | 0–100 | −20–80 | 0–100 | 0 to 80 |

| Resolution [°C] | 0.3 | 0.3 | 0.09 | 0.61 | 0.09 |

| Conversion Time [s] | 22 × 10−6 | 30 × 10−3 | 8 × 10−3 | 10 × 10−6–1 | 3.9 |

| Power [nW] | 154,000 | 71 | 570 | 488.3–0.17 | 156 |

| Calibration | 2-point | 2-point | 2-point | 1-point | 2-point |

| Inaccuracy [°C] | ±0.9 | +1.5/−1.4 | ±0.76 | +1.5/−1.1 | +0.37/−0.32 |

© 2020 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Li, J.; Lin, Y.; Ye, S.; Wu, K.; Ning, N.; Yu, Q. A CMOS-Thyristor Based Temperature Sensor with +0.37 °C/−0.32 °C Inaccuracy. Micromachines 2020, 11, 124. https://doi.org/10.3390/mi11020124

Li J, Lin Y, Ye S, Wu K, Ning N, Yu Q. A CMOS-Thyristor Based Temperature Sensor with +0.37 °C/−0.32 °C Inaccuracy. Micromachines. 2020; 11(2):124. https://doi.org/10.3390/mi11020124

Chicago/Turabian StyleLi, Jing, Yuyu Lin, Siyuan Ye, Kejun Wu, Ning Ning, and Qi Yu. 2020. "A CMOS-Thyristor Based Temperature Sensor with +0.37 °C/−0.32 °C Inaccuracy" Micromachines 11, no. 2: 124. https://doi.org/10.3390/mi11020124