Study on Single Event Effect Simulation in T-Shaped Gate Tunneling Field-Effect Transistors

Abstract

:1. Introduction

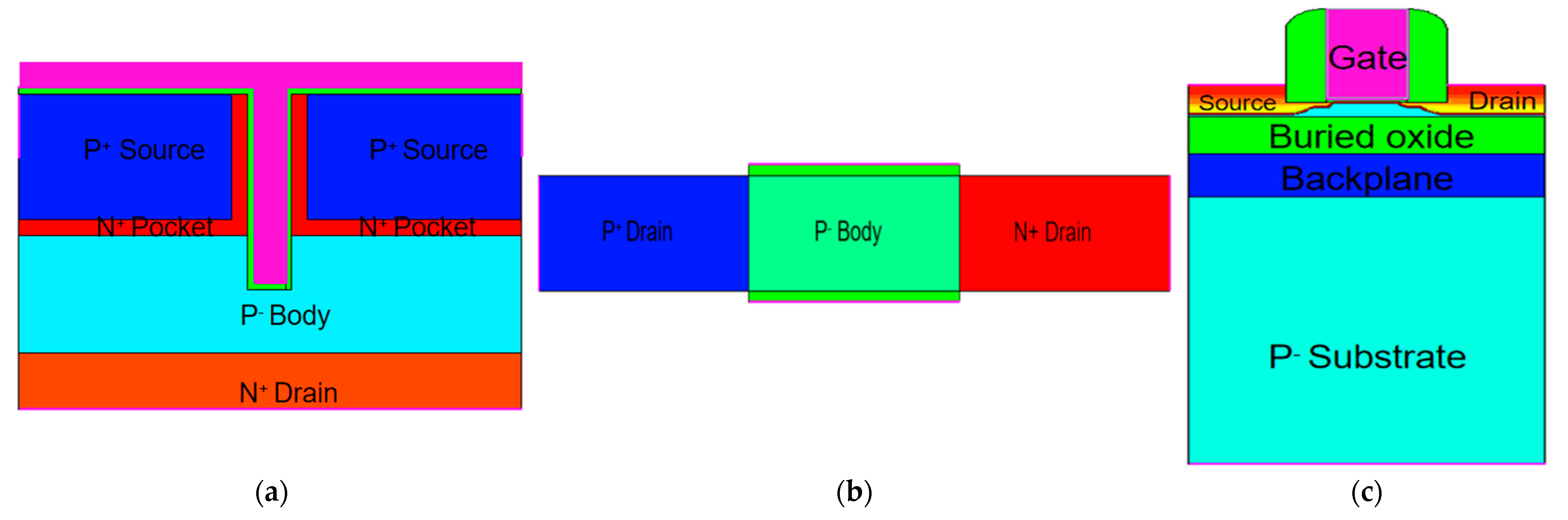

2. Materials and Methods

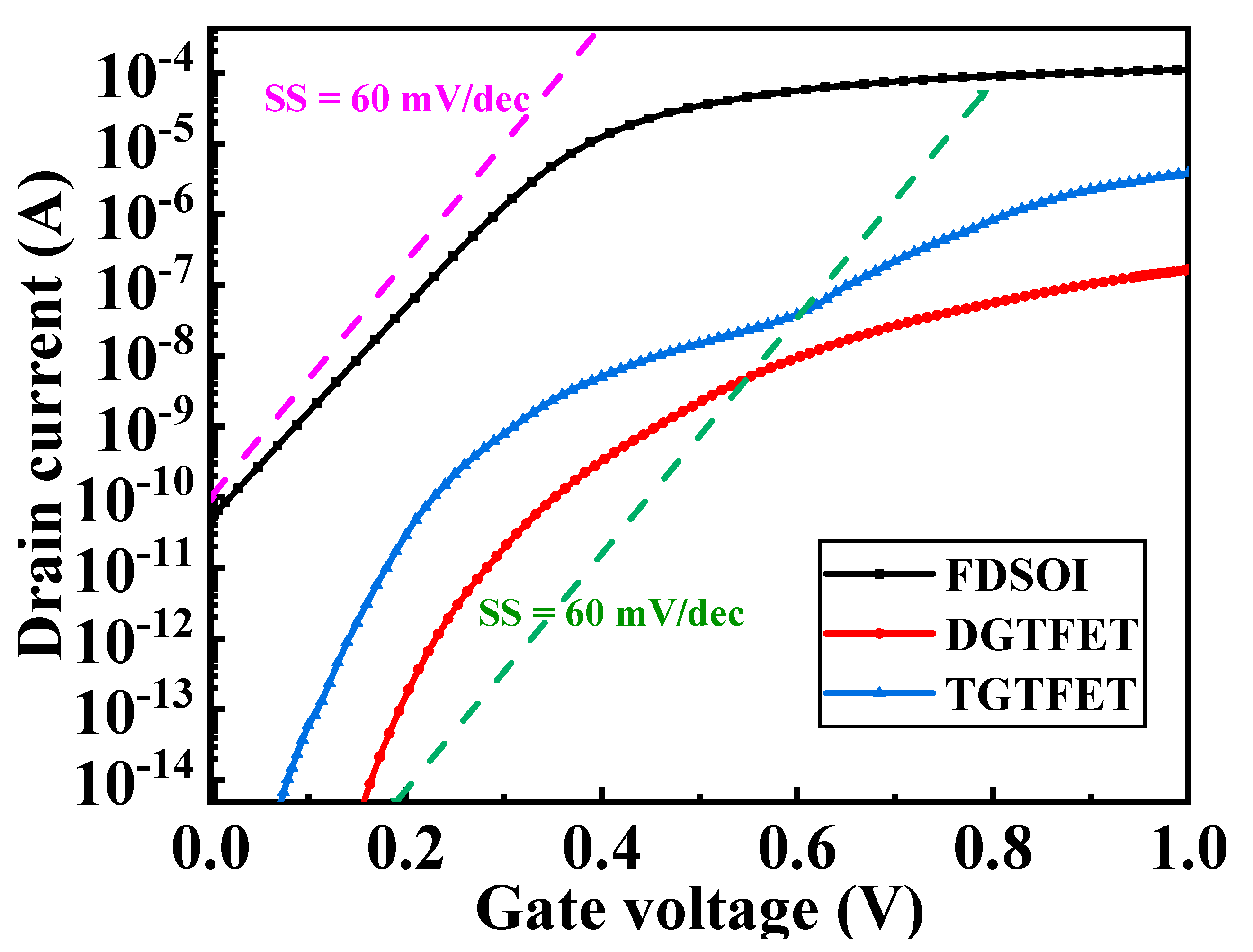

2.1. Simulation Model in TFET

2.2. Simulation Model of SEE

3. Results and Discussion

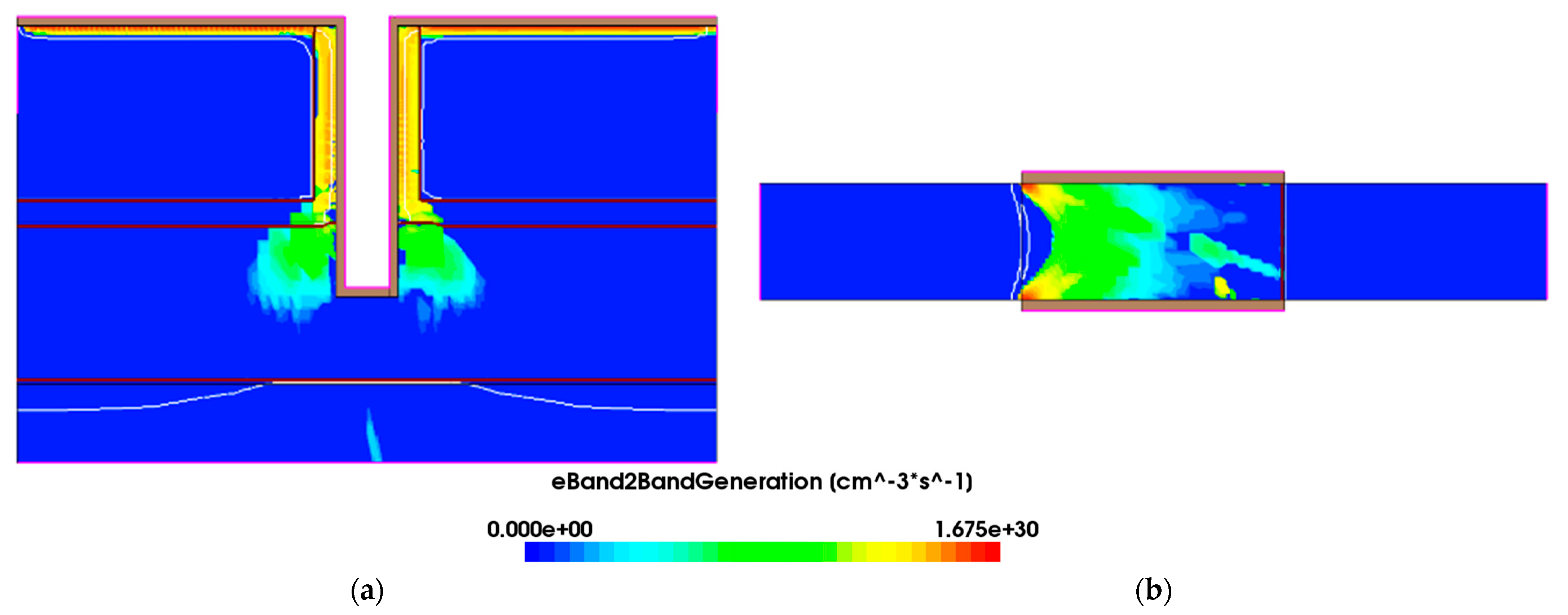

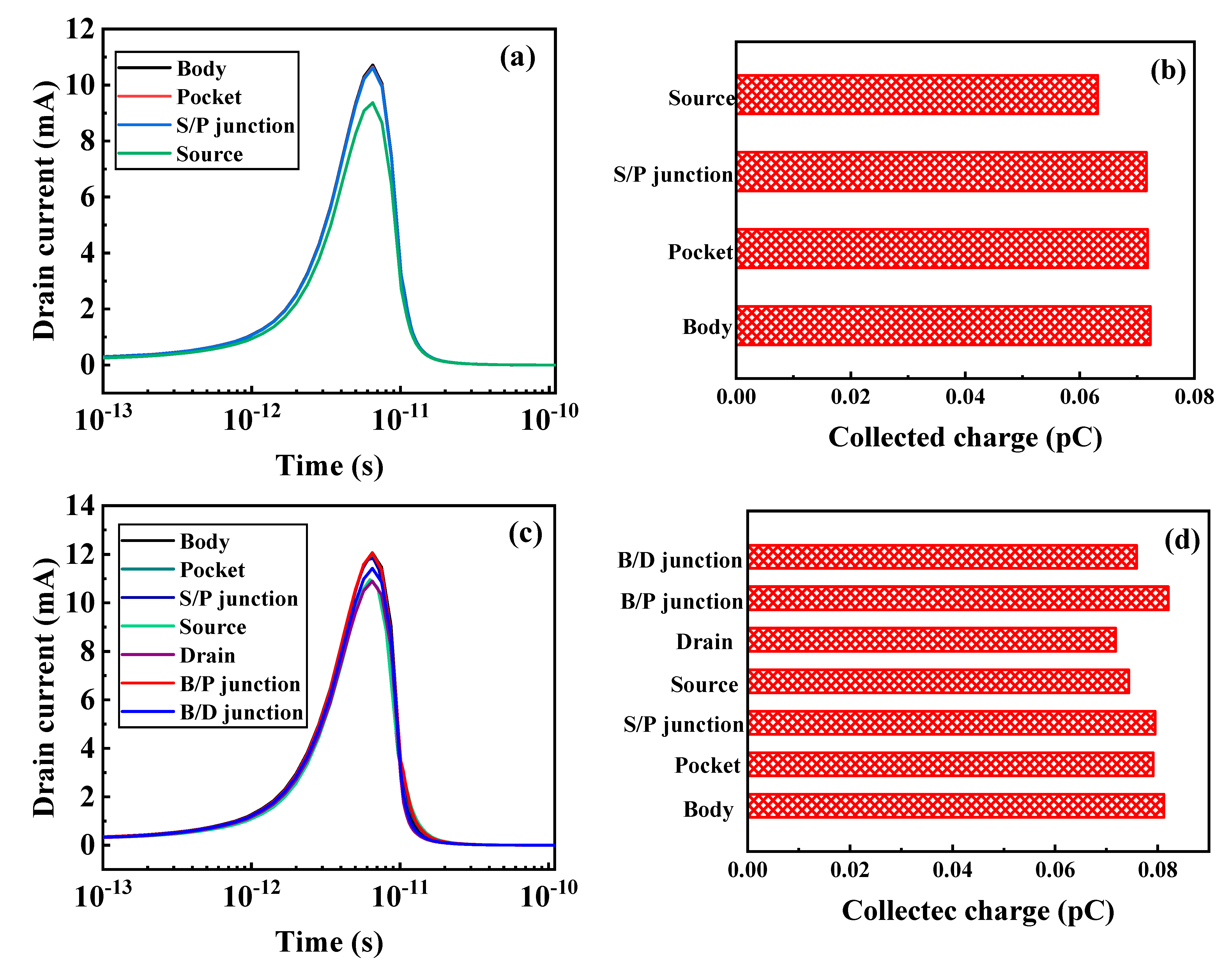

3.1. Heavy Ions Sensitive Region

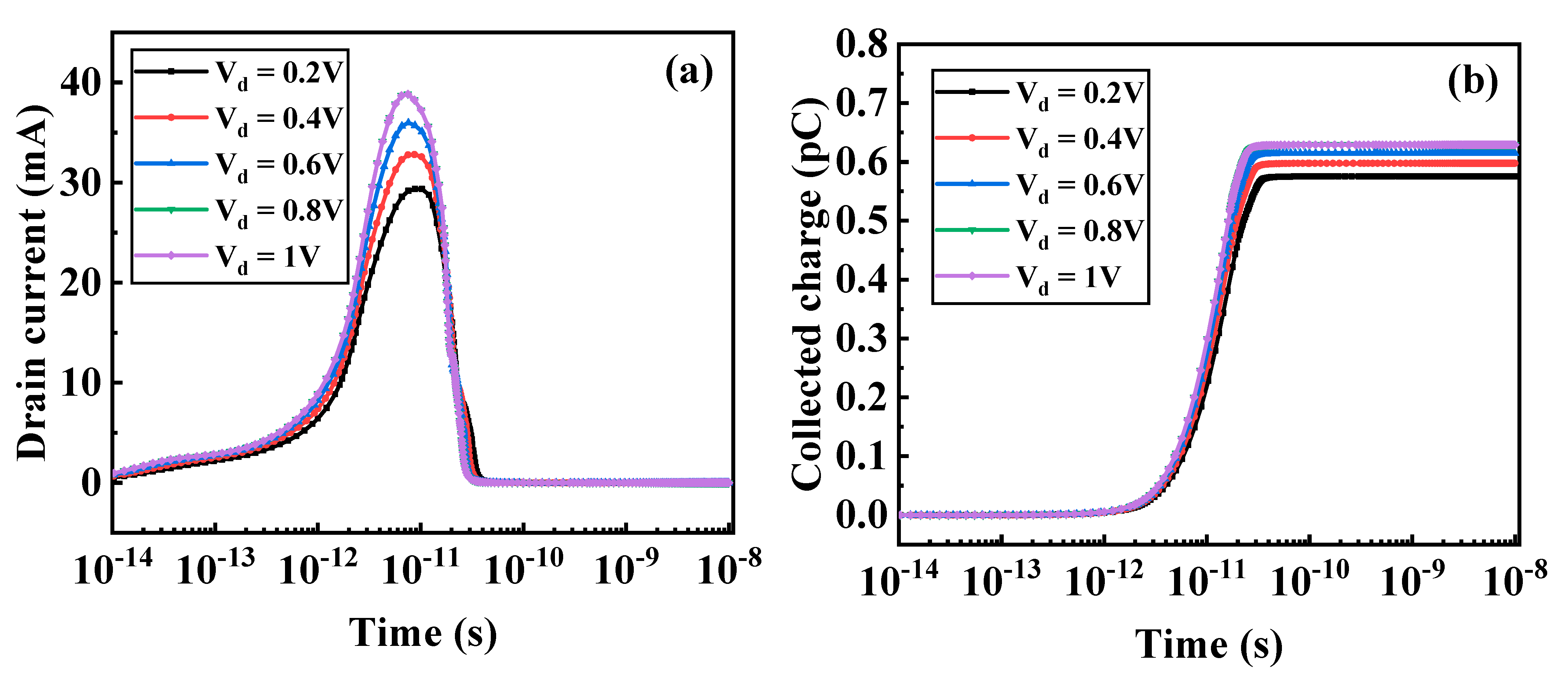

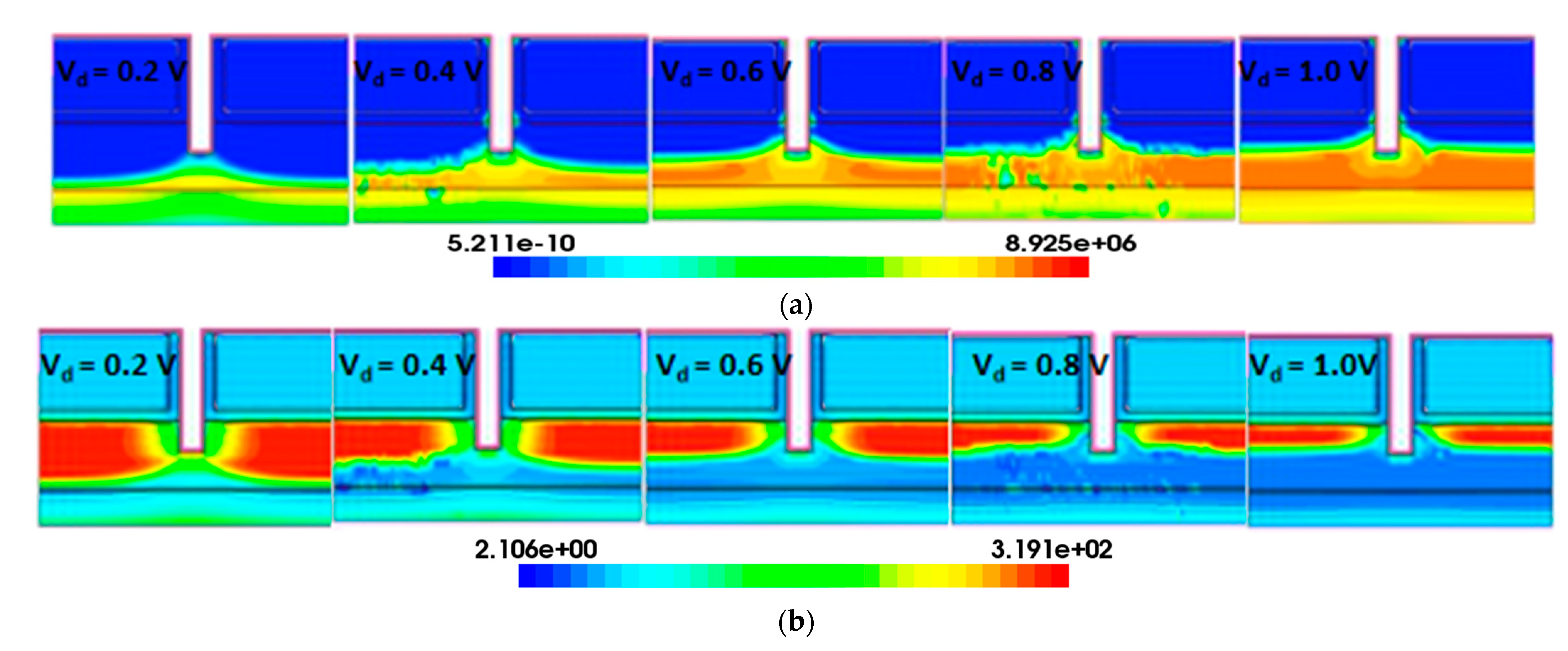

3.2. Impact of Drain Voltage on SEE in TGTFET

3.3. Impact of LET on Single-Event Transient Effects in TGTFET

4. Conclusions

Author Contributions

Funding

Conflicts of Interest

References

- Ionescu, M.; Riel, H. Tunnel field-effect transistors as energy efficient electronic switches. Nature 2011, 11, 329–337. [Google Scholar] [CrossRef] [PubMed]

- Huang, Q.; Huang, R.; Zhan, Z.; Qiu, Y.; Jiang, W.; Wu, C.; Wang, Y. A novel Si tunnel FET with 36 mV/dec subthreshold slope based on junction depleted-modulation through striped gate configuration. In Proceedings of the 2012 International Electron Devices Meeting, San Francisco, CA, USA, 10–13 December 2012; Volume 12, pp. 8.5.1–8.5.4. [Google Scholar]

- Wang, C.; Wu, C.; Wang, J.; Huang, Q.; Huang, R. Analytical current model of tunneling field-effect transistor considering the impacts of both gate and drain voltages on tunneling. Sci. China Inf. Sci. 2014, 58, 1–8. [Google Scholar] [CrossRef]

- Tajalli, A.; Leblebici, Y. Design Trade-offs in Ultra-Low-Power Digital Nanoscale CMOS. IEEE Trans. Circuits Syst. I Regul. Pap. 2011, 58, 2189–2200. [Google Scholar] [CrossRef]

- Jeon, K.; Loh, W.-Y.; Patel, P.; Kang, C.Y.; Oh, J.; Bowonder, A.; Park, C.; Smith, C.; Majhi, P.; Tseng, H.-H.; et al. Si tunnel transistors with a novel silicided source and 46mV/dec swing. In Proceedings of the 2010 Symposium on VLSI Technology, Honolulu, HI, USA, 15–17 June 2010; Volume 6, pp. 121–122. [Google Scholar]

- Avci, U.E.; Young, I.A. Heterojunction TFET scaling and resonant-TFET for steep subthreshold slope at sub-9nm gate-length. In Proceedings of the 2013 IEEE International Electron Devices Meeting, Washington, DC, USA, 9–11 December 2013; Volume 12, pp. 4.3.1–4.3.4. [Google Scholar]

- Kim, S.W.; Kim, J.H.; Liu, T.-J.K.; Choi, W.Y.; Park, B.-G. Demonstration of L-Shaped Tunnel Field-Effect Transistors. IEEE Trans. Electron Devices 2016, 63, 1774–1778. [Google Scholar] [CrossRef]

- Kam, H.; Liu, T.-J.K.; Alon, E. Design Requirements for Steeply Switching Logic Devices. IEEE Trans. Electron Devices 2011, 59, 326–334. [Google Scholar] [CrossRef]

- Chen, S.; Wang, S.; Liu, H.; Li, W.; Wang, Q.; Wang, X. Symmetric U-Shaped Gate Tunnel Field-Effect Transistor. IEEE Trans. Electron Devices 2017, 64, 1343–1349. [Google Scholar] [CrossRef]

- Villalon, A.; Le Carval, G.; Martinie, S.; Le Royer, C.; Jaud, M.-A.; Cristoloveanu, S. Further Insights in TFET Operation. IEEE Trans. Electron Devices 2014, 61, 2893–2898. [Google Scholar] [CrossRef]

- Seabaugh, C.; Zhang, Q. Low-voltage tunnel transistors for beyond CMOS logic. Proc. IEEE 2010, 12, 2095–2110. [Google Scholar] [CrossRef]

- Nagavarapu, V.; Jhaveri, R.; Woo, J.C.S. The Tunnel Source (PNPN) n-MOSFET: A Novel High Performance Transistor. IEEE Trans. Electron Devices 2008, 55, 1013–1019. [Google Scholar] [CrossRef]

- Toh, E.-H.; Wang, G.H.; Samudra, G.; Yeo, Y.-C. Device physics and design of double-gate tunneling field-effect transistor by silicon film thickness optimization. Appl. Phys. Lett. 2007, 90, 263507. [Google Scholar] [CrossRef]

- Kumar, M.J.; Janardhanan, S. Doping-Less Tunnel Field Effect Transistor: Design and Investigation. IEEE Trans. Electron Devices 2013, 60, 3285–3290. [Google Scholar] [CrossRef] [Green Version]

- Wang, W.; Wang, P.F.; Zhang, C.M.; Lin, X.; Liu, X.Y.; Sun, Q.Q.; Zhang, D.W. Design of U-shape channel tunnel FETs with SiGe source regions. IEEE Trans. Electron Devices 2014, 1, 193–197. [Google Scholar] [CrossRef]

- Brocard, S.; Pala, M.G.; Esseni, D. Design options for hetero-junction tunnel FETs with high on current and steep sub-threshold voltage slope. In Proceedings of the 2013 IEEE International Electron Devices Meeting, Washington, DC, USA, 9–11 December 2013; Volume 12, pp. 5.4.1–5.4.4. [Google Scholar]

- Li, W.; Liu, H.; Wang, S.; Chen, S. Reduced Miller Capacitance in U-Shaped Channel Tunneling FET by Introducing Heterogeneous Gate Dielectric. IEEE Electron Device Lett. 2017, 38, 403–406. [Google Scholar] [CrossRef]

- Li, W.; Liu, H.; Wang, S.; Chen, S.; Yang, Z. Design of High Performance Si/SiGe Heterojunction Tunneling FETs with a T-Shaped Gate. Nanoscale Res. Lett. 2017, 12, 1–8. [Google Scholar] [CrossRef] [Green Version]

- Oldham, T.; McLean, F. Total ionizing dose effects in MOS oxides and devices. IEEE Trans. Nucl. Sci. 2003, 50, 483–499. [Google Scholar] [CrossRef] [Green Version]

- Mazer, J.A.; Kang, K.; Buchner, S. Laser simulation of single-event upset in a p-well CMOS counter. IEEE Trans. Nucl. Sci. 1989, 1, 1330–1332. [Google Scholar]

- Xi, K.; Bi, J.; Chu, J.; Xu, G.; Li, B.; Wang, H.; Sandip, M. Total ionization dose effects of N type tunnel field effect transistor (TFET) with ul-tra shallow pocket junction. Appl. Phys. A 2020, 126, 1–8. [Google Scholar] [CrossRef]

- Ferlet-Cavrois, V.; Gasiot, G.; Marcandella, C.; D’hose, C.; Flament, O.; Faynot, O.; de Pontcharra, J.D.; Raynaud, C. Insights on the transient response of fully and partially depleted SOI technologies under heavy-ion and dose-rate irradiations. IEEE Trans. Nucl. Sci. 2002, 6, 2948–2956. [Google Scholar] [CrossRef]

- Manohari, R.G.; Nagarajan, K.K.; Srinivasan, R. Single event transient analyses of conventional planar tunnel FET, planar Tunnel FET with pocket and L shaped tunnel FET. In Proceedings of the 2017 International Conference on Nextgen Electronic Technologies: Silicon to Software (ICNETS2), Chennai, India, 23–25 March 2017; Volume 3, pp. 172–175. [Google Scholar]

- Wang, Q.; Liu, H.; Wang, S.; Chen, S. TCAD Simulation of Single-Event-Transient Effects in L-Shaped Chan-nel Tunneling Field-Effect Transistors. IEEE Trans. Nucl. Sci. 2018, 8, 2250–2259. [Google Scholar] [CrossRef]

- Chen, S.; Liu, H.; Wang, S.; Li, W.; Wang, X.; Zhao, L. Analog/RF Performance of T-Shape Gate Dual-Source Tunnel Field-Effect Transisitor. Nanoscale Res. Lett. 2018, 13, 321. [Google Scholar] [CrossRef] [Green Version]

- Aragão-Rêgo, H.; Soares, D.; Lucena, L.; Da Silva, L.; Lenzi, E.; Fa, K.S. Bose–Einstein and Fermi–Dirac distributions in nonextensive Tsallis statistics: An exact study. Phys. A Stat. Mech. Its Appl. 2003, 317, 199–208. [Google Scholar] [CrossRef]

- Masetti, G.; Severi, M.; Solmi, S. Modeling of carrier mobility against carrier concentration in arsenic-, phosphorus-, and boron-doped silicon. IEEE Trans. Electron Devices 1983, 30, 764–769. [Google Scholar] [CrossRef]

- Lombardi, C.; Manzini, S.; Saporito, A.; Vanzi, M. A Physically Based Mobility Model for Numerical Simulation of Nonplanar Devices. IEEE Trans. Comput. Aided Des. 1988, 11, 1164–1171. [Google Scholar] [CrossRef]

- Leitz, C.W.; Currie, M.T.; Lee, M.L.; Cheng, Z.Y.; Antoniadis, D.A.; Fitzgerald, E.A. Hole mobility enhancements and alloy scattering-limited mobility in tensile strained Si/SiGe surface channel metal-oxide-semiconductor field-effect transistors. J. Appl. Phys. 2002, 7, 3745–3751. [Google Scholar] [CrossRef]

- Caughey, D.M.; Thomas, R.E. Carrier Mobilities in Silicon Empirically Related to Doping and Field. Proc. IEEE 1967, 12, 2192–2193. [Google Scholar] [CrossRef]

- Fossum, J.G.; Mertens, R.P.; Lee, D.S.; Nijs, J.F. Carrier Recombination and Lifetime in Highly Doped Silicon. Solid-State Electron. 1983, 6, 569–576. [Google Scholar] [CrossRef]

- Register, L.F.; Rosenbaum, E.; Yang, K. Analytic model for direct tunneling current in polycrystalline silicon-gate metal–oxide–semiconductor devices. Appl. Phys. Lett. 1999, 74, 457–459. [Google Scholar] [CrossRef]

- Bartra, W.C.; Vladimirescu, A.; Reis, R. Bulk and FDSOI Sub-micron CMOS transistors resilience to single-event transients. In Proceedings of the 2015 IEEE International Conference on Electronics, Circuits, and Systems (ICECS), Cairo, Egypt, 6–9 December 2015; Volume 12, pp. 133–136. [Google Scholar]

- Northcliffe, L.; Schilling, R. Range and stopping-power tables for heavy ions. At. Data Nucl. Data Tables 1970, 7, 233–463. [Google Scholar] [CrossRef]

| Parameter Name | Symbol | Value | Unit |

|---|---|---|---|

| Pocket thickness | tp | 5 | nm |

| Gate oxide thickness | tox | 2 | nm |

| Source height | HS | 40 | nm |

| Drain height | HD | 18 | nm |

| Body doping | NB | 1 × 1017 | cm−3 |

| Pocket doping | NP | 1 × 1019 | cm−3 |

| Source doping | NS | 1 × 1020 | cm−3 |

| Drain doping | ND | 1 × 1018 | cm−3 |

| Parameters | Value |

|---|---|

| depth | 0.5 um |

| time | 5 × 10−12 s |

| direction | (0,1,0) |

| location | (0,0,0) |

| radius | 0.1 um |

| LET | 2~10 pC/μm |

| Vd | 0.2~1 V |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2021 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Chong, C.; Liu, H.; Wang, S.; Chen, S.; Xie, H. Study on Single Event Effect Simulation in T-Shaped Gate Tunneling Field-Effect Transistors. Micromachines 2021, 12, 609. https://doi.org/10.3390/mi12060609

Chong C, Liu H, Wang S, Chen S, Xie H. Study on Single Event Effect Simulation in T-Shaped Gate Tunneling Field-Effect Transistors. Micromachines. 2021; 12(6):609. https://doi.org/10.3390/mi12060609

Chicago/Turabian StyleChong, Chen, Hongxia Liu, Shulong Wang, Shupeng Chen, and Haiwu Xie. 2021. "Study on Single Event Effect Simulation in T-Shaped Gate Tunneling Field-Effect Transistors" Micromachines 12, no. 6: 609. https://doi.org/10.3390/mi12060609