A Single-Event-Hardened Scheme of Phase-Locked Loop Microsystems for Aerospace Applications

Abstract

:1. Introduction

2. Responses of SET in CP

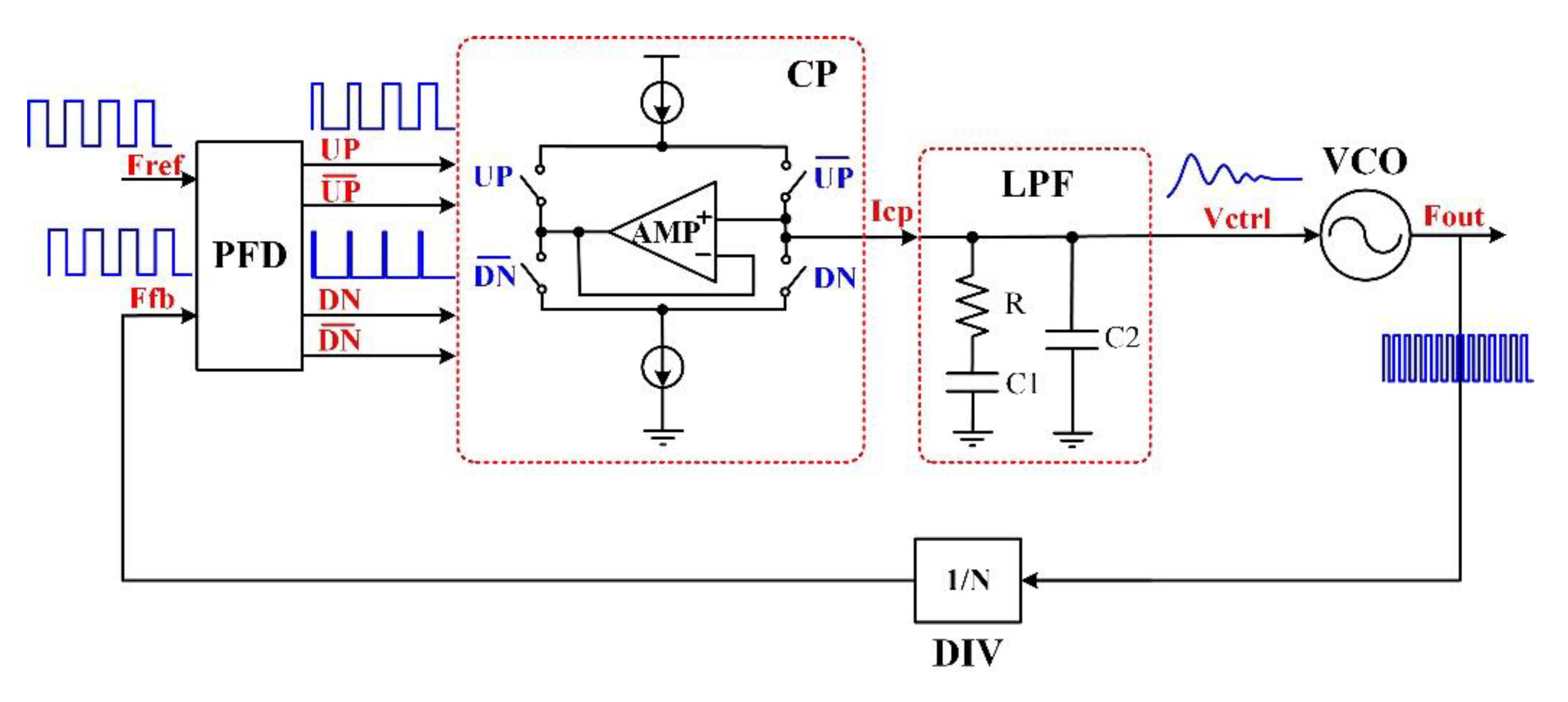

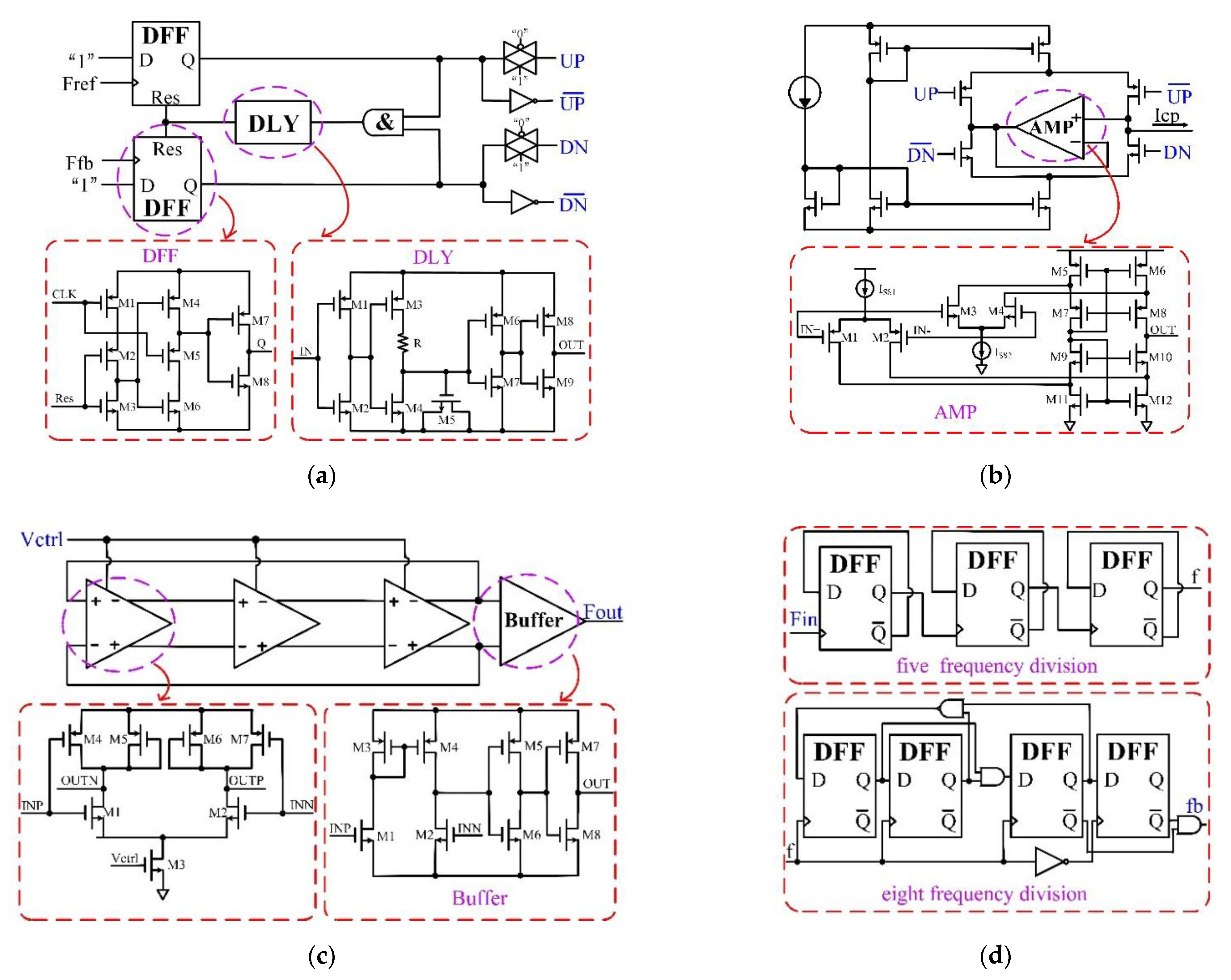

2.1. Topology of the CPPLL

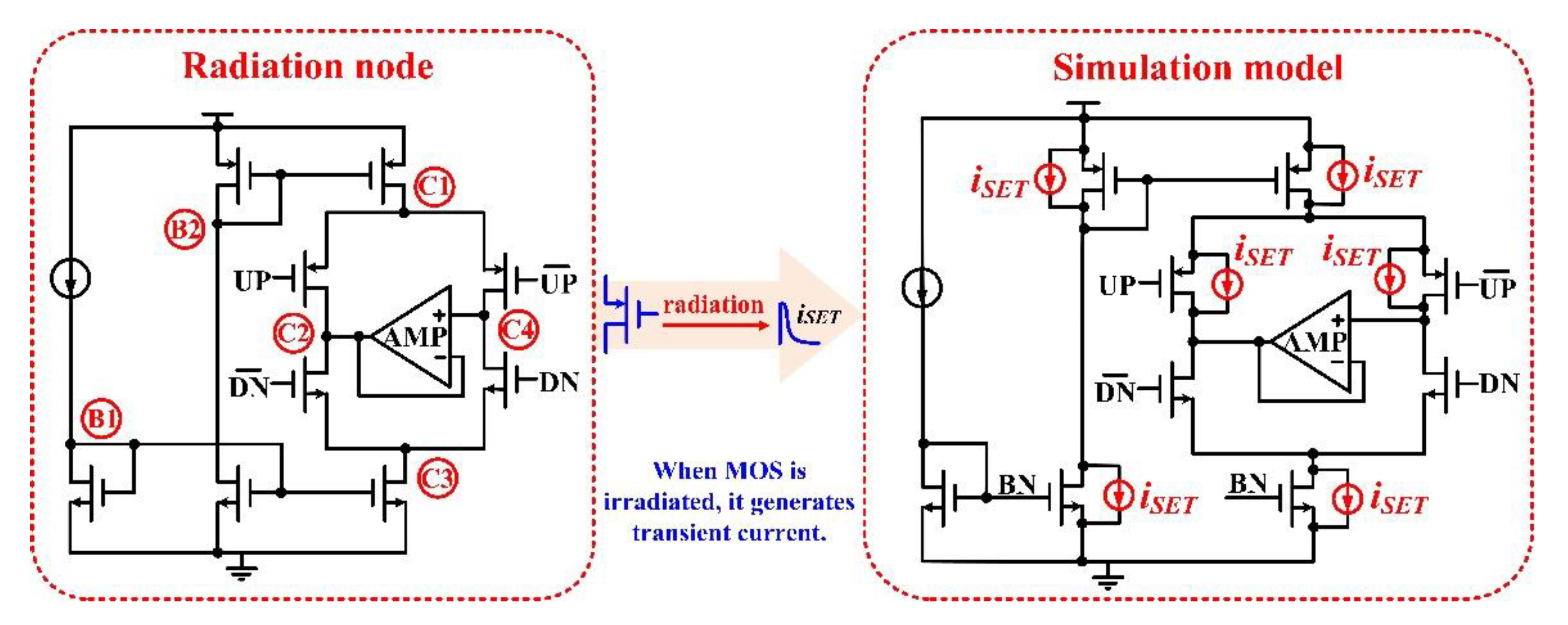

2.2. Analysis of SET’s Impact on CP

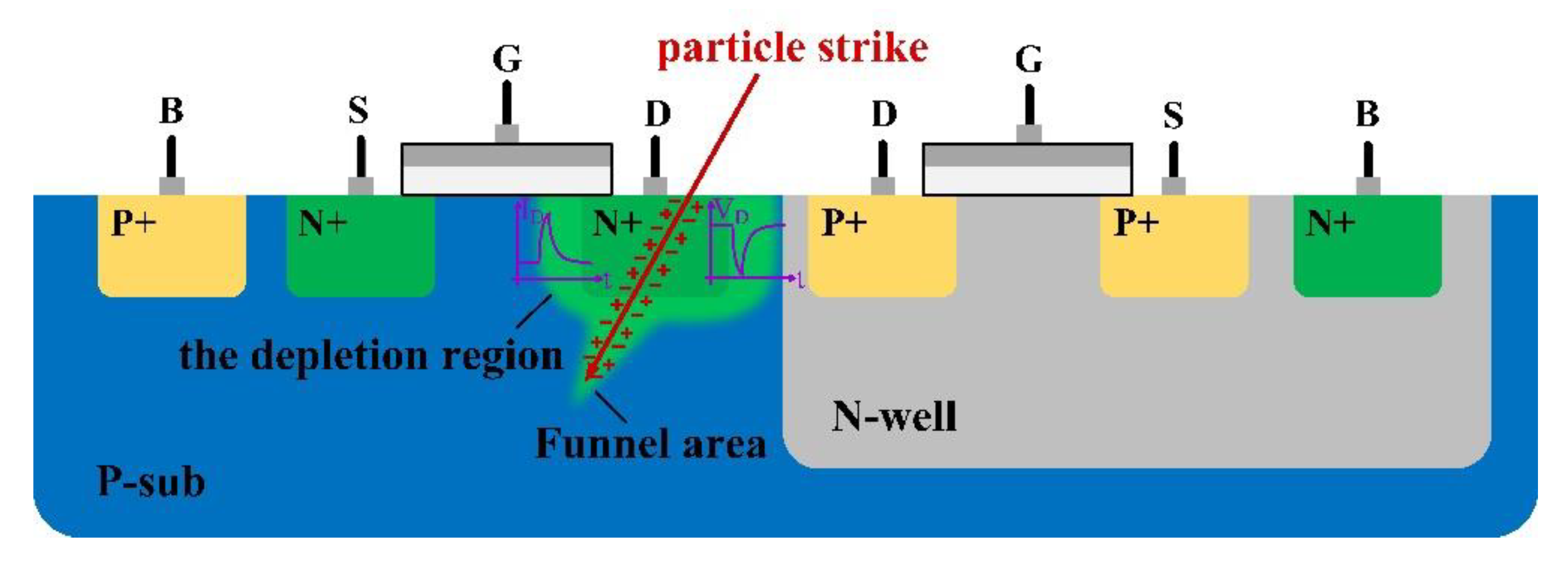

2.2.1. SET Current Pulse Model

2.2.2. SET Response of Different Bombardment Nodes

2.2.3. SET Response of Different Bombardment Energy

3. The Proposed SET Hardened CP Circuit

4. Simulation and Result Analysis

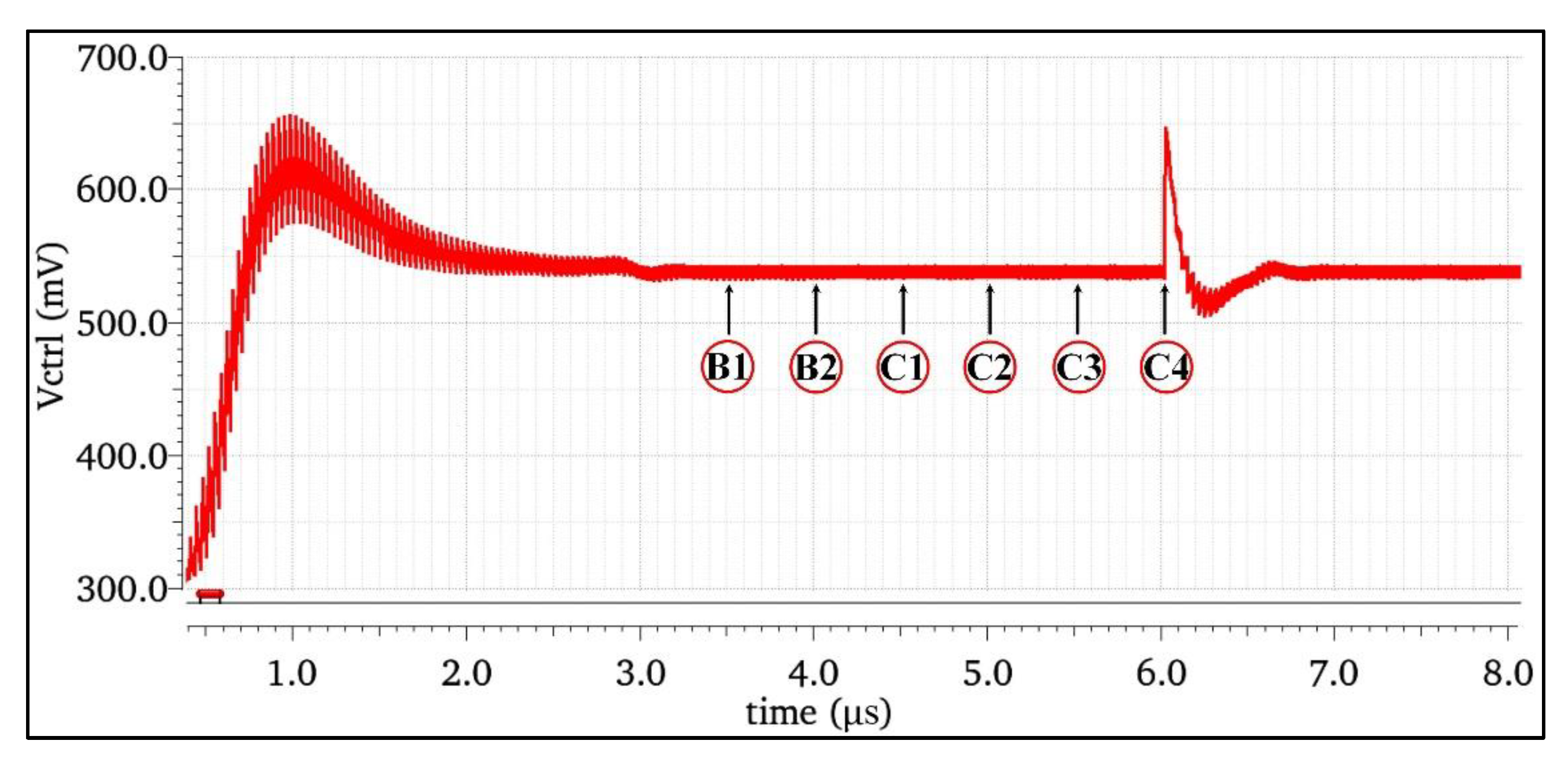

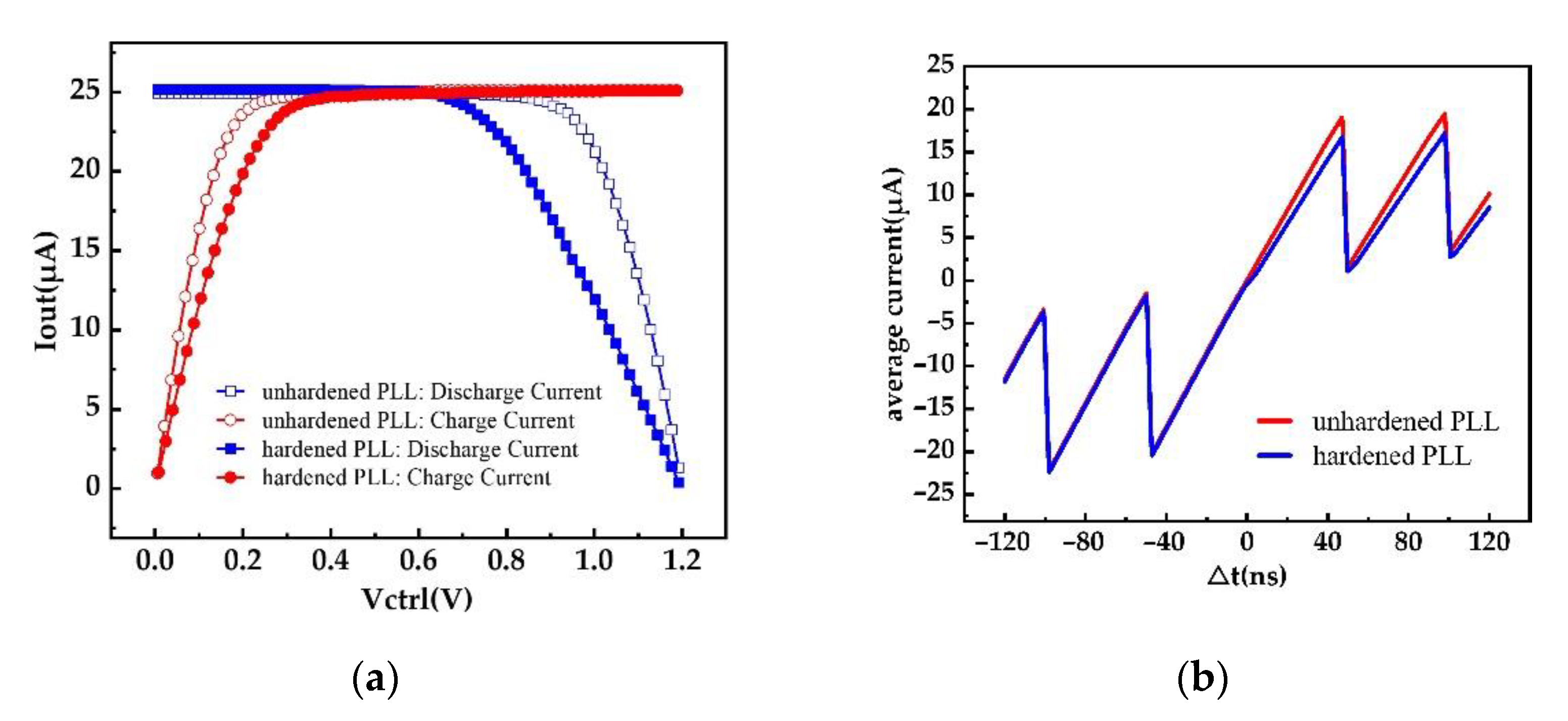

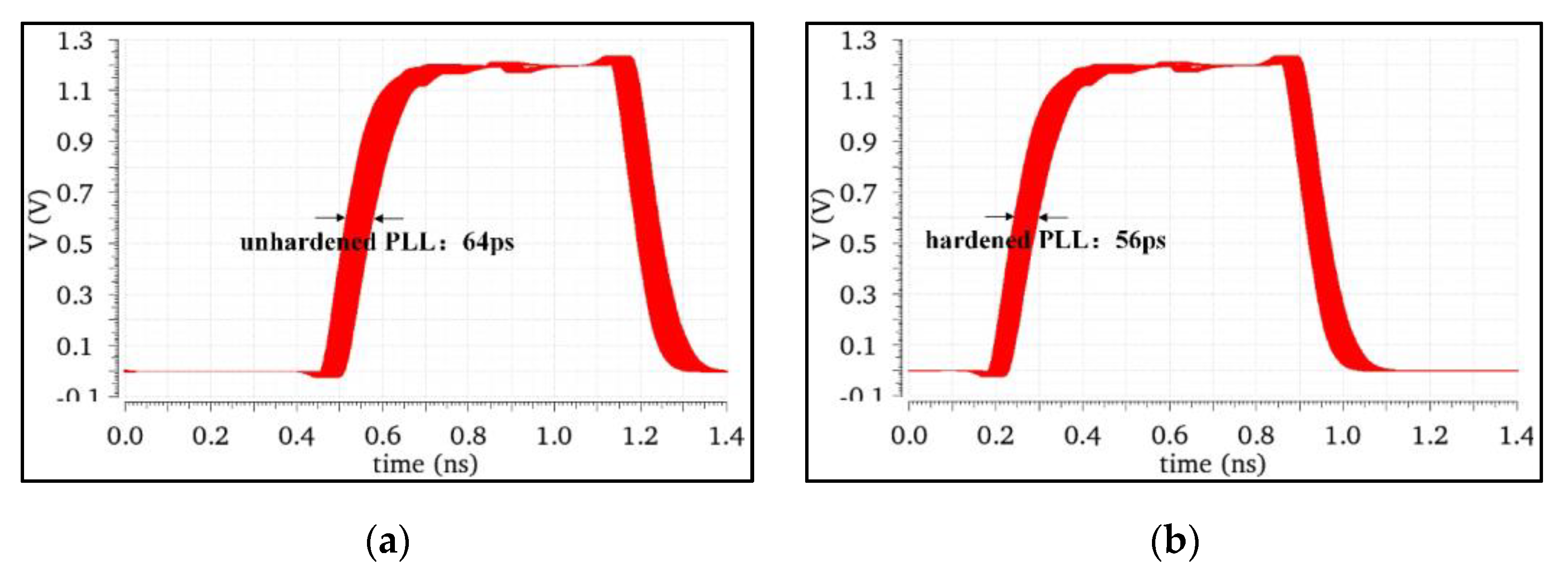

4.1. Verification of Basic Performance

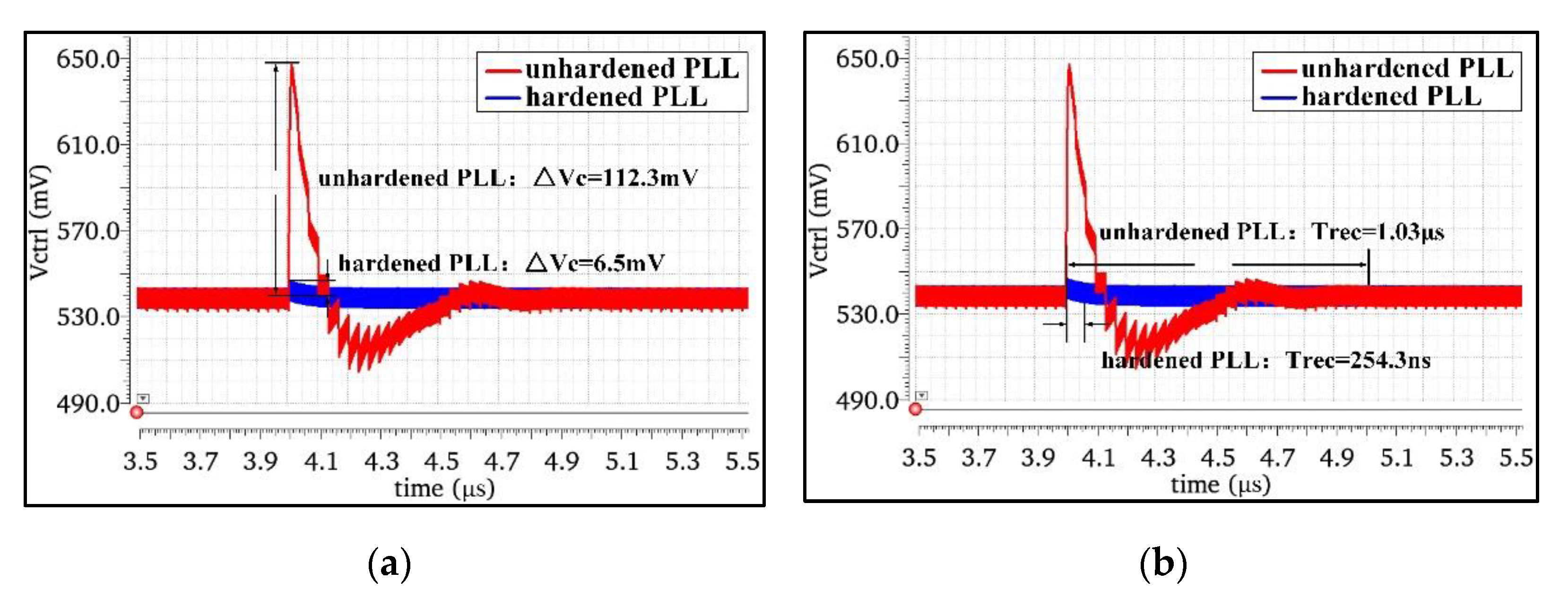

4.2. Verification of Hardened Effect

5. Conclusions

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

References

- von Kaenel, V.R. A high-speed, low-power clock generator for a microprocessor application. IEEE J. Solid-State Circuits 1998, 33, 1634–1639. [Google Scholar] [CrossRef]

- Chen, Z.; Ding, D.; Dong, Y.; Shan, Y.; Zeng, Y.; Gao, J. Design of a High-Performance Low-Cost Radiation-Hardened Phase-Locked Loop for Space Application. IEEE Trans. Aerosp. Electron. Syst. 2020, 56, 3588–3598. [Google Scholar] [CrossRef]

- Grubin, H.L.; Kreskovsky, J.P.; Weinberg, B.C. Numerical Studies of Charge Collection and Funneling in Silicon Device. IEEE Trans. Nucl. Sci. 1984, 31, 1161–1166. [Google Scholar] [CrossRef]

- Van Dam, C.; Hauser, M. Ring oscillator reliability model to hardware correlation in 45nm SOI. In Proceedings of the 2013 IEEE International Reliability Physics Symposium (IRPS), Monterey, CA, USA, 14–18 April 2013; pp. CM.1.1–CM.1.5. [Google Scholar]

- Alaoui, Z.; Alaoui, I.; Ajib, E.W.; Nabki, F.; Gagnon, F. A 0.1–9-GHz Frequency Synthesizer for Avionic SDR Applications in 0.13-μm CMOS Technology. IEEE Trans. Very Large Scale Integr. (VLSI) Syst. 2021, 29, 2119–2129. [Google Scholar] [CrossRef]

- Rossetto, A.C., Jr.; Wirth, G.I.; Dallasen, R.V. Performance analysis of a clock generator PLL under TID effects. In Proceedings of the 2014 15th Latin American Test Workshop—LATW, Fortaleza, Brazil, 12–15 March 2014; pp. 1–5. [Google Scholar]

- Boulghassoul, Y.; Massengill, L.W.; Sternberg, A.L.; Bhuva, B.L.; Holman, W.T. Towards SET Mitigation in RF Digital PLLs: From Error Characterization to Radiation Hardening Considerations. IEEE Trans. Nucl. Sci. 2006, 53, 2047–2053. [Google Scholar] [CrossRef]

- Chen, Z.; Lin, M.; Zheng, Y.; Wei, Z.; Huang, S.; Zou, S. Single-Event Transient Characterization of a Radiation-Tolerant Charge-Pump Phase-Locked Loop Fabricated in 130 nm PD-SOI Technology. IEEE Trans. Nucl. Sci. 2016, 63, 2402–2408. [Google Scholar] [CrossRef]

- Chen, Z.; Lin, M.; Zheng, Y.; Wei, Z.; Huang, S.; Zou, S. Analysis of Single-Event Effects in a Radiation-Hardened Low-Jitter PLL Under Heavy Ion and Pulsed Laser Irradiation. IEEE Trans. Nucl. Sci. 2017, 64, 106–112. [Google Scholar] [CrossRef]

- Loveless, T.D.; Massengill, L.W.; Bhuva, B.L.; Holman, W.T. A Single-Event-Hardened Phase-Locked Loop Fabricated in 130 nm CMOS. IEEE Trans. Nucl. Sci. 2007, 54, 2012–2020. [Google Scholar] [CrossRef]

- Loveless, T.D.; Olson, B.D.; Bhuva, B.L.; Holman, W.T.; Hafer, C.C. Analysis of Single-Event Transients in Integer-N Frequency Dividers and Hardness Assurance Implications for Phase-Locked Loops. IEEE Trans. Nucl. Sci. 2009, 56, 3489–3498. [Google Scholar] [CrossRef]

- Richards, E.W.; Loveless, T.D.; Kauppila, J.S.; Haeffner, T.D.; Holman, W.T.; Massengill, L.W. Radiation Hardened by Design Subsampling Phase-Locked Loop Techniques in PD-SOI. IEEE Trans. Nucl. Sci. 2020, 67, 1144–1151. [Google Scholar] [CrossRef]

- Liu, H.; Zhang, X.; Li, P.; Xu, X. A Hardened Phase-Locked Loop Using Novel Charge Pump. In Proceedings of the 2015 8th International Symposium on Computational Intelligence and Design (ISCID), Hangzhou, China, 12–13 December 2015; pp. 566–568. [Google Scholar]

- Liang, B.; Xu, X.; Yuan, H.; Chen, J. A system-level method for hardening phase-locked loop to single-event effects. Mater. Res. Express 2022, 9, 2053–2061. [Google Scholar] [CrossRef]

- Loveless, T.D.; Massengill, L.W.; Bhuva, B.L. A Hardened-by-Design Technique for RF Digital Phase Lock Loops. IEEE Trans. Nucl. Sci. 2006, 53, 3432–3438. [Google Scholar] [CrossRef]

- Zhao, Z.; Zhang, M.; Chen, S.; Chen, J.; Li, J. A radiation-hardened-by-design technique for improving single-event transient tolerance of charge pumps in PLLs. J. Semicond. 2009, 30, 125009. [Google Scholar]

- Han, B.; Guo, Z.; Wu, L.; Liu, Y. A single-event-hardened phase-locked loop using the radiation-hardened-by-design technique. J. Semicond. 2012, 33, 105007. [Google Scholar] [CrossRef]

- Adesina, N.O.; Srivastava, A.; Khan, M.A.U.; Xu, J. Phase Noise and Jitter Measurements in SEU-Hardened CMOS Phase Locked Loop Design. In Proceedings of the 2021 IEEE International IOT, Electronics and Mechatronics Conference (IEMTRONICS), Toronto, ON, Canada, 21–24 April 2021; pp. 1–6. [Google Scholar]

- Messenger, G.C. Collection of charge on junction nodes from ion tracks. IEEE Trans. Nucl. Sci. 1982, 29, 2024–2031. [Google Scholar] [CrossRef]

- Casey, M.C.; Bhuva, B.L.; Black, J.D. HBD using cascode-voltage switch logic gates for SET tolerant digital designs. IEEE Trans. Nucl. Sci. 2005, 52, 2510–2515. [Google Scholar] [CrossRef]

- You, Y.; Chen, J.; Feng, Y. SET detection and compensation and its application in PLL design. J. Instrum. 2015, 10, 22–26. [Google Scholar] [CrossRef]

| Performance Parameter | NHPLL | RHPLL | |

|---|---|---|---|

| Supply voltage | 1.2 V | 1.2 V | |

| Output frequency range | 0.6 GHz~1.6 GHz | 0.6 GHz~1.6 GHz | |

| CP working current | 25 μA | 25 μA | |

| CP current mismatch | 0.65% | 0.67% | |

| Control voltage ripple | 8 mV | 8 mV | |

| Lock [email protected] GHz | 2.3 μs | 2.5 μs | |

| Power consumption | 8.56 mW | 9.12 mW | |

| Area | 265 μm × 199 μm (1×) | 275 μm × 207 μm (1.08×) | |

| SET response | Vctrl fluctuation peak | 112.3 mV | 6.5 mV |

| Recovery time | 1031 ns | 254.3 ns | |

| Number of error pulses | 7 | 2 | |

| Maximum phase error | 86.58° | 7.93° | |

| Parameter | Reference [14] | Reference [21] | This Work | ||||||

|---|---|---|---|---|---|---|---|---|---|

| Technology node | 130 nm CMOS | 130 nm CMOS | 130 nm CMOS | ||||||

| Frequency | 700 MHz | 850 MHz | 800 MHz | ||||||

| Deposited charge or LET | 200 fC(≈20 MeVcm2/mg) | 500 fC(≈48 MeVcm2/mg) | 500 fC(≈48 MeVcm2/mg) | ||||||

| Loop parameters | Redesign | Redesign | No change | ||||||

| Hardened or not | unhardened | hardened | improvement | unhardened | hardened | improvement | unhardened | hardened | improvement |

| Voltage perturbation | 640 | 42 | 93% | 85 | 13 | 84.7% | 112.3 | 6.5 | 94.2% |

| Recovery time | 400 | 98 | 75.5% | 340 | 114 | 66.5% | 1031 | 254.3 | 75.3% |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2022 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Xiang, Q.; Liu, H.; Zhou, Y. A Single-Event-Hardened Scheme of Phase-Locked Loop Microsystems for Aerospace Applications. Micromachines 2022, 13, 2102. https://doi.org/10.3390/mi13122102

Xiang Q, Liu H, Zhou Y. A Single-Event-Hardened Scheme of Phase-Locked Loop Microsystems for Aerospace Applications. Micromachines. 2022; 13(12):2102. https://doi.org/10.3390/mi13122102

Chicago/Turabian StyleXiang, Qi, Hongxia Liu, and Yulun Zhou. 2022. "A Single-Event-Hardened Scheme of Phase-Locked Loop Microsystems for Aerospace Applications" Micromachines 13, no. 12: 2102. https://doi.org/10.3390/mi13122102