CMOS MEMS Fabrication Technologies and Devices

Abstract

:1. Introduction

2. Classification of CMOS MEMS Technologies

3. Pre-CMOS MEMS

4. Inter-CMOS MEMS

5. Post-CMOS MEMS

5.1. Additive MEMS Structures on CMOS Substrate

| Authors and References | Institute | Structural Material | Sacrificial Material | Interconnect Material | Year |

|---|---|---|---|---|---|

| Hornbeck [34] | Texas Instruments | Al | Photoresist | Al | 1989 (invented in 1987) |

| Yun et al. [31] | UC-Berkeley | Polysilicon | SiO2 | W/TiN | 1992 |

| Franke et al. [35] | UC-Berkeley | Poly-SiGe | Ge or SiO2 | Al | 1999 |

| Huang et al. [22] | UC-Berkeley, University of Michigan | Nickel | SiO2 | TiN | 2008 |

| Wojciechowski et al. [25] | Sandia National Laboratory | AlN | Si | W/Ti/TiN | 2009 |

| Uranga et al. [26] | Autonomous University of Barcelona | Bimetallic Nitride | Polymer | W | 2015 |

| Sedky et al. [36] | IMEC | Poly-SiGe | Ge | Al | 1998 |

| Yamane et al. [32] | Tokyo Institute of Technology | Gold | Polyimide | Al | 2013 |

| Li et al. [33] | Shanghai Institute of Microsystems | Copper | Photoresist | Al | 2008 |

| Severi et al. [29] | IMEC, Intel | Poly-SiGe | SiO2 | Doped SiGe | 2010 |

5.2. Subtractive Post-CMOS MEMS

5.2.1. Subtractive CMOS MEMS by Wet Etching

| Authors and References | Institutions | Device | Structural Materials | Etching Method | Year |

|---|---|---|---|---|---|

| Wise et al. [47] | University of Michigan | Pressure sensor | Silicon diaphragm | Backside ethylene diamine-pyrocatechol (EDP) etching | 1979 |

| Wise et al. [39] | University of Michigan | Neuron probe array | Nitride/SiO2, poly and Si substrate | EDP etching, p++ etching stop | 1985 |

| Yoon and Wise [48] | University of Michigan | Mass flow sensor | CMOS nitride/SiO2, Au/Cr | Backside, SiO2 etching stop | 1990 |

| Baltes et al. [4] | ETH Zurich | Thermal capacitor | Metal/SiO2, poly | Front side etching | 1996 |

| Haberli et al. [49] | ETH Zurich | Pressure sensor | Metal/SiO2, poly | Front side etching of aluminum as sacrificial layer | 1996 |

| Schneider et al. [50] | ETH Zurich | Thermal sensor | Metal/SiO2, poly, suspended Si | PN junction electrochemical etch stop | 1997 |

| Akiyama et al. [51] | University of Neuchatel, ETH Zurich | Atomic force microscope (AFM) probe | CMOS Nitride/SiO2, Si | N well electrochemical etch stop | 2000 |

| Schaufelbuhl et al. [52] | ETH Zurich | Infrared imager | Nitride/SiO2, Al, gate poly | Backside KOH | 2001 |

| Verd et al. [41] | Autonomous University of Barcelona | Integrated Resonator | Al layer | Front side SiO2 etching | 2006 |

| Chen et al. [40] | National Tsing Hua University | Integrated resonator | Al/SiO2/Vias | Front side SiO2 etching | 2011 |

| Narducci et al. [42] | IME, Singapore | Absolute pressure sensor | Al/SiO2/Vias | Front side Metal and via etching | 2013 |

| Li et al. [43] | National Tsing Hua University | Integrated Resonator | Al/SiO2/Vias | Front side Metal and via etching | 2015 |

5.2.2. Subtractive Post-CMOS MEMS by Dry Etching

Thin-Film Post-CMOS MEMS Dry Processes

Bulk CMOS-MEMS Dry Process

An Improved Bulk CMOS MEMS Process

5.2.3. Combined Wet/Dry Processes

5.3. Silicon-on-Insulators (SOI) CMOS MEMS Technologies and Devices

6. Summary and Future Trends for System-On-Chip (SOC)

Acknowledgments

Conflicts of Interest

References

- EETimes. MEMS Market to Top $22 Billion by 2018. Available online: http://www.eetimes.com (accessed on 20 January 2016).

- Fedder, G.K.; Howe, R.T.; Tsu-Jae King, L.; Quevy, E.P. Technologies for cofabricating MEMS and electronics. Proc. IEEE 2008, 96, 306–322. [Google Scholar] [CrossRef]

- Hornbeck, L.J. The DMD projection display chip: A MEMS-based technology. MRS Bull. 2001, 26, 325–327. [Google Scholar] [CrossRef]

- Baltes, H.; Paul, O.; Korvink, J.G.; Schneider, M.; Buhler, J.; Schneeberger, N.; Jaeggi, D.; Malcovati, P.; Hornung, M.; Hiberli, A.; et al. IC MEMS microtransducers. In Proceedings of the IEEE International Electron Devices Meeting, San Francisco, CA, USA, 8–11 December 1996; pp. 521–524.

- Brand, O. Microsensor integration into systems-on-chip. Proc. IEEE 2006, 94, 1160–1176. [Google Scholar] [CrossRef]

- Zahorian, J.; Hochman, M.; Xu, T.; Satir, S.; Gurun, G.; Karaman, M.; Degertekin, F.L. Monolithic CMUT-on-CMOS integration for intravascular ultrasound applications. IEEE Trans. Ultrason. Ferroelectr. Freq. Control 2011, 58, 2659–2667. [Google Scholar] [CrossRef] [PubMed]

- Muller, R.; Hanh-Phuc, L.; Wen, L.; Ledochowitsch, P.; Gambini, S.; Bjorninen, T.; Koralek, A.; Carmena, J.M.; Maharbiz, M.M.; Alon, E.; et al. A minimally invasive 64-channel wireless μECOG implant. IEEE J. Solid State Circuits 2015, 50, 344–359. [Google Scholar] [CrossRef]

- Frey, A.; Schienle, M.; Seidel, H. CMOS based sensors for biochemical analysis. In Proceedings of the International Conference on Solid-State Sensors, Actuators and Microsystems (Transducers 2009), Denver, CO, USA, 21–25 June 2009; pp. 1670–1673.

- Christen, J.B.; Andreou, A.G. Design, fabrication, and testing of a hybrid CMOS/PDMS microsystem for cell culture and incubation. IEEE Trans. Biomed. Circuits Syst. 2007, 1, 3–18. [Google Scholar] [CrossRef] [PubMed]

- Li, Z.; Xu, J.; Lu, W.; Xi, J. Merging SOC and LOC together. In Proceedings of the International Conference on Solid-State and Integrated-Circuit Technology, Beijing, China, 20–23 October 2008; pp. 2553–2556.

- Baltes, H.; Brand, O.; Fedder, G.; Hierold, C.; Korvink, J.G.; Tabata, O. CMOS-MEMS: Advanced Micro and Nanosystems, 1st ed.; Wiley-VCH: Hoboken, NJ, USA, 2005. [Google Scholar]

- Smith, J.H.; Montague, S.; Sniegowski, J.J.; Murray, J.R.; McWhorter, P.J. Embedded micromechanical devices for the monolithic integration of MEMS with CMOS. In Proceedings of the International Electron Devices Meeting, Washington, DC, USA, 10–13 December 1995; pp. 609–612.

- Lemkin, M.; Boser, B.E. A three-axis micromachined accelerometer with a CMOS position-sense interface and digital offset-trim electronics. IEEE J. Solid State Circuits 1999, 34, 456–468. [Google Scholar] [CrossRef]

- Kuehnel, W.; Sherman, S. A surface micromachined silicon accelerometer with on-chip detection circuitry. Sens. Actuators A Phys. 1994, 45, 7–16. [Google Scholar] [CrossRef]

- Analog Devices, Inc. Available online: http://www.analog.com (accessed on 20 January 2016).

- Chau, K.; Sulouff, R.E., Jr. Technology for the high-volume manufacturing of integrated surface-micromachined accelerometer products. Microelectron. J. 1998, 29, 579–586. [Google Scholar] [CrossRef]

- Davis, B.S.; Denison, T.; Jinbo, K. A monolithic high-g SOI-MEMS accelerometer for measuring projectile launch and flight accelerations. In Proceedings of the IEEE Sensors, Vienna, Austria, 24–27 October 2004; pp. 296–299.

- Hierold, C. Intelligent CMOS sensors. In Proceedings of the 13th International Conference on Micro Electro Mechanical Systems, Miyazaki, Japan, 23–27 January 2000; pp. 1–6.

- Infinion. Sensor Solutions for Automotive, Industrial and Consumer Applications. Available online: http://www.infinion.com/sensors (accessed on 20 January 2016).

- Borky, J.; Wise, K. Integrated signal conditioning for diaphragm pressure sensors. In Proceedings of the IEEE International Solid-State Circuits Conference, Philadelphia, PA, USA, 14–16 February 1979.

- Uranga, A.; Verd, J.; Barniol, N. CMOS-MEMS resonators: From devices to applications. Microelectron. Eng. 2015, 132, 58–73. [Google Scholar] [CrossRef]

- Huang, W.; Ren, Z.; Lin, Y.; Chen, H.; Lahann, J.; Nguyen, C.T.C. Fully monolithic CMOS nickel micromechanical resonator oscillator. In Proceedings of the IEEE International Conference on Micro Electro Mechanical Systems, Tucson, AZ, USA, 13–17 January 2008; pp. 10–13.

- Olsson, R.H.; Fleming, J.G.; Wojciechowski, K.E.; Baker, M.S.; Tuck, M.R. Post-CMOS compatible aluminum nitride MEMS filters and resonant sensors. In Proceedings of the IEEE International Frequency Control Symposium 2007 Joint with the 21st European Frequency and Time Forum, Geneva, Switzerland, 29 May 2007–1 June 2007; pp. 412–419.

- Kim, B.; Nguyen, J.; Wojciechowski, K.E.; Olsson, R.H. Oven-based thermally tunable aluminum nitride microresonators. J. Microelectromech. Syst. 2013, 22, 265–275. [Google Scholar] [CrossRef]

- Wojciechowski, K.E.; Olsson, R.H.; Tuck, M.R.; Roherty-Osmun, E.; Hill, T.A. Single-chip precision oscillators based on multi-frequency, high-q aluminum nitride MEMS resonators. In Proceedings of the International Conference on Solid-State Sensors, Actuators and Microsystems, Denver, CO, USA, 21–25 June 2009; pp. 2126–2130.

- Uranga, A.; Sobreviela, G.; Barniol, N.; Marigo, E.; Tay-Wee-Song, C.; Shunmugam, M.; Zainuddin, A.A.; Kumar-Kantimahanti, A.; Madhaven, V.; Soundara-Pandian, M. Dual-clock with single and monolithical 0-level vacuum packaged MEMS-on-CMOS resonator. In Proceedings of the IEEE International Conference on Micro Electro Mechanical Systems, Estoril, Portugal, 18–22 January 2015; pp. 1004–1007.

- Wen, L.; Guo, B.; Haspeslagh, L.; Severi, S.; Witvrouw, A.; Puers, R. Thin film encapsulated SiGe accelerometer for MEMS above IC integration. In Proceedings of the 16th International Conference on Solid-State Sensors, Actuators and Microsystems (Trandsducers 2011), Beijing, China, 5–9 June 2011; pp. 2046–2049.

- Franke, A.E.; Heck, J.M.; Tsu-Jae, K.; Howe, R.T. Polycrystalline silicon-germanium films for integrated microsystems. J. Microelectromech. Syst. 2003, 12, 160–171. [Google Scholar] [CrossRef]

- Severi, S.; Heck, J.; Chou, T.K.A.; Belov, N.; Park, J.S.; Harrar, D.; Jain, A.; van Hoof, R.; du Bois, B.; de Coster, J.; et al. CMOS-integrated poly-SiGe cantilevers with read/write system for probe storage device. In Proceedings of the International Conference on Solid-State Sensors, Actuators and Microsystems (Transducers 2009), Denver, CO, USA, 21–25 June 2009; pp. 2409–2412.

- Silicon Laboratory, Inc. Available online: http://www.silabs.com (accessed on 20 January 2016).

- Yun, W.; Howe, R.T.; Gray, P.R. Surface micromachined, digitally force-balanced accelerometer with integrated CMOS detection circuitry. In Proceedings of the Technical Degist of Solid State Sensor and Actuator Workshop, Hilton Head Island, SC, USA, 22–25 June 1992; pp. 126–131.

- Yamane, D.; Konishi, T.; Matsushima, T.; Motohashi, G.; Kagaya, K.; Ito, H.; Ishihara, N.; Toshiyoshi, H.; Machida, K.; Masu, K. An arrayed MEMS accelerometer with a wide range of detection. In Proceedings of the International Conference on Solid-State Sensors, Actuators and Microsystems (Transducers 2013), Barcelona, Spain, 16–20 June 2013; pp. 22–25.

- Li, X.; Gu, L.; Wu, Z. High-performance RF passives using post-CMOS MEMS techniques for RF SOC. In Proceedings of the IEEE Radio Frequency Integrated Circuits Symposium, Atlanta, GA, USA, 17 June 2008; pp. 163–166.

- Hornbeck, L. Deformable-mirror spatial light modulators and applications. SPIE Crit. Rev. 1989, 1150, 86–102. [Google Scholar]

- Franke, A.E.; Bilic, D.; Chang, D.T.; Jones, P.T.; King, T.J.; Howe, R.T.; Johnson, G.C. Post-CMOS integration of germanium microstructures. In Proceedings of the IEEE International Conference on Micro Electro Mechanical Systems, Orlando, FL, USA, 17–21 January 1999; pp. 630–637.

- Sedky, S.; Fiorini, P.; Caymax, M.; Loreti, S.; Baert, K.; Hermans, L.; Mertens, R. Structural and mechanical properties of polycrystalline silicon germanium for micromachining applications. J. Microelectromech. Syst. 1998, 7, 365–372. [Google Scholar] [CrossRef]

- Salo, T.; Vancura, T.; Brand, O.; Baltes, H. CMOS-based sealed membranes for medical tactile sensor arrays. In Proceedings of the IEEE International Conference on Micro Electro Mechanical Systems, Kyoto, Japan, 23 January 2003; pp. 590–593.

- Muller, T.; Brandl, M.; Brand, O.; Baltes, H. An industrial CMOS process family adapted for the fabrication of smart silicon sensors. Sens. Actuators A Phys. 2000, 84, 126–133. [Google Scholar] [CrossRef]

- Najafi, K.; Wise, K.D.; Mochizuki, T. A high-yield IC-compatible multichannel recording array. IEEE Trans. Electron Devices 1985, 32, 1206–1211. [Google Scholar] [CrossRef]

- Chen, W.C.; Fang, W.L.; Li, S.S. A generalized CMOS-MEMS platform for micromechanical resonators monolithically integrated with circuits. J. Micromech. Microeng. 2011, 21, 065012. [Google Scholar] [CrossRef]

- Verd, J.; Uranga, A.; Teva, J.; Lopez, J.L.; Torres, F.; Esteve, J.; Abadal, G.; Perez-Murano, F.; Barniol, N. Integrated CMOS-MEMS with on-chip readout electronics for high-frequency applications. IEEE Electron Device Lett. 2006, 27, 495–497. [Google Scholar] [CrossRef]

- Narducci, M.; Yu-Chia, L.; Fang, W.; Tsai, J. CMOS MEMS capacitive absolute pressure sensor. J. Micromech. Microeng. 2013, 23, 055007. [Google Scholar] [CrossRef]

- Li, M.H.; Chen, C.Y.; Li, C.S.; Chin, C.H.; Li, S.S. Design and characterization of a dual-mode CMOS-MEMS resonator for TCF manipulation. J. Microelectromech. Syst. 2015, 24, 446–457. [Google Scholar] [CrossRef]

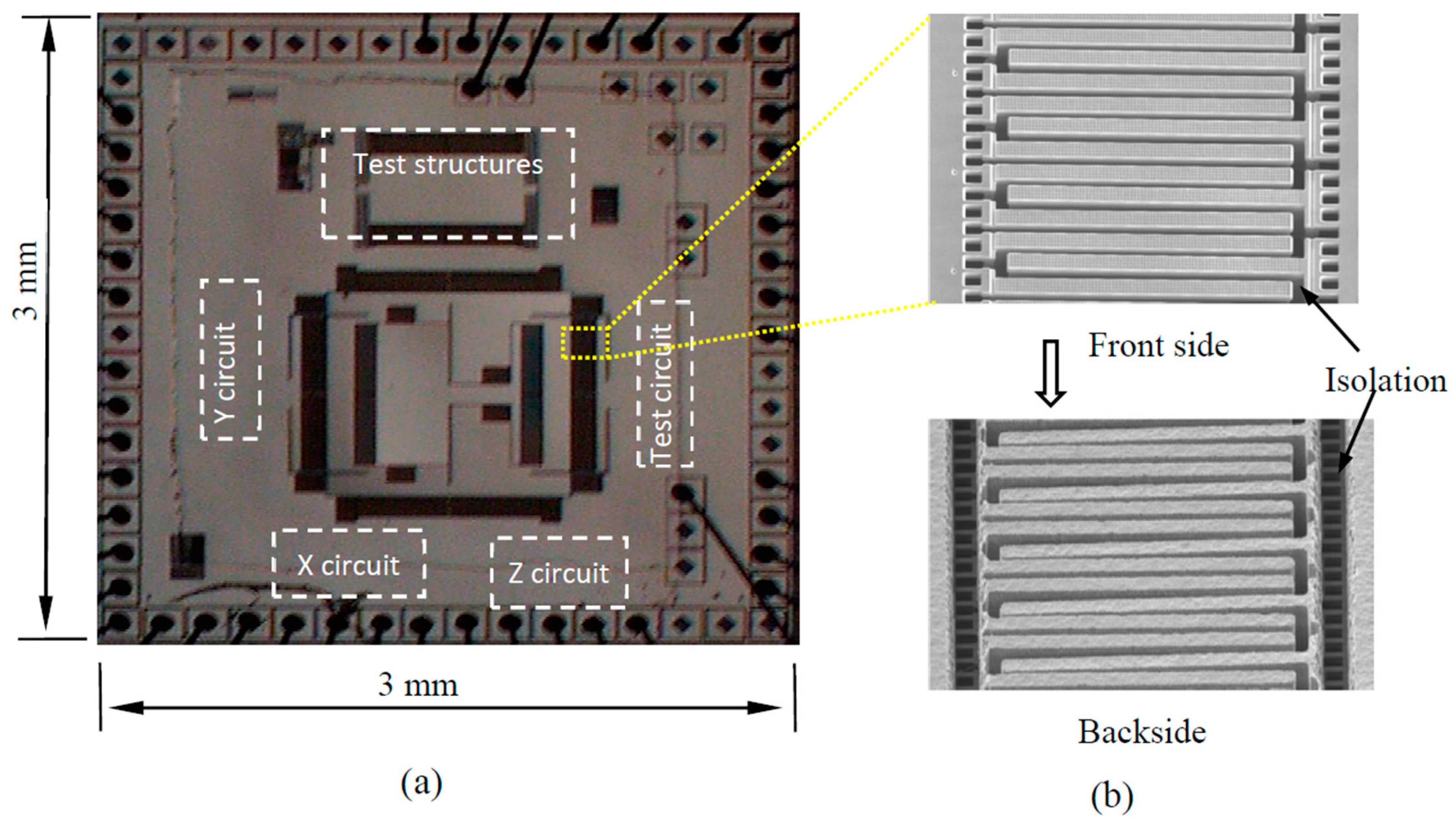

- Tsai, M.H.; Liu, Y.C.; Fang, W. A three-axis CMOS-MEMS accelerometer structure with vertically integrated fully differential sensing electrodes. J. Microelectromech. Syst. 2012, 21, 1329–1337. [Google Scholar] [CrossRef]

- Baltes, H.; Haberli, A. CMOS MEMS. In Proceedings of the IEEE International Symposium on Circuits and Systems, Hong Kong, China, 9–12 June 1997; pp. 2813–2816.

- Montanya i Silvestre, J.; Valle Fraga, J.J.; Barrachina Saralegui, L.; Fernandez Martinez, D. MEMS devices and sensors in standard CMOS processing. In Proceedings of the International Conference on Solid-State Sensors, Actuators and Microsystems, Barcelona, Spain, 16–20 June 2013; pp. 713–717.

- Borky, J.M.; Wise, K.D. Integrated signal conditioning for silicon pressure sensors. IEEE Trans. Electron. Devices 1979, 27, 927–930. [Google Scholar] [CrossRef]

- Yoon, E.; Wise, K.D. A multi-element monolithic mass flowmeter with on-chip CMOS readout electronics. In Proceedings of the IEEE Solid-State Sensor and Actuator Workshop, Hilton Head Island, SC, USA, 4–7 June 1990; pp. 161–164.

- Haberli, A.; Paul, O.; Malcovati, P.; Faccio, M.; Maloberti, F.; Baltes, H. CMOS integration of a thermal pressure sensor system. In Proceedings of the IEEE International Symposium on Circuits and Systems, Atlanta, GA, USA, 12–15 May 1996; pp. 377–380.

- Schneider, M.; Muller, T.; Haberli, A.; Hornung, M.; Baltes, H. Integrated micromachined decoupled CMOS chip on chip. In Proceedings of the International Workshop on Micro Electro Mechanical Systems, Nagoya, Japan, 26–30 January 1997; pp. 512–517.

- Akiyama, T.; Staufer, U.; Rooij, N.F.D.; Lange, D.; Hagleitner, C.; Brand, O.; Baltes, H.; Tonin, A.; Hidber, H.R. Integrated atomic force microscopy array probe with MOSFET transistor stress sensor, thermal bimorph actuator, and on-chip CMOS electronics. J. Vac. Sci. Technol. B 2000, 18, 2669–2675. [Google Scholar] [CrossRef]

- Schaufelbuhl, A.; Schneeberger, N.; Munch, U.; Waelti, M.; Paul, O.; Brand, O.; Baltes, H.; Menolfi, C.; Huang, Q.; Doering, E.; et al. Uncooled low-cost thermal imager based on micromachined CMOS integrated sensor array. J. Microelectromech. Syst. 2001, 10, 503–510. [Google Scholar] [CrossRef]

- Laermer, F.; Schilp, A. Method of Anisotropically Etching Silicon. U.S. Patent 5501893, 5 December 1992. [Google Scholar]

- Kruglick, E.J.J.; Warneke, B.A.; Pister, K.S.J. CMOS 3-axis accelerometers with integrated amplifier. In Proceedings of the IEEE International Workshop on Micro Electro Mechanical Systems, Heidelberg, Germany, 25–29 January 1998; pp. 631–636.

- Fedder, G.K.; Santhanam, S.; Reed, M.L.; Eagle, S.C.; Guillou, D.F.; Lu, M.S.C.; Carley, L.R. Laminated high-aspect-ratio microstructures in a conventional CMOS process. In Proceedings of the IEEE International Workshop on Micro Electro Mechanical Systems, San Diego, CA, USA, 11–15 February 1996; pp. 13–18.

- Xie, H.; Fedder, G.K. A CMOS z-axis capacitive accelerometer with comb-finger sensing. In Proceedings of the IEEE International Workshop on Micro Electro Mechanical Systems, Miyazaki, Japan, 23–27 January 2000; pp. 496–501.

- Xie, H.; Fedder, G.K. A CMOS-MEMS lateral-axis gyroscope. In Proceedings of the IEEE International Workshop on Micro Electro Mechanical Systems, Interlaken, Switzerland, 21–25 January 2001; pp. 162–165.

- Luo, H.; Fedder, G.; Carley, L.R. Integrated multiple-device IMU system with continuous-time sensing circuitry. In Proceedings of the IEEE International Solid-State Circuits Conference, San Francisco, CA, USA, 13 February 2003; pp. 204–205.

- Dai, C.L. A capacitive humidity sensor integrated with micro heater and ring oscillator circuit fabricated by CMOS-MEMS technique. Sens. Actuators B Chem. 2007, 122, 375–380. [Google Scholar] [CrossRef]

- Lazarus, N.; Bedair, S.S.; Lo, C.C.; Fedder, G.K. CMOS-MEMS capacitive humidity sensor. J. Microelectromech. Syst. 2010, 19, 183–191. [Google Scholar] [CrossRef]

- Chang, C.; Tsai, M.; Liu, Y.; Sun, C.; Fang, W. Development of multi-axes CMOS-MEMS resonant magnetic sensor using lorentz and electromagnetic forces. In Proceedings of the International Conference on Micro Electro Mechanical Systems, Taipei, Taiwan, 20–24 January 2013; pp. 193–196.

- Wang, C.; Lee, S.Y.; Sun, C.M.; Tsai, M.H.; Fang, W. Implementation of CMOS-MEMS compound lens. In Proceedings of the IEEE/LEOS International Conference on Optical MEMS and Nanophotonics, Hualien, Taiwan, 12–16 August 2007; pp. 143–144.

- Tsai, T.H.; Tsai, H.C.; Wu, T.K. A CMOS micromachined capacitive tactile sensor with integrated readout circuits and compensation of process variations. IEEE Trans. Biomed. Circuits Syst. 2014, 8, 608–616. [Google Scholar] [CrossRef] [PubMed]

- Munoz-Contreras, F.; Verd, J.; Segura, J.; Uranga, A.; Riverola, M.; Barniol, N. Torwards a fully-integrated CMOS microcalorimeter with on-chip quasi-digital output signal. In Proceedings of the IEEE Sensors Conference, Baltimore, MD, USA, 3–6 November 2013; pp. 1–4.

- Jahnes, C.; Cotte, J.; Lund, J.; Deligianni, H.; Chinthakindi, A.; Buchwalter, L.; Fryer, P.; Tornello, J.; Hoivik, N.; Magerlein, J.; et al. Simultaneous fabrication of RF MEMS switches and resonators using copper-based CMOS interconnect manufacturing methods. In Proceedings of the IEEE International Conference on Micro Electro Mechanical Systems, Maastricht, The Netherlands, 25–29 January 2004.

- Stamper, A.K.; Jahnes, C.V.; Dupuis, S.R.; Gupta, A.; He, Z.X.; Herrin, R.T.; Luce, S.E.; Maling, J.; Miga, D.R.; Murphy, W.J.; et al. Planar MEMS RF capacitor integration. In Proceedings of the International Conference on Solid-State Sensors, Actuators and Microsystems (Transducers 2011), Beijing, China, 5–9 June 2011; pp. 1803–1806.

- AKUSTICA Bosch Group. Available online: http://www.akustica.com (accessed on 20 January 2016).

- Jiang, L.; Cai, Y.; Liu, H.; Zhao, Y. A micromachined monolithic 3 axis accelerometer based on convection heat transfer. In Proceedings of the IEEE International Conference on Nano/Micro Engineered and Molecular Systems, Suzhou, China, 7–10 April 2013; pp. 248–251.

- Zhang, G.; Xie, H.; de Rosset, L.E.; Fedder, G.K. A lateral capacitive CMOS accelerometer with structural curl compensation. In Proceedings of the IEEE International Conference on Micro Electro Mechanical Systems, Orlando, FL, USA, 19–21 January 1999; pp. 606–611.

- Xie, H.; Erdmann, L.; Zhu, X.; Gabriel, K.J.; Fedder, G.K. Post-CMOS processing for high-aspect-ratio integrated silicon microstructures. J. Microelectromech. Syst. 2002, 11, 93–101. [Google Scholar]

- Jain, A.; Qu, H.; Todd, S.; Xie, H. A thermal bimorph micromirror with large bi-directional and vertical actuation. Sens. Actuators A Phys. 2005, 122, 9–15. [Google Scholar] [CrossRef]

- Xie, H.; Fedder, G.K. Fabrication, characterization, and analysis of a DRIE CMOS-MEMS gyroscope. IEEE Sens. J. 2003, 3, 622–631. [Google Scholar]

- Haris, M.; Qu, H. Fully differential CMOS-MEMS z-axis accelerometer with torsional structures and planar comb fingers. J. Micro Nanolithogr. MEMS MOEMS 2010, 9, 013031. [Google Scholar] [CrossRef]

- Khir, M.; Qu, P.; Qu, H. A low-cost CMOS-MEMS piezoresistive accelerometer with large proof mass. Sensors 2011, 11, 7892–7907. [Google Scholar] [CrossRef] [PubMed]

- Qu, H.; Xie, H. Process development for CMOS-MEMS sensors with robust electrically isolated bulk silicon microstructures. J. Microelectromech. Syst. 2007, 16, 1152–1161. [Google Scholar]

- Qu, H.; Fang, D.; Xie, H. A monolithic CMOS-MEMS 3-axis accelerometer with a low-noise, low-power dual-chopper amplifier. IEEE Sens. J. 2008, 8, 1511–1518. [Google Scholar]

- Tan, S.S.; Liu, C.Y.; Yeh, L.K.; Chiu, Y.H.; Hsu, K.Y.J. A new process for CMOS MEMS capacitive sensors with high sensitivity and thermal stability. J. Micromech. Microeng. 2011, 21, 035005. [Google Scholar] [CrossRef]

- Sung, J.; Kim, J.Y.; Seok, S.; Kwon, H.J.; Kim, M.; Kim, G.; Lim, G. A gyroscope fabrication method for high sensitivity and robustness to fabrication tolerances. J. Micromech. Microeng. 2014, 24, 075013. [Google Scholar] [CrossRef]

- Lee, Y.S.; Jang, Y.H.; Kim, Y.K.; Kim, J.M. Thermal de-isolation of silicon microstructures in a plasma etching environment. J. Micromech. Microeng. 2013, 23, 025026. [Google Scholar] [CrossRef]

- Jin, J.Y.; Park, J.H.; Yoo, B.W.; Jang, Y.H.; Kim, Y.K. Numerical analysis and demonstration of a 2-DoF large-size micromirror with sloped electrodes. J. Micromech. Microeng. 2011, 21, 095006. [Google Scholar] [CrossRef]

- Hagleitner, C.; Lange, D.; Hierlemann, A.; Brand, O.; Baltes, H. CMOS single-chip gas detection system comprising capacitive, calorimetric and mass-sensitive microsensors. IEEE J. Solid State Circuits 2002, 37, 1867–1878. [Google Scholar] [CrossRef]

- Sun, C.; Tsai, M.; Wang, C.; Liu, Y.; Fang, W. Implementation of a monolithic TPMS using CMOS-MEMS technique. In Proceedings of the International Conference on Solid-State Sensors, Actuators and Microsystems (Transducers 2009), Denver, CO, USA, 21–25 June 2009; pp. 1730–1733.

- Yen, T.H.; Tsai, M.H.; Chang, C.I.; Liu, Y.C.; Li, S.S.; Chen, R.; Chiou, J.C.; Fang, W. Improvement of CMOS-MEMS accelerometer using the symmetric layers stacking design. In Proceedings of the IEEE Sensors Conference, Taipei, Taiwan, 28–31 October 2011; pp. 145–148.

- Dai, C.L.; Lu, P.W.; Chang, C.L.; Liu, C.Y. Capacitive micro pressure sensor integrated with a ring oscillator circuit on chip. Sensors 2009, 9, 10158–10170. [Google Scholar] [CrossRef] [PubMed]

- Bakri-Kassem, M.; Fouladi, S.; Mansour, R.R. Novel high-Q MEMS curled-plate variable capacitors fabricated in 0.35-μm CMOS technology. IEEE Trans. Microw. Theory Tech. 2008, 56, 530–541. [Google Scholar] [CrossRef]

- Arcamone, J.; Philippe, J.; Arndt, G.; Dupre, C.; Savoye, M.; Hentz, S.; Ernst, T.; Colinet, E.; Duraffourg, L.; Ollier, E. Nanosystems monolithically integrated with CMOS: Emerging applications and technologies. In Proceedings of the IEEE International Electron Devices Meeting, San Francisco, CA, USA, 15–17 December 2014; pp. 21–24.

- Philippe, J.; Arndt, G.; Colinet, E.; Savoye, M.; Ernst, T.; Ollier, E.; Arcamone, J. Fully monolithic and ultra-compact NEMS-CMOS self-oscillator based-on single-crystal silicon resonators and low-cost CMOS circuitry. In Proceedings of the IEEE International Conference on Micro Electro Mechanical Systems, San Francisco, CA, USA, 26–30 January 2014; pp. 1071–1074.

- Takao, H.; Ichikawa, T.; Nakata, T.; Sawada, K.; Ishida, M. A versatile integration technology of SOI-MEMS/CMOS devices using microbridge interconnection structures. J. Microelectromech. Syst. 2010, 19, 919–926. [Google Scholar] [CrossRef]

- Villarroya, M.; Figueras, E.; Montserrat, J.; Verd, J.; Teva, J.; Abadal, G.; Murano, F.P.; Esteve, J.; Barniol, N. A platform for monolithic CMOS-MEMS integration on SOI wafers. J. Micromech. Microeng. 2006, 16, 2203–2210. [Google Scholar] [CrossRef]

- Chen, T.D.; Kelly, T.W.; Collins, D.; Berthold, B.; Brosnihan, T.J.; Denison, T.; Kuang, J.; O’Kane, M.; Weigold, J.W.; Bain, D. The next generation integrated MEMS and CMOS process on SOI wafers for overdamped accelerometers. In Proceedings of the International Conference on Solid-State Sensors, Actuators and Microsystems, Seoul, Korea, 5–9 June 2005; pp. 1122–1125.

- Takahashi, K.; Mita, M.; Nakada, M.; Yamane, D.; Higo, A.; Fujita, H.; Toshiyoshi, H. Development of multi-user multi-chip SOI CMOS-MEMS processes. In Proceedings of the IEEE International Conference on Micro Electro Mechanical Systems, Sorrento, Italy, 25–29 January 2009; pp. 701–704.

- Liu, H.; Chollet, F. Layout controlled one-step dry etch and release of MEMS using deep RIE on SOI wafer. J. Microelectromech. Syst. 2006, 15, 541–547. [Google Scholar]

- Xu, M.; Yumin, W.; Zhenchuan, Y.; Guizhen, Y. Fabrication of SOI MEMS inertial sensors with dry releasing process. In Proceedings of the IEEE Sensors Conference, Christchurch, New Zealand, 25–28 October 2009; pp. 479–482.

- Analog Devices, Inc. ADXRS453 Datasheet High Performance, Digital Output Gyroscope. Available online: http://www.analog.com (accessed on 20 January 2016).

- Takao, H.; Ichikawa, T.; Nakata, T.; Sawada, K.; Ishida, M. Post-CMOS integration technology of thick-film SOI MEMS devices using micro bridge interconnections. In Proceedings of the IEEE International Conference on Micro Electro Mechanical Systems, Tucson, AZ, USA, 13–17 January 2008; pp. 359–362.

- Rajaraman, V.; Koning, J.J.; Ooms, E.; Pandraud, G.; Makinwa, K.A.A.; Boezen, H. Below-IC post-CMOS integration of thick MEMS on a thin-SOI platform using embedded interconnects. In Proceedings of the IEEE International Conference on Micro Electro Mechanical Systems, Paris, France, 29 January–2 February 2012; pp. 220–223.

- Ali, S.Z.; Udrea, F.; Milne, W.I.; Gardner, J.W. Tungsten-based SOI microhotplates for smart gas sensors. J. Microelectromech. Syst. 2008, 17, 1408–1417. [Google Scholar] [CrossRef]

- Corcos, D.; Goren, D.; Nemirovsky, Y. CMOS-SOI-MEMS transistor (teramos) for terahertz imaging. In Proceedings of the IEEE International Conference on Microwaves, Communications, Antennas and Electronics Systems, Tel-Aviv, Israel, 9–11 November 2009; pp. 1–5.

- Gitelman, L.; Stolyarova, S.; Bar-Lev, S.; Gutman, Z.; Ochana, Y.; Nemirovsky, Y. CMOS-SOI-MEMS transistor for uncooled IR imaging. IEEE Trans. Electron Devices 2009, 56, 1935–1942. [Google Scholar] [CrossRef]

- Maruyama, S.; Takahashi, K.; Fujita, H.; Toshiyoshi, H. A MEMS digital mirror array integrated with high-voltage level-shifter. In Proceedings of the International Conference on Solid-State Sensors, Actuators and Microsystems (Transducers 2009), Denver, CO, USA, 21–25 June 2009; pp. 2314–2317.

- Lee, K.; Noriki, A.; Kiyoyama, K.; Fukushima, T.; Tanaka, T.; Koyanagi, M. Three-dimensional hybrid integration technology of CMOS, MEMS and photonics circuits for optoelectronic heterogeneous integrated systems. IEEE Trans. Electron Devices 2011, 58, 748–757. [Google Scholar] [CrossRef]

- Chan, W.P.; George, A.K.; Narducci, M.S.; Cheam, D.D.; Leong, S.C.; Tsai, M.L.; Rahman, A.R.A.; Park, M.K.; Kong, Z.H.; Rao, J.P.; et al. A pressure/oxygen/temperature sensing SOC for multimodality intracranial neuromonitoring. In Proceedings of the IEEE Asian Solid-State Circuits Conference, Sentosa, Singapore, 11–13 November 2013; pp. 89–92.

- Ramm, P.; Klumpp, A.; Weber, J.; Lietaer, N.; Taklo, M.; de Raedt, W.; Fritzsch, T.; Couderc, P. 3D integration technology: Status and application development. In Proceedings of the IEEE European Conference on Solid-State Circuits, Seville, Spain, 14–16 September 2010; pp. 9–16.

- Masayoshi, E. Wafer level packaging of MEMS. J. Micromech. Microeng. 2008, 18, 073001. [Google Scholar]

- International Technology Roadmap for Semiconductors (ITRS). Micro-Electro-Mechanical Systems (MEMS) Summary. Available online: http://www.itrs2.net/ (accessed on 20 July 2015).

© 2016 by the author; licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons by Attribution (CC-BY) license ( http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Qu, H. CMOS MEMS Fabrication Technologies and Devices. Micromachines 2016, 7, 14. https://doi.org/10.3390/mi7010014

Qu H. CMOS MEMS Fabrication Technologies and Devices. Micromachines. 2016; 7(1):14. https://doi.org/10.3390/mi7010014

Chicago/Turabian StyleQu, Hongwei. 2016. "CMOS MEMS Fabrication Technologies and Devices" Micromachines 7, no. 1: 14. https://doi.org/10.3390/mi7010014