Monolithic Low Noise and Low Zero-g Offset CMOS/MEMS Accelerometer Readout Scheme

Abstract

:1. Introduction

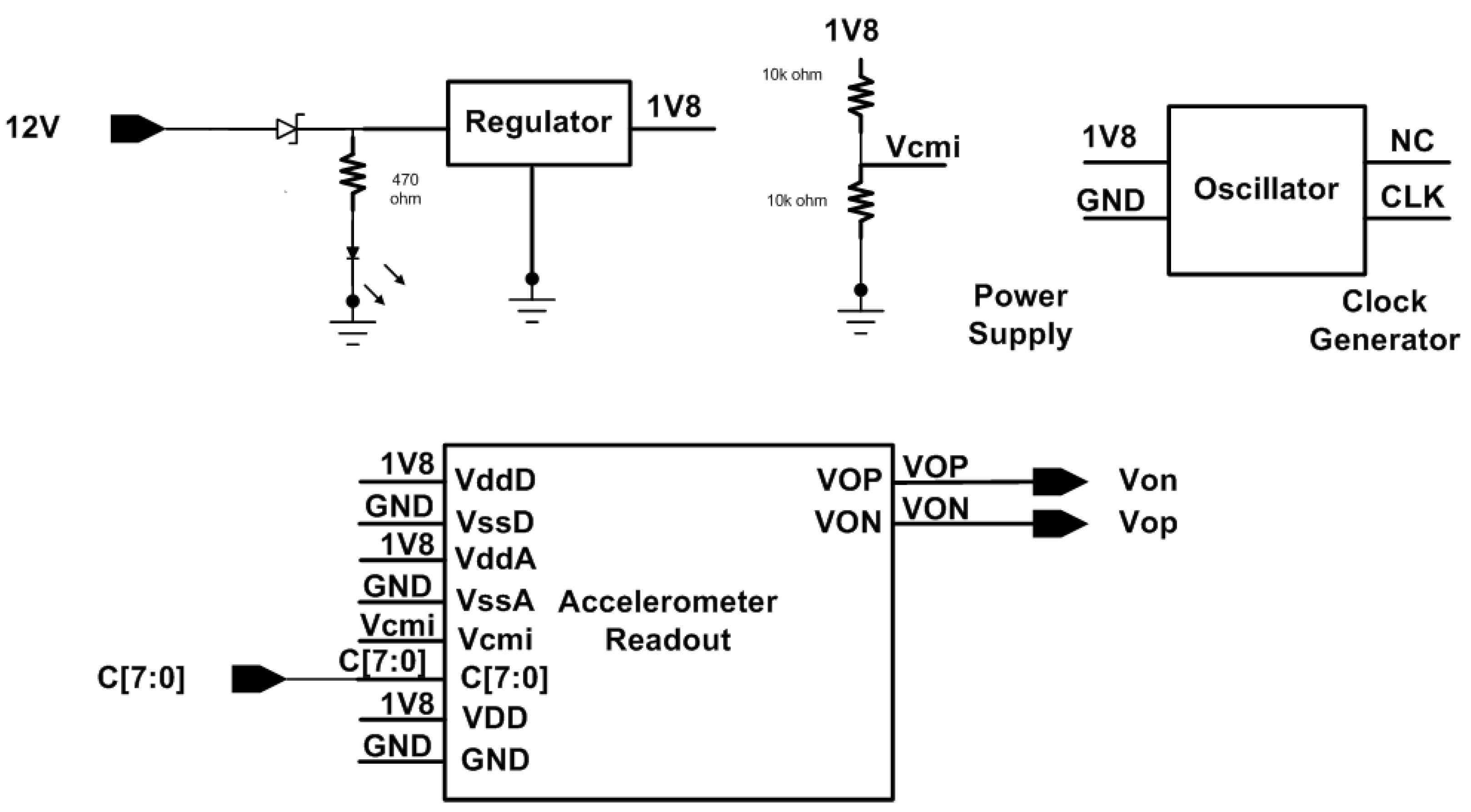

2. Materials and Methods

2.1. CMOS/MEMS Accelerometer

2.2. Readout Circuit Design

2.2.1. Low Noise Chopper Architecture

2.2.2. Low Zero-g Offset Design

3. Results

3.1. CMOS/MEMS Accelerometer

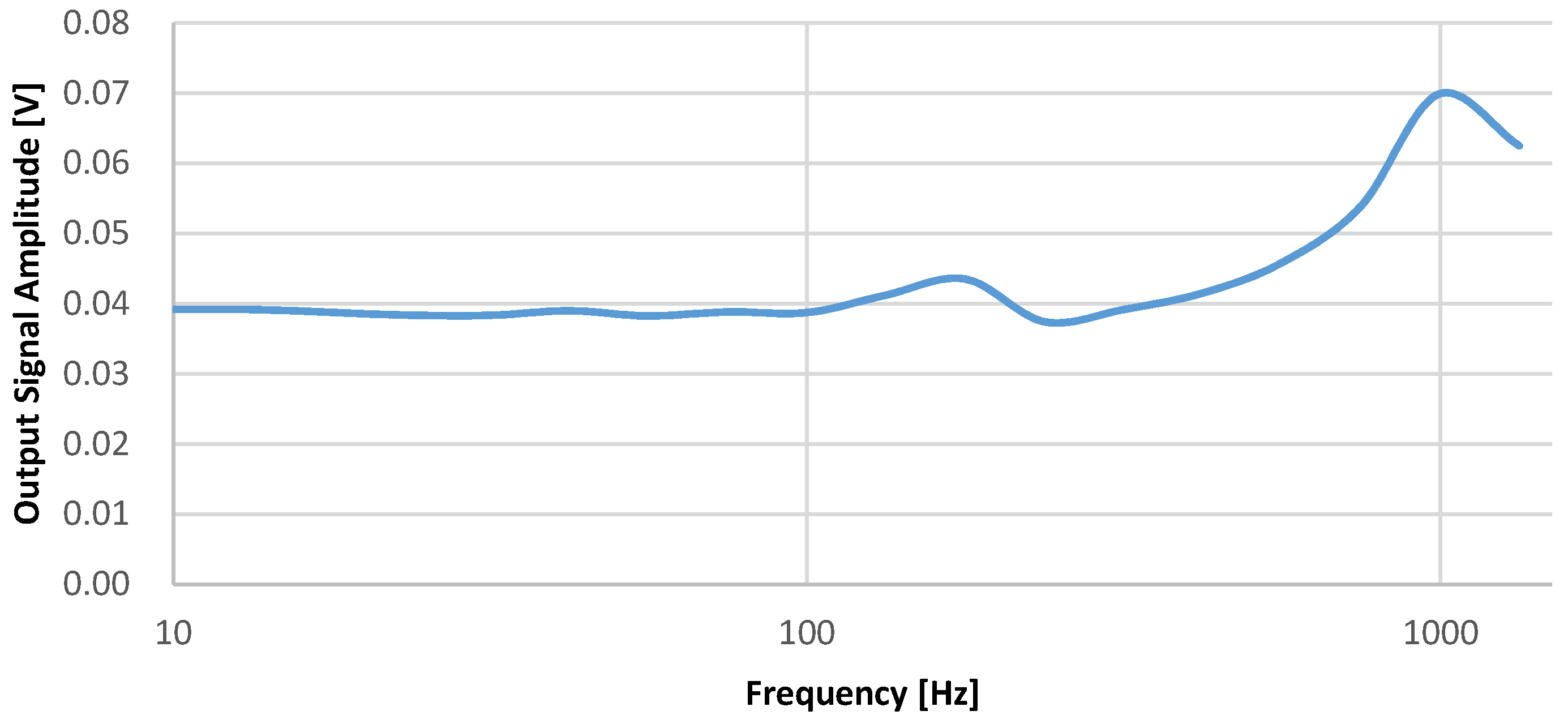

3.2. Low Noise Design

Noise Considerations in Board Design

3.3. Low Zero-g Offset Design

4. Discussion and Conclusions

Author Contributions

Funding

Conflicts of Interest

References

- Qu, H.; Fang, D.; Xie, H. A monolithic CMOS-MEMS 3-axis accelerometer with a low-noise, low-power dual-chopper amplifier. IEEE Sens. J. 2008, 8, 1511–1518. [Google Scholar] [CrossRef]

- Akita, I.; Okazawa, T.; Kurui, Y.; Fujimoto, A.; Asano, T. A 181 nW 970 µg/√Hz accelerometer analog front-end employing feedforward noise reduction technique. In Proceedings of the 2018 IEEE Symposium on VLSI Circuits, Honolulu, HI, USA, 18–22 June 2018; pp. 161–162. [Google Scholar] [CrossRef]

- Paavola, M. A Micropower ΔΣ-Based Interface ASIC for a Capacitive 3-Axis Micro-Accelerometer. IEEE J. Solid-State Circuits 2009, 44, 3193–3210. [Google Scholar] [CrossRef]

- Petkov, V.P.; Balachandran, G.K.; Beintner, J. A fully differential charge-balanced accelerometer for electronic stability control. IEEE J. Solid-State Circuits 2014, 49, 262–270. [Google Scholar] [CrossRef]

- Fang, D.; Qu, H.; Xie, H. A 1mW dual-chopper amplifier for a 50-μg/√Hz monolithic CMOS-MEMS capacitive accelerometer. In Proceedings of the 2006 IEEE Symposium on VLSI Circuits, Honolulu, HI, USA, 15–17 June 2016. [Google Scholar] [CrossRef]

- Sun, H.; Fang, D.; Jia, K.; Maarouf, F.; Qu, H.; Xie, H. A low-power low-noise dual-chopper amplifier for capacitive CMOS-MEMS accelerometers. IEEE Sens. J. 2011, 11, 925–933. [Google Scholar] [CrossRef]

- Sun, H.; Maarouf, F.; Fang, D.; Jia, K.; Xie, H. An improved low-power low-noise dual-chopper amplifier for capacitive CMOS-MEMS accelerometers. In Proceedings of the 2008 3rd IEEE International Conference on Nano/Micro Engineered and Molecular Systems, Sanya, China, 6–9 January 2008. [Google Scholar]

- Bergert, J.; Strache, S.; Wunderlich, R.; Droste, D.; Heinen, S. Offset correction in dual-chopper read-out circuits for half-bridge capacitive accelerometers. In Proceedings of the 2012 8th Conference on Ph.D. Research in Microelectronics & Electronics (PRIME), Aachen, Germany, 12–15 June 2012. [Google Scholar]

- Lemkin, M.; Boser, B.E. A three-axis micromachined accelerometer with a CMOS position-sense interface and digital offset-trim electronics. IEEE J. Solid-State Circuits 1999, 34, 456–468. [Google Scholar] [CrossRef]

- ADXL103, Datasheet, Analog Devices, Inc. Available online: https://www.analog.com/ADXL103 (accessed on 26 November 2018).

- Liu, Y.; Huang, C.; Kuo, F.; Wen, K.; Fan, L. A monolithic CMOS/MEMS accelerometer with zero-g calibration readout circuit. In Proceedings of the Eurocon 2013, Zagreb, Croatia, 1–4 July 2013; pp. 2106–2110. [Google Scholar] [CrossRef]

- Friis, H.T. Noise figures of radio receivers. Proc. IRE 1944, 32, 419–422. [Google Scholar] [CrossRef]

- Zhao, J. A 0.23-μg bias instability and 1-μg/√Hz acceleration noise density silicon oscillating accelerometer with embedded frequency-to-digital converter in PLL. IEEE J. Solid-State Circuits 2017, 52, 1053–1065. [Google Scholar] [CrossRef]

| Specifications | Post-Sim | Measurement |

|---|---|---|

| System frequency (MHz) | 1 | 1 |

| Chopper frequency (kHz) | 333.33 | 333.33 |

| Overall sensitivity (mV/g) (at 1 g 100 Hz) | 434.93 | 470 |

| Noise (μg/√Hz) (at 1 g 100 Hz) | 10 | 421.70 |

| Resonance Frequency (kHz) | 4.16 | 1.25 |

| Brownian noise (μg/√Hz) | 7.9 | - |

| Sensing Range (g) | ±1 | ±1 |

| Power (mW) | 2 | 1.67 |

| Stage | This Work | Reference [1] | ||||

|---|---|---|---|---|---|---|

| Signal Frequency (Hz) | Power (μW) | Noise (μg/√Hz) | Signal Frequency (Hz) | Power (μW) | Noise (μg/√Hz) | |

| Main Amp. | 333.33 kHz | 37.18 | 40.45 | 1 MHz | 29.93 | 30.18 |

| Pre-Amp | 333.33 kHz | 40.17 | 59.84 | 20 kHz | 39.40 | 171.80 |

| Total | 77.34 | 48.04 | 69.33 | 51.97 | ||

| Parameters | [3] | [4] | [13] | [2] | This Work |

|---|---|---|---|---|---|

| Sensing Range (g) | ±4 | ±49 | ±30 | ±8 | ±1 |

| Noise Floor (μg/√Hz) | 930 | 380 | 1 | 970 | 421.70 |

| Zero-g Offset (mg) | N/A | N/A | N/A | ±33 | 2.30 |

| Supply Power (V) | 1.2 | 1.9/3.3 1 | 1.5 | 1 | 1.8 |

| Power (W) | 25.44 μ | 1.4 m | 2.7 m | 181 n | 1.67 m |

| Chip Area (Readout Circuit) (mm2) | 1.73 | 1.1 | 10.9 | 1.14 | 1.23 |

| Process | 0.25 μm CMOS process | 0.18 μm CMOS process | 0.35 μm CMOS process | 0.18 μm CMOS process | UMC 0.18 μm CMOS/MEMS |

© 2018 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Liu, Y.-S.; Wen, K.-A. Monolithic Low Noise and Low Zero-g Offset CMOS/MEMS Accelerometer Readout Scheme. Micromachines 2018, 9, 637. https://doi.org/10.3390/mi9120637

Liu Y-S, Wen K-A. Monolithic Low Noise and Low Zero-g Offset CMOS/MEMS Accelerometer Readout Scheme. Micromachines. 2018; 9(12):637. https://doi.org/10.3390/mi9120637

Chicago/Turabian StyleLiu, Yu-Sian, and Kuei-Ann Wen. 2018. "Monolithic Low Noise and Low Zero-g Offset CMOS/MEMS Accelerometer Readout Scheme" Micromachines 9, no. 12: 637. https://doi.org/10.3390/mi9120637