Efficient Activation and High Mobility of Ion-Implanted Silicon for Next-Generation GaN Devices

Abstract

:1. Introduction

2. Materials and Methods

3. Results

4. Conclusions

Author Contributions

Funding

Data Availability Statement

Acknowledgments

Conflicts of Interest

References

- Pengelly, R.S.; Wood, S.M.; Milligan, J.W.; Sheppard, S.T.; Pribble, W.L. A review of GaN on SiC high electron-mobility power transistors and MMICs. IEEE Trans. Microw. Theory Tech. 2012, 60, 1764–1783. [Google Scholar] [CrossRef]

- Wu, Y.F.; Gritters, J.; Shen, L.; Smith, R.P.; Swenson, B. kV-Class GaN-on-Si HEMTs enabling 99% efficiency converter at 800 V and 100 kHz. IEEE Trans. Power Electron. 2014, 29, 2634–2637. [Google Scholar] [CrossRef]

- Chen, K.J.; Häberlen, O.; Lidow, A.; Tsai, C.L.; Ueda, T.; Uemoto, Y.; Wu, Y. GaN-on-Si power technology: Devices and applications. IEEE Trans. Electron. Devices 2017, 64, 779–795. [Google Scholar] [CrossRef]

- DenBaars, S.P.; Feezell, D.; Kelchner, K.; Pimputkar, S.; Pan, C.-C.; Yen, C.-C.; Tanaka, S.; Zhao, Y.; Pfaff, N.; Farrell, R.; et al. Development of gallium-nitride-based light-emitting diodes (LEDs) and laser diodes for energy-efficient lighting and displays. Acta Mater. 2013, 61, 945–951. [Google Scholar] [CrossRef]

- Nie, H.; Diduck, Q.; Alvarez, B.; Edwards, A.P.; Kayes, B.M.; Zhang, M.; Ye, G.; Prunty, T.; Bour, D.; Kizilyalli, I.C. 1.5-kV and 2.2-mΩ-cm2 Vertical GaN Transistors on Bulk-GaN Substrates. IEEE Electron Device Lett. 2014, 35, 939–941. [Google Scholar] [CrossRef]

- Sun, M.; Zhang, Y.; Gao, X.; Palacios, T. High-performance GaN vertical fin power transistors on bulk GaN substrates. IEEE Electron Device Lett. 2017, 38, 509–512. [Google Scholar] [CrossRef]

- Zhang, Y.; Liu, Z.; Tadjer, M.J.; Sun, M.; Piedra, D.; Hatem, C.; Anderson, T.J.; Luna, L.E.; Nath, A.; Koehler, A.D.; et al. Vertical GaN junction barrier schottky rectifiers by selective ion implantation. IEEE Electron Device Lett. 2017, 38, 1097–1100. [Google Scholar] [CrossRef]

- Chang, A.S.; Li, B.; Wang, S.; Frisone, S.; Goldman, R.S.; Han, J.; Lauhon, L.J. Unveiling the influence of selective-area-regrowth interfaces on local electronic properties of GaN p-n junctions for efficient power devices. Nano Energy 2022, 102, 107689. [Google Scholar] [CrossRef]

- Unland, J.; Onderka, B.; Davydov, A.; Schmid-Fetzer, R. Thermodynamics and phase stability in the Ga–N system. J. Cryst. Growth 2003, 256, 33–51. [Google Scholar] [CrossRef]

- Unland, J.; Onderka, B.; Davydov, A.; Schmid-Fetzer, R. Recent progress of Mg-ion implantation and thermal activation process for p-doping in GaN (conference presentation). In Proceedings of the Gallium Nitride Materials and Devices XIV, San Francisco, CA, USA, 13 March 2019; p. 30. [Google Scholar]

- Sierakowski, K.; Jakiela, R.; Lucznik, B.; Kwiatkowski, P.; Iwinska, M.; Turek, M.; Sakurai, H.; Kachi, T.; Bockowski, M. High pressure processing of ion implanted gan. Electron 2020, 9, 1380. [Google Scholar] [CrossRef]

- Sakurai, H.; Narita, T.; Hirukawa, K.; Yamada, S.; Koura, A.; Kataoka, K.; Horita, M.; Ikarashi, N.; Bockowski, M.; Suda, J.; et al. Impacts of high temperature annealing above 1400 °C under N2 overpressure to activate acceptors in Mg-implanted GaN. In Proceedings of the 2020 32nd International Symposium on Power Semiconductor Devices and ICs (ISPSD), Vienna, Austria, 13–18 September 2020; pp. 321–324. [Google Scholar]

- Narita, T.; Yoshida, H.; Tomita, K.; Kataoka, K.; Sakurai, H.; Horita, M.; Bockowski, M.; Ikarashi, N.; Suda, J.; Kachi, T.; et al. Progress on and challenges of p-type formation for GaN power devices. J. Appl. Phys. 2020, 128, 090901. [Google Scholar] [CrossRef]

- Matys, M.; Ishida, T.; Nam, K.P.; Sakurai, H.; Kataoka, K.; Narita, T.; Uesugi, T.; Bockowski, M.; Nishimura, T.; Suda, J.; et al. Design and demonstration of nearly-ideal edge termination for GaN p-n junction using Mg-implanted field limiting rings. Appl. Phys. Express 2021, 14, 074002. [Google Scholar] [CrossRef]

- Matys, M.; Ishida, T.; Nam, K.P.; Sakurai, H.; Narita, T.; Uesugi, T.; Bockowski, M.; Suda, J.; Kachi, T. Mg-implanted bevel edge termination structure for GaN power device applications. Appl. Phys. Lett. 2021, 118, 3–8. [Google Scholar] [CrossRef]

- Irokawa, Y.; Kim, J.; Ren, F.; Baik, K.; Gila, B.; Abernathy, C.; Pearton, S.; Pan, C.-C.; Chen, G.-T.; Chyi, J.-I.; et al. Si+ ion implanted MPS bulk GaN diodes. Solid State Electron. 2004, 48, 827–830. [Google Scholar] [CrossRef]

- Yoshino, M.; Ando, Y.; Deki, M.; Toyabe, T.; Kuriyama, K.; Honda, Y.; Nishimura, T.; Amano, H.; Kachi, T.; Nakamura, T. Fully ion implanted normally-off GaN DMOSFETs with ALD-Al 2 O 3 gate dielectrics. Materials 2019, 12, 689. [Google Scholar] [CrossRef] [PubMed]

- Ito, K.; Tomita, K.; Kikuta, D.; Horita, M.; Narita, T. Analysis of channel mobility in GaN-based metal-oxide-semiconductor field-effect transistors. J. Appl. Phys. 2021, 129, 084502. [Google Scholar] [CrossRef]

- Tan, H.H.; Williams, J.S.; Zou, J.; Cockayne, D.J.H.; Pearton, S.J.; Stall, R.A. Damage to epitaxial GaN layers by silicon implantation. Appl. Phys. Lett. 1996, 69, 2364–2366. [Google Scholar] [CrossRef]

- Dupuis, R.D.; Eiting, C.J.; Grudowski, P.A.; Hsia, H.; Tang, Z.; Becher, D.; Kuo, H.; Stillman, G.E.; Feng, M. Activation of silicon ion-implanted gallium nitride by furnace annealing. J. Electron. Mater. 1999, 28, 319–324. [Google Scholar]

- Nakano, Y.; Jimbo, T. Co-implantation of Si+N into GaN for n -type doping. J. Appl. Phys. 2002, 92, 3815–3819. [Google Scholar] [CrossRef]

- Nakano, Y.; Kachi, T.; Jimbo, T. N-type implantation doping of GaN. Mater. Sci. Semicond. Process. 2003, 6, 515–517. [Google Scholar] [CrossRef]

- Hager, C.E.; Jones, K.A.; Derenge, M.A.; Zheleva, T.S. Activation of ion implanted Si in GaN using a dual AlN annealing cap. J. Appl. Phys. 2009, 105, 033713. [Google Scholar] [CrossRef]

- Greenlee, J.D.; Feigelson, B.N.; Anderson, T.J.; Tadjer, M.J.; Hite, J.K.; Mastro, M.A.; Eddy, C.R.J.; Hobart, K.D.; Kub, F.J. Multicycle rapid thermal annealing optimization of Mg-implanted GaN: Evolution of surface, optical, and structural properties. J. Appl. Phys. 2014, 116, 063502. [Google Scholar] [CrossRef]

- Jacobs, A.G.; Feigelson, B.N.; Hite, J.K.; Gorsak, C.A.; Luna, L.E.; Anderson, T.J.; Kub, F.J. Polarity dependent implanted p-type dopant activation in GaN. Jpn. J. Appl. Phys. 2019, 58, SCCD07. [Google Scholar] [CrossRef]

- Jacobs, A.G.; Feigelson, B.N.; Hite, J.K.; Gorsak, C.A.; Luna, L.E.; Anderson, T.J.; Kub, F.J. Role of capping material and GaN polarity on Mg ion implantation activation. Phys. Status Solidi Appl. Mater. Sci. 2019, 217, 1900789. [Google Scholar] [CrossRef]

- Ebrish, M.A.; Anderson, T.J.; Jacobs, A.G.; Gallagher, J.C.; Hite, J.K.; Mastro, M.A.; Feigelson, B.N.; Wang, Y.; Liao, M.; Goorsky, M.; et al. Process optimization for selective area doping of GaN by ion implantation. J. Electron. Mater. 2021, 50, 4642–4649. [Google Scholar] [CrossRef]

- Gallagher, J.C.; Kub, F.J.; Anderson, T.J.; Koehler, A.D.; Foster, G.M.; Jacobs, A.G.; Feigelson, B.N.; Mastro, M.A.; Hite, J.K.; Hobart, K.D. Reduced contact resistance in GaN using selective area Si ion implantation. IEEE Trans. Semicond. Manuf. 2019, 32, 478–482. [Google Scholar] [CrossRef]

- Gallagher, J.C.; Anderson, T.J.; Koehler, A.D.; Foster, G.M.; Jacobs, A.G.; Feigelson, B.N.; Mastro, M.M.; Hite, J.K.; Hobart, K.D. Activation of ion implanted Si in semi-insulating C-doped GaN by high pressure annealing for photoconductive semiconductor switch (PCSS) applications. In Proceedings of the CS MANTECH 2019–2019 International Conference on Compound Semiconductor Manufacturing Technology, Digest of Papers, Minneapolis, MN, USA, 29 April–2 May 2019. [Google Scholar]

- Anderson, T.; Gallagher, J.; Luna, L.; Koehler, A.; Jacobs, A.; Xie, J.; Beam, E.; Hobart, K.; Feigelson, B. Effect of high temperature, high pressure annealing on GaN drift layers for vertical power devices. J. Cryst. Growth 2018, 499, 35–39. [Google Scholar] [CrossRef]

- Hite, J.; Anderson, T.; Luna, L.; Gallagher, J.; Mastro, M.; Freitas, J.; Eddy, C. Influence of HVPE substrates on homoepitaxy of GaN grown by MOCVD. J. Cryst. Growth 2018, 498, 352–356. [Google Scholar] [CrossRef]

- Jacobs, A.G.; Spencer, J.A.; Hite, J.K.; Hobart, K.D.; Anderson, T.J.; Feigelson, B.N. Novel Co-doping Moiety to Achieve Enhanced P-type doping in GaN by Ion Implantation. Phys. Status Solidi Appl. Mater. Sci. 2023. [Google Scholar] [CrossRef]

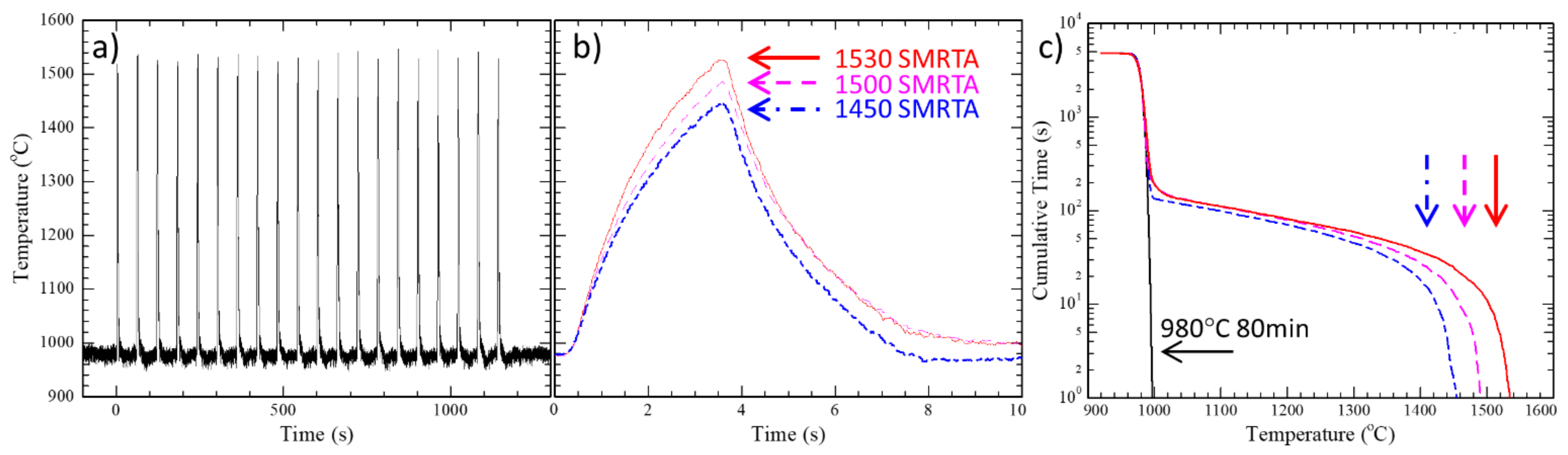

- Greenlee, J.D.; Feigelson, B.; Anderson, T.J.; Hite, J.K.; Hobart, K.D.; Kub, F.J. From MRTA to SMRTA: Improvements in activating implanted dopants in GaN. ECS Trans. 2015, 69, 97–102. [Google Scholar] [CrossRef]

- Chin, V.W.L.; Tansley, T.L.; Osotchan, T. Electron mobilities in gallium, indium, and aluminum nitrides. J. Appl. Phys. 1994, 75, 7365–7372. [Google Scholar] [CrossRef]

- Pandey, P.; Nelson, T.M.; Collings, W.M.; Hontz, M.R.; Georgiev, D.G.; Koehler, A.D.; Anderson, T.J.; Gallagher, J.C.; Foster, G.M.; Jacobs, A.; et al. A simple edge termination design for vertical GaN P-N diodes. Trans. Electron Devices 2021, 69, 5096–5103. [Google Scholar] [CrossRef]

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2023 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Jacobs, A.G.; Feigelson, B.N.; Spencer, J.A.; Tadjer, M.J.; Hite, J.K.; Hobart, K.D.; Anderson, T.J. Efficient Activation and High Mobility of Ion-Implanted Silicon for Next-Generation GaN Devices. Crystals 2023, 13, 736. https://doi.org/10.3390/cryst13050736

Jacobs AG, Feigelson BN, Spencer JA, Tadjer MJ, Hite JK, Hobart KD, Anderson TJ. Efficient Activation and High Mobility of Ion-Implanted Silicon for Next-Generation GaN Devices. Crystals. 2023; 13(5):736. https://doi.org/10.3390/cryst13050736

Chicago/Turabian StyleJacobs, Alan G., Boris N. Feigelson, Joseph A. Spencer, Marko J. Tadjer, Jennifer K. Hite, Karl D. Hobart, and Travis J. Anderson. 2023. "Efficient Activation and High Mobility of Ion-Implanted Silicon for Next-Generation GaN Devices" Crystals 13, no. 5: 736. https://doi.org/10.3390/cryst13050736