Topology and Control Strategy of PV MVDC Grid-Connected Converter with LVRT Capability

Abstract

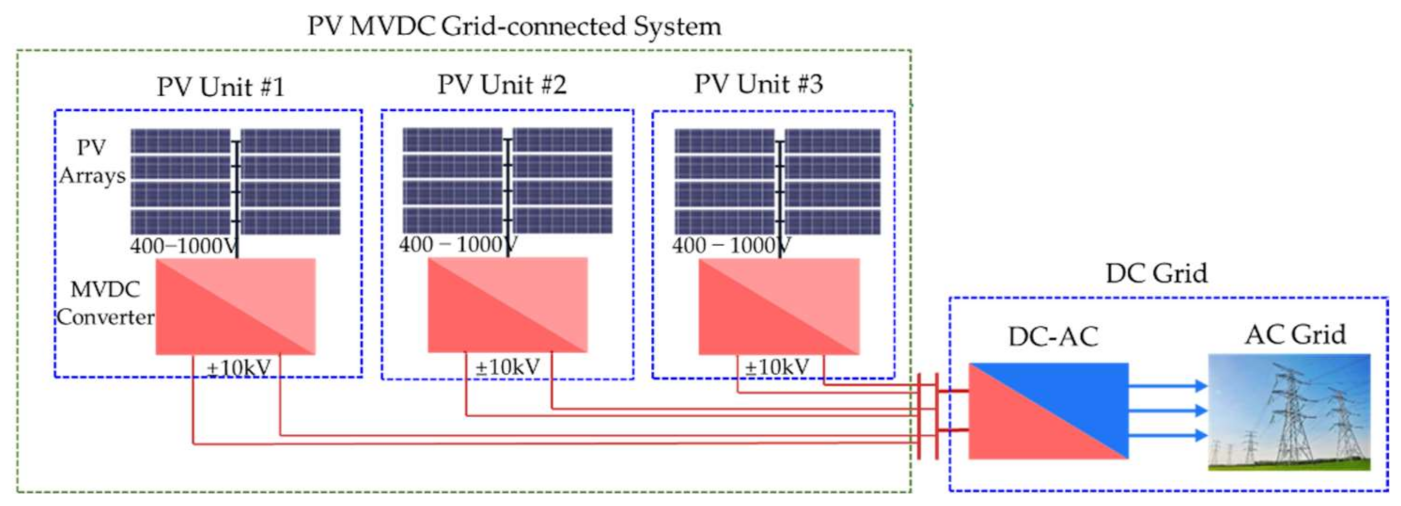

:1. Introduction

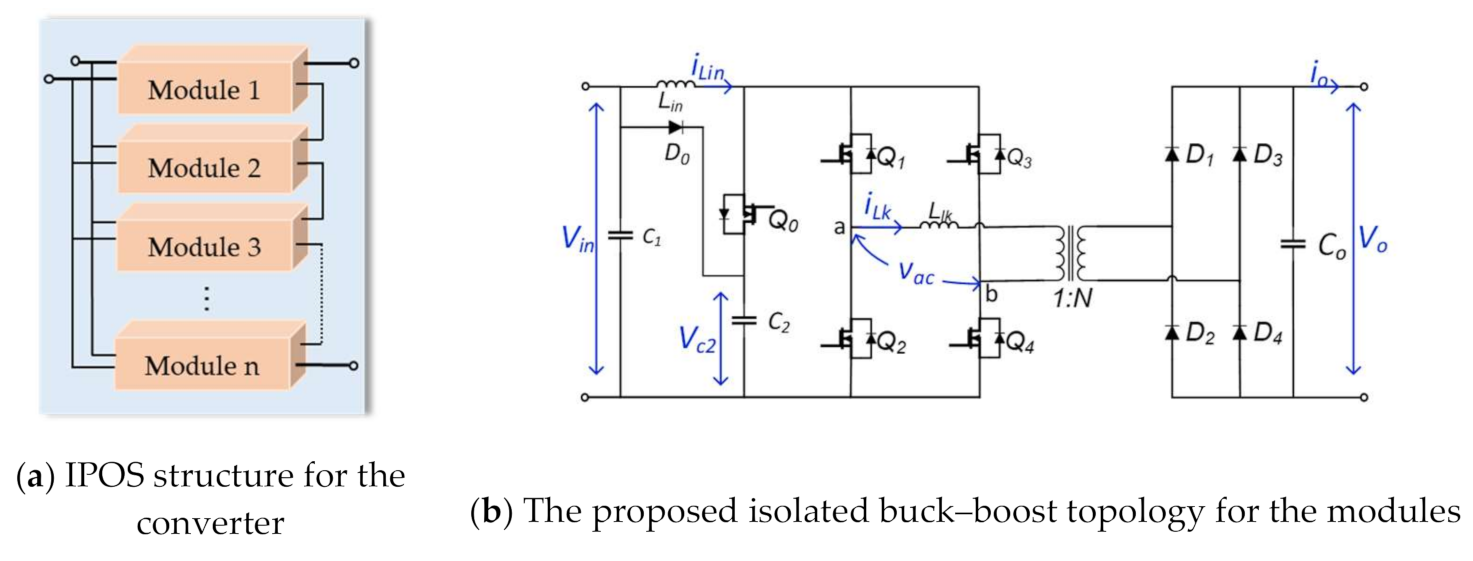

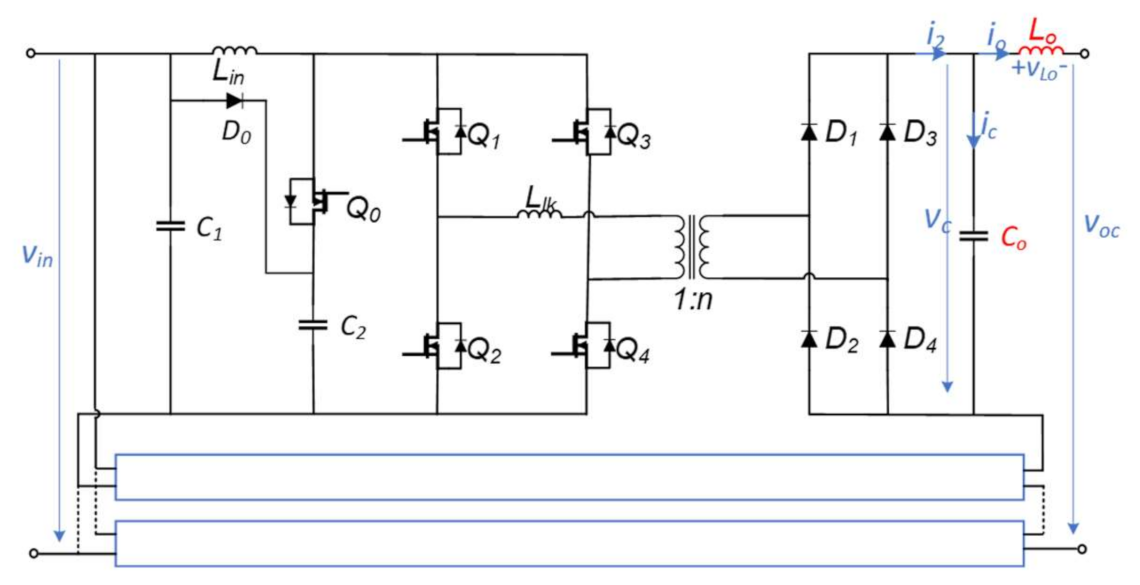

2. Principle of the Converter

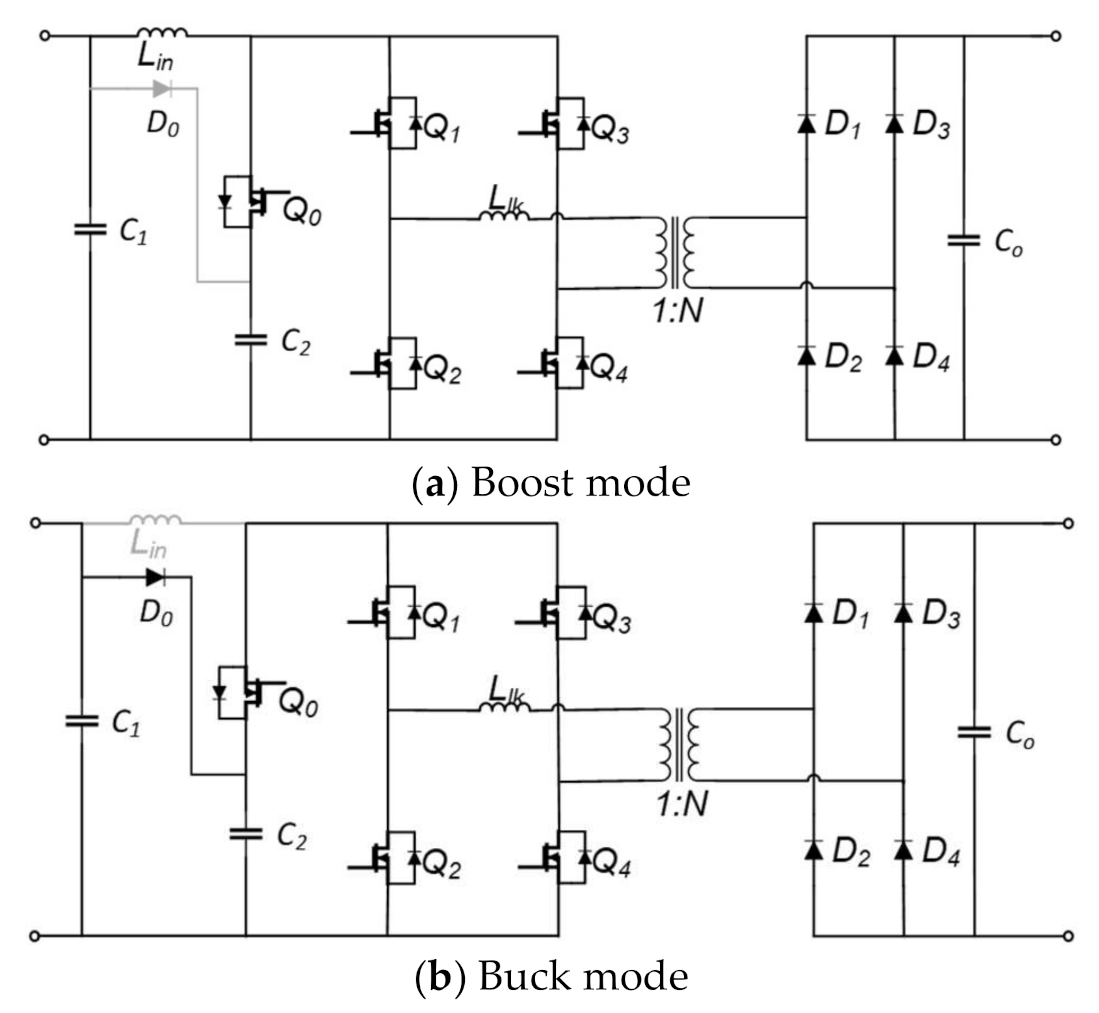

2.1. Proposed Topology

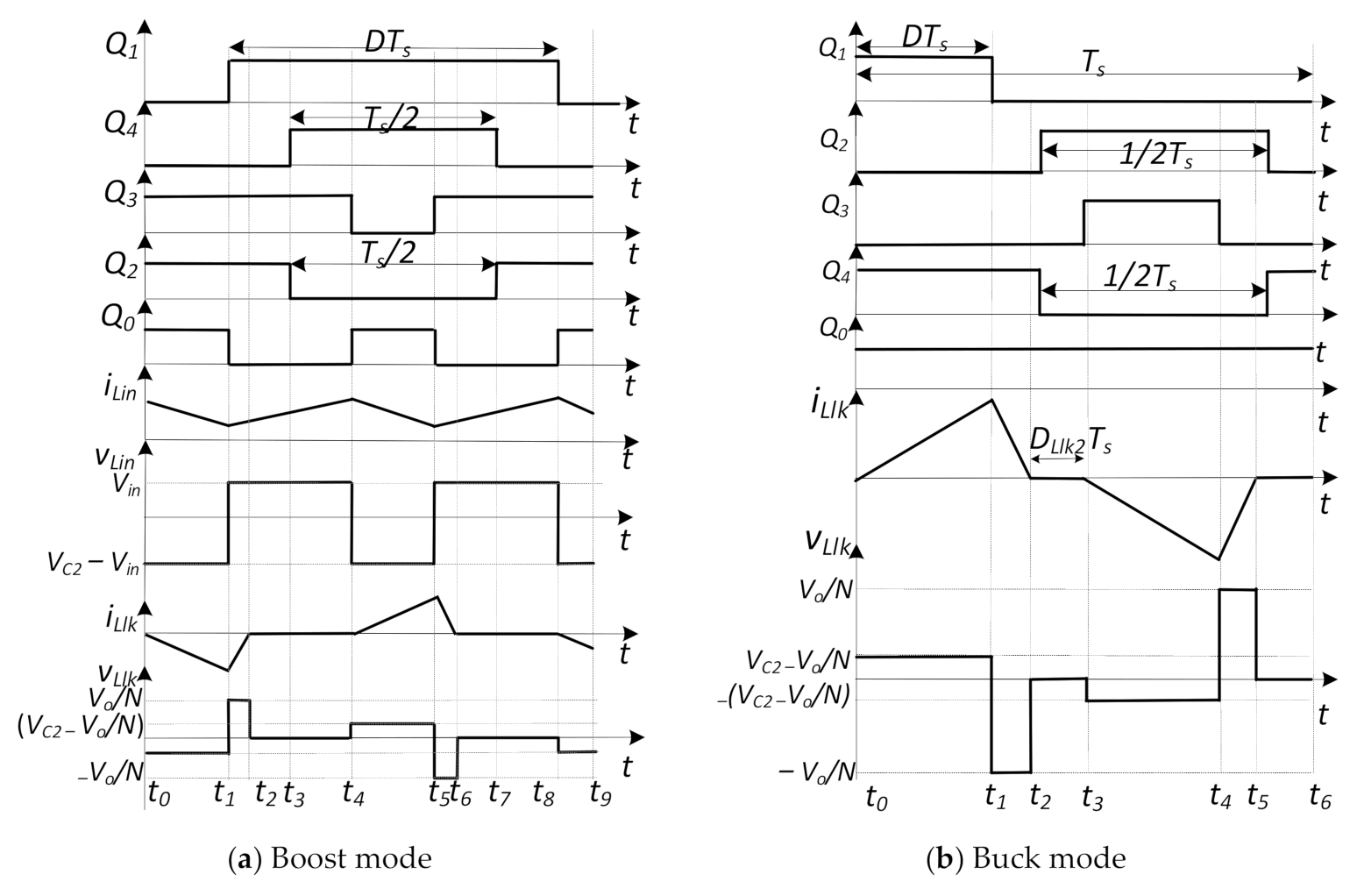

2.2. Modulation of the Proposed Topology

2.3. Derivation of Voltage Gain

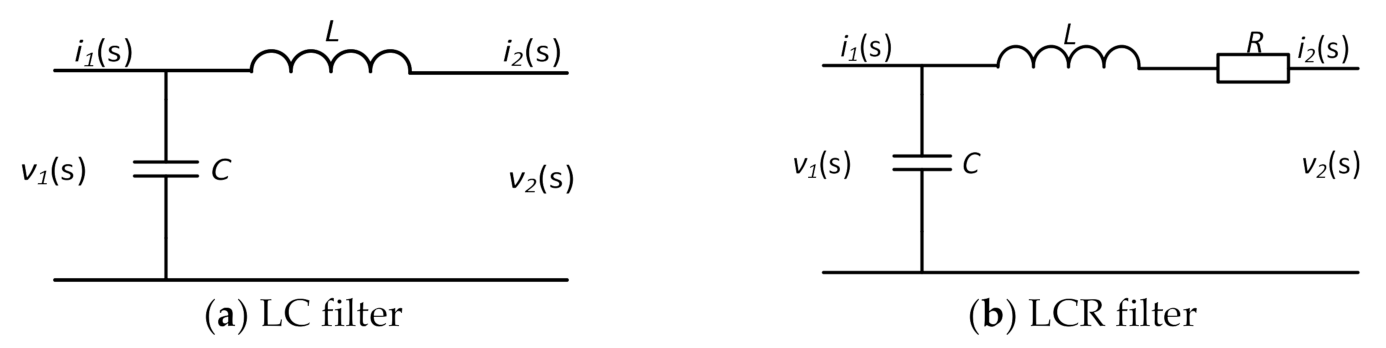

2.4. LC Filter in the Converter

2.4.1. Design of the Output Capacitor

2.4.2. Design of the Output Inductor

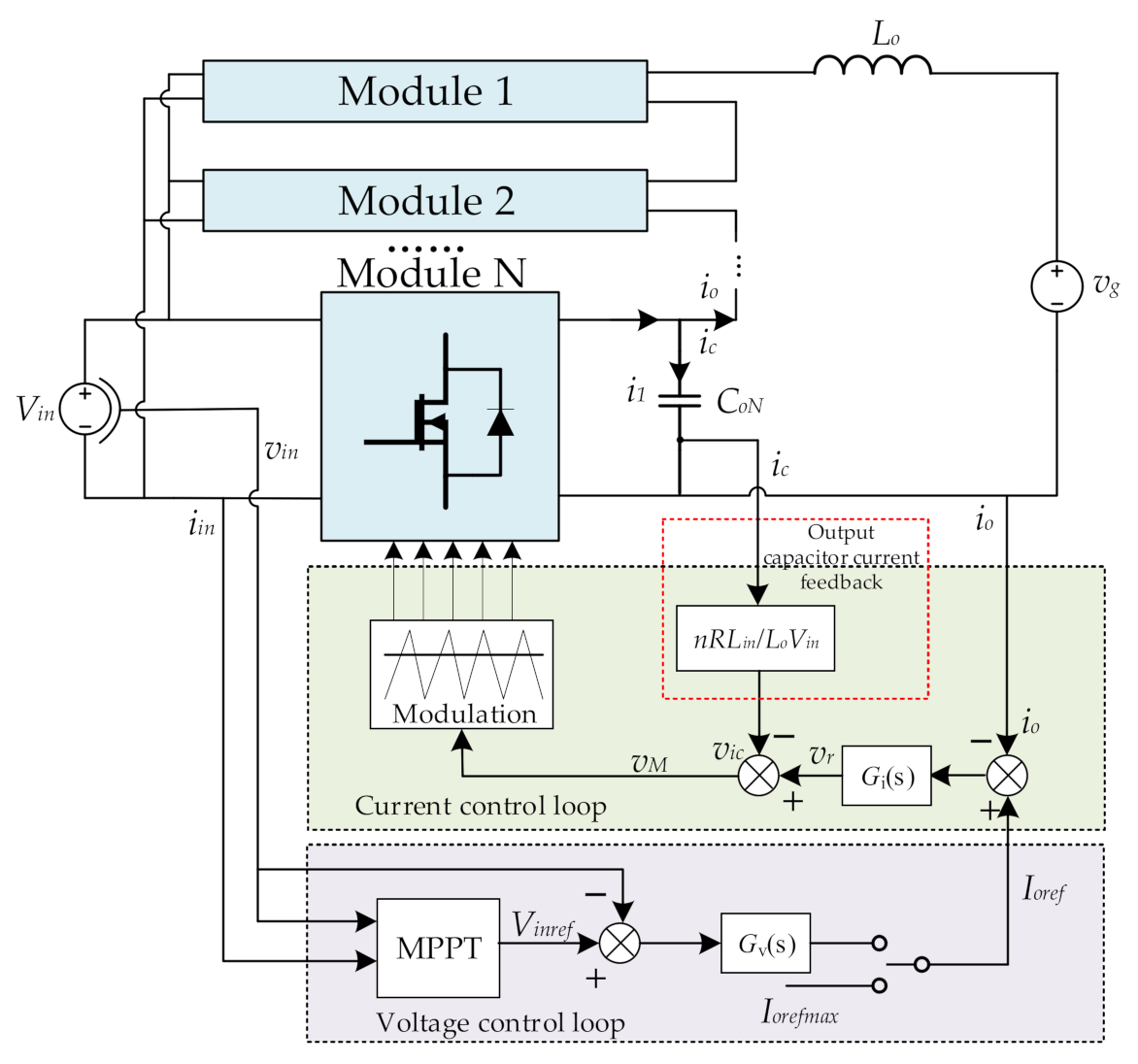

3. Control Strategy of the Converter

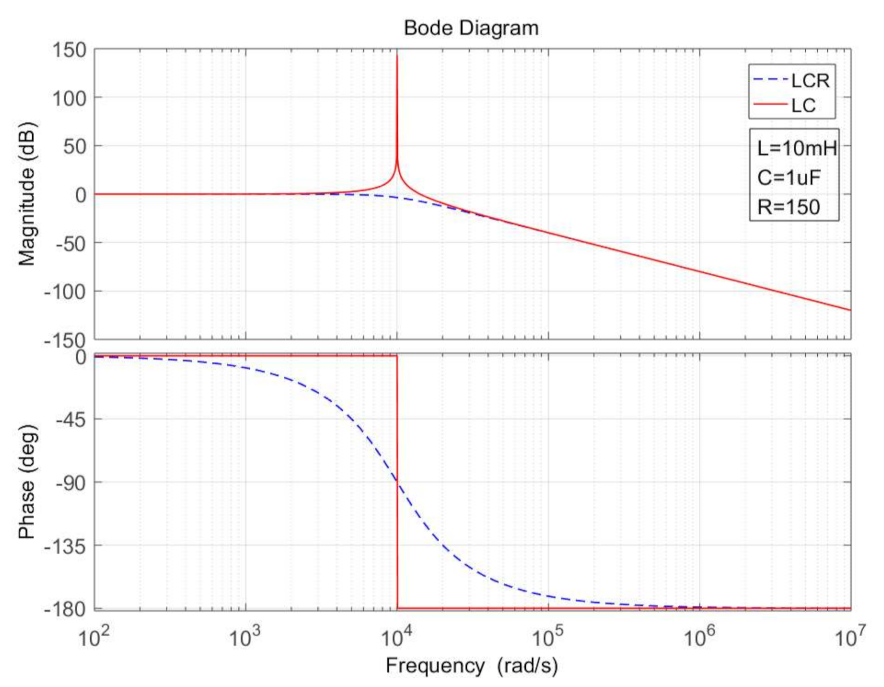

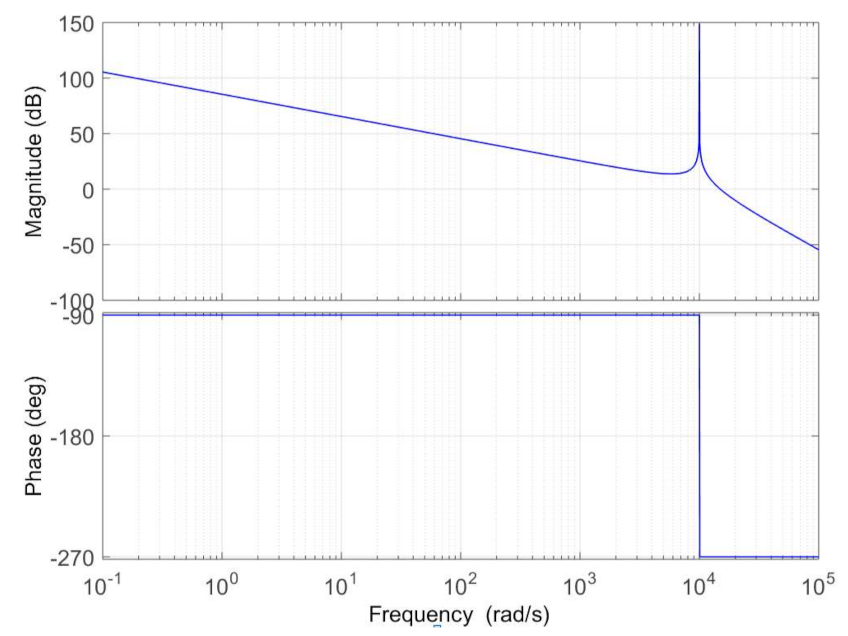

3.1. The Effect of LC Filter

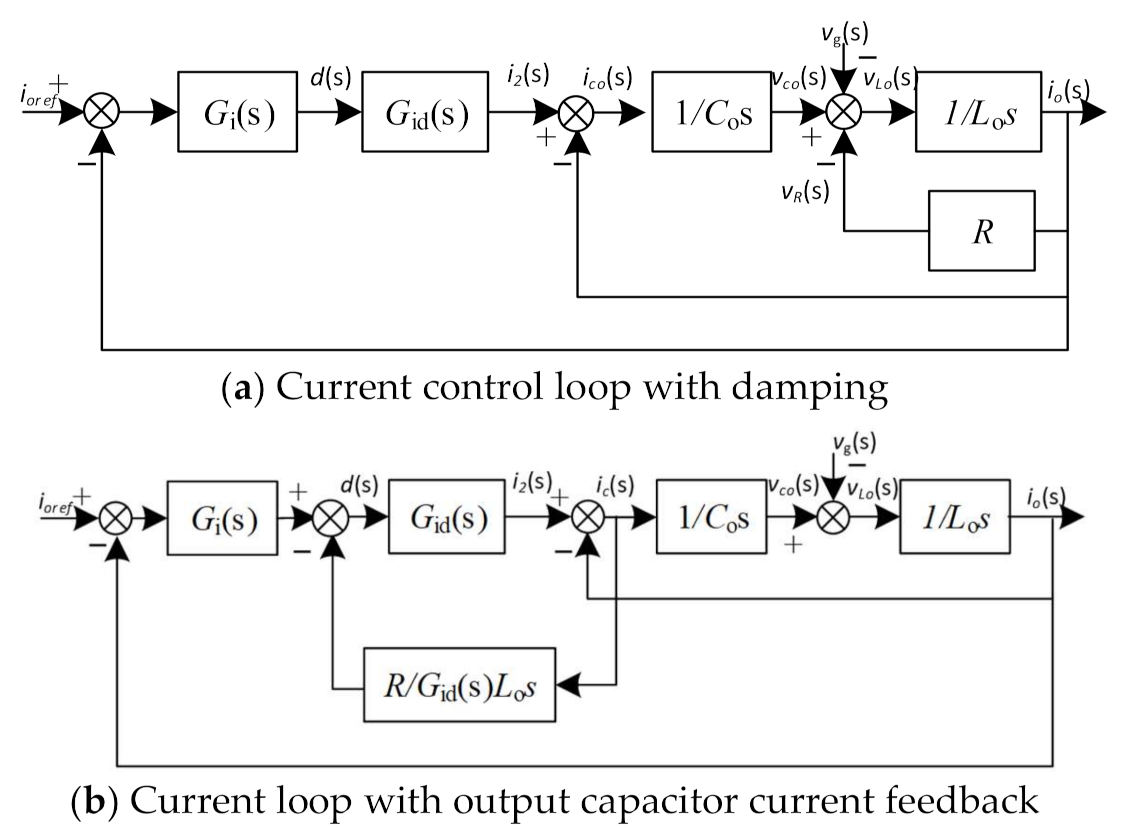

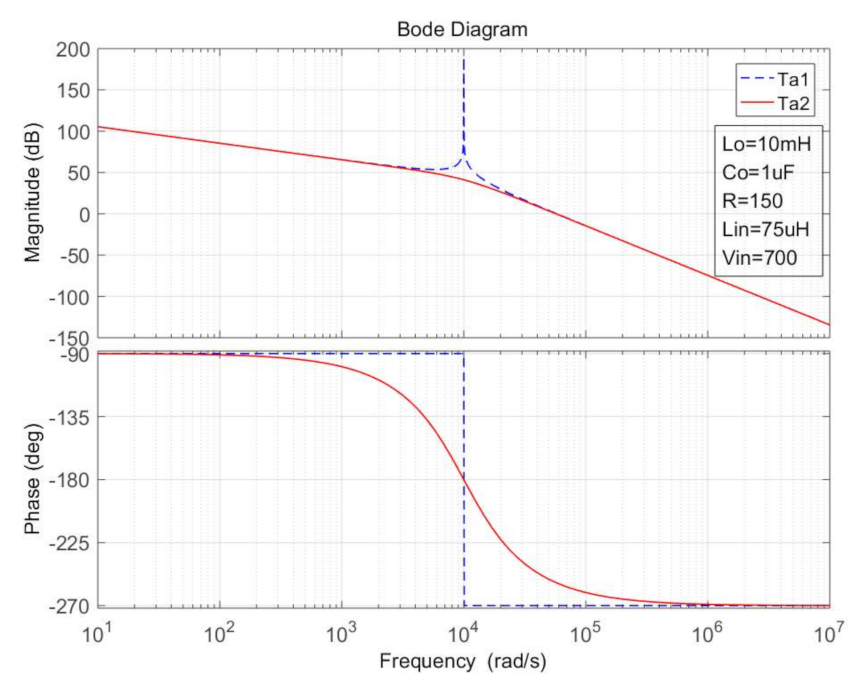

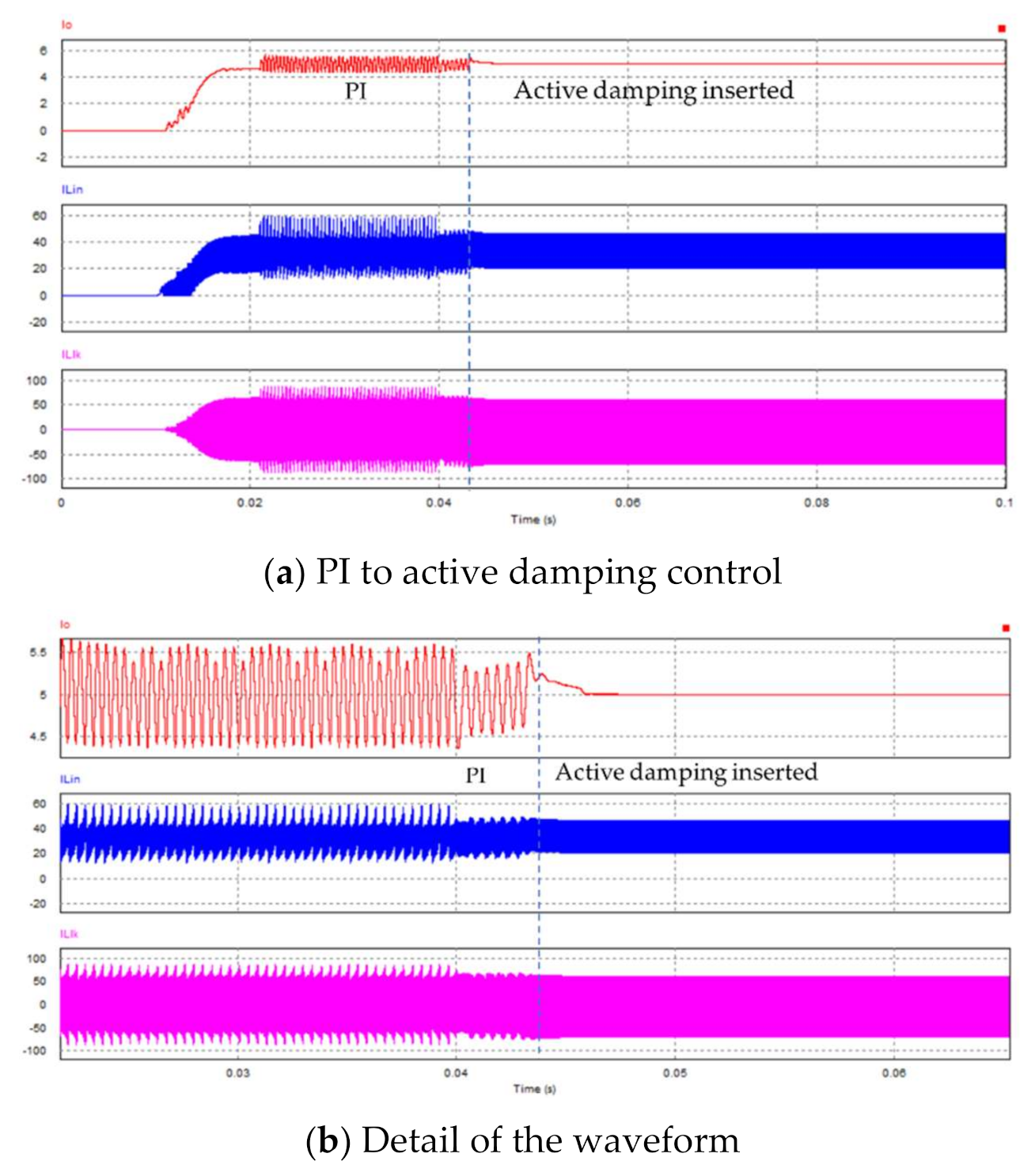

3.2. Current Control Strategy with Active Damping

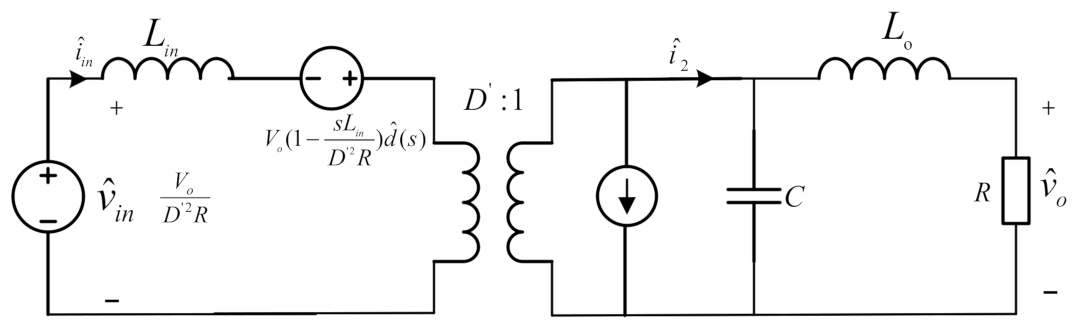

3.2.1. Model of Current Closed Loop with LC Filter

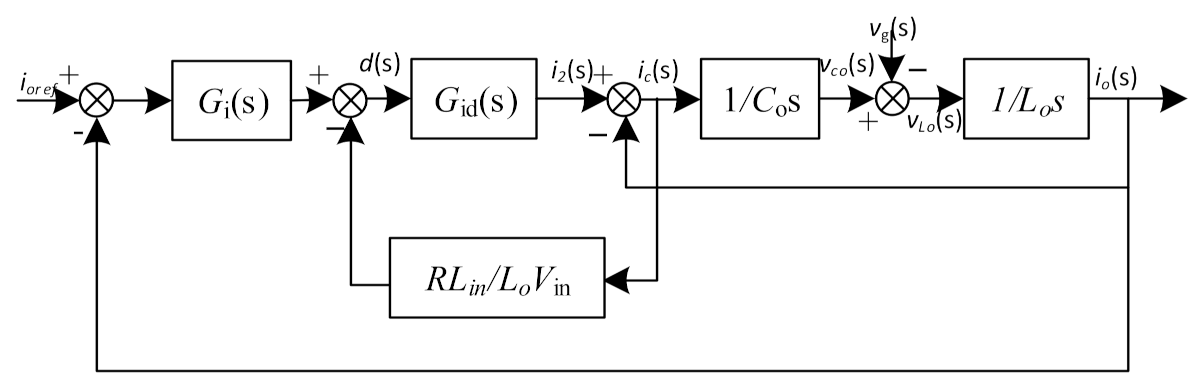

3.2.2. Adding Active Damping in the Converter

3.3. Complete Control Strategy

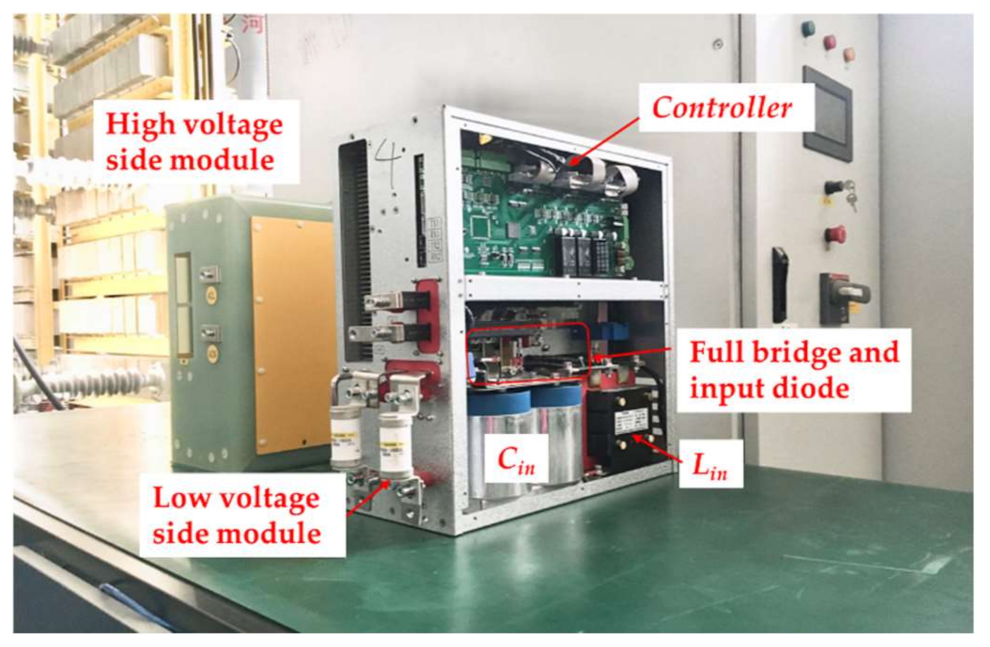

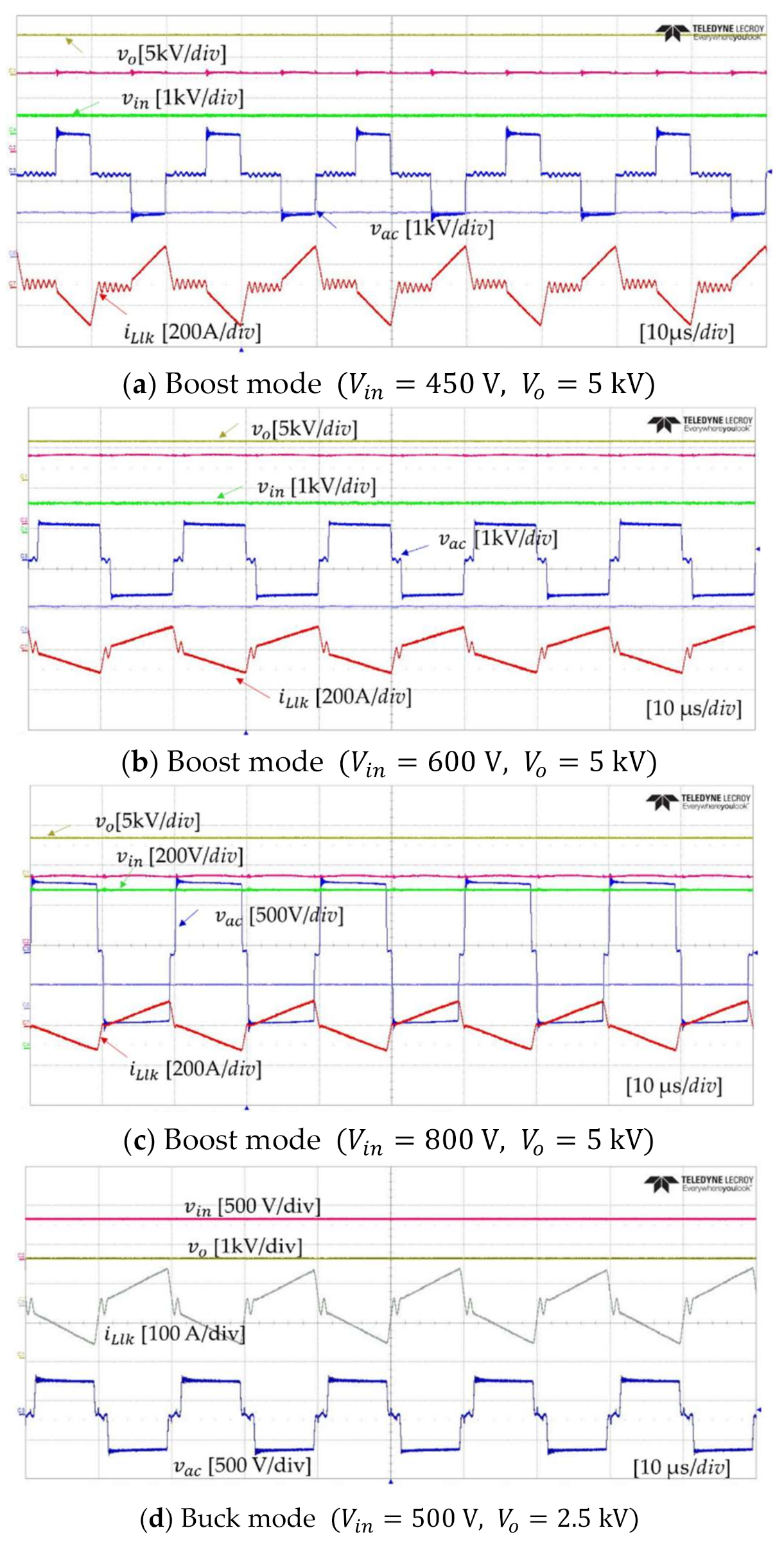

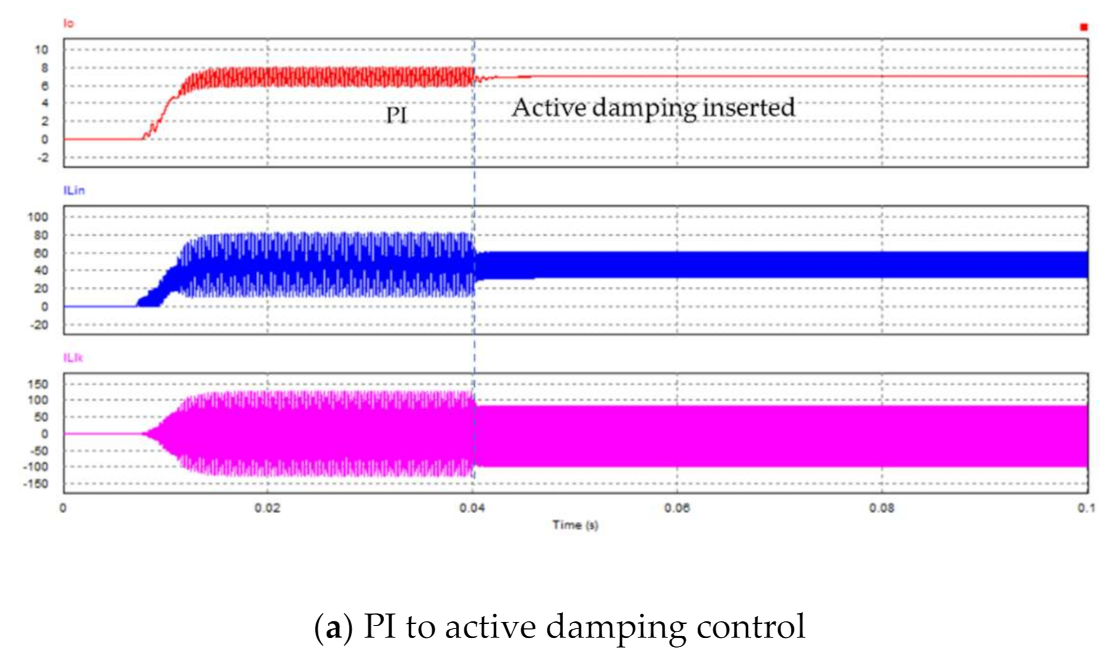

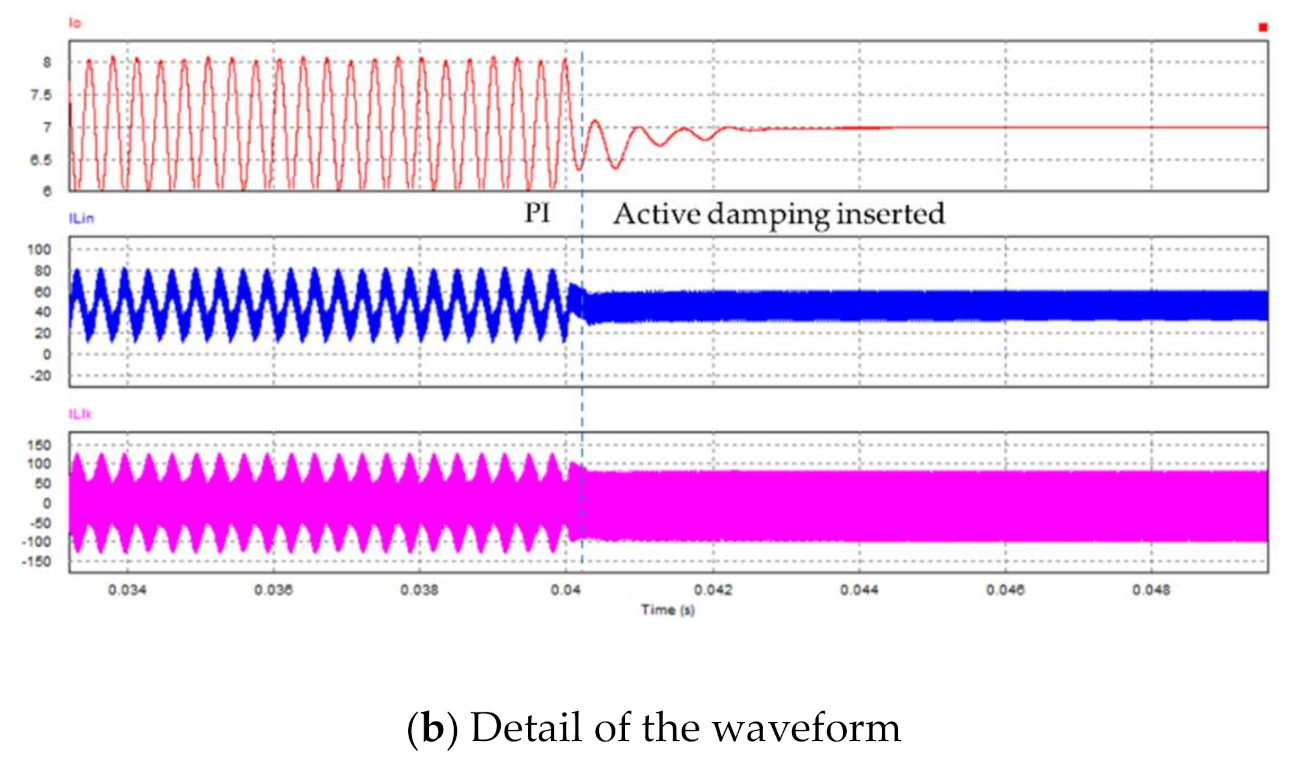

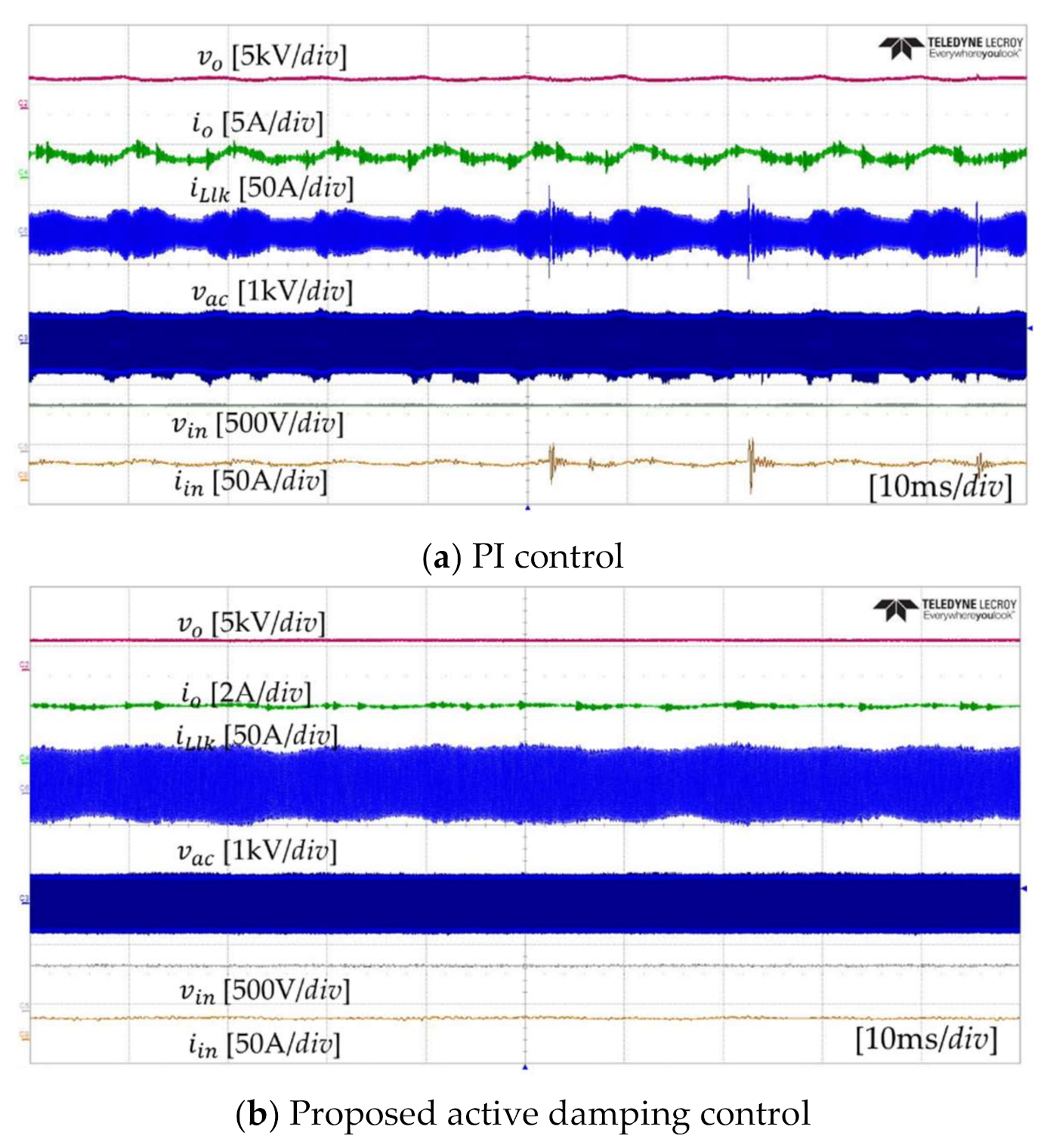

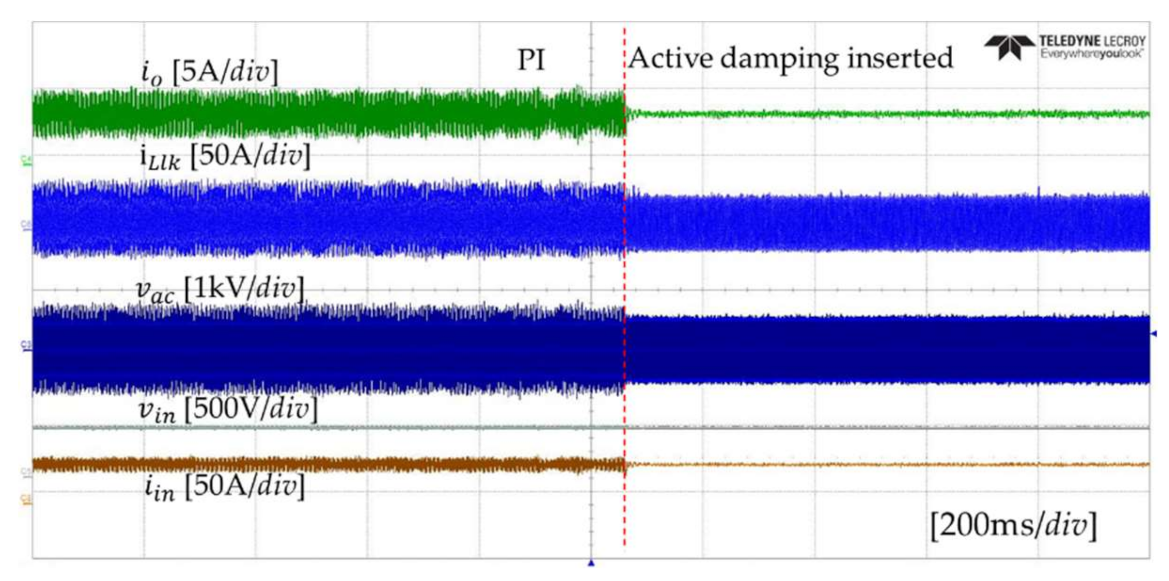

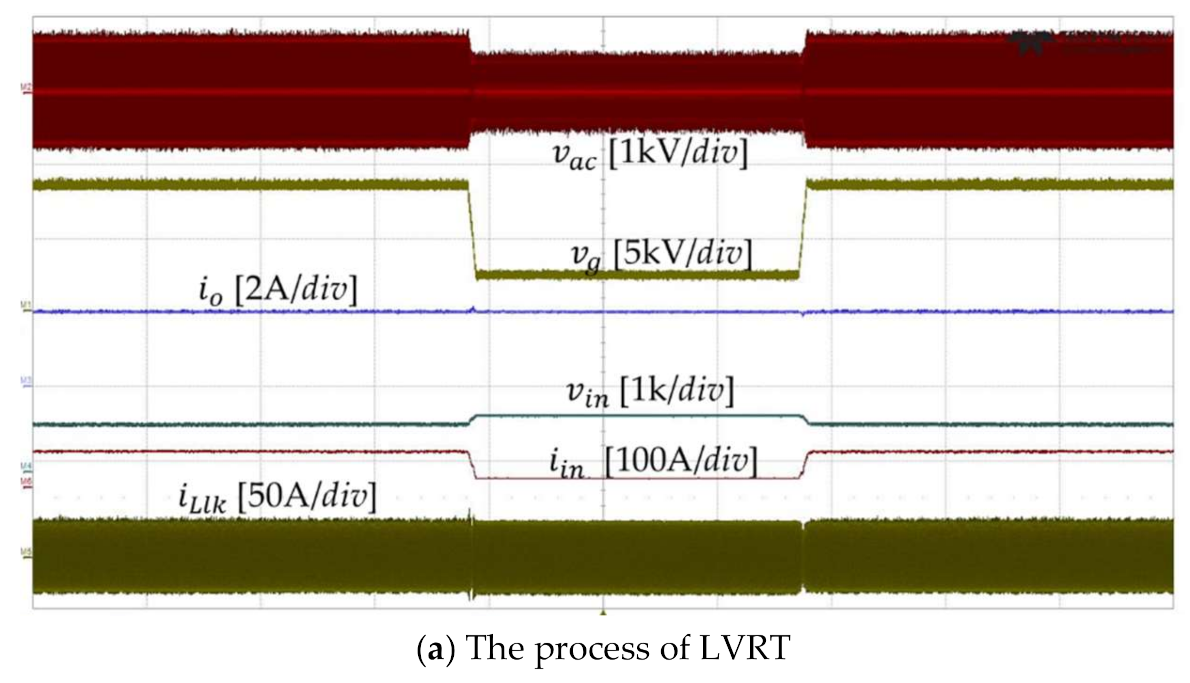

4. Simulation and Experimental Results

5. Conclusions

Author Contributions

Funding

Institutional Review Board Statement

Informed Consent Statement

Data Availability Statement

Conflicts of Interest

References

- Engel, S.P.; Stieneker, M.; Soltau, N.; Rabiee, S.; Stagge, H.; De Doncker, R.W. Comparison of the Modular Multilevel DC Converter and the Dual-Active Bridge Converter for Power Conversion in HVDC and MVDC Grids. IEEE Trans. Power Electron. 2015, 30, 124–137. [Google Scholar] [CrossRef]

- Nguyen, T.-T.; Yoo, H.-J.; Kim, H.-M. A comparison study of MVDC and MVAC for deployment of distributed wind generations. In Proceedings of the 2016 IEEE International Conference on Sustainable Energy Technologies (ICSET), Hanoi, Vietnam, 14–17 November 2016; pp. 138–141. [Google Scholar]

- Ning, G.; Chen, W. A Hybrid Resonant ZCS PWM Converter for Renewable Energy Sources Connecting to MVDC Collection System. IEEE Trans. Ind. Electron. 2018, 65, 7911–7920. [Google Scholar] [CrossRef]

- IEEE Standards Association. IEEE Recommended Practice for 1kV to 35kV Medium-Voltage DC Power System on Ship; IEEE Standard 1709; US-ANSI; IEEE: New York, NY, USA, 2010. [Google Scholar]

- Barker, C.D.; Davidson, C.D.; Trainer, D.R.; Whitehouse, R.S. Requirements of DC-DC converters to facilitate large DC grids. In Proceedings of the CIGRE Conference, Paris, France, 26–31 August 2012; pp. 1–10. [Google Scholar]

- Han, J.; Kong, X.; Li, P.; Zhang, Z.; Yin, X. A novel low voltage ride through strategy for cascaded power electronic transformer. Prot. Control. Mod. Power Syst. 2019, 4, 20. [Google Scholar] [CrossRef]

- Tafti, H.D.; Maswood, A.I.; Konstantinou, G.; Pou, J. Low-voltage ride-through capability of cascaded H-bridge multilevel converters for large-scale photovoltaic power plants. In Proceedings of the IEEE Innovative Smart Grid Technologies, Melbourne, Australia, 28 November–1 December 2016; pp. 52–57. [Google Scholar]

- Zheng, S.; Lyu, F. Compact Medium Voltage DC/DC Converter Using Series-Connected Power Devices. Electronics 2020, 9, 1024. [Google Scholar] [CrossRef]

- Wang, Y.; Song, Q.; Sun, Q.; Zhao, B.; Li, J.; Liu, W. Multilevel MVDC Link Strategy of High-Frequency-Link DC Transformer Based on Switched Capacitor for MVDC Power Distribution. IEEE Trans. Ind. Electron. 2017, 64, 2829–2835. [Google Scholar] [CrossRef]

- Wang, X.; Tang, G.; He, Z.; Wei, X. Topology Research of DC/DC Converters for Offshore Wind Farm DC Collection Systems. Proc. CSEE 2017, 37, 837–848. [Google Scholar] [CrossRef]

- Mogorovic, M.; Dujic, D. Sensitivity Analysis of Medium-Frequency Transformer Designs for Solid-State Transformers. IEEE Trans. Power Electron. 2019, 34, 8356–8367. [Google Scholar] [CrossRef]

- Zhao, B.; Yu, Q.; Sun, W. Extended-Phase-Shift Control of Isolated Bidirectional DC–DC Converter for Power Distribution in Microgrid. IEEE Trans. Power Electron. 2012, 27, 4667–4680. [Google Scholar] [CrossRef]

- Huang, X.; Wang, H.; Guo, L.; Ju, C.; Liu, R.; Meng, S.; Wang, Y.; Xu, H. Large-scale photovoltaic generation system connected to HVDC grid with centralized high voltage and high power DC/DC converter. In Proceedings of the 2017 20th International Conference on Electrical Machines and Systems (ICEMS), Sydney, Australia, 11–14 August 2017; pp. 1–6. [Google Scholar]

- Yao, C.; Ruan, X.; Wang, X.; Tse, C.K. Isolated Buck–Boost DC/DC Converters Suitable for Wide Input-Voltage Range. IEEE Trans. Power Electron. 2011, 26, 2599–2613. [Google Scholar] [CrossRef]

- Wu, F.; Fan, S.; Li, X.; Luo, S. Bidirectional Buck–Boost Current-Fed Isolated DC–DC Converter and Its Modulation. IEEE Trans. Power Electron. 2020, 35, 5506–5516. [Google Scholar] [CrossRef]

- Liu, Y.; Abu-Rub, H.; Ge, B. Front-End Isolated Quasi-Z-Source DC-DC Converter Modules in Series for High-Power PV Sys-tems—Part I: Configuration, Operation, and Evaluation. IEEE Trans. Ind. Electron. 2017, 64, 347–358. [Google Scholar] [CrossRef]

- Sun, Q.; Li, Y.; Shen, X.; Cheng, F.; Li, G.; Liang, J.; Mu, Q.; Meng, J. Analysis and Experimental Validation of Current-Fed Switched Capacitor-Based Modular DC Transformer. IEEE Trans. Ind. Inform. 2020, 16, 5137–5149. [Google Scholar] [CrossRef]

- Wu, H.; Lu, Y.; Sun, K.; Xing, Y. Phase-Shift-Controlled Isolated Buck-Boost Converter with Active-Clamped Three-Level Rectifier (AC-TLR) Featuring Soft-Switching Within Wide Operation Range. IEEE Trans. Power Electron. 2016, 31, 2372–2386. [Google Scholar] [CrossRef]

- Lu, Y.; Wu, H.; Tu, B.; Li, M.; Xia, Y.; Xing, Y. Ultra-Wide Output Voltage Range Power Supply Based on Modular Switched-Converter Principle. IEEE Trans. Power Electron. 2020, 35, 94–106. [Google Scholar] [CrossRef]

- Li, Y.; Li, F.; Zhao, F.-W.; You, X.-J.; Zhang, K.; Liang, M. Hybrid Three-Level Full-Bridge Isolated Buck–Boost Converter with Clamped Inductor for Wider Voltage Range Application. IEEE Trans. Power Electron. 2019, 34, 2923–2937. [Google Scholar] [CrossRef]

- Zhao, B.; Li, X.; Wei, Y.; An, F.; Sun, J.; Liu, G.; Zhao, Y. Modular Hybrid-Full-Bridge DC Transformer with Full-Process Matching Switching Strategy for MVdc Power Distribution Application. IEEE Trans. Ind. Electron. 2020, 67, 3317–3328. [Google Scholar] [CrossRef]

- Zhao, B.; Song, Q.; Liu, W.; Sun, Y. Overview of Dual-Active-Bridge Isolated Bidirectional DC–DC Converter for High-Frequency-Link Power-Conversion System. IEEE Trans. Power Electron. 2014, 29, 4091–4106. [Google Scholar] [CrossRef]

- Zhao, X.; Li, B.; Fu, Q.; Mao, S.; Xu, D.G.; Leon, J.I.; Franquelo, L.G. DC Solid State Transformer Based on Three-Level Power Module for Interconnecting MV and LV DC Distribution Systems. IEEE Trans. Power Electron. 2021, 36, 1563–1577. [Google Scholar] [CrossRef]

| Mode | Voltage Gain | |

|---|---|---|

| Boost | Boost-CCM1 | |

| Boost-CCM2 | ||

| Boost-DCM1 | ||

| Boost-DCM2 | ||

| Buck | Buck-CCM | |

| Buck-DCM1 | ||

| Buck-DCM2 |

| Topology | DAB | Isolated Boost | [18] | [20] | Proposed Topology | |

|---|---|---|---|---|---|---|

| High-voltage side | Switches | 4 | 0 | 2 | 2 | 0 |

| Diodes | 0 | 4 | 4 | 2 | 4 | |

| Low-voltage side | Switches | 4 | 5 | 4 | 6 | 5 |

| Diodes | 0 | 0 | 2 | 2 | 1 | |

| Number of capacitors | 2 | 3 | 6 | 4 | 3 | |

| Number of inductors | 0 | 1 | 0 | 0 | 1 | |

| Output voltage | Low | High | Medium | Medium | High | |

| Boosting capability | Low | Strong | Medium | Medium | Strong | |

| Output voltage range | Narrow | Medium | Wide | Wide | Wide | |

| Efficiency | Medium | High | Medium | High | High | |

| Parameters | Value | |

|---|---|---|

| Converter | Rated output power Pco | 200 kW |

| Rated output voltage Vco | ±10 kV | |

| Input voltage Vin | 450–850 V | |

| Number of modules | 4 | |

| Output inductor Lo | 10 mH | |

| Switching frequency fs | 50 kHz | |

| DC module | Rated power Po | 50 kW |

| Rated output voltage Vo | 5000 V | |

| Output capacitor Co | 1 uF | |

| Input inductor Lin | 75 uH | |

| Transformer ratio N | 5.8 |

| DAB | Isolated Boost | Proposed Topology | |

|---|---|---|---|

| Output voltage range | 0–2.3 kV | 2.3–5 kV | 0–5 kV |

| Input voltage | 400 V | 400 V | 400 V |

| Turn ratio | 5.8 | 5.8 | 5.8 |

| PI | Proposed Method | |

|---|---|---|

| Output voltage | 2.5 kV | 2.5 kV |

| Output current | 4 A | 4 A |

| Percent of output current ripple | 30% | 6% |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2021 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Wang, H.; Zhou, Y.; Huang, X.; Wang, Y.; Xu, H. Topology and Control Strategy of PV MVDC Grid-Connected Converter with LVRT Capability. Appl. Sci. 2021, 11, 2739. https://doi.org/10.3390/app11062739

Wang H, Zhou Y, Huang X, Wang Y, Xu H. Topology and Control Strategy of PV MVDC Grid-Connected Converter with LVRT Capability. Applied Sciences. 2021; 11(6):2739. https://doi.org/10.3390/app11062739

Chicago/Turabian StyleWang, Huan, Yu Zhou, Xinke Huang, Yibo Wang, and Honghua Xu. 2021. "Topology and Control Strategy of PV MVDC Grid-Connected Converter with LVRT Capability" Applied Sciences 11, no. 6: 2739. https://doi.org/10.3390/app11062739