2.1. Circuital Model for Evaluating the Conducted Emission

In order to provide to the designers simple and effective tools for simulating the impact of an IC on the EMC performance of a complex system made by an IC, package, and PCB, suitable equivalent circuital models have been proposed over the years. A first attempt to provide an IC circuit model was the so-called IBIS model, based on the “

Input/

output buffer information specifications”, hence, on the characterization of the electrical performance at the terminal pins of an IC [

13]. This model has the advantage of simplicity, but shows major drawbacks coming from the lack of inclusion of main phenomena, such as the switching noise and the load effect of the PCB. An enhanced circuital model for the IC conducted emission has been proposed, for instance, in [

14], based on the so-called “

linear equivalent circuit and current source” model.

More recently, the International Electrotechnical Commission proposed the so-called Integrated Circuit Emission Model (ICEM), with the purpose to accurately take into account the internal activity of the ICs [

15,

16]. The ICEM model has been successfully used over the years to carry out performance analysis of ICs, in terms of emission, immunity, jitter, and so on [

9,

17,

18]. The limitation of this model in terms of maximum operating frequencies can be easily removed, as recently shown in [

8], by taking into account the effects of the loads (specifically the transmission lines of the PCB) with a distributed model. This paper adopts the latter approach to derive a circuit model in the frame of the ICEM standard. Specifically, the high-frequency behavior of the PCB is described by exploiting its S-parameter characterization.

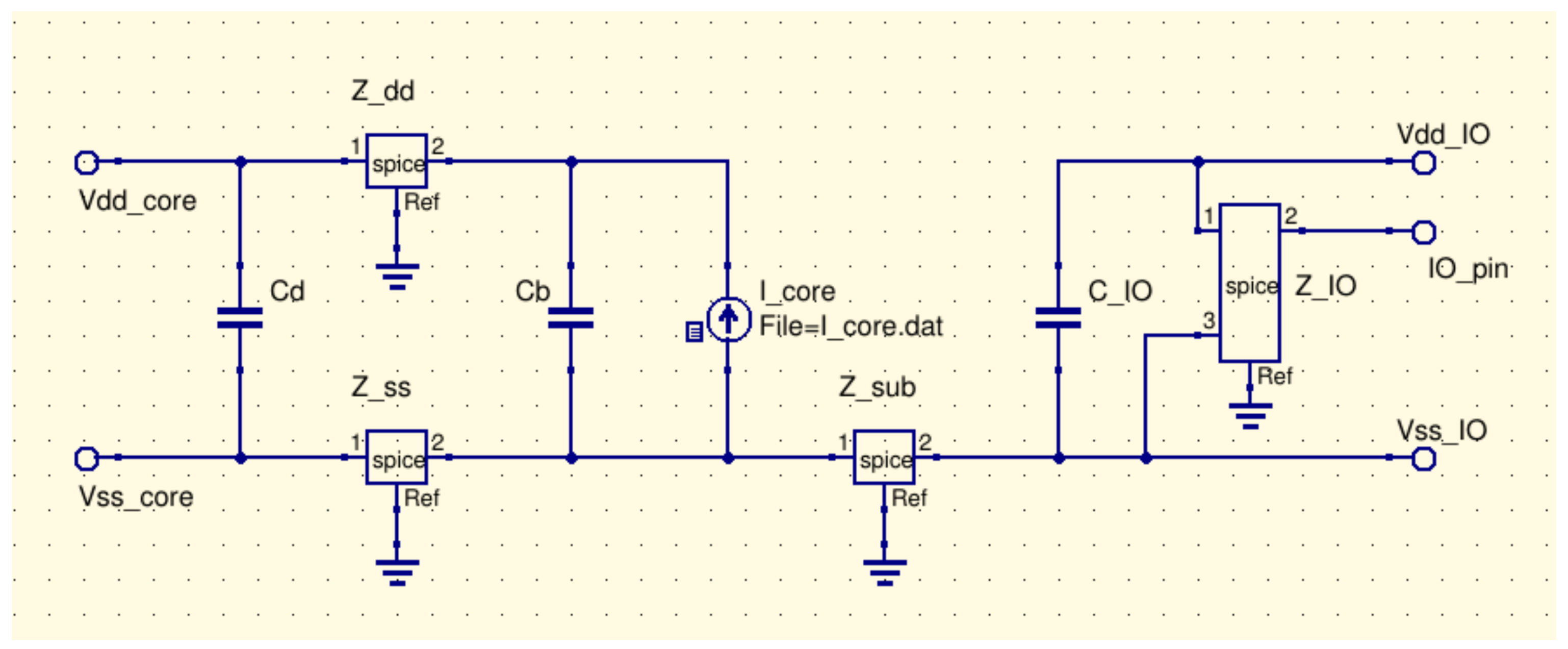

The conceptual scheme of the adopted approach is reported in

Figure 1, showing the overall circuit as composed of four main subparts: the first subpart (internal activity, IA) describes the core and the I/O buffers, the second one describes the package, whereas the third one refers to the printed circuit board (PCB). The final subpart represents a generic load that simulates a buffer that exchanges data with the IC. The above subdivision is based on the features of the circuit models to be adopted for the different subparts: for the IA the circuit is active and lumped, for the IC it is passive and lumped, whereas for the PCB it is passive and distributed.

According to the ICEM model [

16], the first subpart is modelled as in

Figure 2, where the core activity is represented by an equivalent current source

Icore, and the parasitic of the supply rails are given by series impedance R-L,

Zdd and

Zss, which also separates the decoupling into two contributions:

Cd, between

Vdd and

Vss, and

Cb, close to the current generator

Icore. The core model is coupled to the I/O buffer, which is described here by means of an IBIS model [

13]. In the IC analyzed in this paper, the core supply and the I/O supply are separated and, thus, according to the ICEM rules [

16] the coupling model must contain a substrate impedance

Zsub, and an additional decoupling capacitor

CI/O. The

Vdd and

Vss pins at the left and right side of

Figure 2 are connected to the corresponding pins of the package. Each I/O pin is connected to the corresponding signal interconnect at the package and the PCB level, as shown in the circuit model in

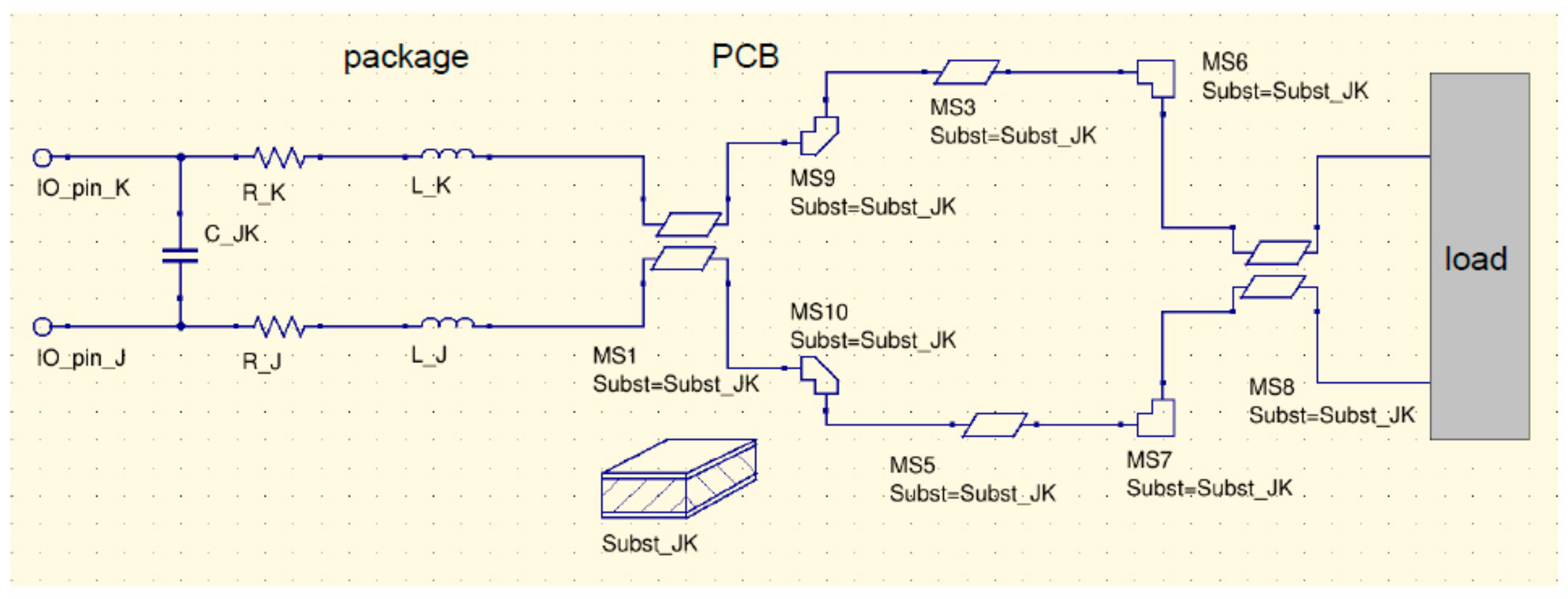

Figure 3, which also reports the parasitics for the package interconnects and the equivalent circuital models for the PCB traces.

In this paper, as specified in

Section 3, the IA circuit model has been obtained from a transistor-level simulation. Alternatively, a characterization based on measurements can be carried out, following the standards set in [

19]. The advantage of this approach is that no internal description of the IC is required, but the main disadvantages are the need to de-embed the text-fixture and the impossibility to directly measure the current

Icore. Such a current must be derived from indirect measurement of currents flowing in the board traces, by using, for instance, identification techniques like the backward current division rule, as shown in [

20]. An alternative model for the current sources is based on a harmonic decomposition, as proposed in [

8].

The subpart “package” takes into account all passive elements in the package. As described in

Figure 3, all these passives are modeled with lumped elements (RLC) and are extracted here by a quasi-static field solver. Indeed, this assumption is valid if the components are electrically short, namely:

where

is the characteristic length of the component,

v is the propagation velocity and

is the maximum frequency of the signals. Condition (1) is always verified for IC passives up to frequencies of the order of tens of GHz (mm-wavelength), since the maximum lenghts of nowadays on-chip interconnects are of the order of hundreds of microns (e.g., typical values of a global level interconnect length for 22 and 14 nm technology nodes [

1]).

Finally, the subpart “PCB” is modeled through a distributed circuit, namely an equivalent transmission line (TL). Indeed, as pointed out in [

8], the use of a distributed model for the PCB allows extending to higher frequencies (tens of GHz) the validity limit of the classical ICEM models. Specifically, this distributed subpart is here modelled in the overall circuit by means of a low-order equivalent macromodel synthezised from the PCB multiport admittance matrix,

Y. In turn, according to the TL theory [

21], such a matrix can be obtained from the scattering matrix,

S, as:

where

is a reference impedance value (usually taken as 50 Ω) and

I is the identity matrix. Indeed, the

S-parameters are the natural frame for a high-frequency characterization of a PCB, either based on full-wave simulations (as done in this paper) or on measurements. After the

Y-matrix is retrieved from Equation (2), a low-order equivalent circuit may be derived through a synthesis procedure based on the vector fitting technique, as in [

22]. Indeed, the generic entry of the admittance matrix can be expressed in terms of a truncated series of pole-residue pairs:

and the pole-residue pairs may be associated to R-L or R-C branches in the final circuit model [

22].

2.2. Electromagnetic Model for Evaluating the Radiated Emission

A main goal of this paper is the evaluation of the direct radiated emission from an IC in the far-field zone, assuming to know the currents flowing from the IC into the package. These currents are indeed the output of the circuit model developed in

Section 2.1, hence, the electromagnetic problem is cast in terms of the emission of known currents in the far-field zone. This field may be computed at a distance

r by superimposing the contribution of each current loop in the package (see

Figure 4a), if the following conditions hold [

23]:

being

the average value of the loop radius. For typical package dimensions of today’s ICs (of the order of mm × mm), Equation (4) is fulfilled for frequencies up to the order of GHz. In the same assumption, a very good approximation of a small loop is the infinitesimal loop (or the infinitesimal magnetic dipole), whose far fields (see

Figure 4b) are given in the frequency domain by [

23]:

where

I(

f) is the spectrum of the loop current,

is the intrinsic impedance, β is the wavenumber, and

A is the loop area. Note that the presence of a grounded metallic layer at the opposite side of the board where the package will be mounted can be taken into account by applying the image theorem, thus, by taking into account the contribution coming from image currents located by symmetry at opposite sides of the ground plane. In principle, vertical tracts of the package-to-board interconnects should be also taken into account if the area of the corresponding loop currents is comparable to that of the horizontal loops in

Figure 4a. However, this is not the case for the application studied in this paper, where the vertical tracts of the interconnects to the pins are much smaller in length with respect to the horizontal ones.

2.3. Experiment Design and Setup

In this paper, an IC from the 110 nm technology node has been studied, mounted on a quad-flat package. A custom test board has been specifically designed to minimize the effect of the PCB on the conducted and radiated emission, see

Figure 5. A multilayered structure has been adopted, where the package pins are directly connected to vertical vias, and then routed in inner layers. In this way, no trace is routed on the upper side of the board, so avoiding indirect radiation. The power traces (

Vdd and

Vss) are routed in different layers with respect to the signal traces, to avoid any effect of coupling between power and signal subsections. In addition, the signal traces connected to adjacent package pins are routed in different layers, in order to mitigate the high-frequency crosstalk effect. Specifically, in the board used for the conducted emission test, additional traces are routed independently to the board surface to provide contact points for the current probes. In the board used for radiated emission, addition bottom layers are included, where no signal is routed and no via is connected. The presence of blind vias and of electromagnetically-decoupled bottom layers minimize the contribution to the emitted field possibly related to parasitic cavity resonances.

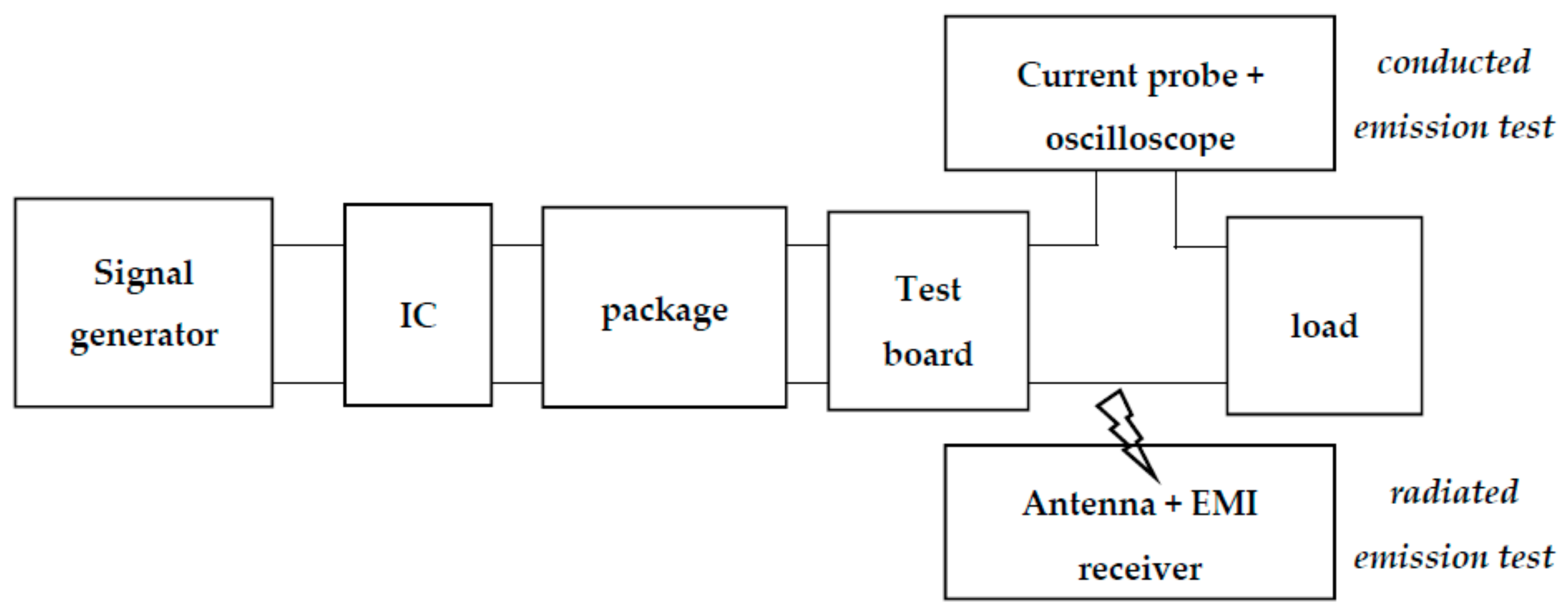

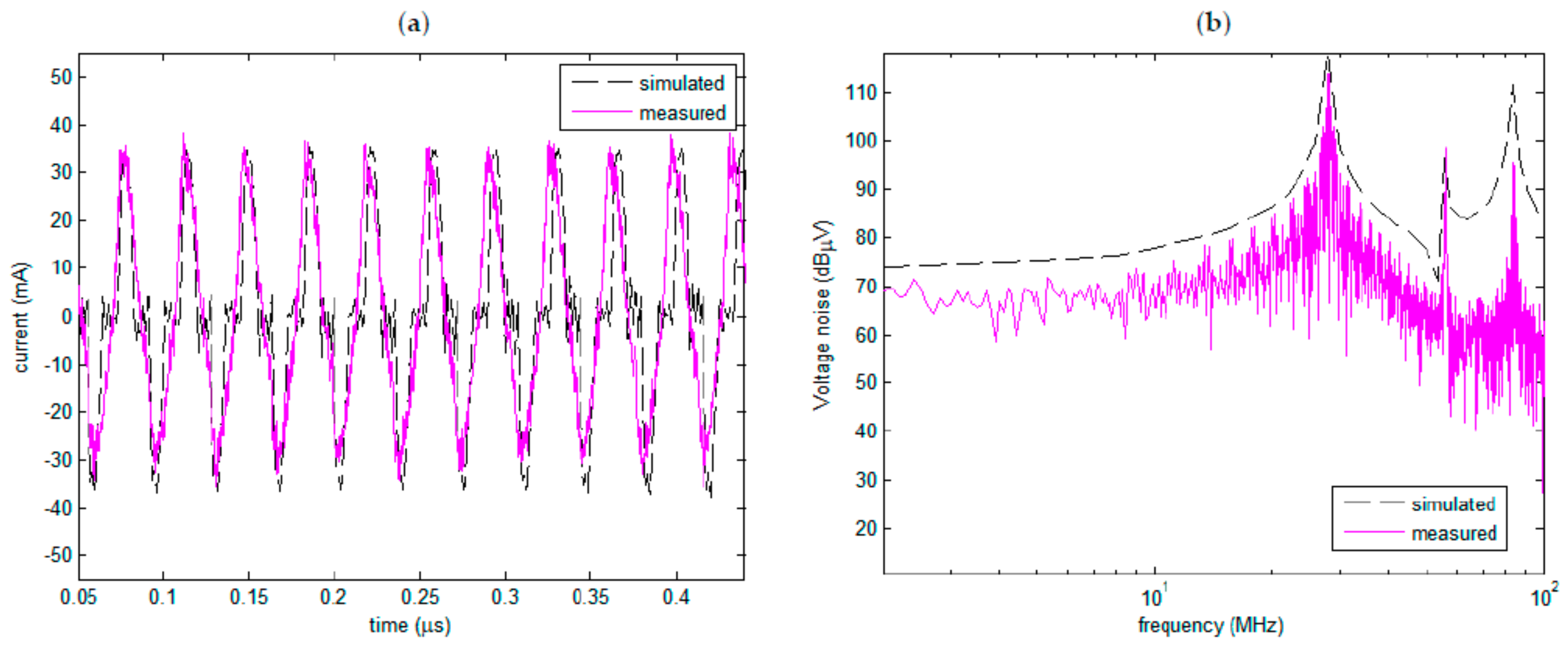

The block diagrams of the experimental setups used for evaluating the conducted and radiated emissions is schematically reported in

Figure 6. For both cases, the test board is terminated on a load simulating a buffer that exchanges data with the IC, so that the emission analysis is performed while the equipment is operating in nominal conditions, as requested by the EMC norms [

24,

25,

26]. To this end, a signal generator (Keysight, US: model N9310A, bandwidth 9 kHz–3 GHz) was connected, with an internal impedance of 50 Ω in the considered range, in parallel to a 40 pF capacitor representing a buffer. As for the conducted emission test, the currents have been acquired at the test board pads by a current probe (Lecroy D410-A-PS, bandwidth 4 GHz), then sent to an oscilloscope (LeCroy, Korea: model WavePro 7 Zi-A oscilloscope, bandwidth 6 GHz, 40 GS/s). The adopted measurement chain accounts for a maximum measurement uncertainty of ±2.5 dB on the considered frequency range.

With reference to the radiated emission test, the far-field electrical field has been collected by a broadband receiving antenna (a biconical-log antenna HL, Czech, model HL-1000, bandwidth 30 MHz–1 GHz) connected to an EMI receiver (R and S ESPC, bandwidth 9 kHz–2.5 GHz). Additionally, in this case, the maximum measurement uncertainty in the considered frequency range is ±2.5 dB. Specifically, a 3 m-radiated test was performed in a semi-anechoic chamber, according to the CISPR 16-4 standards for the radiated emission, in the frequency range from 30 MHz to 1 GHz [

25]. A preliminary measurement with the device off has been performed to estimate the background noise and remove it from the results. The device under test was made by the IC mounted in its test board, connected to a signal generator through shielded cables, to avoid unwanted emission from interconnects.