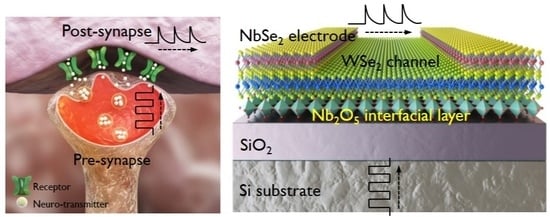

Artificial 2D van der Waals Synapse Devices via Interfacial Engineering for Neuromorphic Systems

Abstract

:1. Introduction

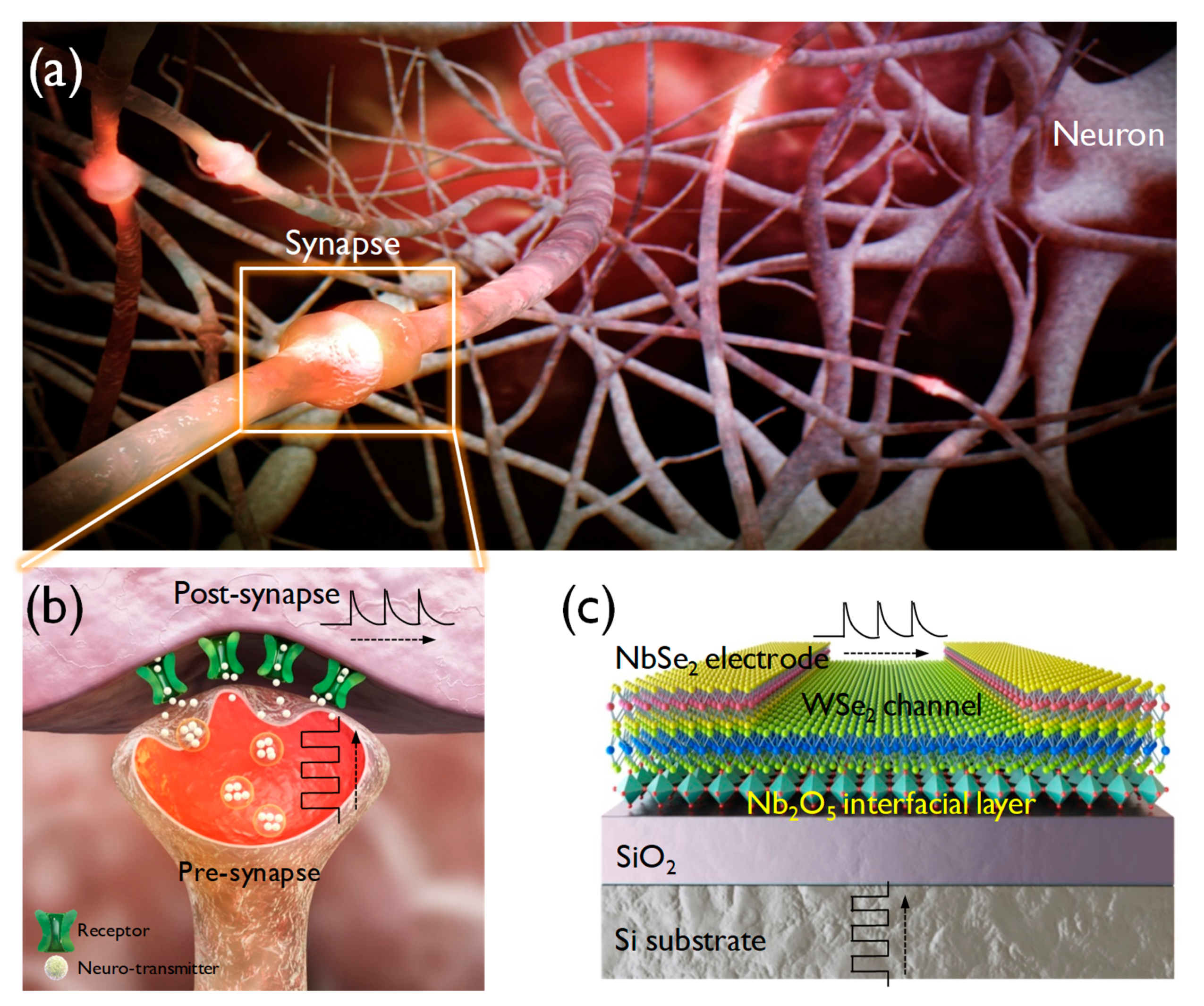

2. Materials and Methods

2.1. CVD Synthesis of WSe2 and NbSe2

2.2. Fabrication of 3-Terminal Synapse Device

2.3. Electrical Characterization

3. Results and Discussion

4. Conclusions

Supplementary Materials

Author Contributions

Funding

Conflicts of Interest

References

- Kim, S.; Yoon, J.; Kim, H.D.; Choi, S.J. Carbon Nanotube Synaptic Transistor Network for Pattern Recognition. ACS Appl. Mater. Interfaces 2015, 7, 25479–25486. [Google Scholar] [CrossRef]

- Fuller, E.J.; Gabaly, F.E.; Léonard, F.; Agarwal, S.; Plimpton, S.J.; Jacobs-Gedrim, R.B.; James, C.D.; Marinella, M.J.; Talin, A.A. Li-Ion Synaptic Transistor for Low Power Analog Computing. Adv. Mater. 2017, 29, 1604310. [Google Scholar] [CrossRef] [PubMed]

- Van De Burgt, Y.; Lubberman, E.; Fuller, E.J.; Keene, S.T.; Faria, G.C.; Agarwal, S.; Marinella, M.J.; Alec Talin, A.; Salleo, A. A non-volatile organic electrochemical device as a low-voltage artificial synapse for neuromorphic computing. Nat. Mater. 2017, 16, 414–418. [Google Scholar] [CrossRef] [PubMed]

- Choi, S.; Tan, S.H.; Li, Z.; Kim, Y.; Choi, C.; Chen, P.Y.; Yeon, H.; Yu, S.; Kim, J. SiGe epitaxial memory for neuromorphic computing with reproducible high performance based on engineered dislocations. Nat. Mater. 2018, 17, 335–340. [Google Scholar] [CrossRef] [PubMed]

- Kim, H.; Hwang, S.; Park, J.; Park, B.G. Silicon synaptic transistor for hardware-based spiking neural network and neuromorphic system. Nanotechnology 2017, 28, 405202. [Google Scholar] [CrossRef] [PubMed]

- Cao, Q.L.; Yan, X.X.; Luo, X.G.; Garey, L.J. Prenatal development of parvalbumin immunoreactivity in the human striate cortex. Cereb. Cortex 1996, 6, 620–630. [Google Scholar] [CrossRef] [PubMed] [Green Version]

- Li, G.L.; Keen, E.; Andor-Ardó, D.; Hudspeth, A.J.; Von Gersdorff, H. The unitary event underlying multiquantal EPSCs at a hair cell’s ribbon synapse. J. Neurosci. 2009, 29, 7558–7568. [Google Scholar] [CrossRef]

- Kauer, J.A.; Malenka, R.C. Synaptic plasticity and addiction. Nat. Rev. Neurosci. 2007, 8, 844–858. [Google Scholar] [CrossRef]

- Shi, R.Z.; Horiuchi, T. A summating, exponentially-decaying CMOS synapse for spiking neural systems. In Proceedings of the Advances in Neural Information Processing Systems. Proc. Adv. Neural Inf. Process. Syst. 2004, 16, 1003–1010. [Google Scholar]

- Merolla, P.A.; Arthur, J.V.; Alvarez-icaza, R.; Cassidy, A.S.; Sawada, J.; Akopyan, F.; Jackson, B.L.; Imam, N.; Guo, C.; Nakamura, Y.; et al. A million spiking-neuron integrated circuit with a scalable communication network and interface. Science 2014, 345, 668–673. [Google Scholar] [CrossRef]

- Frenkel, C.; Lefebvre, M.; Legat, J.D.; Bol, D. A 0.086-mm2 12.7-pJ/SOP 64k-Synapse 256-Neuron Online-Learning Digital Spiking Neuromorphic Processor in 28-nm CMOS. IEEE Trans. Biomed. Circuits Syst. 2019, 13, 145–158. [Google Scholar] [PubMed] [Green Version]

- Kim, S.; Choi, B.; Lim, M.; Yoon, J.; Lee, J.; Kim, H.D.; Choi, S.J. Pattern Recognition Using Carbon Nanotube Synaptic Transistors with an Adjustable Weight Update Protocol. ACS Nano 2017, 11, 2814–2822. [Google Scholar] [CrossRef] [PubMed]

- Shi, J.; Ha, S.D.; Zhou, Y.; Schoofs, F.; Ramanathan, S. A correlated nickelate synaptic transistor. Nat. Commun. 2013, 4, 2676. [Google Scholar] [CrossRef] [PubMed] [Green Version]

- Pillai, P.B.; De Souza, M.M. Nanoionics-based three-terminal synaptic device using zinc oxide. ACS Appl. Mater. Interfaces 2017, 9, 1609–1618. [Google Scholar] [CrossRef]

- Shao, F.; Yang, Y.; Zhu, L.Q.; Feng, P.; Wan, Q. Oxide-based Synaptic Transistors Gated by Sol-Gel Silica Electrolytes. ACS Appl. Mater. Interfaces 2016, 8, 3050–3055. [Google Scholar] [CrossRef]

- Radisavljevic, B.; Radenovic, A.; Brivio, J.; Giacometti, V.; Kis, A. Single-layer MoS2 transistors. Nat. Nanotechnol. 2011, 6, 147–150. [Google Scholar] [CrossRef]

- Yin, Z.; Li, H.; Li, H.; Jiang, L.; Shi, Y.; Sun, Y.; Lu, G.; Zhang, Q.; Chen, X.; Zhang, H. Single-Layer MoS2 Phototransistors. ACS Nano 2012, 6, 74–80. [Google Scholar] [CrossRef] [Green Version]

- Bertolazzi, S.; Brivio, J.; Kis, A. Stretching and breaking of ultrathin MoS2. ACS Nano 2011, 5, 9703–9709. [Google Scholar] [CrossRef]

- Salvatore, G.A.; Münzenrieder, N.; Barraud, C.; Petti, L.; Zysset, C.; Büthe, L.; Ensslin, K.; Tröster, G. Fabrication and transfer of flexible few-layers MoS2 thin film transistors to any arbitrary substrate. ACS Nano 2013, 7, 8809–8815. [Google Scholar] [CrossRef]

- Zhu, J.; Yang, Y.; Jia, R.; Liang, Z.; Zhu, W.; Rehman, Z.U.; Bao, L.; Zhang, X.; Cai, Y.; Song, L.; et al. Ion Gated Synaptic Transistors Based on 2D van der Waals Crystals with Tunable Diffusive Dynamics. Adv. Mater. 2018, 30, 1800195. [Google Scholar] [CrossRef]

- Sangwan, V.K.; Lee, H.S.; Bergeron, H.; Balla, I.; Beck, M.E.; Chen, K.S.; Hersam, M.C. Multi-terminal memtransistors from polycrystalline monolayer molybdenum disulfide. Nature 2018, 554, 500–504. [Google Scholar] [CrossRef] [PubMed]

- Suri, M.; Bichler, O.; Hubert, Q.; Perniola, L.; Sousa, V.; Jahan, C.; Vuillaume, D.; Gamrat, C.; Desalvo, B. Addition of HfO2 interface layer for improved synaptic performance of phase change memory (PCM) devices. Solid-State Electron. 2013, 79, 227–232. [Google Scholar] [CrossRef]

- Deswal, S.; Kumar, A.; Kumar, A. NbOx based memristor as artificial synapse emulating short term plasticity. AIP Adv. 2019, 9, 095022. [Google Scholar] [CrossRef]

- Kim, A.R.; Kim, Y.; Nam, J.; Chung, H.S.; Kim, D.J.; Kwon, J.D.; Park, S.W.; Park, J.; Choi, S.Y.; Lee, B.H.; et al. Alloyed 2D Metal-Semiconductor Atomic Layer Junctions. Nano Lett. 2016, 16, 1890–1895. [Google Scholar] [CrossRef]

- Kim, Y.; Kim, A.R.; Yang, J.H.; Chang, K.E.; Kwon, J.D.; Choi, S.Y.; Park, J.; Lee, K.E.; Kim, D.H.; Choi, S.M.; et al. Alloyed 2D Metal-Semiconductor Heterojunctions: Origin of Interface States Reduction and Schottky Barrier Lowering. Nano Lett. 2016, 16, 5928–5933. [Google Scholar] [CrossRef]

- Wang, J.C.; Kao, C.H.; Wu, C.H.; Lin, C.F.; Lin, C.J. Nb2O5 and Ti-doped Nb2O5 charge trapping nano-layers applied in flash memory. Nanomaterials 2018, 8, 799. [Google Scholar] [CrossRef] [Green Version]

- Ang, Y.S.; Yang, H.Y.; Ang, L.K. Universal Scaling Laws in Schottky Heterostructures Based on Two-Dimensional Materials. Phys. Rev. Lett. 2018, 121, 56802. [Google Scholar] [CrossRef] [Green Version]

- Zhou, J.; Wan, C.; Zhu, L.; Shi, Y.; Wan, Q. Synaptic behaviors mimicked in flexible oxide-based transistors on plastic substrates. IEEE Electron Device Lett. 2013, 34, 1433–1435. [Google Scholar] [CrossRef]

- John, R.A.; Ko, J.; Kulkarni, M.R.; Tiwari, N.; Chien, N.A.; Ing, N.G.; Leong, W.L.; Mathews, N. Flexible Ionic-Electronic Hybrid Oxide Synaptic TFTs with Programmable Dynamic Plasticity for Brain-Inspired Neuromorphic Computing. Small 2017, 13, 15–23. [Google Scholar] [CrossRef]

- Sun, L.; Zhang, Y.; Hwang, G.; Jiang, J.; Kim, D.; Eshete, Y.A.; Zhao, R.; Yang, H. Synaptic Computation Enabled by Joule Heating of Single-Layered Semiconductors for Sound Localization. Nano Lett. 2018, 18, 3229–3234. [Google Scholar] [CrossRef]

© 2020 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Park, W.; Jang, H.Y.; Nam, J.H.; Kwon, J.-D.; Cho, B.; Kim, Y. Artificial 2D van der Waals Synapse Devices via Interfacial Engineering for Neuromorphic Systems. Nanomaterials 2020, 10, 88. https://doi.org/10.3390/nano10010088

Park W, Jang HY, Nam JH, Kwon J-D, Cho B, Kim Y. Artificial 2D van der Waals Synapse Devices via Interfacial Engineering for Neuromorphic Systems. Nanomaterials. 2020; 10(1):88. https://doi.org/10.3390/nano10010088

Chicago/Turabian StylePark, Woojin, Hye Yeon Jang, Jae Hyeon Nam, Jung-Dae Kwon, Byungjin Cho, and Yonghun Kim. 2020. "Artificial 2D van der Waals Synapse Devices via Interfacial Engineering for Neuromorphic Systems" Nanomaterials 10, no. 1: 88. https://doi.org/10.3390/nano10010088