TiCl4 Barrier Process Engineering in Semiconductor Manufacturing

Abstract

:1. Introduction

2. Experimental Section

3. Results and Discussion

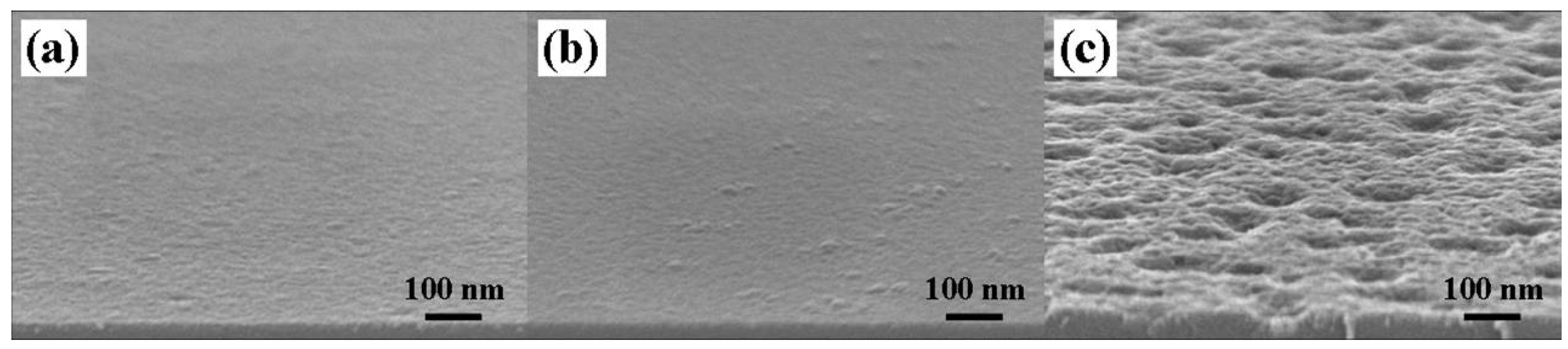

3.1. PECVD TiCl4-Based Ti Process

3.2. Impurity Analysis of TiN

| Case | TiN Type | Cycle Count | Process Temperature | Normalized Cl Concentration |

|---|---|---|---|---|

| A | Conventional HSC | NA | STD | 236.28 |

| B | SFD | Multi | STD | 100 |

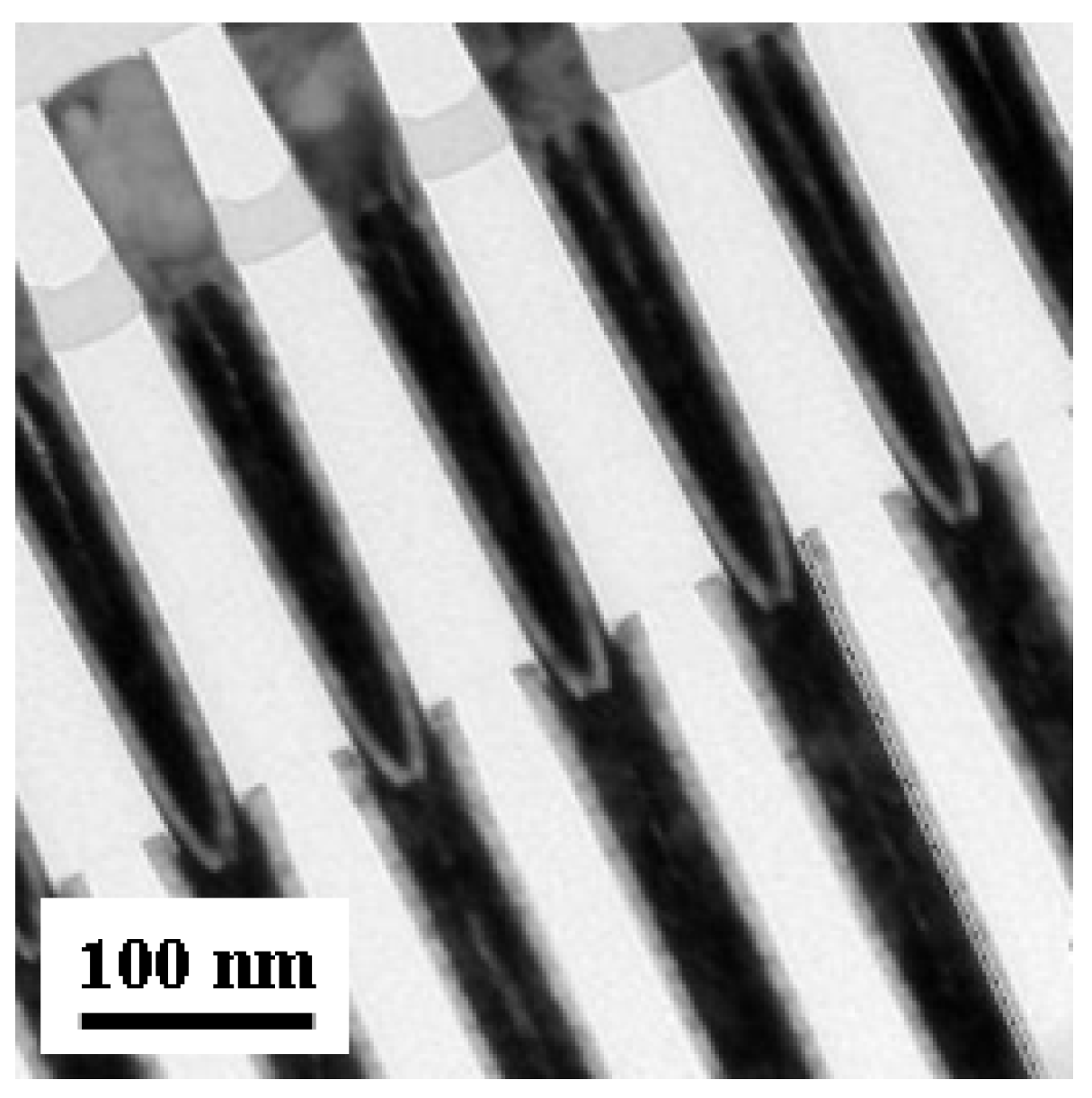

3.3. Excellent Step Coverage Requirement for High Aspect Ratio Deep Contact

3.4. Erase Performance Improvement by TiN Metal Gate

4. Conclusions

Author Contributions

Conflicts of Interest

References

- Santecchia, E.; Hamouda, A.M.S.; Musharavati, F.; Zalnezhad, E.; Cabibbo, M.; Spigarelli, S. Wear resistance investigation of titanium nitride-based coatings. Ceram. Int. 2015, 41, 10349–10379. [Google Scholar] [CrossRef]

- Cheng, M.-D.; Luoh, T.; Su, C.-T.; Yang, T.-H.; Chen, K.-C.; Lu, C.-Y. Improvement of the properties and electrical performance on TiCl4-based TiN film using sequential flow chemical vapor deposition process. Thin Solid Films 2010, 518, 2285–2289. [Google Scholar] [CrossRef]

- Liu, P.-T.; Chang, T.-C.; Hu, J.C.; Yang, Y.L.; Szea, S.M. Reliability of multistacked chemical vapor deposited Ti/TiN structure as the diffusion barrier in ultra large scale integrated metallization. J. Electrochem. Soc. 2000, 147, 368–372. [Google Scholar] [CrossRef]

- Shin, Y.-H.; Shimogaki, Y. Diffusion barrier property of TiN and TiN/Al/TiN films deposited with FMCVD for Cu interconnection in ULSI. Sci. Technol. Adv. Mater. 2004, 5, 399–405. [Google Scholar] [CrossRef]

- Sidhwa, A.; Spinner, C.; Gandy, T.; Brown, W.; Ang, S.; Naseem, H.; Ulrich, R. Evaluation of contact and via step coverage using a novel two-step titanium nitride barrier deposition process. MRS Proc. 2002, 716. [Google Scholar] [CrossRef]

- Prikh, S.; Akselrod, L.; Gardner, J.; Armstrong, K.; Parekh, N. TiN barrier integrity and volcano formation in W-plug applications. Thin Solid Films 1998, 320, 26–30. [Google Scholar] [CrossRef]

- Asinovsky, L.; Frisa, L.E. Characterization of PVD TiN uniformity. Thin Solid Films 1998, 313–314, 303–307. [Google Scholar] [CrossRef]

- Wu, C.M.; Wang, M.Y.; Shue, S.L.; Yu, C.H.; Liang, M.S. Integration of CVD W on MOCVD TiN. In Proceedings of the IEEE International Symposium on VLSI technology, System and Applications, Hsinchu, Taiwan, 18–20 April 2001.

- Huang, T.-Y.; Liang, W.-P.; Su, K.-H.; Wu, C.-R.; Lin, Y.-C.; Satoshi, W.; Lin, J.P. Effects of TiCl4-based PECVD-Ti/CVD-TiN barrier layers on the BF2-doped Si for contact plug technology. ECS Trans. 2007, 6, 15–20. [Google Scholar]

- Luoh, T.; Cheng, M.D.; Yeh, W.; Su, C.-T.; Yang, T.-H.; Chen, K.-C.; Ku, J.; Lu, C.-Y. Temperature and RF-plasma power effect on TiCl4 PECVD-Ti process for 0.1 m contact size and beyond. In Proceedings of the SEMICON Taiwan 2006, Taipei, Taiwan, 11–13 September 2006.

- Musher, J.N.; Gordon, R.G. Low-temperature CVD TiN as a diffusion barrier between gold and silicon. J. Electron. Mater. 1991, 20, 1105–1107. [Google Scholar] [CrossRef]

- Akahori, T.; Tanihara, A.; Yano, M. Preparation of TiN films by electron cyclotron resonance plasma chemical vapor deposition. Jpn. J. Appl. Phys. 1991, 30, 3558–3561. [Google Scholar] [CrossRef]

- Kim, Y.-S.; Jeon, H.; Kim, Y.D. Atomic-layer chemical-vapor-deposition of TiN thin films on Si(100) and Si(111). J. Korean Phys. Soc. 2000, 37, 1045–1050. [Google Scholar]

- Park, D.-G.; Kim, T.-K. Effects of fluorine and chlorine on the gate oxide integrity of W/TiN/SiO2/Si metal-oxide-semiconductor structure. Thin Solid Films 2005, 483, 232–238. [Google Scholar] [CrossRef]

- Ducroquet, F.; Achard, H.; Coudert, F.; Previtali, B.; Lugand, J.-F.; Ulmer, L.; Farjot, T.; Gobil, Y.; Heitzmann, M.; Tedesco, S.; et al. Full CMP integration of CVD TiN damascene sub-0.1 um metal gate devices for ULSI applications. IEEE Trans. Electron Devices 2001, 48, 1816–1821. [Google Scholar] [CrossRef]

- Yang, H.; Brown, G.A.; Hu, J.C.; Lu, J.P.; Kraft, R.; Rotondaro, A.L.P.; Hattangady, S.; Chen, I.-C.; Luttmer, J.D.; Chapman, R.A.; et al. A comparison of TiN processes for CVD W/TiN gate electrode on 3 nm gate oxide. IEDM 1997, 459–462. [Google Scholar]

- Nakajima, K.; Akasaki, Y.; Kaneko, M.; Tamaoki, M.; Yamada, Y.; Shimizu, T.; Ozawa, Y.; Suguro, K. Work function controlled metal gate electrode on ultrathin gate insulator. VLSI Tech. Dig. 1999, 96–97. [Google Scholar]

- Lee, S.-H.; Choi, R.; Choi, C. Effects of composition and thickness of TiN metal gate on the equivalent oxide thickness and flat-band voltage in metal oxide semiconductor devices. Microelectron. Eng. 2013, 109, 160–162. [Google Scholar] [CrossRef]

- Vitale, S.A.; Kedzierski, J.; Healey, P.; Wyatt, P.W.; Keast, C.L. Work-function-tuned TiN metal gate FDSOI transistors for subthreshold operation. IEEE Trans. Electron Devices 2011, 58, 419–426. [Google Scholar] [CrossRef]

© 2016 by the authors; licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons by Attribution (CC-BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Luoh, T.; Huang, Y.-K.; Hung, Y.-T.; Yang, L.-W.; Yang, T.-H.; Chen, K.-C. TiCl4 Barrier Process Engineering in Semiconductor Manufacturing. Coatings 2016, 6, 2. https://doi.org/10.3390/coatings6010002

Luoh T, Huang Y-K, Hung Y-T, Yang L-W, Yang T-H, Chen K-C. TiCl4 Barrier Process Engineering in Semiconductor Manufacturing. Coatings. 2016; 6(1):2. https://doi.org/10.3390/coatings6010002

Chicago/Turabian StyleLuoh, Tuung, Yu-Kai Huang, Yung-Tai Hung, Ling-Wuu Yang, Ta-Hone Yang, and Kuang-Chao Chen. 2016. "TiCl4 Barrier Process Engineering in Semiconductor Manufacturing" Coatings 6, no. 1: 2. https://doi.org/10.3390/coatings6010002

APA StyleLuoh, T., Huang, Y.-K., Hung, Y.-T., Yang, L.-W., Yang, T.-H., & Chen, K.-C. (2016). TiCl4 Barrier Process Engineering in Semiconductor Manufacturing. Coatings, 6(1), 2. https://doi.org/10.3390/coatings6010002