A Low-Power Active Self-Interference Cancellation Technique for SAW-Less FDD and Full-Duplex Receivers

Abstract

:1. Introduction

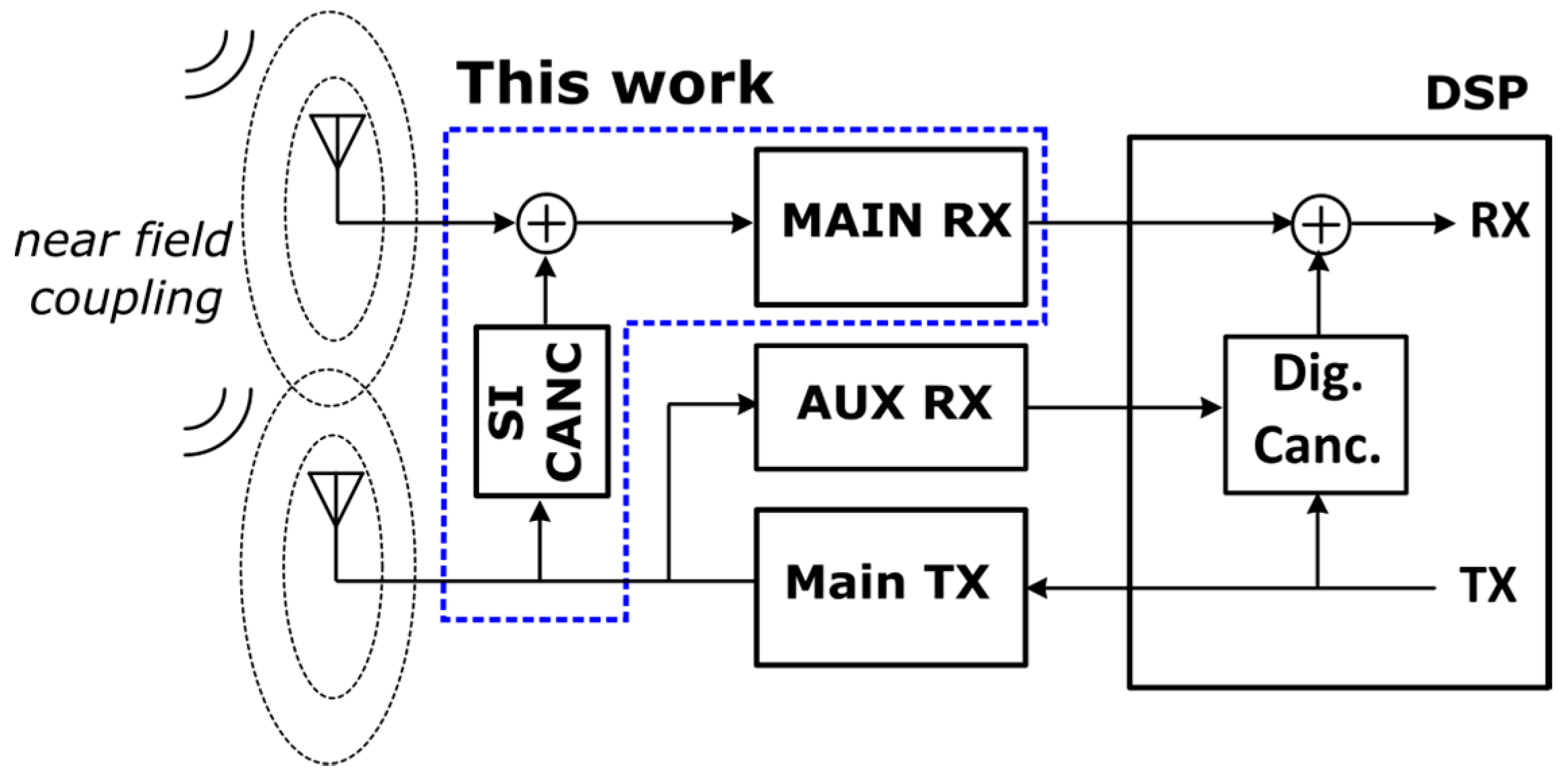

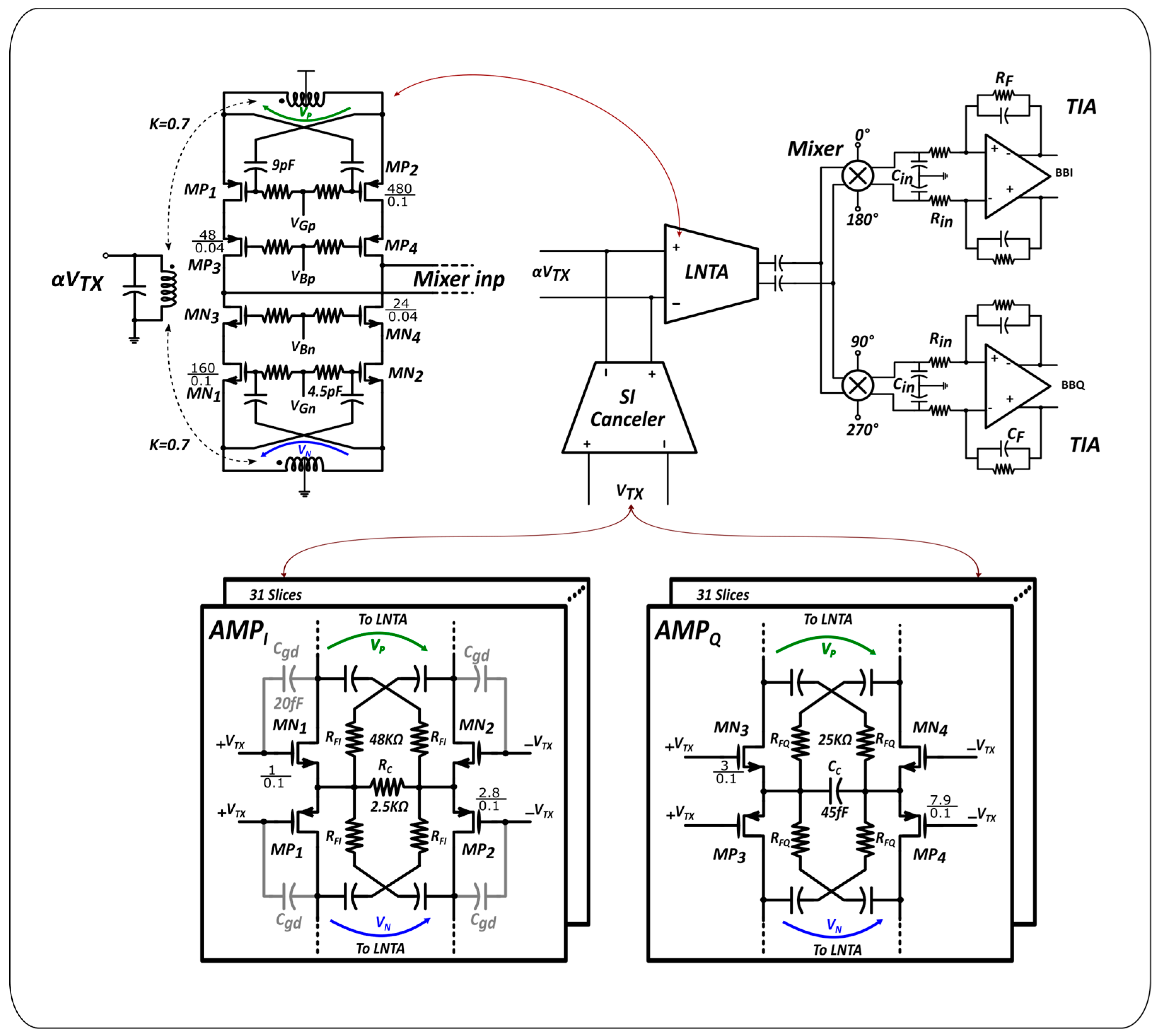

2. System Architecture and Requirements

2.1. Receive Chain

2.1.1. Requirements for FDD

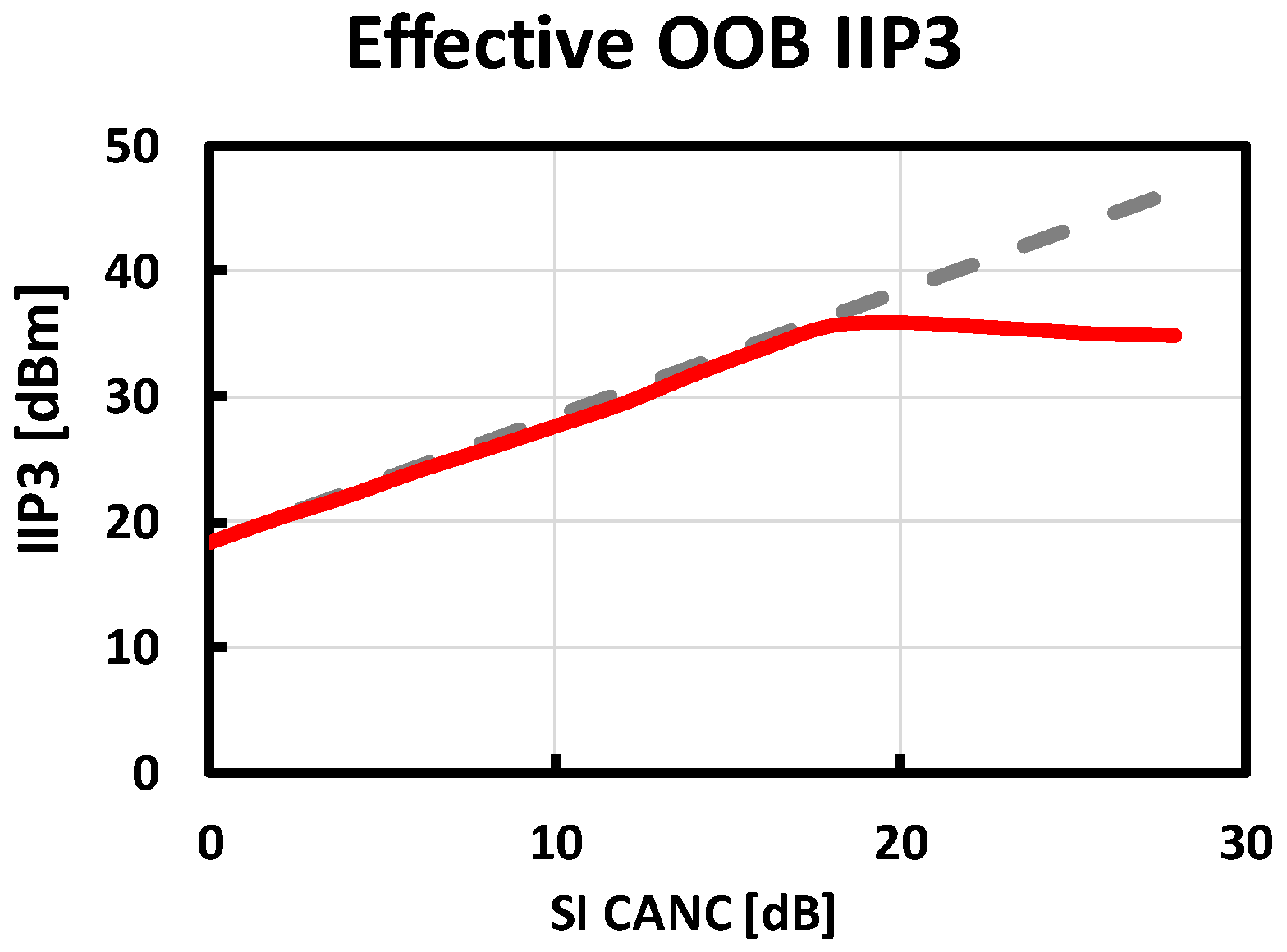

2.1.2. Requirements for FD

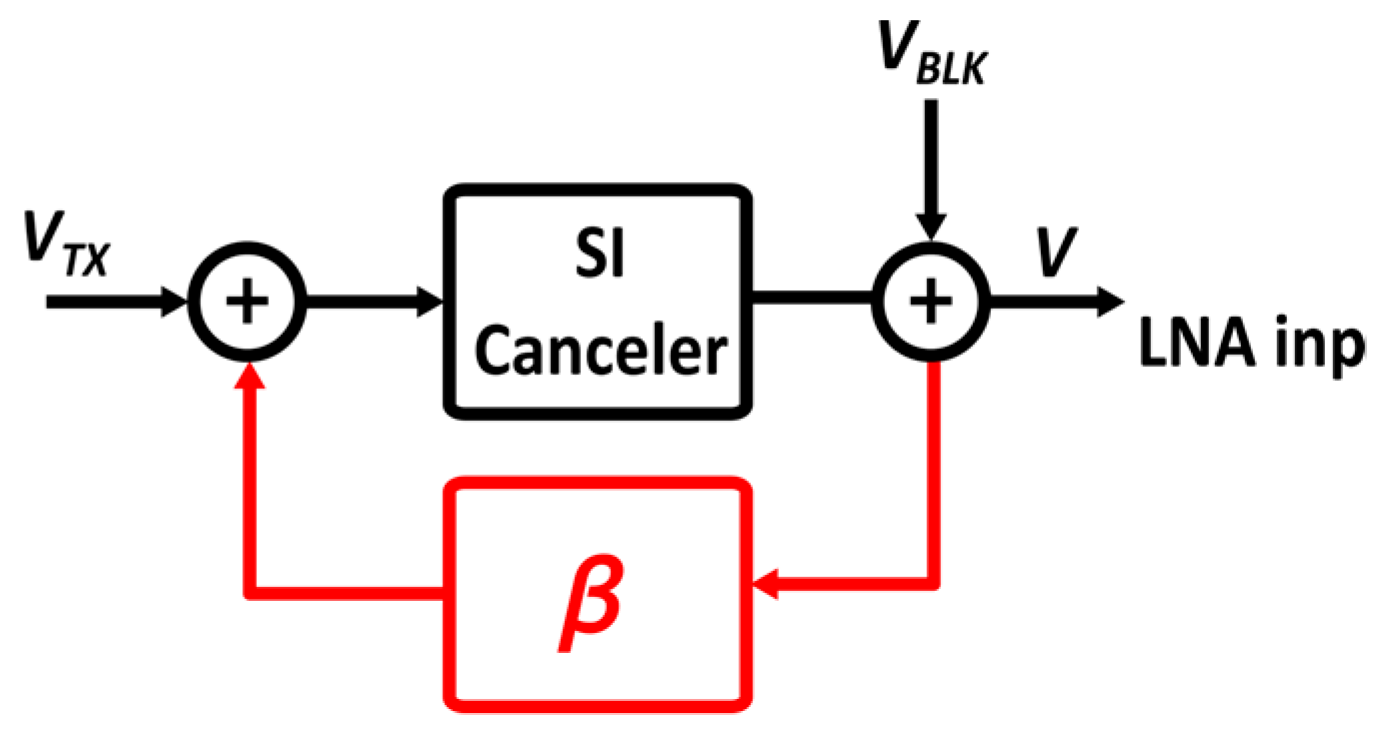

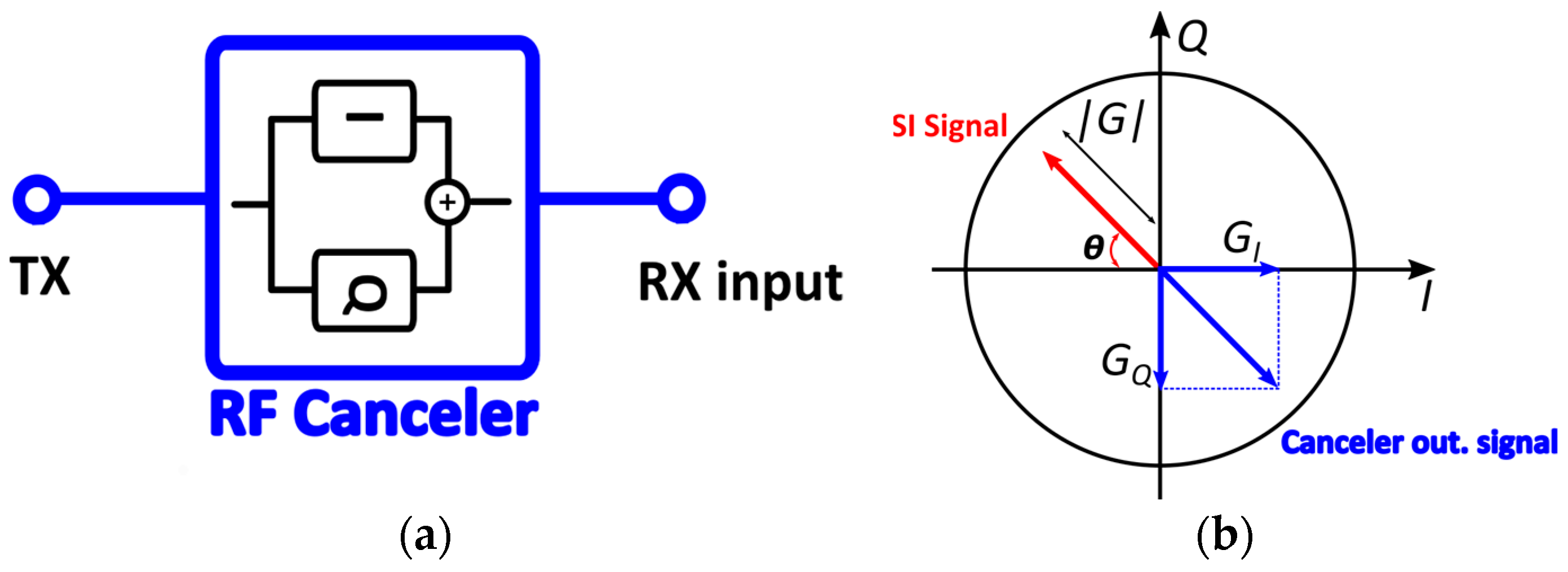

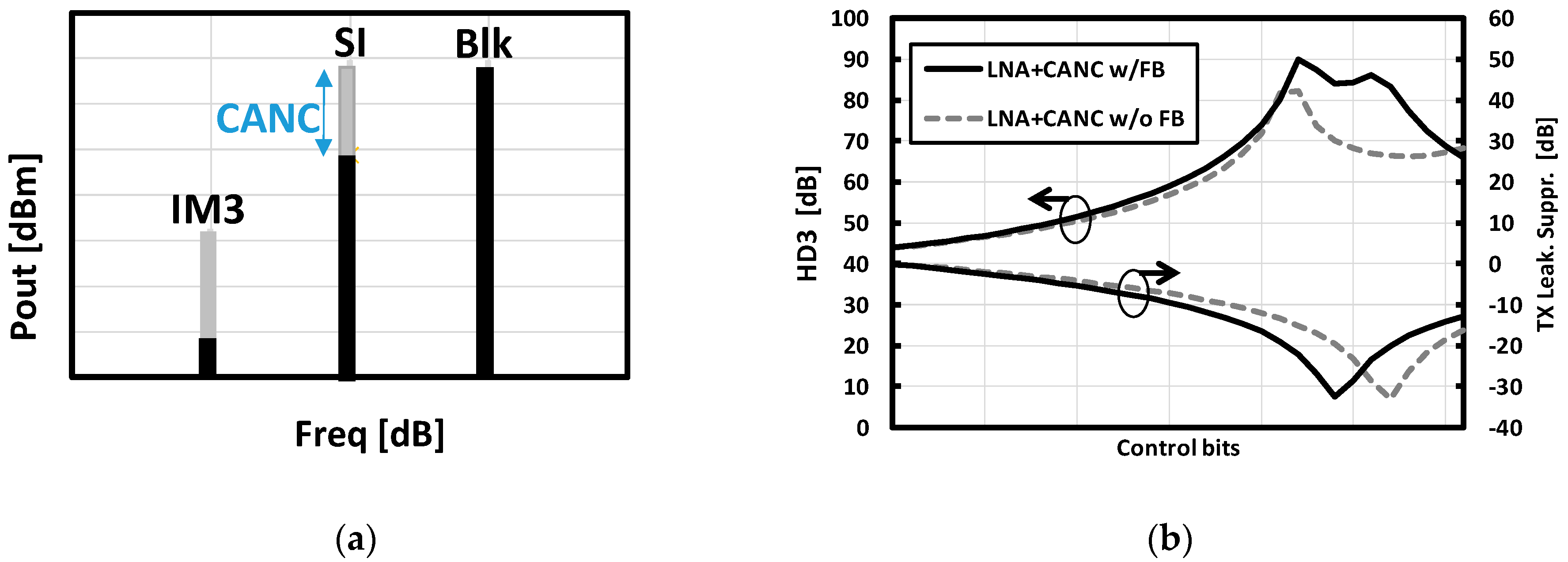

2.2. Self-Interference Canceler Architecture

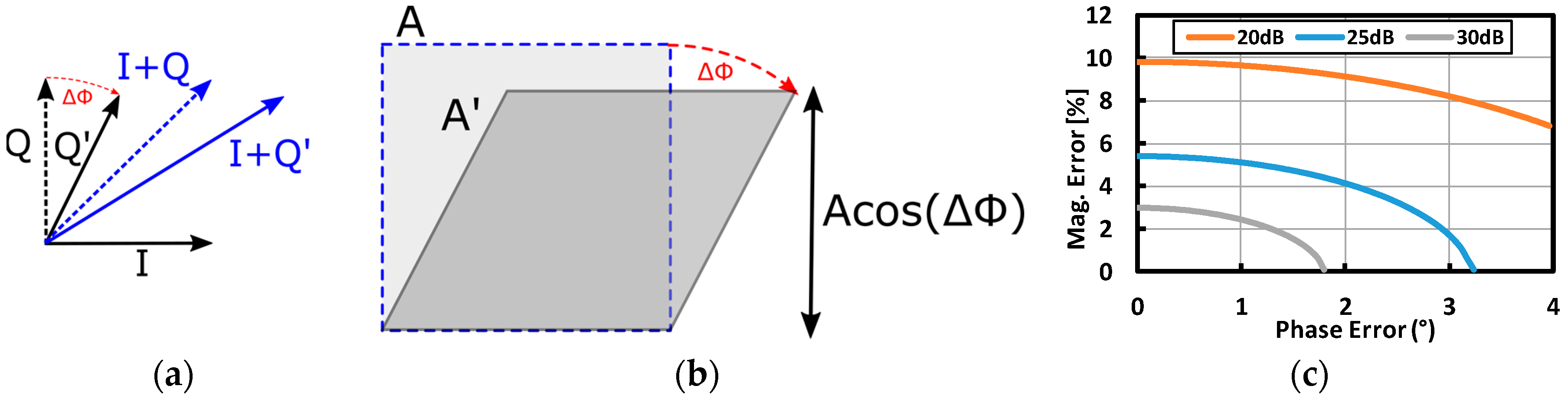

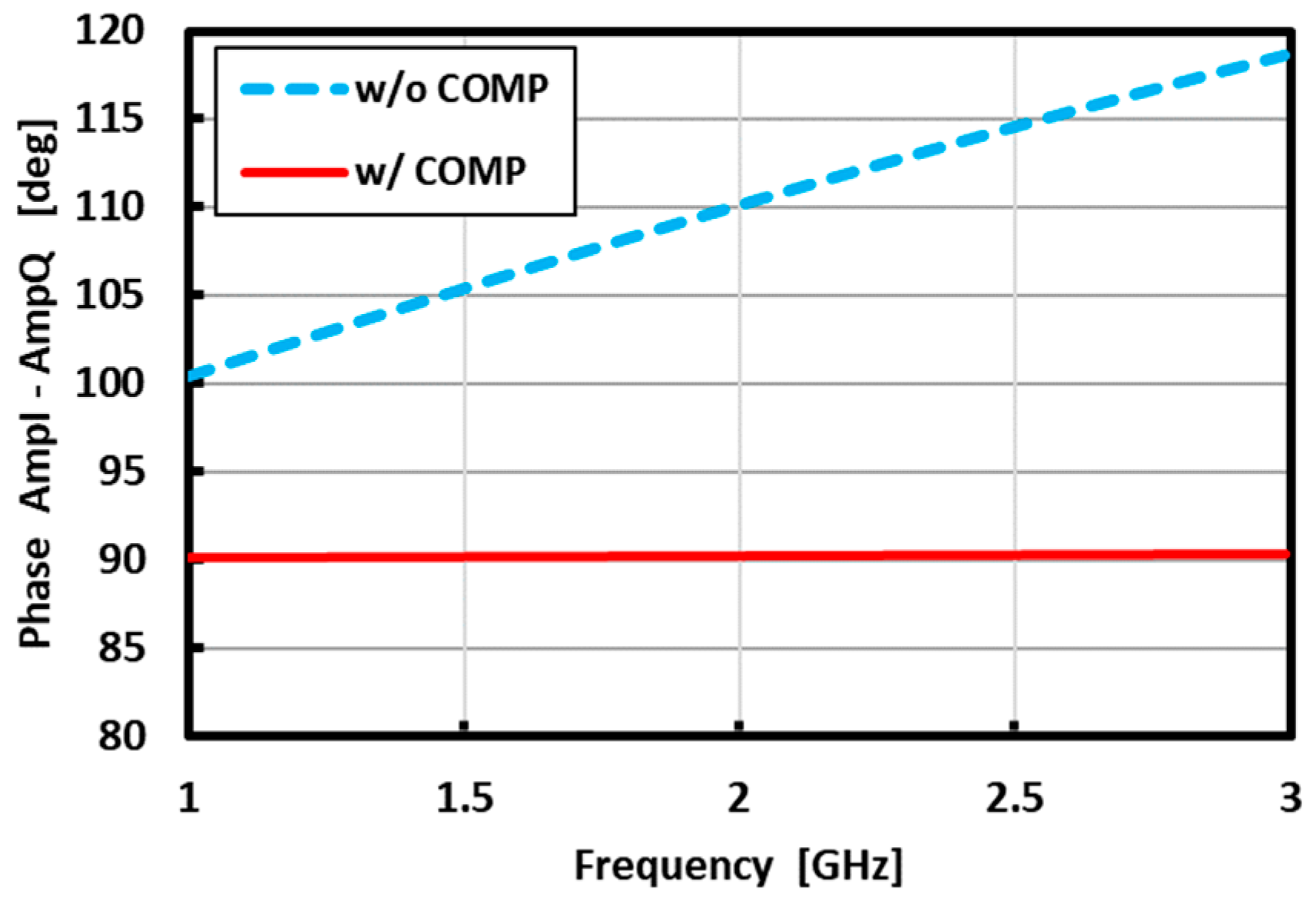

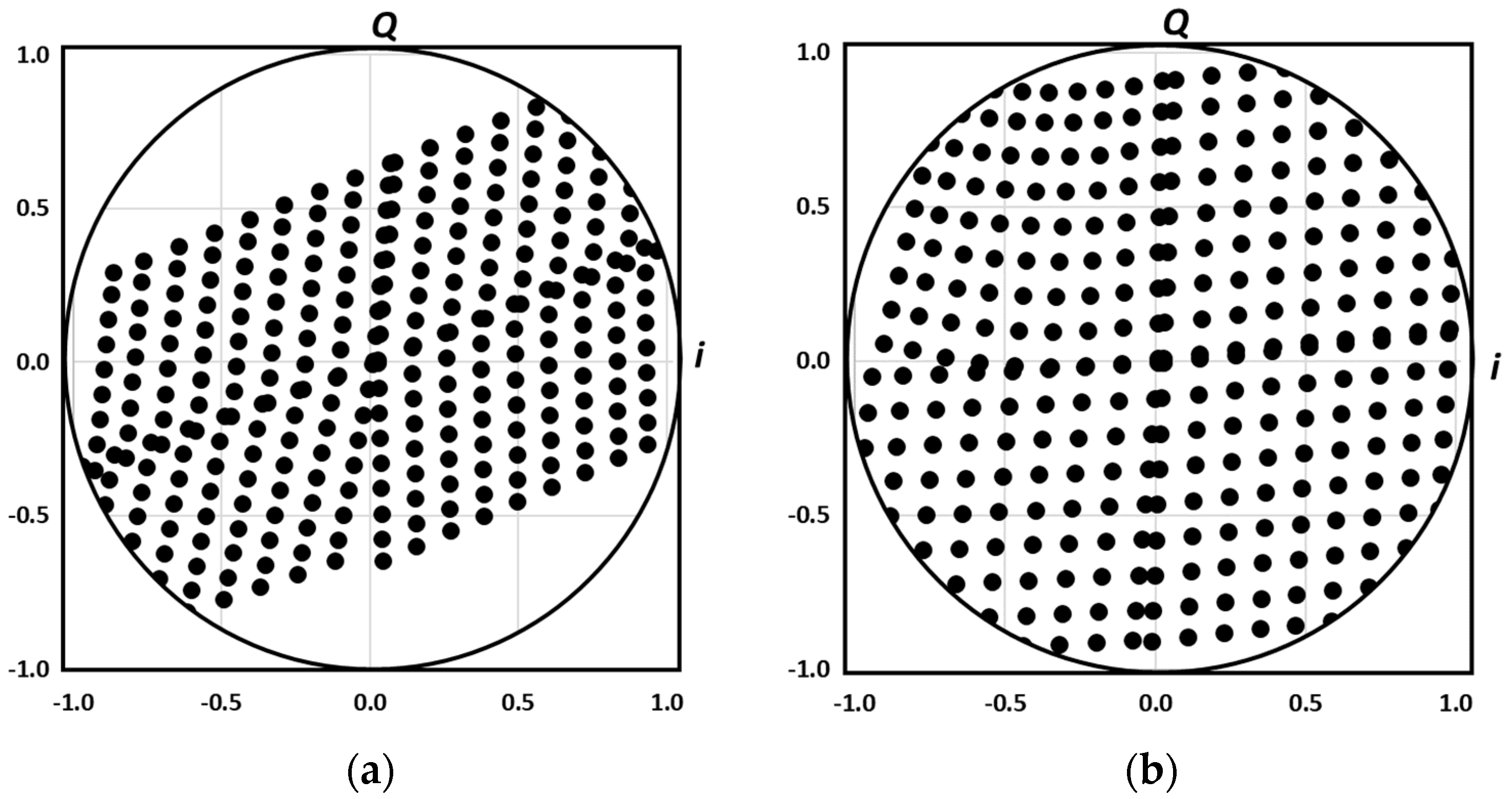

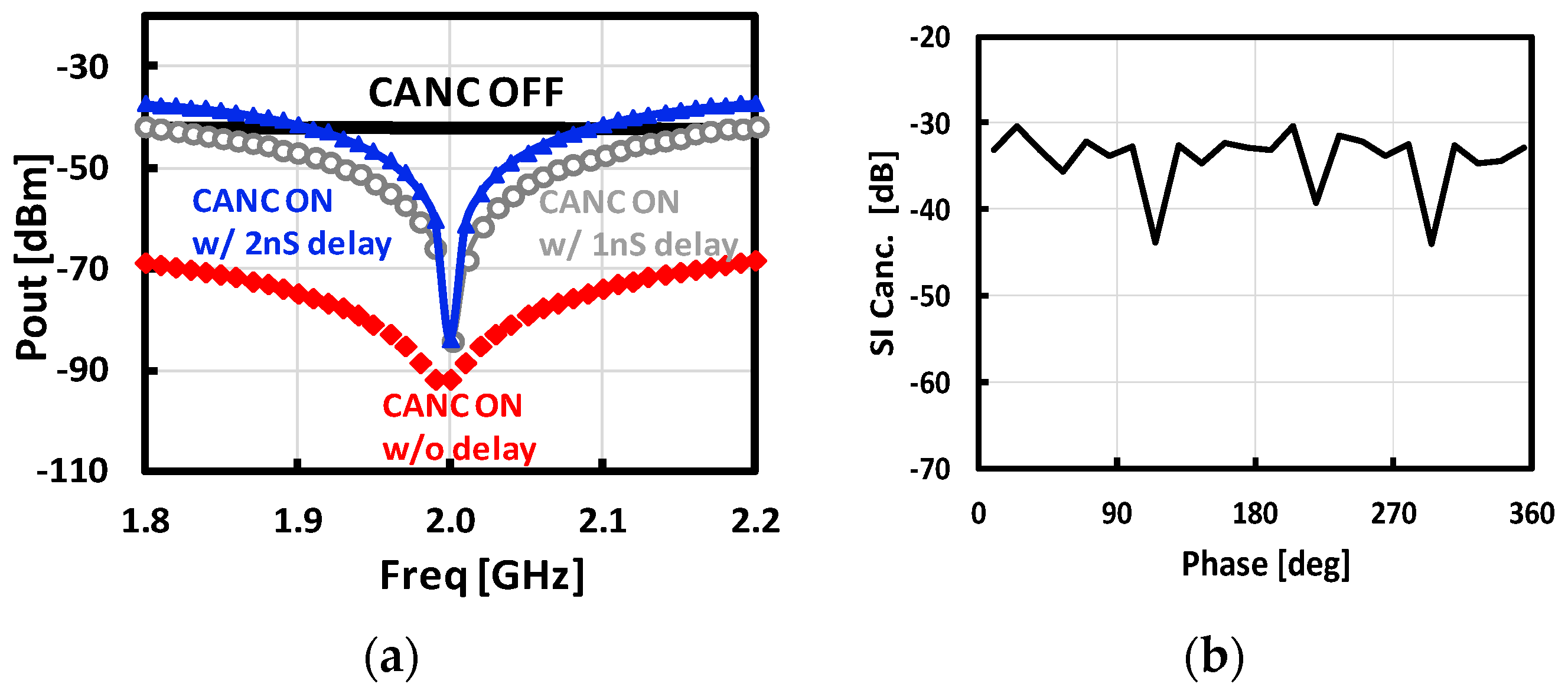

2.3. Magnitude and Phase Errors on Cancellation

3. System Implementation

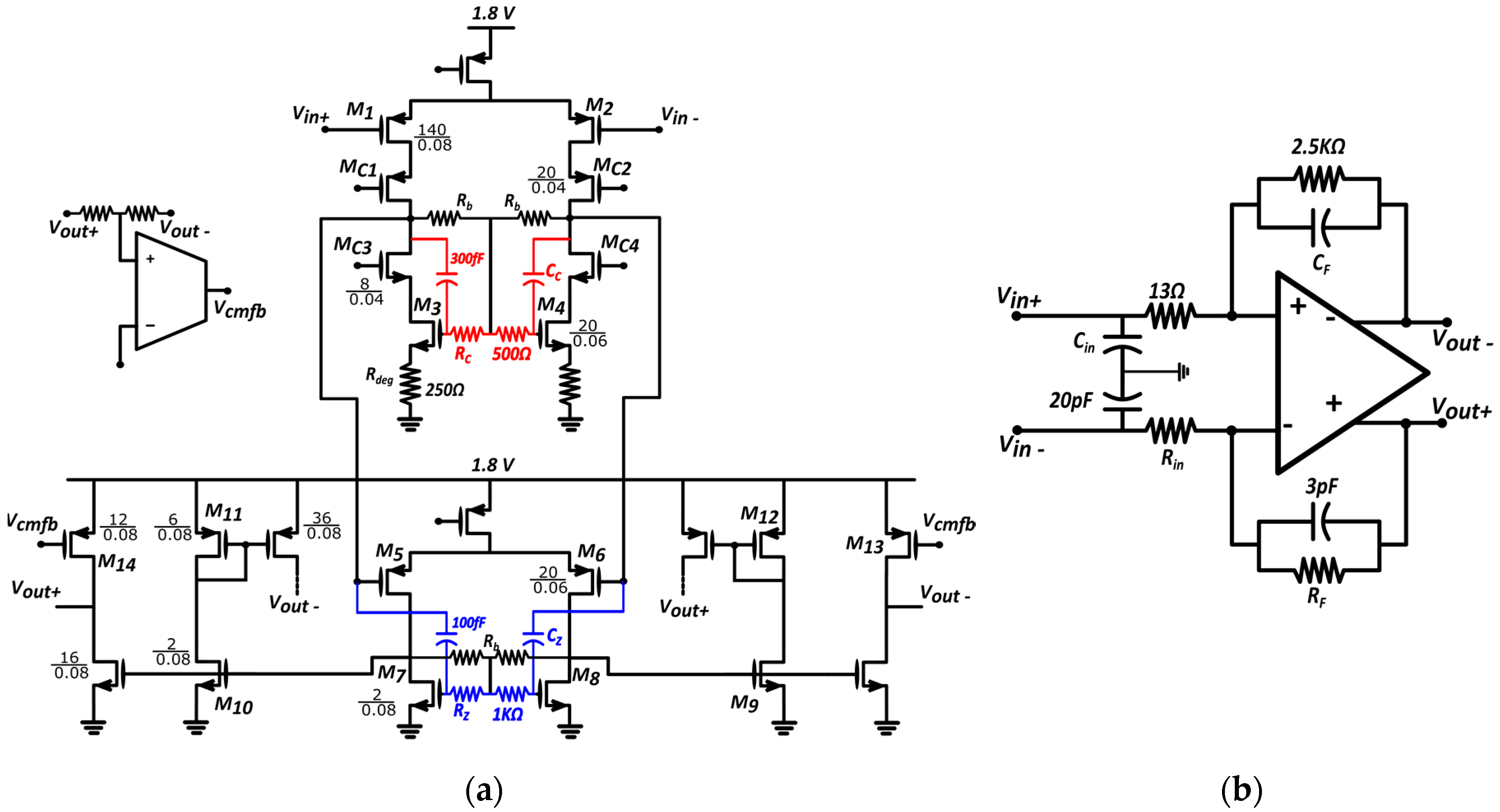

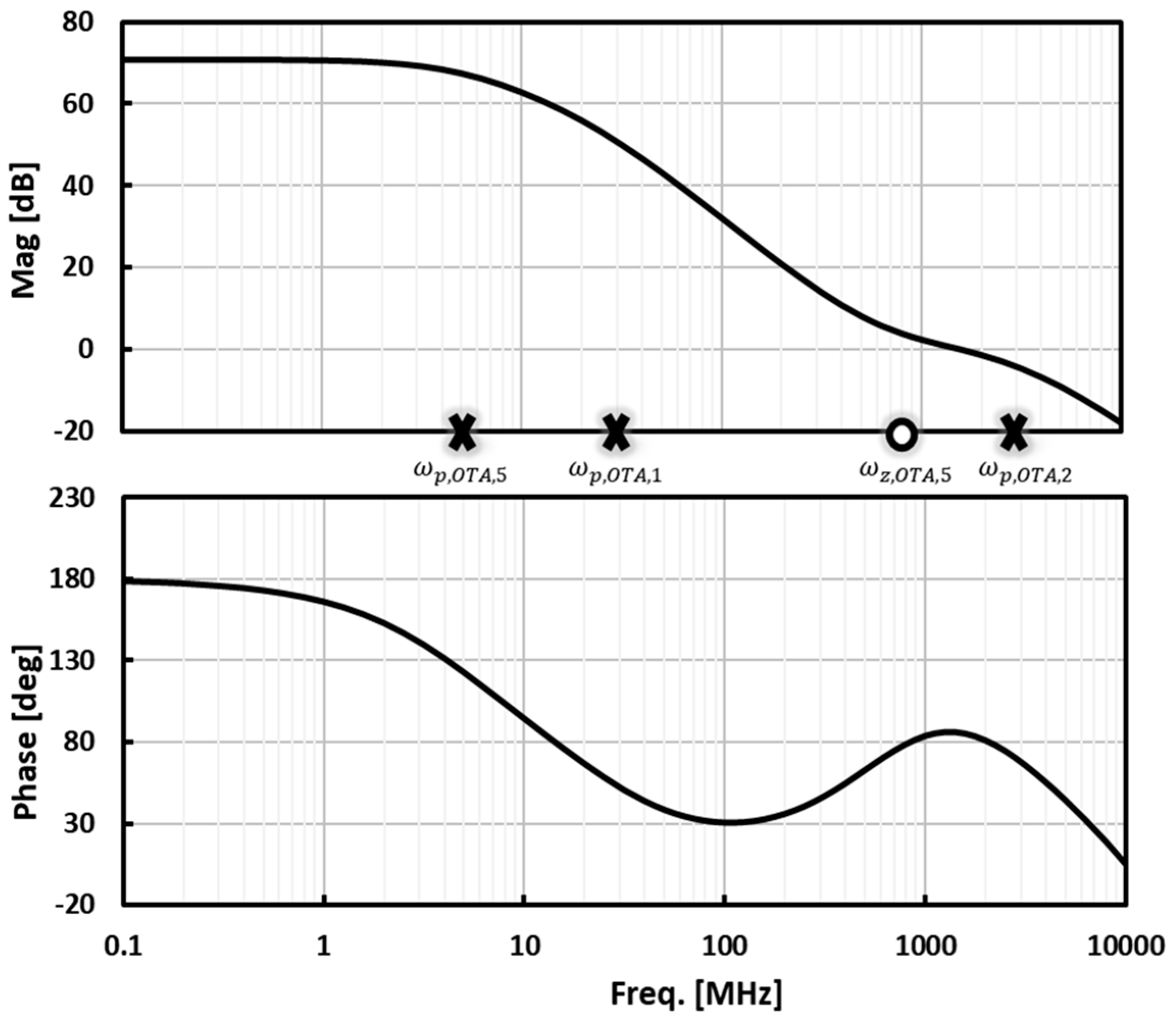

3.1. Low Noise Transconductance Amplifier (LNTA) Design

3.2. Active Self-Interference Canceler

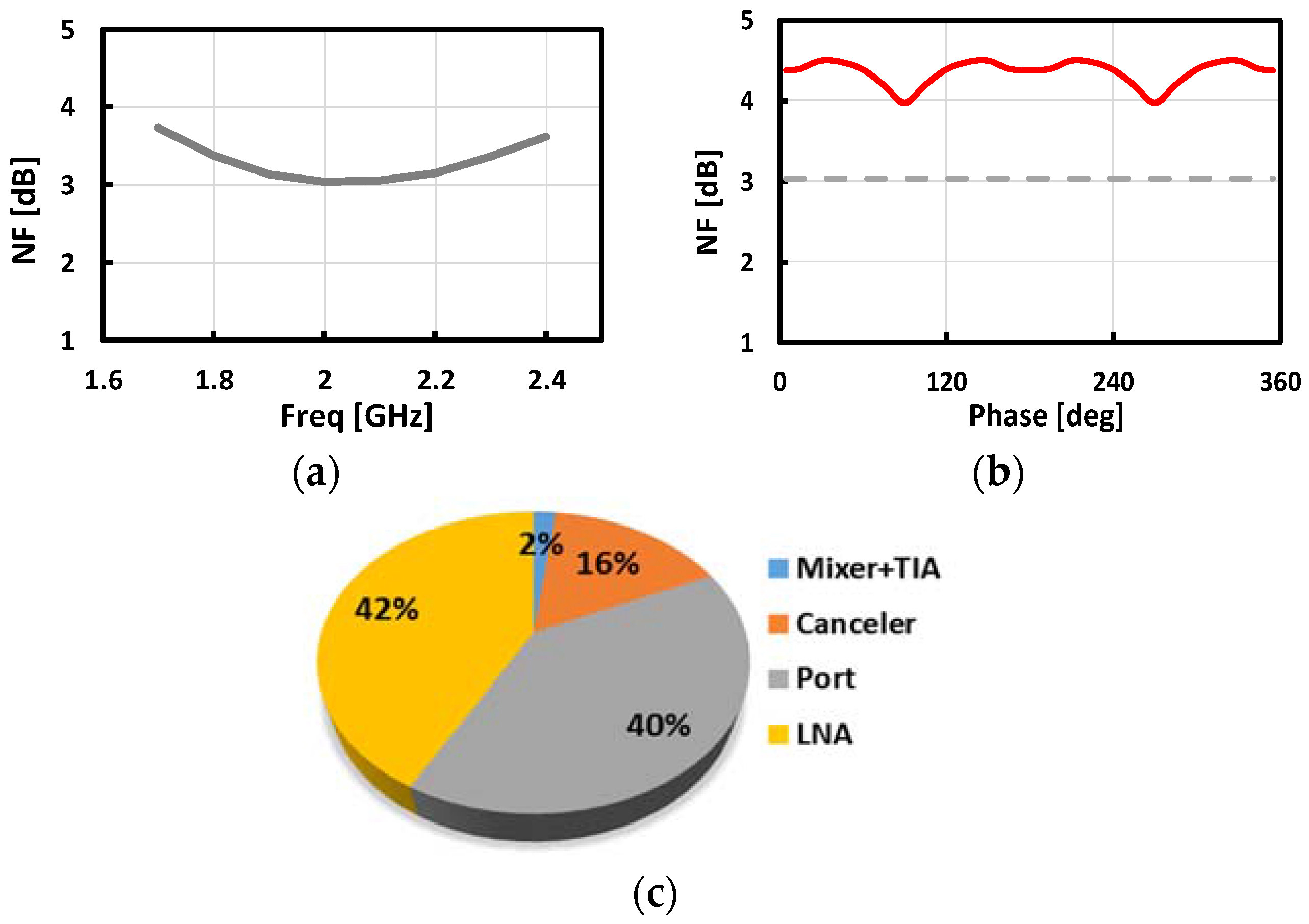

3.2.1. Canceler Noise Analysis

3.2.2. Canceler Linearization

3.3. Baseband Trans-Impedance Amplifier (TIA)

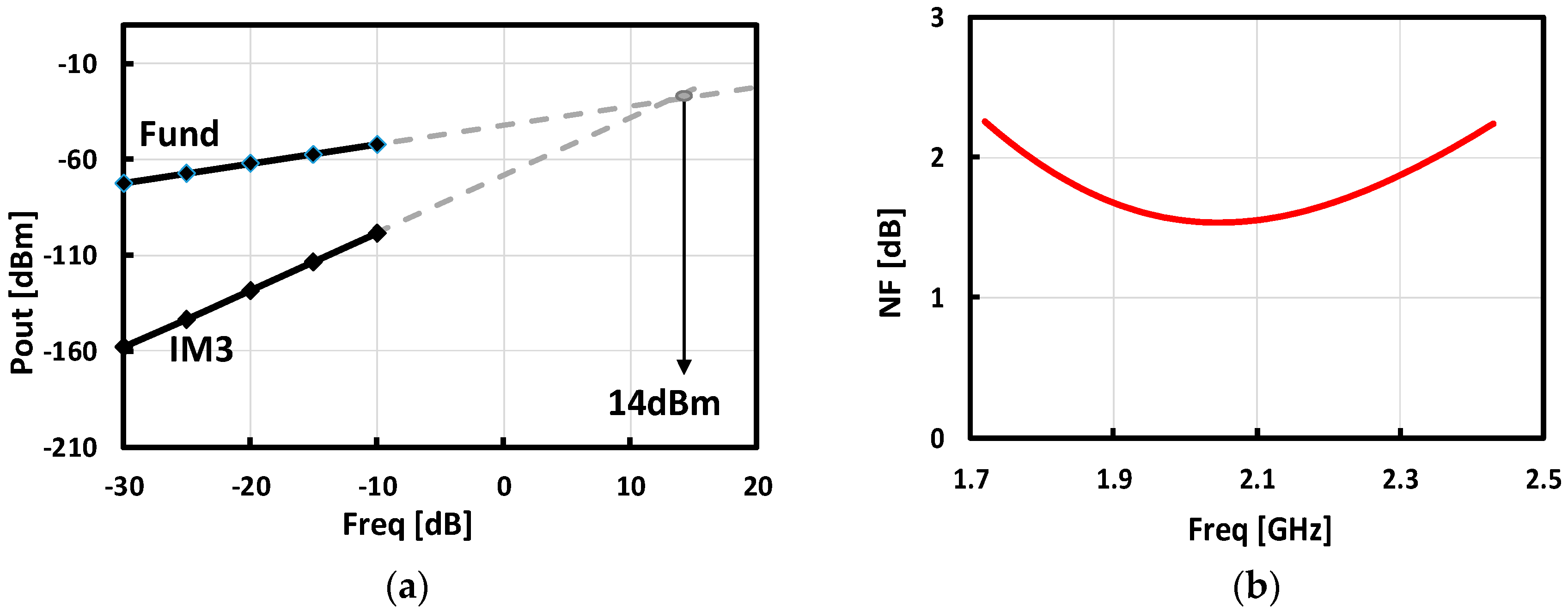

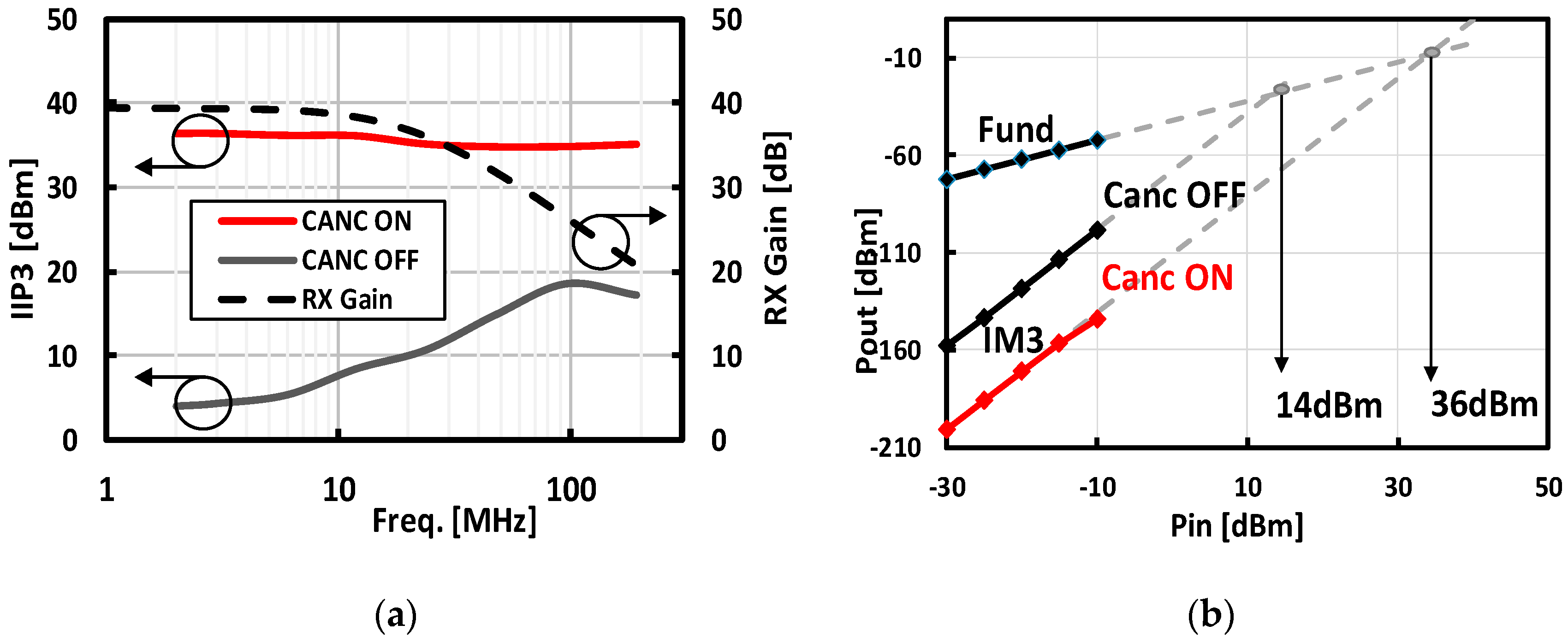

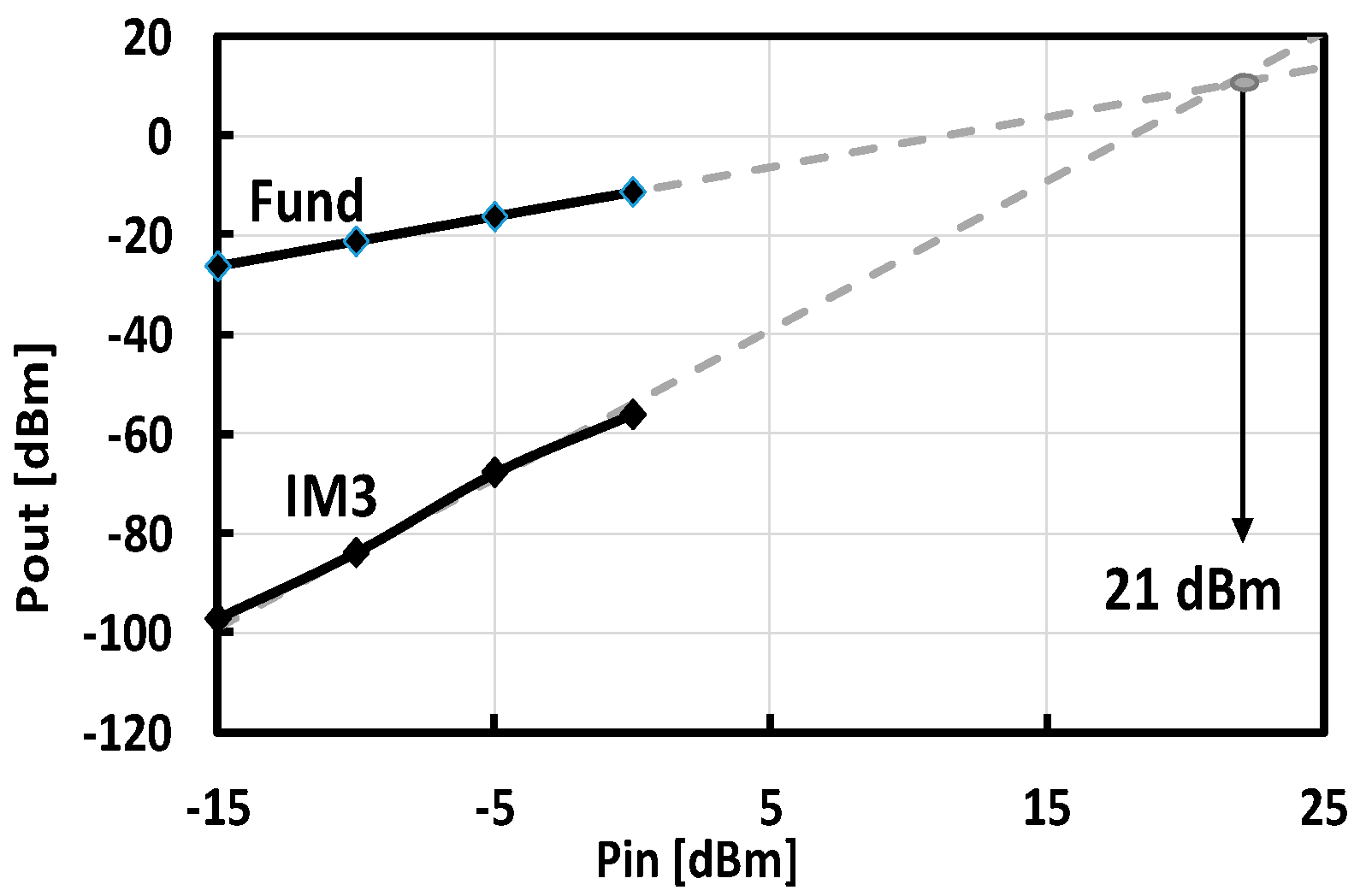

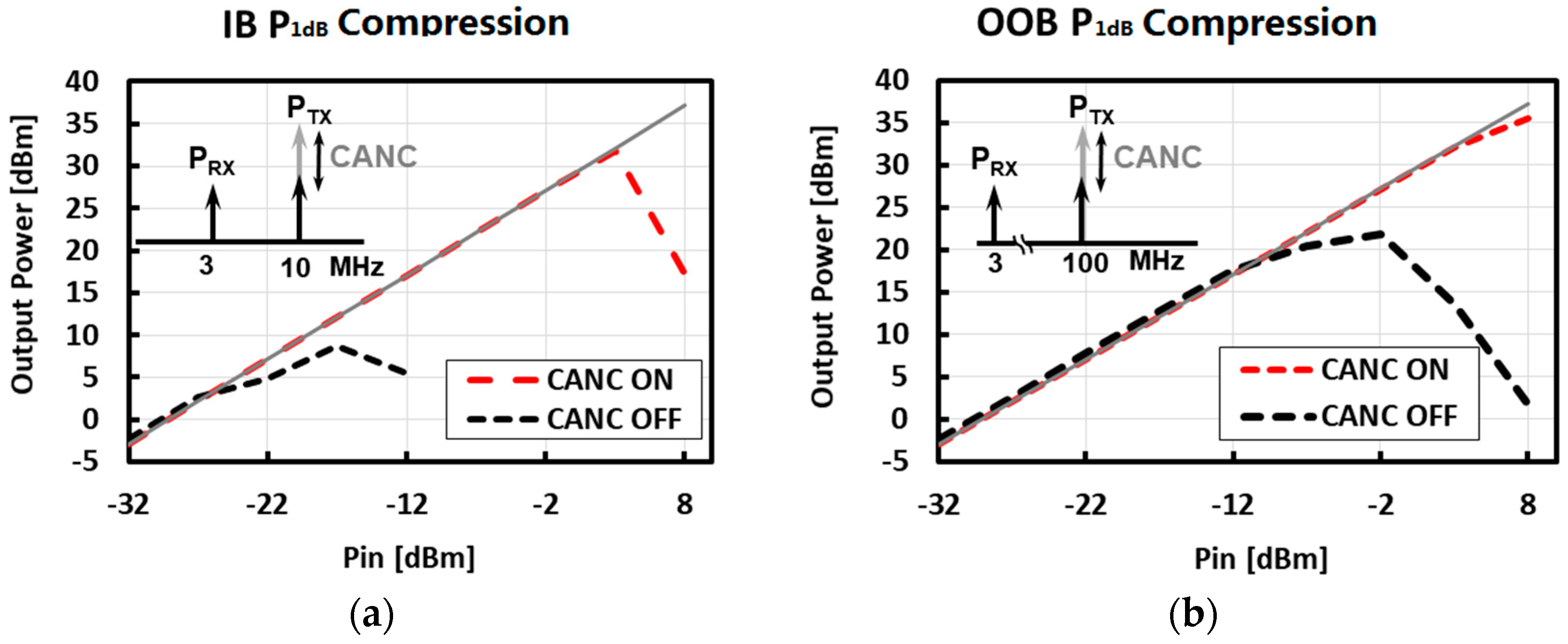

4. Simulation Results

5. Conclusions

Author Contributions

Conflicts of Interest

References

- Fabiano, I.; Sosio, M.; Liscidini, A.; Castello, R. SAW-less analog front-end receivers for TDD and FDD. IEEE J. Solid-State Circuits 2013, 48, 3067–3079. [Google Scholar] [CrossRef]

- Bharadia, D.; McMilin, E.; Katti, S. Full Duplex Radios. In Proceedings of the ACM SIGCOMM, Hong Kong, China, 12–16 August 2013. [Google Scholar]

- Huusari, T.; Choi, Y.S.; Liikkanen, P.; Korpi, D.; Talwar, S.; Valkama, M. Wideband Self-Adaptive RF Cancellation Circuit for Full-Duplex Radio: Operating Principle and Measurements. In Proceedings of the 2015 IEEE 81st Vehicular Technology Conference (VTC Spring), Glasgow, UK, 11–14 May 2015; pp. 1–7. [Google Scholar]

- Tamminen, J.; Turunen, M.; Korpi, D.; Huusari, T.; Choi, Y.; Talwar, S.; Valkama, M. Digitally-controlled RF self-interference canceller for full-duplex radios. In Proceedings of the 2016 24th European Signal Processing Conference (EUSIPCO), Budapest, Hungary, 29 August–2 September 2016; pp. 783–787. [Google Scholar]

- Kiayani, A.; Anttila, L.; Valkama, M. Active RF cancellation of nonlinear TX leakage in FDD transceivers. In Proceedings of the 2016 IEEE Global Conference on Signal and Information Processing (GlobalSIP), Washington, DC, USA, 7–9 December 2016; pp. 689–693. [Google Scholar]

- Roverato, E.; Kosunen, M.; Cornelissens, K.; Vatti, S.; Stynen, P.; Bertrand, K.; Korhonen, T.; Samsom, H.; Vandenameele, P.; Ryynänen, J.; et al. 13.4 All-digital RF transmitter in 28 nm CMOS with programmable RX-band noise shaping. In Proceedings of the 2017 IEEE International Solid-State Circuits Conference (ISSCC), San Francisco, CA, USA, 5–6 February 2017; pp. 222–223. [Google Scholar]

- Abdelhalem, S.H.; Gudem, P.S.; Larson, L.E. Hybrid Transformer-Based Tunable Differential Duplexer in a 90-nm CMOS Process. IEEE Trans. Microw. Theory Tech. 2013, 61, 1316–1326. [Google Scholar] [CrossRef]

- Fabiano, I.; Ramella, M.; Manstretta, D.; Castello, R. A +25 dBm IIP3 1.7–2.1 GHz FDD Receiver Front-End with Integrated Hybrid-Transformer in 28 nm CMOS. IEEE Trans. Microw. Theory Tech. 2017, 65, 4677–4688. [Google Scholar] [CrossRef]

- Calderin, L.; Ramakrishnan, S.; Puglielli, A.; Alon, E.; Nikolić, B.; Niknejad, A.M. Analysis and Design of Integrated Active Cancellation Transceiver for Frequency Division Duplex Systems. IEEE J. Solid-State Circuits 2017, 52, 2038–2054. [Google Scholar] [CrossRef]

- Zhou, J.; Reiskarimian, N.; Krishnaswamy, H. 9.8 Receiver with integrated magnetic-free N-path-filter-based non-reciprocal circulator and baseband self-interference cancellation for full-duplex wireless. In Proceedings of the 2016 IEEE International Solid-State Circuits Conference (ISSCC), San Francisco, CA, USA, 31 January–4 February 2016; pp. 178–180. [Google Scholar]

- Zhang, T.; Suvarna, A.R.; Bhagavatula, V.; Rudell, J.C. An Integrated CMOS Passive Self-Interference Mitigation Technique for FDD Radios. IEEE JSSC 2015, 50, 1176–1188. [Google Scholar] [CrossRef]

- Zhang, T.; Chen, Y.; Huang, C.; Rudell, J.C. A Low-Noise Reconfigurable Full-Duplex Front-End with Self-Interference Cancellation and Harmonic-Rejection Power Amplifier for Low Power Radio Applications. In Proceedings of the 43rd European Solid-State Circuit Conference (ESSCIRC), Leuven, Belgium, 11–14 September 2017. [Google Scholar]

- Reiskarimian, N.; Dastjerdi, M.B.; Zhou, J.; Krishnaswamy, H. Highly-linear integrated magnetic-free circulator-receiver for full-duplex wireless. In Proceedings of the 2017 IEEE International Solid-State Circuits Conference (ISSCC), San Francisco, CA, USA, 5–9 February 2017; pp. 316–317. [Google Scholar]

- Yang, D.; Yuksel, H.; Molnar, A. A Wideband Highly Integrated and Widely Tunable Transceiver for In-Band Full-Duplex Communication. IEEE J. Solid-State Circuits 2015, 50, 1189–1202. [Google Scholar] [CrossRef]

- Ramakrishnan, S.; Calderin, L.; Niknejad, A.; Nikolić, B. An FD/FDD transceiver with RX band thermal, quantization, and phase noise rejection and 64 dB TX signal cancellation. In Proceedings of the 2017 IEEE Radio Frequency Integrated Circuits Symposium (RFIC), Honolulu, HI, USA, 4–6 June 2017; pp. 352–355. [Google Scholar]

- Ayati, S.A.; Mandal, D.; Bakkaloglu, B.; Kiaei, S. Adaptive integrated CMOS circulator. In Proceedings of the 2016 IEEE Radio Frequency Integrated Circuits Symposium (RFIC), San Francisco, CA, USA, 22–24 May 2016; pp. 146–149. [Google Scholar]

- Zhou, J.; Chakrabarti, A.; Kinget, P.; Krishnaswamy, H. Low-Noise Active Cancellation of Transmitter Leakage and Transmitter Noise in Broadband Wireless Receivers for FDD/Co-Existence. IEEE J. Solid-State Circuits 2014, 49, 3046–3062. [Google Scholar] [CrossRef]

- Luo, C.; Gudem, P.S.; Buckwalter, J.F. 0.4–6 GHz,17-dBm B1dB, 36-dBm IIP3 Channel-selecting, Low-noise Amplifier for SAW-less 3G/4G FDD Receivers. In Proceedings of the IEEE RFIC Symposium, Phoenix, AZ, USA, 17–19 May 2015. [Google Scholar]

- Zhou, J.; Chuang, T.H.; Dinc, T.; Krishnaswamy, H. Reconfigurable Receiver with >20 MHz bandwidth self-interference cancellation suitable for FDD, co-existence and full-duplex applications. In Proceedings of the 2015 IEEE International Solid-State Circuits Conference (ISSCC), San Francisco, CA, USA, 22–26 February 2015; pp. 342–343. [Google Scholar]

- Van den Broek, D.J.; Klumperink, E.A.M.; Nauta, B. A self-interference-cancelling receiver for in-band full-duplex wireless with low distortion under cancellation of strong TX leakage. In Proceedings of the 2015 IEEE ISSCC, San Francisco, CA, USA, 22–26 February 2015. [Google Scholar]

- Zhang, T.; Najafi, A.; Su, C.; Rudell, J.C. 18.1 A 1.7-to-2.2 GHz full-duplex transceiver system with >50 dB self-interference cancellation over 42 MHz bandwidth. In Proceedings of the 2017 IEEE International Solid-State Circuits Conference (ISSCC), San Francisco, CA, USA, 5–6 February 2017; pp. 314–315. [Google Scholar]

- Tijani, S.; Manstretta, D. A SAW-less receiver front-end with low power active self-interference canceler. In Proceedings of the 2015 IEEE International Conference on Electronics, Circuits, and Systems (ICECS), Cairo, Egypt, 6–9 December 2015; pp. 89–92. [Google Scholar]

- Montanari, D.; Silvestri, L.; Bozzi, M.; Manstretta, D. Antenna coupling and self-interference cancellation bandwidth in SAW-less diversity receivers. In Proceedings of the 2016 46th European Microwave Conference (EuMC), London, UK, 4–6 October 2016; pp. 731–734. [Google Scholar]

- Montanari, D.; Castellano, G.; Manstretta, D.; Castello, R. A 0.7–2 GHz Auxiliary Receiver with Enhanced Compression for SAW-less FDD. In Proceedings of the 43rd European Solid-State Circuit Conference (ESSCIRC), Leuven, Belgium, 11–14 September 2017. [Google Scholar]

- Yang, X.; Babakhani, A. A 4.6–5.35 GHz transceiver with 38 dB on-chip self-interference cancelation at 10 kHz offset frequency. In Proceedings of the 2015 IEEE Radio Frequency Integrated Circuits Symposium (RFIC), Phoenix, AZ, USA, 17–19 May 2015; pp. 239–242. [Google Scholar]

- ETSI. LTE (E-UTRA) User Equipment (UE) Radio Transmission and Reception, 3GPP TS 136.101 ver. 12.5.0, Release 12. November 2014. Available online: http://www.etsi.org/deliver/etsi_ts/136100_136199/136101/12.05.00_60/ts_136101v120500p.pdf (accessed on 21 August 2017).

- Kim, H.; Woo, S.; Jung, S.; Lee, K.-L. A CMOS Transmitter Leakage Canceller for WCDMA Applications. IEEE Trans. Microw. Theory Tech. 2013, 61, 3373–3380. [Google Scholar] [CrossRef]

- Van den Broek, D.J.; Klumperink, E.A.M.; Nauta, B. An In-Band Full-Duplex Radio Receiver with a Passive Vector Modulator Downmixer for Self-Interference Cancellation. IEEE J. Solid-State Circuits 2015, 50, 3003–3014. [Google Scholar] [CrossRef]

- Zhuo, W.; Embabi, S.; de Gyvez, J.P.; Sanchez-Sinencio, E. Using capacitive cross-coupling technique in RF low noise amplifiers and down-conversion mixer design. In Proceedings of the 26th European Solid-State Circuits Conference, Stockholm, Sweden, 19–21 September 2000; pp. 77–80. [Google Scholar]

- Pini, G.; Manstretta, D.; Castello, R. Highly linear TIA for SAW-less FDD receivers. In Proceedings of the 2016 IEEE Asian Solid-State Circuits Conference (A-SSCC), Toyama, Japan, 7–9 November 2016; pp. 117–120. [Google Scholar]

| This Work | [18] b JSSC ’14 | [20] b ISSCC ’15 | [21] b ISSCC ’15 | [12] b ESSCIRC ’15 | |

|---|---|---|---|---|---|

| FDD/FD | FD/FDD | FDD | FDD/FD | FD | FD |

| Technology | 40 nm | 65 nm | 65 nm | 65 nm | 40 nm |

| CMOS | CMOS | CMOS | CMOS | CMOS | |

| Frequency | 1.5–2.5 GHz | 0.5–1.5 GHz | 0.8–1.4 GHz | 0.15–3.5 GHz | 1–3 GHz |

| NF w/o canc | 3 dB | 4.2–5.6 dB | 4.8–5.8 dB | 6.3 dB | 4.8–5.8 dB |

| NF w/canc | 3.9–4.6 dB | 5–6.4 dB | 5.3/7 dB | 10.3–12.3 dB | 5.3/7 dB |

| IP3 RX | 14 dBm | 12 dBm | 17/−22 dBm | 16.2 dBm a | 18 dBm |

| Eff. IIP3 | 35 dBm | 33 dBm | 27/2 dBm | 19 dBm a | N/A |

| SI Cancellation | >30 dB | 30 dB | 20 dB | 27 dB | 30 dB |

| /250 c–10 d MHz | /25 MHz | /4 MHz | |||

| Max TX Leak. | −4 dBm | +2 dBm | −8 dBm | 1.5 dBm | −20 dBm |

| Power | 14 mW RX | 83 mW RX 72 | 69 mW RX | 23–56 mW | 11 mW RX |

| 11 mW canc | mW canc | 91 mW/path | 0.6 mW/Cac |

© 2017 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Tijani, S.; Manstretta, D. A Low-Power Active Self-Interference Cancellation Technique for SAW-Less FDD and Full-Duplex Receivers. J. Low Power Electron. Appl. 2017, 7, 27. https://doi.org/10.3390/jlpea7040027

Tijani S, Manstretta D. A Low-Power Active Self-Interference Cancellation Technique for SAW-Less FDD and Full-Duplex Receivers. Journal of Low Power Electronics and Applications. 2017; 7(4):27. https://doi.org/10.3390/jlpea7040027

Chicago/Turabian StyleTijani, Saheed, and Danilo Manstretta. 2017. "A Low-Power Active Self-Interference Cancellation Technique for SAW-Less FDD and Full-Duplex Receivers" Journal of Low Power Electronics and Applications 7, no. 4: 27. https://doi.org/10.3390/jlpea7040027