Journal Description

Journal of Low Power Electronics and Applications

Journal of Low Power Electronics and Applications

is an international, peer-reviewed, open access journal on low power electronics published quarterly online by MDPI.

- Open Access— free for readers, with article processing charges (APC) paid by authors or their institutions.

- High Visibility: indexed within Scopus, ESCI (Web of Science), Inspec, and other databases.

- Rapid Publication: manuscripts are peer-reviewed and a first decision is provided to authors approximately 22.2 days after submission; acceptance to publication is undertaken in 4.7 days (median values for papers published in this journal in the second half of 2023).

- Recognition of Reviewers: reviewers who provide timely, thorough peer-review reports receive vouchers entitling them to a discount on the APC of their next publication in any MDPI journal, in appreciation of the work done.

Impact Factor:

2.1 (2022)

Latest Articles

Gate-Level Hardware Priority Resolvers for Embedded Systems

J. Low Power Electron. Appl. 2024, 14(2), 25; https://doi.org/10.3390/jlpea14020025 - 17 Apr 2024

Abstract

►

Show Figures

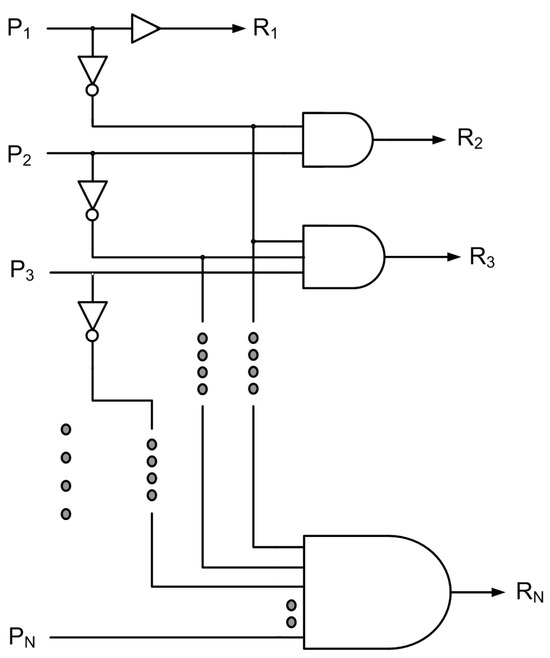

An N-bit priority resolver having N inputs and N outputs functions as polling hardware in an embedded system, enabling access to a resource when multiple devices initiate access requests at its inputs which may be located on-chip or off-chip. Subsystems such as data

[...] Read more.

An N-bit priority resolver having N inputs and N outputs functions as polling hardware in an embedded system, enabling access to a resource when multiple devices initiate access requests at its inputs which may be located on-chip or off-chip. Subsystems such as data buses, comparators, fixed- and floating-point arithmetic units, interconnection network routers, etc., utilize the priority resolver function. In the literature, there are many transistor-level designs for the priority resolver based on dynamic CMOS logic, some of which are modular and others are not. This article presents a novel gate-level modular design of priority resolvers that can accommodate any number of inputs and outputs. Based on our modular design architecture, small-size priority resolvers can be conveniently combined to form medium- or large-size priority resolvers along with extra logic. The proposed modular design approach helps to reduce the coding complexity compared to the conventional direct design approach and facilitates scalability. We discuss the gate-level implementation of 4-, 8-, 16-, 32-, 64-, and 128-bit priority resolvers based on the direct and modular approaches and provide a performance comparison between these based on the design metrics. According to the modular approach, different sizes of priority resolver modules were used to implement larger-size priority resolvers. For example, a 4-bit priority resolver module was used to implement 8-, 16-, 32-, 64-, and 128-bit priority resolvers in a modular fashion. We used a 28 nm CMOS standard digital cell library and Synopsys EDA tools to synthesize the priority resolvers. The estimated design metrics show that the modular approach tends to facilitate increasing reductions in delay and power-delay product (PDP) compared to the direct approach, especially as the size of the priority resolver increases. For example, a 32-bit modular priority resolver utilizing 16-bit priority resolver modules had a 39.4% reduced delay and a 23.1% reduced PDP compared to a directly implemented 32-bit priority resolver, and a 128-bit modular priority resolver utilizing 16-bit priority resolver modules had a 71.8% reduced delay and a 61.4% reduced PDP compared to a directly implemented 128-bit priority resolver.

Full article

Open AccessBrief Report

Efficient Addition Circuits Using Three-Gate Reconfigurable Field Effect Transistors

by

Fanny Spagnolo, Pasquale Corsonello, Fabio Frustaci and Stefania Perri

J. Low Power Electron. Appl. 2024, 14(2), 24; https://doi.org/10.3390/jlpea14020024 - 14 Apr 2024

Abstract

►▼

Show Figures

Reconfigurable FETs (RFETs) are widely recognized as a promising way to overcome conventional CMOS architectures. This paper presents novel addition circuit intentionally designed to exploit the ability of RFETs to operate efficiently on demand as n- or p-type FETs. First, a novel Full

[...] Read more.

Reconfigurable FETs (RFETs) are widely recognized as a promising way to overcome conventional CMOS architectures. This paper presents novel addition circuit intentionally designed to exploit the ability of RFETs to operate efficiently on demand as n- or p-type FETs. First, a novel Full Adder (FA) is proposed and characterized. A comparison with other designs shows that the proposed FA achieves a worst-case delay and a dynamic power consumption of up to 43.5% and 79% lower. As a drawback, in terms of the estimated area, it is up to 32% larger than the competitors. Then, the new FA is used to implement Ripple-Carry Adders (RCAs). A 32-bit adder designed as proposed herein reaches an energy–delay product (EDP) ~25.7× and ~141× lower than its CMOS and the RFET-based counterparts.

Full article

Figure 1

Open AccessArticle

Vehicle Detection in Adverse Weather: A Multi-Head Attention Approach with Multimodal Fusion

by

Nujhat Tabassum and Mohamed El-Sharkawy

J. Low Power Electron. Appl. 2024, 14(2), 23; https://doi.org/10.3390/jlpea14020023 - 13 Apr 2024

Abstract

In the realm of autonomous vehicle technology, the multimodal vehicle detection network (MVDNet) represents a significant leap forward, particularly in the challenging context of weather conditions. This paper focuses on the enhancement of MVDNet through the integration of a multi-head attention layer, aimed

[...] Read more.

In the realm of autonomous vehicle technology, the multimodal vehicle detection network (MVDNet) represents a significant leap forward, particularly in the challenging context of weather conditions. This paper focuses on the enhancement of MVDNet through the integration of a multi-head attention layer, aimed at refining its performance. The integrated multi-head attention layer in the MVDNet model is a pivotal modification, advancing the network’s ability to process and fuse multimodal sensor information more efficiently. The paper validates the improved performance of MVDNet with multi-head attention through comprehensive testing, which includes a training dataset derived from the Oxford Radar RobotCar. The results clearly demonstrate that the multi-head MVDNet outperforms the other related conventional models, particularly in the average precision (AP) of estimation, under challenging environmental conditions. The proposed multi-head MVDNet not only contributes significantly to the field of autonomous vehicle detection but also underscores the potential of sophisticated sensor fusion techniques in overcoming environmental limitations.

Full article

(This article belongs to the Special Issue Advancements in Low-Power Ubiquitous Sensing, Computing, and Communication Interfaces for IoT: Circuits, Systems, and Applications)

►▼

Show Figures

Figure 1

Open AccessArticle

A Low Power Injection-Locked CDR Using 28 nm FDSOI Technology for Burst-Mode Applications

by

Yuqing Mao, Yoann Charlon, Yves Leduc and Gilles Jacquemod

J. Low Power Electron. Appl. 2024, 14(2), 22; https://doi.org/10.3390/jlpea14020022 - 07 Apr 2024

Abstract

►▼

Show Figures

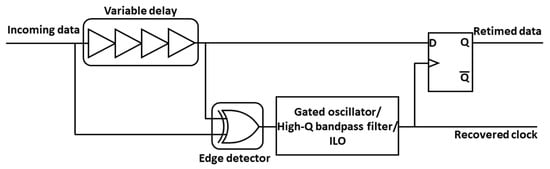

In this paper, a low-power Injection-Locked Clock and Data Recovery (ILCDR) using a 28 nm Ultra-Thin Body and Box-Fully Depleted Silicon On Insulator (UTBB-FDSOI) technology is presented. The back-gate auto-biasing of UTBB-FDSOI transistors enables the creation of a Quadrature Ring Oscillator (QRO) reducing

[...] Read more.

In this paper, a low-power Injection-Locked Clock and Data Recovery (ILCDR) using a 28 nm Ultra-Thin Body and Box-Fully Depleted Silicon On Insulator (UTBB-FDSOI) technology is presented. The back-gate auto-biasing of UTBB-FDSOI transistors enables the creation of a Quadrature Ring Oscillator (QRO) reducing both size and power consumption compared to an LC tank oscillator. By injecting a digital signal into this circuit, we realize an Injection-Locked Oscillator (ILO) with low jitter. Thanks to the good performance of this oscillator, we propose a low-power ILCDR with fast locking time and low jitter for burst-mode applications. The main novelty consists of the implementation of a complementary QRO based on back-gate control using FDSOI technology to realize a simple and efficient ILCDR circuit. With a Pseudo-Random Binary Sequence (PRBS7) at 868 Mbps, the recovered clock jitter is 26.7 ps (2.3% UIp-p) and the recovered data jitter is 11.9 ps (1% UIp-p). With a 0.6 V power supply, the power consumption is 318μW. All the results presented here are based on post-layout simulations, as no prototypes have been produced. Similarly, we can estimate the surface area of the chip (without the pad ring) at around 6600 μm2.

Full article

Figure 1

Open AccessArticle

A 0.3 V OTA with Enhanced CMRR and High Robustness to PVT Variations

by

Riccardo Della Sala, Francesco Centurelli, Giuseppe Scotti and Alessandro Trifiletti

J. Low Power Electron. Appl. 2024, 14(2), 21; https://doi.org/10.3390/jlpea14020021 - 02 Apr 2024

Abstract

►▼

Show Figures

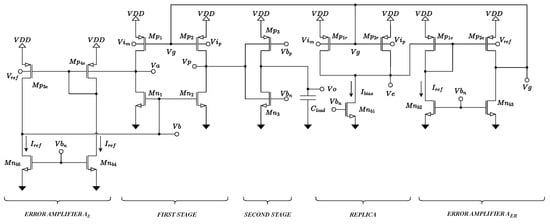

In this paper, we present a 0.3 V body-driven operational transconductance amplifier (OTA) that exploits a biasing approach based on the use of a replica loop with gain. An auxiliary amplifier is exploited both in the current mirror load of the first stage

[...] Read more.

In this paper, we present a 0.3 V body-driven operational transconductance amplifier (OTA) that exploits a biasing approach based on the use of a replica loop with gain. An auxiliary amplifier is exploited both in the current mirror load of the first stage of the OTA and in the replica loop in order to achieve super-diode behavior, resulting in low mirror gain error, which enhances CMRR, and robust biasing. Common-mode feedforward, provided by the replica loop, further enhances CMRR. Simulations in a 180 nm CMOS technology show 65 dB gain with 2 kHz unity-gain frequency on a 200 pF load when consuming 9 nW. Very high linearity with a 0.24% THD at 90% full-scale and robustness to PVT variations are also achieved.

Full article

Figure 1

Open AccessArticle

Dual-Band Large-Frequency Ratio Power Divider Using Mode Composite Transmission Line for 5G Communication Systems

by

Kaijun Song, Lele Fang and Yedi Zhou

J. Low Power Electron. Appl. 2024, 14(2), 20; https://doi.org/10.3390/jlpea14020020 - 31 Mar 2024

Abstract

►▼

Show Figures

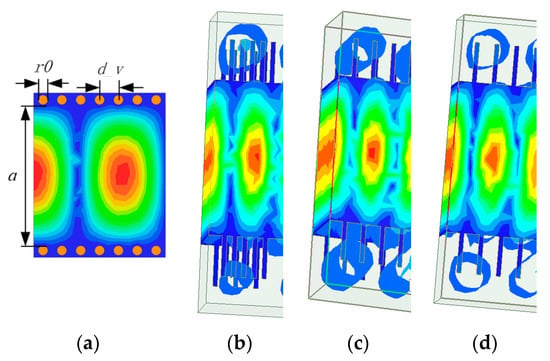

In this paper, a novel kind of mode composite transmission line (MC-TL) is proposed, and a dual-band power divider with a large frequency ratio using this novel MC-TL for 5G communication systems was developed. The proposed MC-TL was developed using spoof surface plasmon

[...] Read more.

In this paper, a novel kind of mode composite transmission line (MC-TL) is proposed, and a dual-band power divider with a large frequency ratio using this novel MC-TL for 5G communication systems was developed. The proposed MC-TL was developed using spoof surface plasmon polaritons (SSPPs) and a corrugated substrate-integrated waveguide (CSIW) transmission line, which supports both a surface plasmon mode and TE10 mode, independently. The surface plasmon mode operates in the grooves of the surface metal layer, while the TE10 mode works in the substrate between two metal layers. These two parts can transmit different modes at independent frequencies. This structure can be used in dual-band transmission lines with a high frequency ratio. The characteristics and design of the MC-TL (SSPPs and CSIW) are analyzed and illustrated. The MC-TL was fabricated and measured to demonstrate its performance. Moreover, based on the proposed MC-TL, a dual-band power divider with a large frequency ratio (operating at 3 GHz and 28 GHz simultaneously) was also designed and fabricated. It can cover the frequency of a fifth-generation communication system perfectly. The measured outcomes align closely with the simulated results, demonstrating robust agreement and showcasing excellent transmission capabilities.

Full article

Figure 1

Open AccessArticle

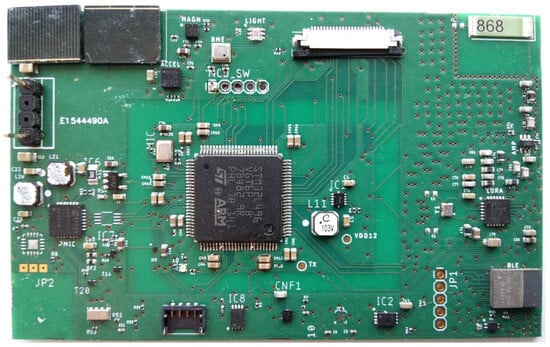

A Citizen Science Tool Based on an Energy Autonomous Embedded System with Environmental Sensors and Hyperspectral Imaging

by

Charalampos S. Kouzinopoulos, Eleftheria Maria Pechlivani, Nikolaos Giakoumoglou, Alexios Papaioannou, Sotirios Pemas, Panagiotis Christakakis, Dimosthenis Ioannidis and Dimitrios Tzovaras

J. Low Power Electron. Appl. 2024, 14(2), 19; https://doi.org/10.3390/jlpea14020019 - 27 Mar 2024

Abstract

►▼

Show Figures

Citizen science reinforces the development of emergent tools for the surveillance, monitoring, and early detection of biological invasions, enhancing biosecurity resilience. The contribution of farmers and farm citizens is vital, as volunteers can strengthen the effectiveness and efficiency of environmental observations, improve surveillance

[...] Read more.

Citizen science reinforces the development of emergent tools for the surveillance, monitoring, and early detection of biological invasions, enhancing biosecurity resilience. The contribution of farmers and farm citizens is vital, as volunteers can strengthen the effectiveness and efficiency of environmental observations, improve surveillance efforts, and aid in delimiting areas affected by plant-spread diseases and pests. This study presents a robust, user-friendly, and cost-effective smart module for citizen science that incorporates a cutting-edge developed hyperspectral imaging (HI) module, integrated in a single, energy-independent device and paired with a smartphone. The proposed module can empower farmers, farming communities, and citizens to easily capture and transmit data on crop conditions, plant disease symptoms (biotic and abiotic), and pest attacks. The developed HI-based module is interconnected with a smart embedded system (SES), which allows for the capture of hyperspectral images. Simultaneously, it enables multimodal analysis using the integrated environmental sensors on the module. These data are processed at the edge using lightweight Deep Learning algorithms for the detection and identification of Tuta absoluta (Meyrick), the most important invaded alien and devastating pest of tomato. The innovative Artificial Intelligence (AI)-based module offers open interfaces to passive surveillance platforms, Decision Support Systems (DSSs), and early warning surveillance systems, establishing a seamless environment where innovation and utility converge to enhance crop health and productivity and biodiversity protection.

Full article

Figure 1

Open AccessCommunication

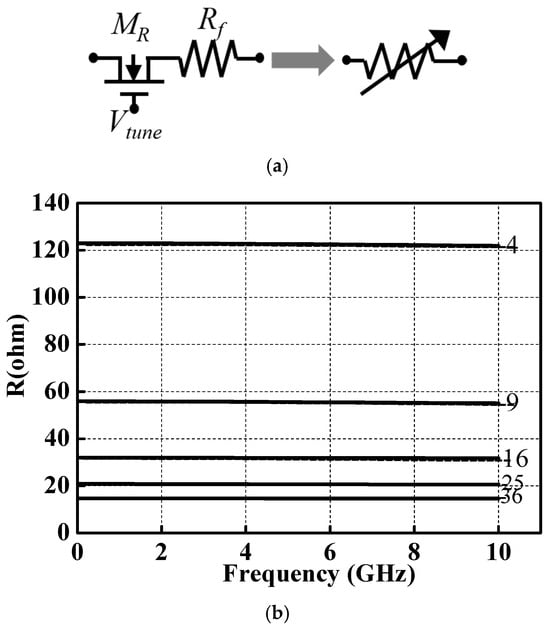

A Compact 0.73~3.1 GHz CMOS VCO Based on Active-Inductor and Active-Resistor Topology

by

Chatrpol Pakasiri, Ke-Chung Hsu and Sen Wang

J. Low Power Electron. Appl. 2024, 14(2), 18; https://doi.org/10.3390/jlpea14020018 - 25 Mar 2024

Abstract

In this paper, a wideband VCO that covers popular Long-Term Evolution (LTE) 0.7 GHz and LTE 2.6 GHz frequencies is designed and developed in a standard 0.18 μm CMOS process. The VCO utilizes active inductors to achieve coarse-tuning of the inductance and a

[...] Read more.

In this paper, a wideband VCO that covers popular Long-Term Evolution (LTE) 0.7 GHz and LTE 2.6 GHz frequencies is designed and developed in a standard 0.18 μm CMOS process. The VCO utilizes active inductors to achieve coarse-tuning of the inductance and a compact chip area. Moreover, an active feedback resistor is introduced into the active inductor for fine-tuning of the inductance. The feedback resistor also affects the equivalent resistance of the active inductor; therefore, wide inductance tuning and low power consumption can be obtained by optimizing the resistor. The core area of the fabricated CMOS chip is merely 0.046 mm2, excluding all testing pads. With a 6.7~10.1 mW DC consumption, the measured oscillation frequencies range from 0.73 GHz to 3.1 GHz, which demonstrates a 123.8% tuning range. At the frequencies of interest, the measured phase noises are from −80.7 to −84.5 dBc/Hz at a 1 MHz offset frequency.

Full article

(This article belongs to the Special Issue Analog/Mixed-Signal Integrated Circuit Design)

►▼

Show Figures

Figure 1

Open AccessArticle

A Simplified Gm − C Filter Technique for Reference Spur Reduction in Phase-Locked Loop

by

P. Purushothama Chary, Rizwan Shaik Peerla and Ashudeb Dutta

J. Low Power Electron. Appl. 2024, 14(1), 17; https://doi.org/10.3390/jlpea14010017 - 20 Mar 2024

Abstract

►▼

Show Figures

This paper presents a wideband approach for L5 and S-band integer-N phase-locked loop (PLL) targeting Indian Regional Navigation Satellite System (IRNSS) applications. A reference spur reduction technique using a

This paper presents a wideband approach for L5 and S-band integer-N phase-locked loop (PLL) targeting Indian Regional Navigation Satellite System (IRNSS) applications. A reference spur reduction technique using a

Figure 1

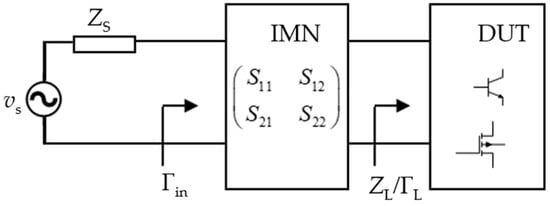

Open AccessCommunication

Design of Impedance Matching Network for Low-Power, Ultra-Wideband Applications

by

Sepideh Hassani, Chih-Hung Chen and Natalia K. Nikolova

J. Low Power Electron. Appl. 2024, 14(1), 16; https://doi.org/10.3390/jlpea14010016 - 19 Mar 2024

Abstract

►▼

Show Figures

This paper addresses the design of ultra-wideband (UWB) impedance matching networks operating in the unlicensed 3.1–10.6 GHz frequency band for low-power applications. It improves the simplified real frequency technique (SRFT) by adding a realizability check and employing an iterative approach with different initial

[...] Read more.

This paper addresses the design of ultra-wideband (UWB) impedance matching networks operating in the unlicensed 3.1–10.6 GHz frequency band for low-power applications. It improves the simplified real frequency technique (SRFT) by adding a realizability check and employing an iterative approach with different initial guesses in optimization to achieve realizable solutions under the requirements of UWB, low-power consumption, and a minimum number of circuit components. The comparison of solutions obtained using the SRFT with published solutions based on the Chebyshev filter theory is presented. It is shown that the optimal SRFT solution requires fewer components in the impedance matching network, maximizes the RF power delivery over the UWB spectrum with a reflection coefficient below −10 dB, and allows for circuit optimization to reduce power consumption. Using the improved SRFT, it demonstrates a systematic approach to find the strategies and limitations of designing the input matching networks for low-power UWB applications using GlobalFoundries 90 nm BiCMOS technology.

Full article

Figure 1

Open AccessArticle

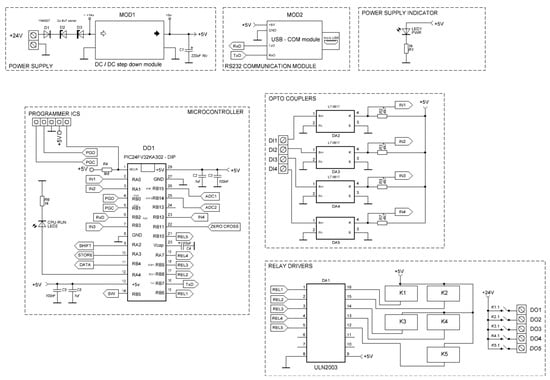

Control of Vibratory Feeder Device Mechanical Frequency Using the Modification of the Sinusoidal Supply Voltage Signal

by

Žydrūnas Kavaliauskas and Igor Šajev

J. Low Power Electron. Appl. 2024, 14(1), 15; https://doi.org/10.3390/jlpea14010015 - 06 Mar 2024

Abstract

►▼

Show Figures

In the industrial and sales processes, dosing systems of various constructions, whose operation is based on mechanical vibrations (vibratory feeders), are very often used. These systems face many problems, such as resonant frequency, flow instability of dosed product, instability of mechanical vibration amplitude,

[...] Read more.

In the industrial and sales processes, dosing systems of various constructions, whose operation is based on mechanical vibrations (vibratory feeders), are very often used. These systems face many problems, such as resonant frequency, flow instability of dosed product, instability of mechanical vibration amplitude, etc., because most of them are based on controlling the frequency of the electrical signal of the supply voltage. All these factors negatively affect the durability and reliability of the vibratory feeder systems. During this research, an automatic control system for vibratory feeder was created, whose control process is based on the modification of the sinusoidal signal (partially changing the signal area). In addition, such a way of controlling the vibratory feeder is not discussed in the literature. As the research conducted in this paper has shown, while using sinusoidal signal modification it was possible to achieve a stable flow rate of bulk production (the flow rate varied from 0 to 100 g/s when the frequency of mechanical vibrations changed from 1 to 50 Hz) and a stable amplitude of mechanical oscillations was achieved and equal to 1.5 mm. The control system is based on the microcontroller PIC24FV32KA302 for which the special software was developed. The thyristor BTA16 used for voltage modification of the sinusoidal signal made it possible to ensure the reliable control of the sinusoidal voltage modification process.

Full article

Figure 1

Open AccessArticle

CMOS Design of Chaotic Systems Using Biquadratic OTA-C Filters

by

Eduardo Juarez-Mendoza, Francisco Asahel del Angel-Diaz, Alejandro Diaz-Sanchez and Esteban Tlelo-Cuautle

J. Low Power Electron. Appl. 2024, 14(1), 14; https://doi.org/10.3390/jlpea14010014 - 04 Mar 2024

Abstract

►▼

Show Figures

This manuscript shows the CMOS design of Lorenz systems using operational transconductance amplifiers (OTAs). Two Lorenz systems are then synchronized in a master–slave topology and used to implement a CMOS secure communication system. The contribution is devoted to the correct design of first-

[...] Read more.

This manuscript shows the CMOS design of Lorenz systems using operational transconductance amplifiers (OTAs). Two Lorenz systems are then synchronized in a master–slave topology and used to implement a CMOS secure communication system. The contribution is devoted to the correct design of first- and second-order OTA-C filters, using 180 nm CMOS technology, to guarantee chaotic behavior. First, Simulink is used to simulate a secure communication system using two Lorenz systems connected in a master–slave topology, which is tested using sinusoidal signals that are masked by chaotic signals. Second, the Lorenz systems are scaled to have amplitudes of the state variables below 1 Volt, to allow for CMOS design using OTA-C filters. The transconductances of the OTAs are tuned to accomplish a Laplace transfer function. In this manner, this work highlights the design of a second-order CMOS OTA-C filter, whose damping factor is tuned to generate appropriate chaotic behavior. Finally, chaotic masking is performed by designing a whole CMOS secure communication system by using OTA-C based Lorenz systems, and its SPICE simulation results show its appropriateness for hardware security applications.

Full article

Figure 1

Open AccessArticle

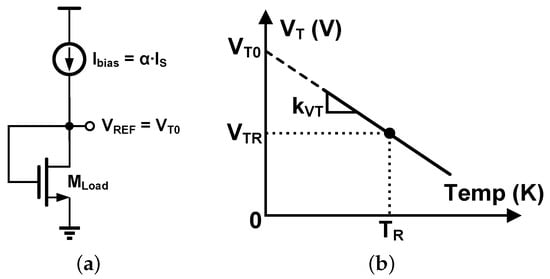

A Sub-1-V Nanopower MOS-Only Voltage Reference

by

Siqi Wang, Zhenghao Lu, Kunpeng Xu, Hongguang Dai, Zhanxia Wu and Xiaopeng Yu

J. Low Power Electron. Appl. 2024, 14(1), 13; https://doi.org/10.3390/jlpea14010013 - 29 Feb 2024

Abstract

A novel low-power MOS-only voltage reference is presented. The Enz–Krummenacher–Vittoz (EKV) model is adopted to provide a new perspective on the operating principle. The normalized charge density, introduced as a new variable, serves as an indicator when trimming the output temperature coefficient. The

[...] Read more.

A novel low-power MOS-only voltage reference is presented. The Enz–Krummenacher–Vittoz (EKV) model is adopted to provide a new perspective on the operating principle. The normalized charge density, introduced as a new variable, serves as an indicator when trimming the output temperature coefficient. The proposed voltage reference consists of a specific current generator and a 5-bit trimmable load. Thanks to the good match between the current source stage and the output stage, the nonlinear temperature dependence of carrier mobility is automatically canceled out. The circuit is designed using 55 nm COMS technology. The operating temperature ranges from −40

(This article belongs to the Special Issue Ultra-Low-Power ICs for the Internet of Things Vol. 2)

►▼

Show Figures

Figure 1

Open AccessArticle

A Low-Power BL Path Design for NAND Flash Based on an Existing NAND Interface

by

Hikaru Makino and Toru Tanzawa

J. Low Power Electron. Appl. 2024, 14(1), 12; https://doi.org/10.3390/jlpea14010012 - 19 Feb 2024

Abstract

►▼

Show Figures

This paper is an extended version of a previously reported conference paper regarding a low-power design for NAND Flash. As the number of bits per NAND Flash die increases with cost scaling, the IO data path speed increases to minimize the page access

[...] Read more.

This paper is an extended version of a previously reported conference paper regarding a low-power design for NAND Flash. As the number of bits per NAND Flash die increases with cost scaling, the IO data path speed increases to minimize the page access time with a scaled CMOS in IOs. The power supply for IO buffers, namely, VDDQ, decreases from 3 V to 1.2 V, accordingly. In this paper, the way in which a reduction in VDDQ can contribute to power reduction in the BL path is discussed and validated. Conventionally, a BL voltage of about 0.5 V has been supplied from a supply voltage source (VDD) of 3 V. The BL path power can be reduced by a factor of VDDQ to VDD when the BL voltage is supplied by VDDQ. To maintain a sense margin at the sense amplifiers, the supply source for BLs is switched from VDDQ to VDD before sensing. As a result, power reduction and an equivalent sense margin can be realized at the same time. The overhead of implementing this operation is an increase in the BL access time of about 2% for switching the power supply from VDDQ to VDD and an increase in the die size of about 0.01% for adding the switching circuit, both of which are not significant in comparison to the significant power reduction in the BL path power of the NAND die of about 60%. The BL path is then designed in 180 nm CMOS to validate the design. When the cost for powering the SSD becomes quite significant, especially for data centers, an additional lower voltage supply, such as 0.8 V, dedicated to BL charging for read and program verifying operations may be the best option for future applications.

Full article

Figure 1

Open AccessArticle

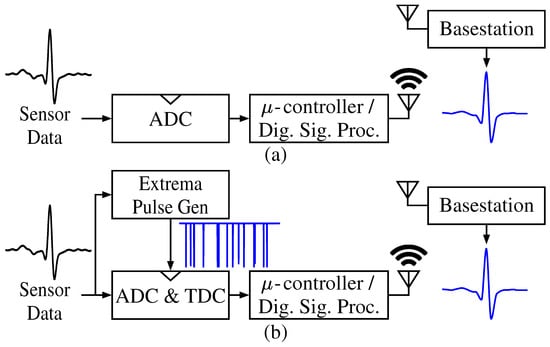

Extrema-Triggered Conversion for Non-Stationary Signal Acquisition in Wireless Sensor Nodes

by

Swagat Bhattacharyya and Jennifer O. Hasler

J. Low Power Electron. Appl. 2024, 14(1), 11; https://doi.org/10.3390/jlpea14010011 - 17 Feb 2024

Abstract

►▼

Show Figures

While wireless sensor node (WSNs) have proliferated with the rise of the Internet of Things (IoT), uniformly sampled analog–digital converters (ADCs) have traditionally reigned paramount in the signal processing pipeline. The large volume of data generated by uniformly sampled ADCs while capturing most

[...] Read more.

While wireless sensor node (WSNs) have proliferated with the rise of the Internet of Things (IoT), uniformly sampled analog–digital converters (ADCs) have traditionally reigned paramount in the signal processing pipeline. The large volume of data generated by uniformly sampled ADCs while capturing most real-world signals, which are highly non-stationary and sparse in information content, considerably strains the power budget of WSNs during data transmission. Given the pressing need for intelligent sampling, this work proposes an extrema pulse generator devised to trigger ADCs at significant signal extrema, thereby curbing the volume of data points collected and transmitted, and mitigating transmission power draw. After providing a comprehensive signal-theoretic rationale, we construct and experimentally validate these circuits on a system-on-chip field-programmable analog array in a 350 nm complementary metal-oxide-semiconductor (MOS) process. Operating within a power range of 4.3–12.3 µW (contingent on the input bandwidth requirements), the extrema pulse generator has proven to be capable of effectively sampling both synthetic and natural signals, achieving significant reductions in data volume and signal reconstruction error. Using a nonideality-resilient reconstruction algorithm, that we develop in this work, experimental comparisons between extrema and uniform sampling show that extrema sampling achieves an 18-fold lower normalized root mean square reconstruction error for a quadratic chirp signal, despite requiring 5-fold fewer sample points. Similar improvements in both the reconstruction error and effective sampling rate objectives are found experimentally for an electrocardiogram signal. Using both theoretical and experimental methods, this work demonstrates the potential of extrema-triggered systems for extending Pareto frontiers in modern, resource-constrained sensing scenarios.

Full article

Figure 1

Open AccessArticle

A Low-Power, 65 nm 24.6-to-30.1 GHz Trusted LC Voltage-Controlled Oscillator Achieving 191.7 dBc/Hz FoM at 1 MHz

by

Abdullah Kurtoglu, Amir H. M. Shirazi, Shahriar Mirabbasi and Hossein Miri Lavasani

J. Low Power Electron. Appl. 2024, 14(1), 10; https://doi.org/10.3390/jlpea14010010 - 02 Feb 2024

Abstract

►▼

Show Figures

This work presents a novel trusted LC voltage-controlled oscillator (VCO) with an embedded compact analog Physically Unclonable Function (PUF) used for authentication. The trusted VCO is implemented in a 1P9M 65 nm standard CMOS process and consumes 1.75 mW. It exhibits a measured

[...] Read more.

This work presents a novel trusted LC voltage-controlled oscillator (VCO) with an embedded compact analog Physically Unclonable Function (PUF) used for authentication. The trusted VCO is implemented in a 1P9M 65 nm standard CMOS process and consumes 1.75 mW. It exhibits a measured phase noise (PN) of −104.8 dBc/Hz @ 1 MHz and −132.2 dBc/Hz @ 10 MHz offset, resulting in Figures of Merit (FoMs) of 191.7 dBc/Hz and 199.1 dBc/Hz, respectively. With the measured frequency tuning range (TR) of ~5.5 GHz, the FoM with tuning (FoMT) reaches 197.6 dBc/Hz and 205.0 dBc/Hz at 1 MHz and 10 MHz offset, respectively. The analog PUF consists of CMOS cross-coupled pairs in the main VCO to change analog characteristics. Benefiting from the impedance change and parasitic capacitance of the cross-coupled pairs, the AC and DC responses of the VCO are utilized for multiple responses for each input. The PUF consumes 0.83 pJ/bit when operating at 1.5 Gbps. The proposed PUF exhibits a measured Inter-Hamming Distance (HD) of 0.5058b and 0.4978b, with Intra-HD reaching 0.0055b and 0.0053b for the current consumption and fosc, respectively. The autocorrelation function (ACF) of 0.0111 and 0.0110 is obtained for the current consumption and fosc, respectively, at a 95% confidence level.

Full article

Figure 1

Open AccessArticle

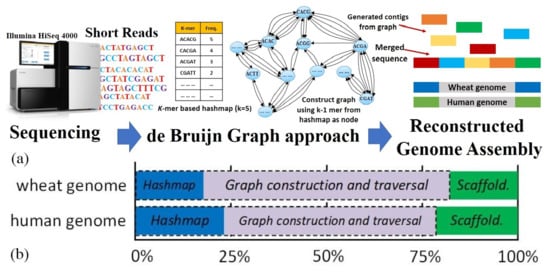

PANDA: Processing in Magnetic Random-Access Memory-Accelerated de Bruijn Graph-Based DNA Assembly

by

Shaahin Angizi, Naima Ahmed Fahmi, Deniz Najafi, Wei Zhang and Deliang Fan

J. Low Power Electron. Appl. 2024, 14(1), 9; https://doi.org/10.3390/jlpea14010009 - 02 Feb 2024

Abstract

►▼

Show Figures

In this work, we present an efficient Processing in MRAM-Accelerated De Bruijn Graph-based DNA Assembly platform, named PANDA, based on an optimized and hardware-friendly genome assembly algorithm. PANDA is able to assemble large-scale DNA sequence datasets from all-pair overlaps. We first design a

[...] Read more.

In this work, we present an efficient Processing in MRAM-Accelerated De Bruijn Graph-based DNA Assembly platform, named PANDA, based on an optimized and hardware-friendly genome assembly algorithm. PANDA is able to assemble large-scale DNA sequence datasets from all-pair overlaps. We first design a PANDA platform that exploits MRAM as computational memory and converts it to a potent processing unit for genome assembly. PANDA can not only execute efficient bulk bit-wise X(N)OR-based comparison/addition operations heavily required for the genome assembly task but also a full set of 2-/3-input logic operations inside the MRAM chip. We then develop a highly parallel and step-by-step hardware-friendly DNA assembly algorithm for PANDA that only requires the developed in-memory logic operations. The platform is then configured with a novel data partitioning and mapping technique that provides local storage and processing to utilize the algorithm level’s parallelism fully. The cross-layer simulation results demonstrate that PANDA reduces the run time and power by a factor of 18 and 11, respectively, compared with CPU. Moreover, speed-ups of up to 2.5 to 10× can be obtained over other recent processing in-memory platforms to perform the same task, like STT-MRAM, ReRAM, and DRAM.

Full article

Figure 1

Open AccessArticle

LC Tank Oscillator Based on New Negative Resistor in FDSOI Technology

by

Yuqing Mao, Yoann Charlon, Yves Leduc and Gilles Jacquemod

J. Low Power Electron. Appl. 2024, 14(1), 8; https://doi.org/10.3390/jlpea14010008 - 01 Feb 2024

Cited by 1

Abstract

►▼

Show Figures

Although Moore’s Law reaches its limits, it has never applied to analog and RF circuits. For example, due to the short channel effect (SCE), drain-induced barrier lowering (DIBL), and sub-threshold slope (SS)…, longer transistors are required to implement analog cells. From 22 nm

[...] Read more.

Although Moore’s Law reaches its limits, it has never applied to analog and RF circuits. For example, due to the short channel effect (SCE), drain-induced barrier lowering (DIBL), and sub-threshold slope (SS)…, longer transistors are required to implement analog cells. From 22 nm CMOS technology and beyond, for reasons of variability, the channel of the transistors has no longer been doped. Two technologies then emerged: FinFET transistors for digital applications and UTBB FDSOI transistors, suitable for analog and mixed applications. In a previous paper, a new topology was proposed utilizing some advantages of the FDSOI technology. Thanks to this technology, a novel cross-coupled back-gate (BG) technique was implemented to improve analog and mixed signal cells in order to reduce the surface of the integrated circuit. This technique was applied to a current mirror to reduce the small channel effect and to provide high-output impedance. It was demonstrated that it is possible to overcompensate the SCE and DIBL effects and to create a negative output resistor. This paper presents a new LC tank oscillator based on this current mirror functioning as a negative resistor.

Full article

Figure 1

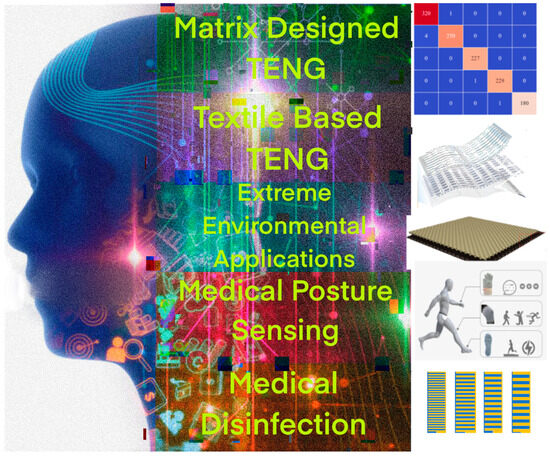

Open AccessReview

Array-Designed Triboelectric Nanogenerator for Healthcare Diagnostics: Current Progress and Future Perspectives

by

Zequan Zhao, Qiliang Zhu, Yifei Wang, Muhammad Shoaib, Xia Cao and Ning Wang

J. Low Power Electron. Appl. 2024, 14(1), 7; https://doi.org/10.3390/jlpea14010007 - 22 Jan 2024

Abstract

►▼

Show Figures

Array-designed triboelectric nanogenerators (AD-TENGs) have firmly established themselves as state-of-the-art technologies for adeptly converting mechanical interactions into electrical signals. Central to the AD-TENG’s prowess is its inherent modularity and the multifaceted, grid-like design that pave the way to robust and adaptable detection platforms

[...] Read more.

Array-designed triboelectric nanogenerators (AD-TENGs) have firmly established themselves as state-of-the-art technologies for adeptly converting mechanical interactions into electrical signals. Central to the AD-TENG’s prowess is its inherent modularity and the multifaceted, grid-like design that pave the way to robust and adaptable detection platforms for wearables and real-time health monitoring systems. In this review, we aim to elucidate the quintessential role of array design in AD-TENGs for healthcare detection, emphasizing its ability to heighten sensitivity, spatial resolution, and dynamic monitoring while ensuring redundancy and simultaneous multi-detection. We begin from the fundamental aspects, such as working principles and design basis, then venture into methodologies for optimizing AD-TENGs that ensure the capture of intricate physiological changes, from nuanced muscle movements to sensitive electronic skin. After this, our exploration extends to the possible cutting-edge electronic systems that are built with specific advantages in filtering noise, magnifying signal-to-noise ratios, and interpreting complex real-time datasets on the basis of AD-TENGs. Culminating our discourse, we highlight the challenges and prospective pathways in the evolution of array-designed AD-TENGs, stressing the necessity to refine their sensitivity, adaptability, and reliability to perfectly align with the exacting demands of contemporary healthcare diagnostics.

Full article

Figure 1

Open AccessArticle

Advancing Smart Lighting: A Developmental Approach to Energy Efficiency through Brightness Adjustment Strategies

by

Vandha Pradwiyasma Widartha, Ilkyeun Ra, Su-Yeon Lee and Chang-Soo Kim

J. Low Power Electron. Appl. 2024, 14(1), 6; https://doi.org/10.3390/jlpea14010006 - 15 Jan 2024

Abstract

►▼

Show Figures

Smart lighting control systems represent an advanced approach to reducing energy use. These systems leverage advanced technology to provide users with better control over their lighting, allowing them to manually, remotely, and automatically modify the brightness, color, and timing of their lights. In

[...] Read more.

Smart lighting control systems represent an advanced approach to reducing energy use. These systems leverage advanced technology to provide users with better control over their lighting, allowing them to manually, remotely, and automatically modify the brightness, color, and timing of their lights. In this study, we aimed to enhance the energy efficiency of smart lighting systems by using light source data. A multifaceted approach was employed, involving the following three scenarios: sensing device, daylight data, and a combination of both. A low-cost sensor and third-party API were used for data collection, and a prototype application was developed for real-time monitoring. The results showed that combining sensor and daylight data effectively reduced energy consumption, and the rule-based algorithm further optimized energy usage. The prototype application provided real-time monitoring and actionable insights, thus contributing to overall energy optimization.

Full article

Figure 1

Highly Accessed Articles

Latest Books

E-Mail Alert

News

Topics

Topic in

Applied Sciences, Designs, Electronics, Energies, JLPEA

Power Electronics Converters

Topic Editors: Mohsin Jamil, Yuanmao Ye, Tomasz PajchrowskiDeadline: 30 April 2024

Topic in

Electricity, Electronics, Energies, JLPEA, Sensors, Automation

Control and Optimization of Networked Microgrids

Topic Editors: Miao Yu, Zhejing BaoDeadline: 31 December 2024

Topic in

Energies, Applied Sciences, Electronics, JLPEA, Designs

Application of Innovative Power Electronic Technologies, 2nd Volume

Topic Editors: Ching-Ming Lai, Yitao LiuDeadline: 10 February 2025

Conferences

Special Issues

Special Issue in

JLPEA

Ultra-Low-Power ICs for the Internet of Things Vol. 2

Guest Editor: Orazio AielloDeadline: 31 May 2024

Special Issue in

JLPEA

Energy Aware Scientific Computing in Distributed Architectures, Low Power Processors and HPC Hybrid Systems

Guest Editor: Sanghamitra RoyDeadline: 30 June 2024

Special Issue in

JLPEA

Recent Advances in Spintronics

Guest Editors: Weigang Wang, Guozhong XingDeadline: 31 July 2024

Special Issue in

JLPEA

Energy Aware Solutions for Battery Management Systems

Guest Editors: Luca Crocetti, Roberto SalettiDeadline: 31 August 2024