A Performance of the Soft-Charging Operation in Series of Step-Up Power Switched-Capacitor Converters

Abstract

:1. Introduction

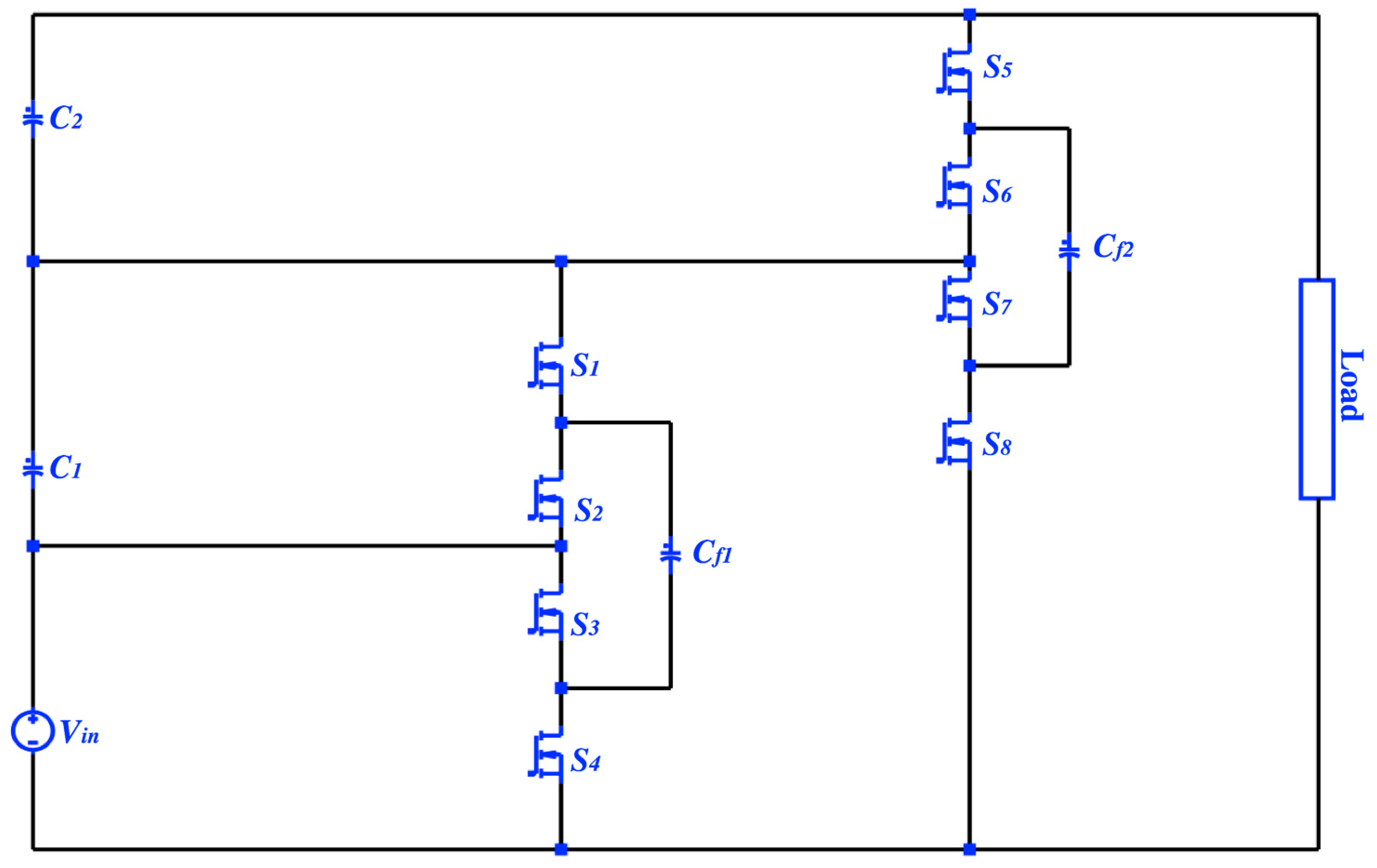

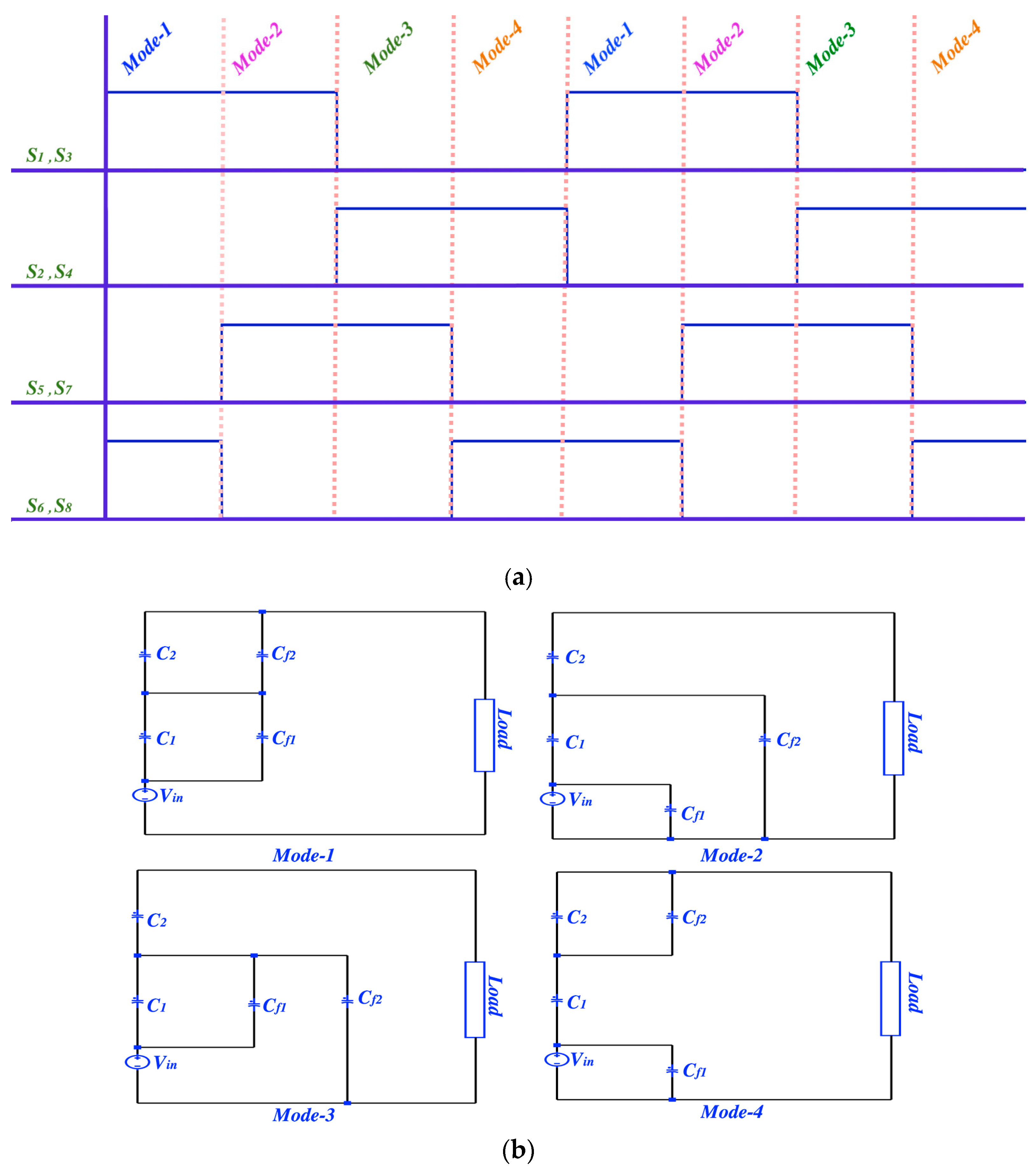

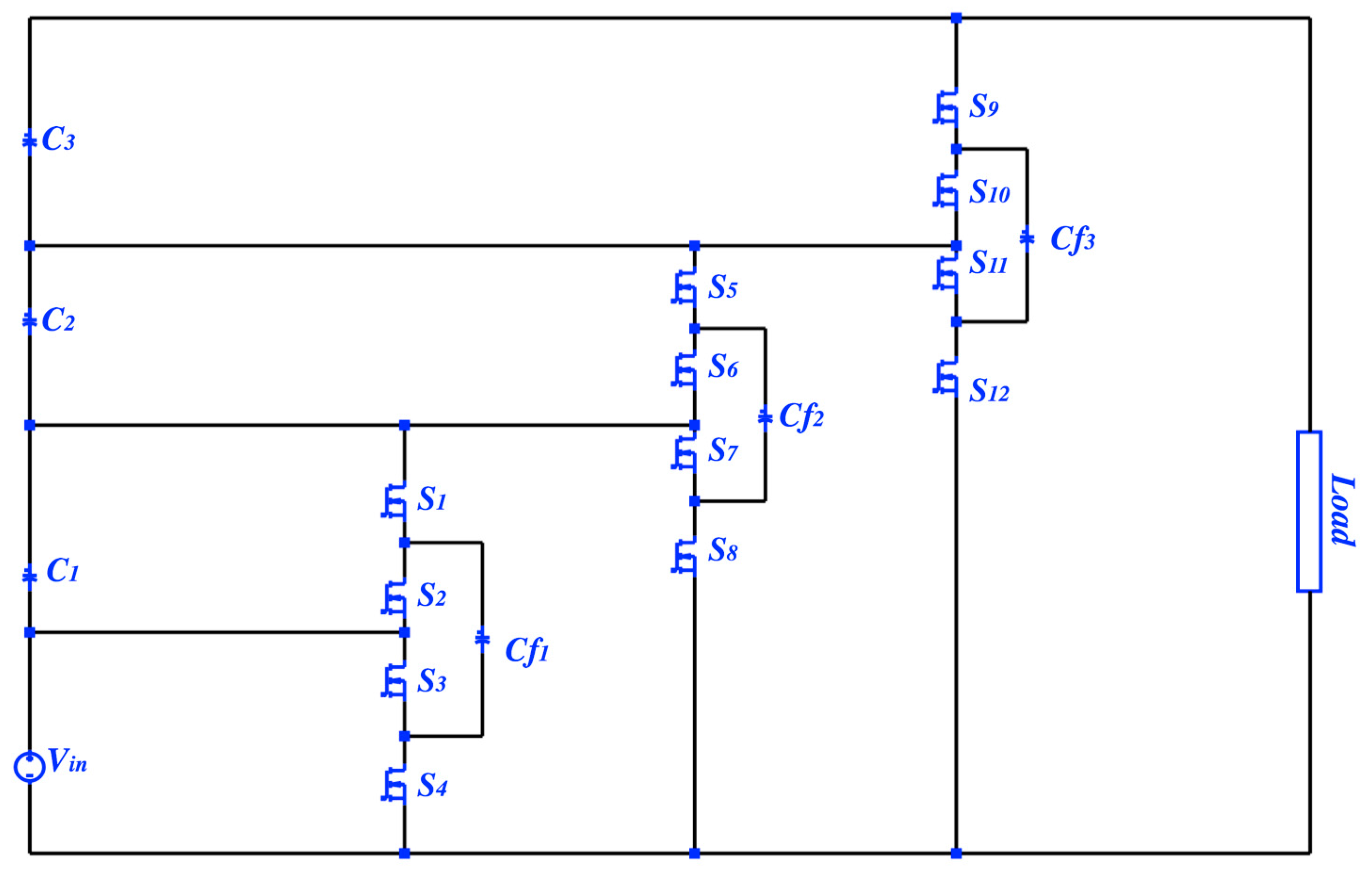

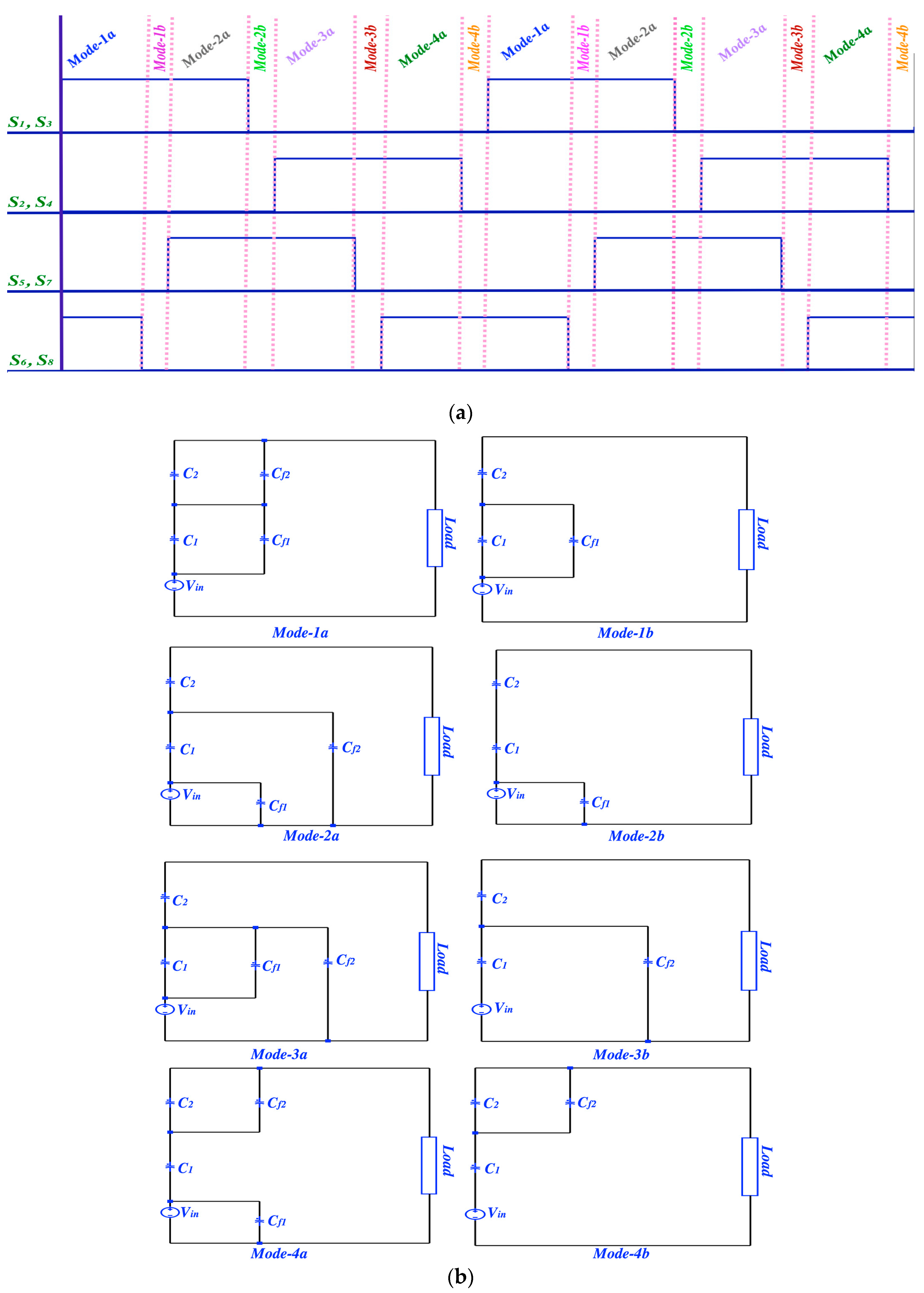

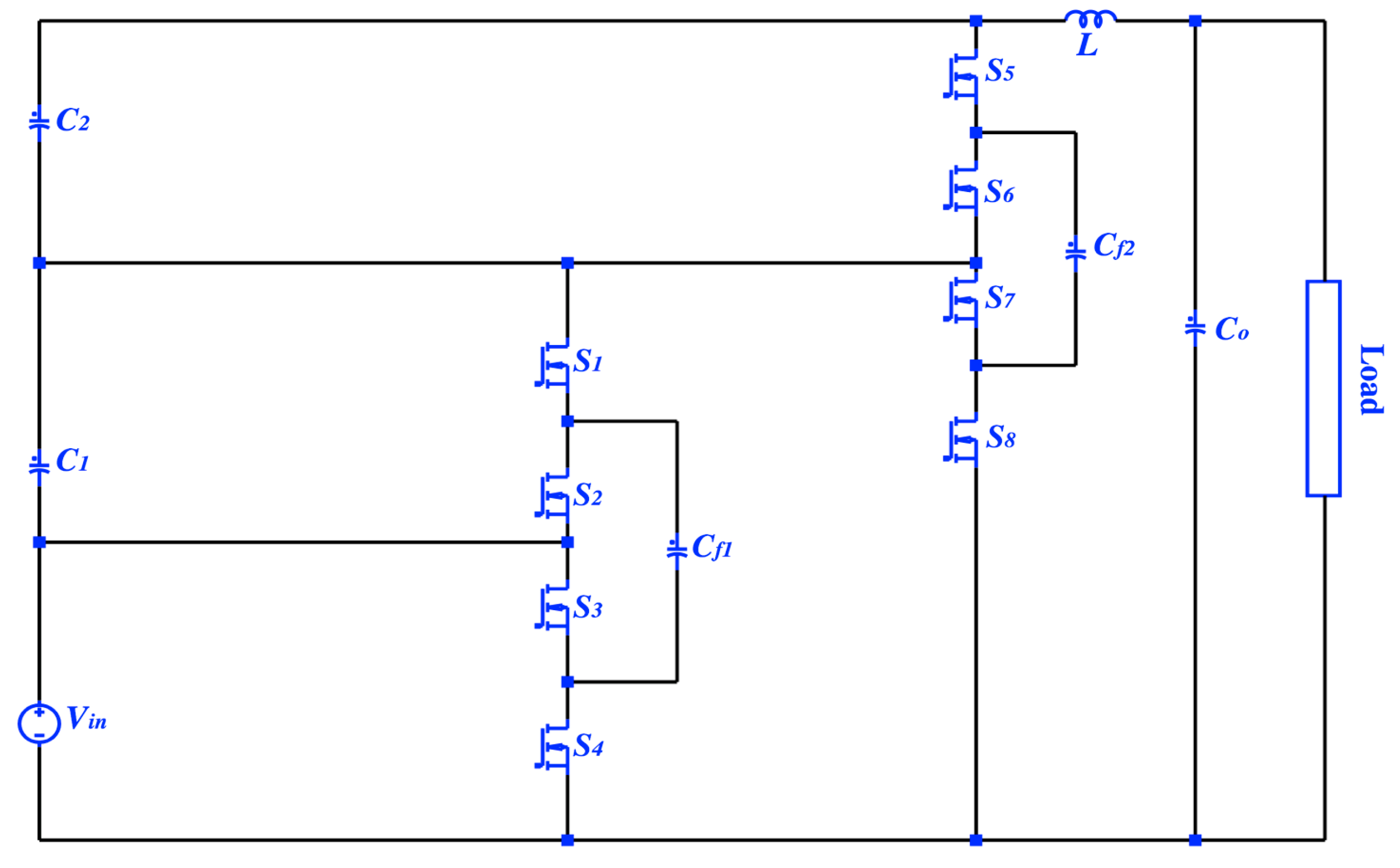

2. A Series of PSC Converters

2.1. A Second-Order PSC Converter; Topology and Operation

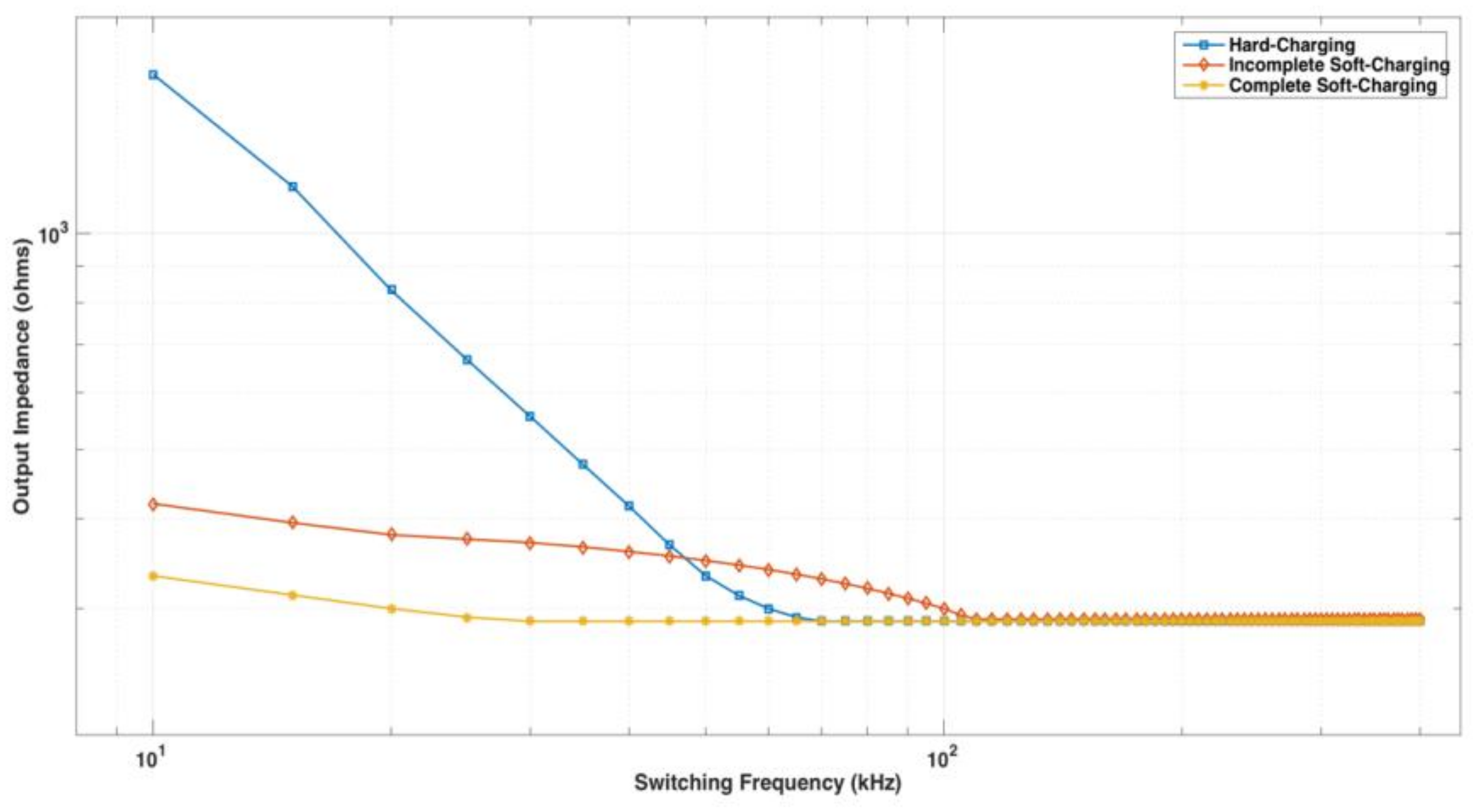

2.2. Slow-Switching Limit Impedance ()

2.3. Fast-Switching Limit Impedance

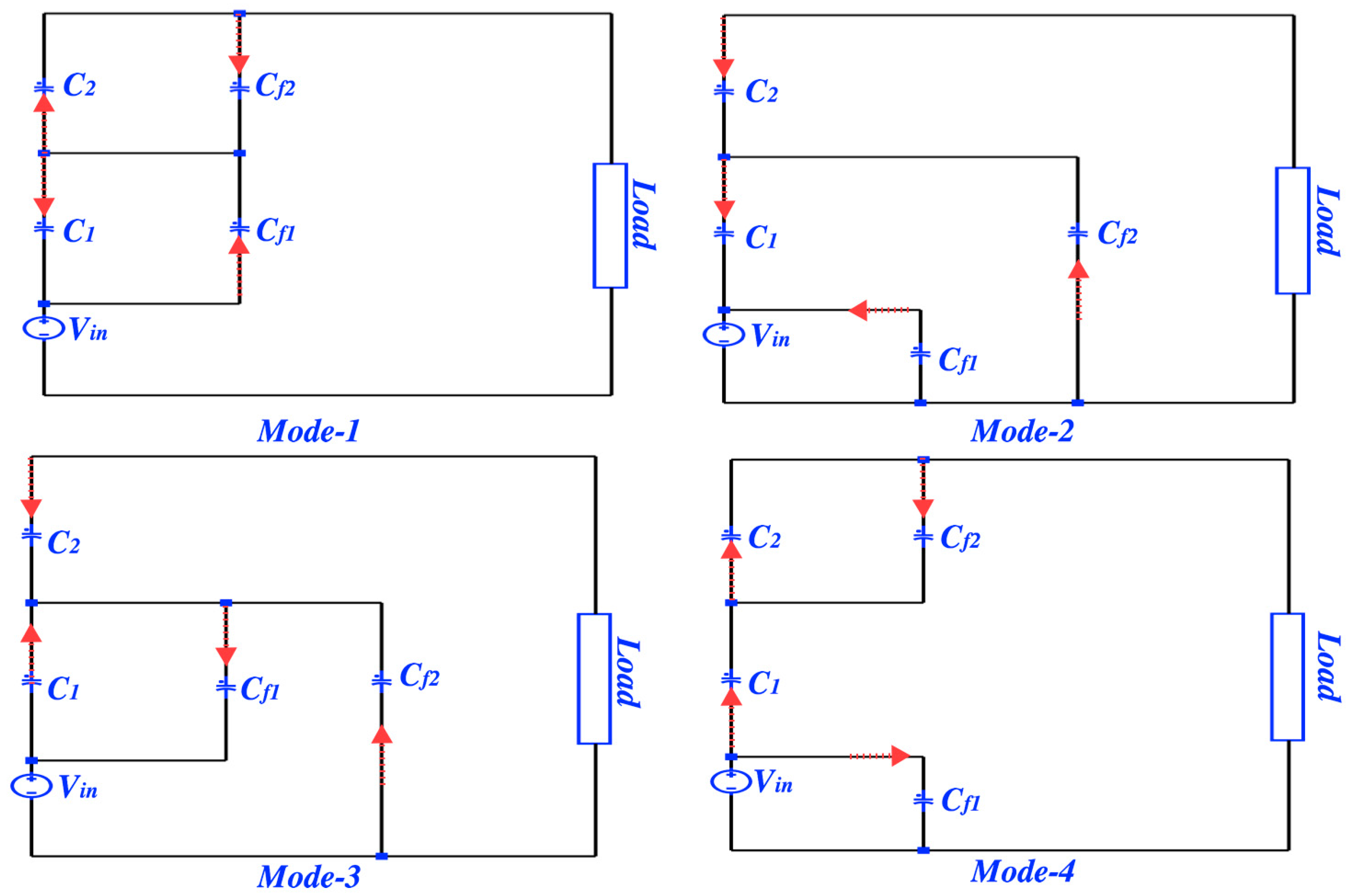

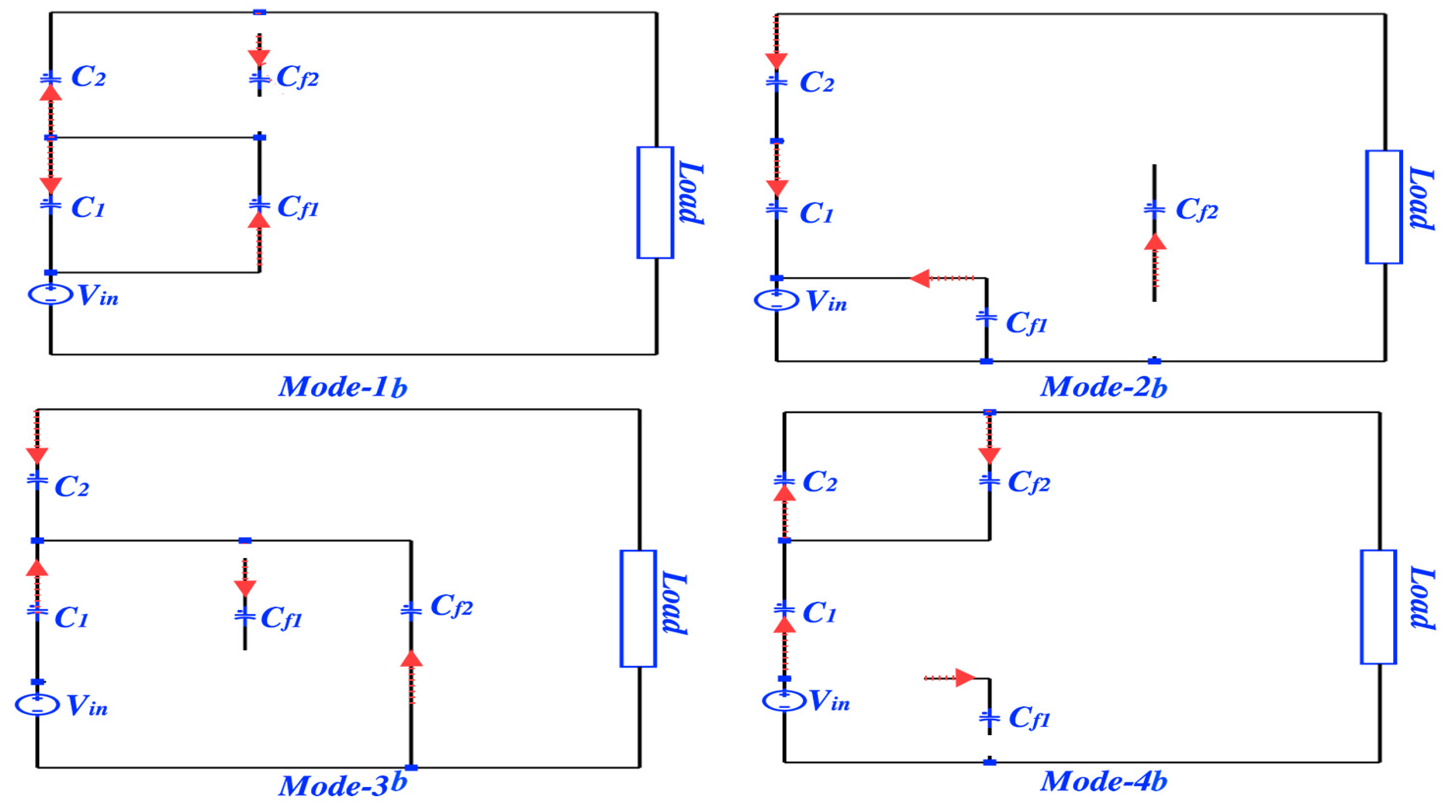

3. An Incomplete Soft-Charging Operation of the Second Order PSC Converter

4. A Complete Soft-Charging Operation of the Second Order PSC Converter

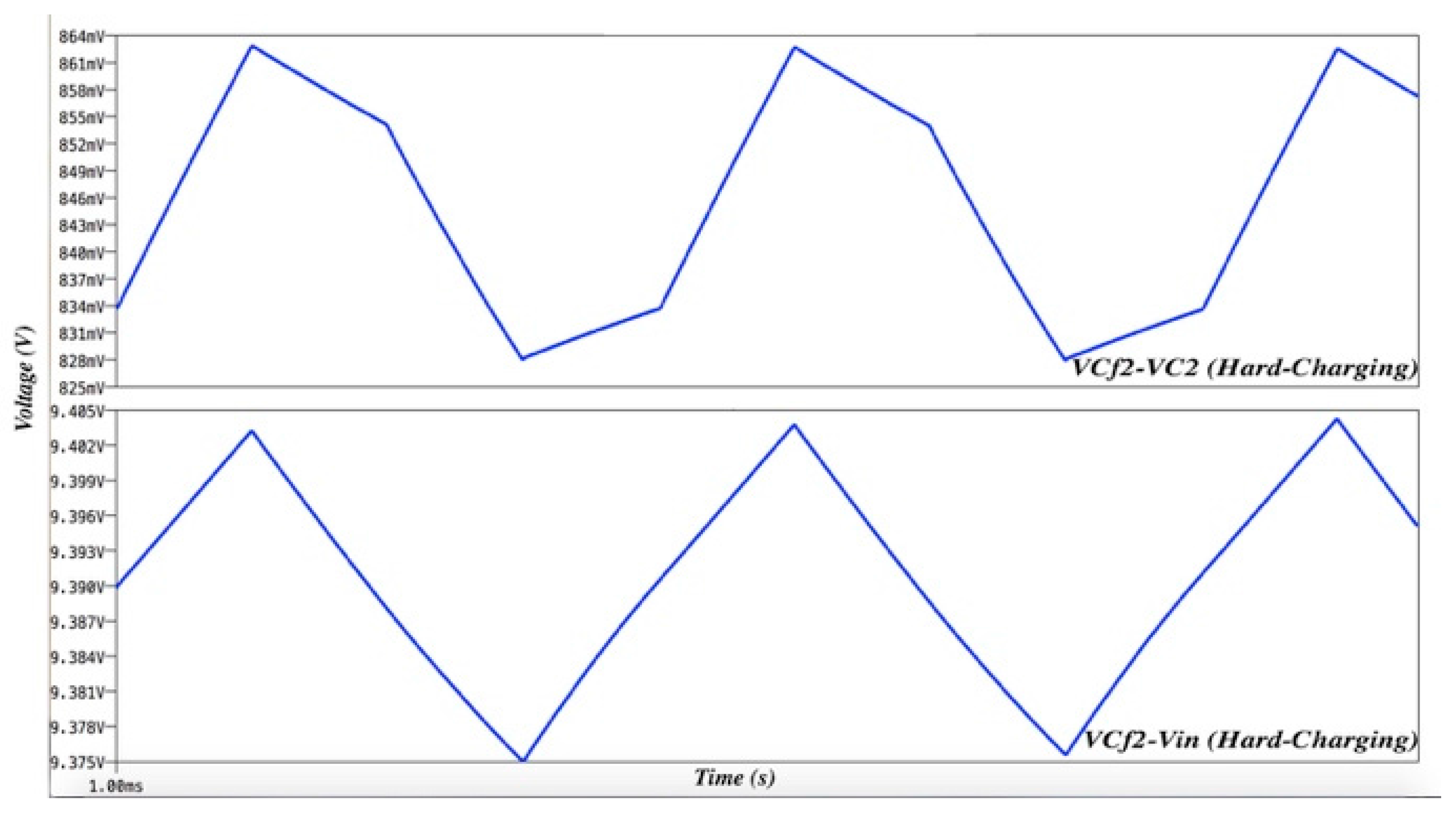

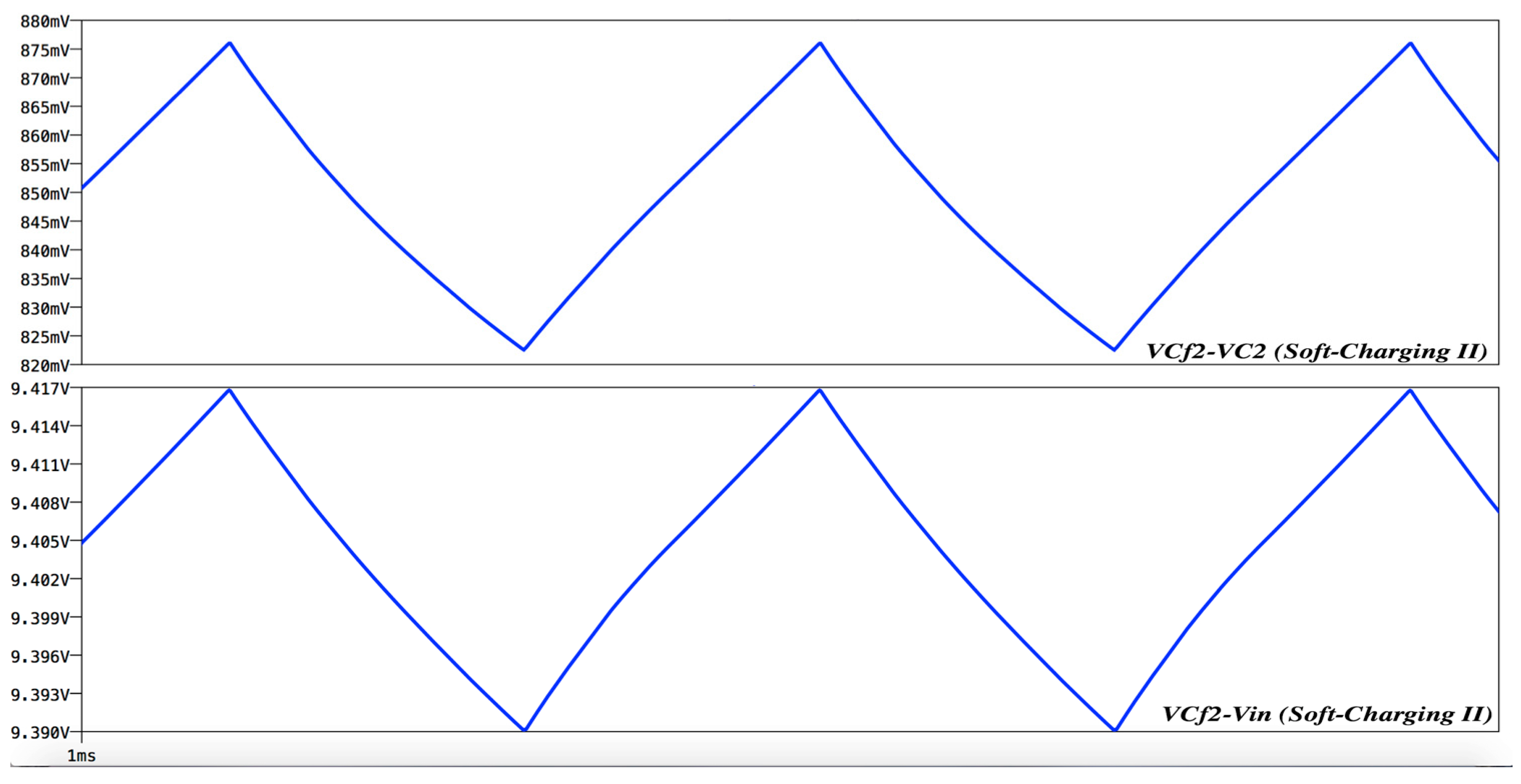

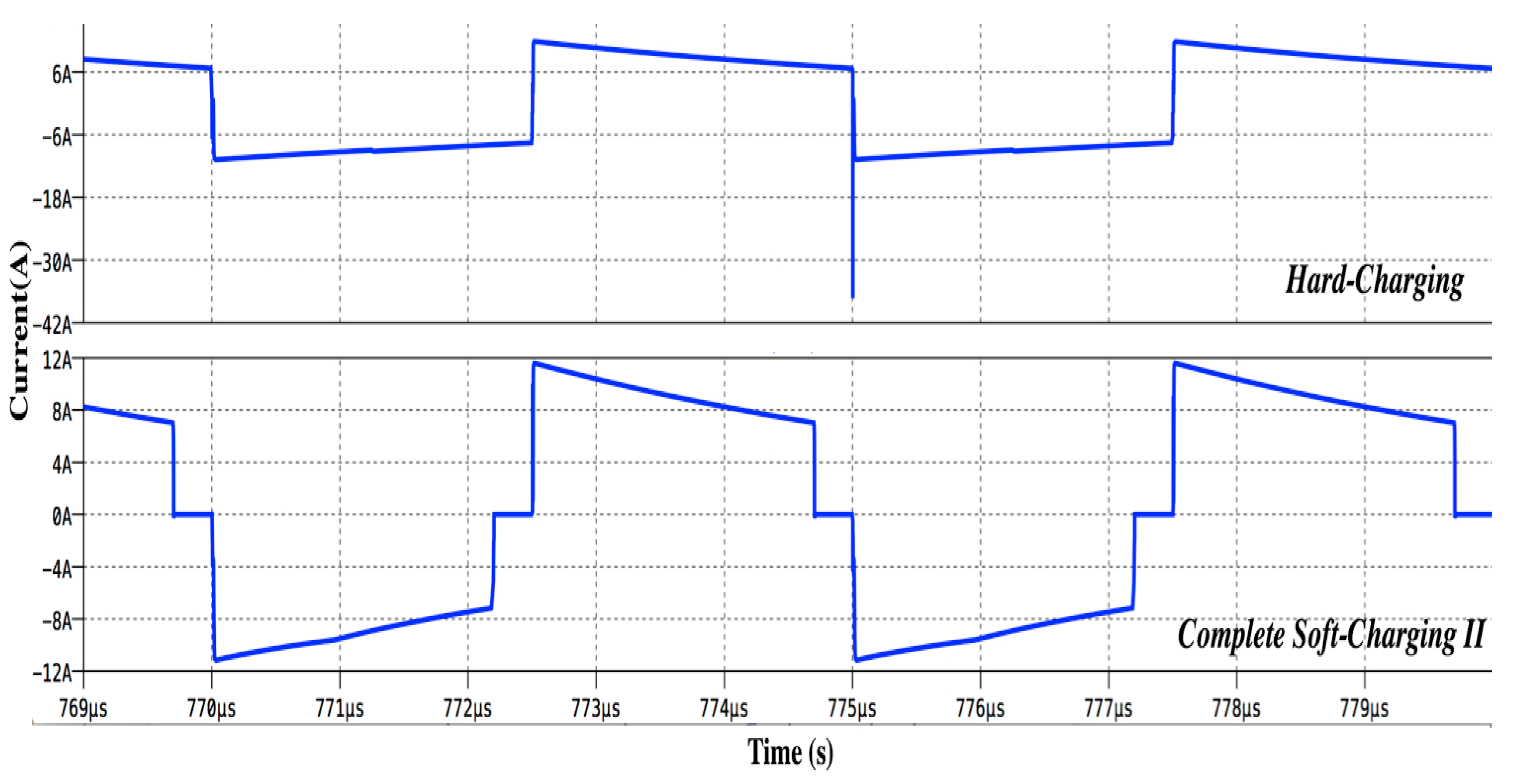

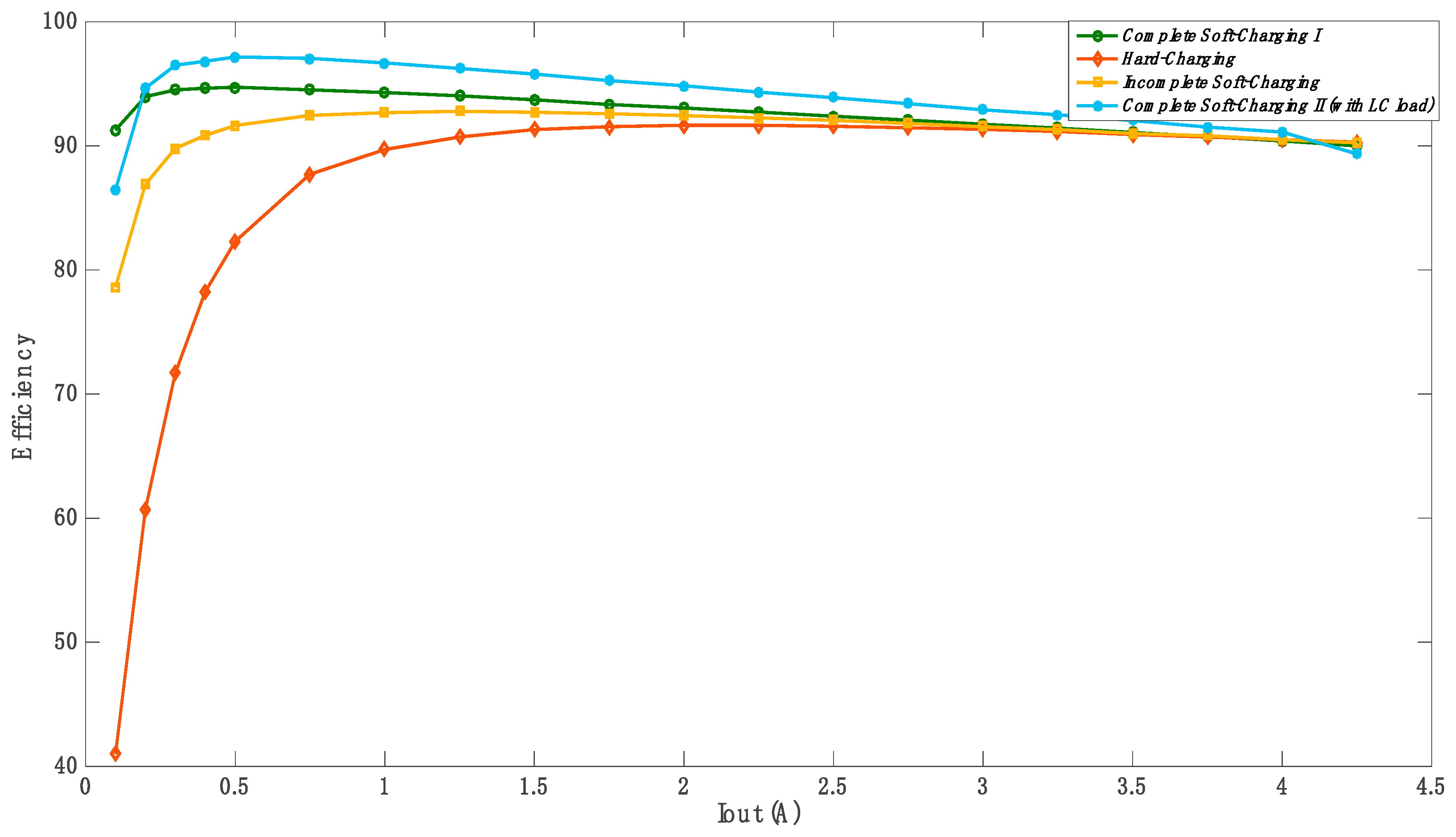

5. Results and Discussion

6. Conclusions

Acknowledgments

Author Contributions

Conflicts of Interest

References

- Almalaq, Y.; Alateeq, A.; Matin, M. Non-isolated high gain switched inductor DC-DC multilevel cuk converter for photovoltaic applications. In Proceedings of the 2017 North American Power Symposium (NAPS), Morgantown, WV, USA, 17–19 September 2017. [Google Scholar]

- Seeman, M.D.; Sanders, S.R. Analysis and Optimization of Switched-Capacitor DC–DC Converters. IEEE Trans. Power Electron. 2008, 23, 841–851. [Google Scholar] [CrossRef]

- Alateeq, A.; Almalaq, Y.; Matin, M. Using SiC MOSFET in switched-capacitor converter for high voltage applications. In Proceedings of the 2016 North American Power Symposium (NAPS), Denver, CO, USA, 18–20 September 2016; pp. 1–5. [Google Scholar]

- Xiong, S.; Wong, S.C.; Tan, S.C. A series of exponential step-down switched-capacitor converters and their applications in two-stage converters. In Proceedings of the 2013 IEEE International Symposium on Circuits and Systems (ISCAS2013), Beijing, China, 19–23 May 2013; pp. 701–704. [Google Scholar]

- Xiong, S.; Wong, S.C.; Tan, S.C.; Tse, C.K. Optimal Design of Complex Switched-Capacitor Converters via Energy-Flow-Path Analysis. IEEE Trans. Power Electron. 2017, 32, 1170–1185. [Google Scholar] [CrossRef]

- Xiong, S.; Wong, S.C.; Tan, S.C.; Tse, C.K. A Family of Exponential Step-Down Switched-Capacitor Converters and Their Applications in Two-Stage Converters. IEEE Trans. Power Electron. 2014, 29, 1870–1880. [Google Scholar] [CrossRef] [Green Version]

- Alateeq, A.S.; Almalaq, Y.A.; Matin, M.A. Modeling and simulation of GaN step-up power switched capacitor converter. In Proceedings of the Wide Bandgap Power Devices and Applications II, San Diego, CA, USA, 7–8 August 2017. [Google Scholar]

- Kesarwani, K.; Sangwan, R.; Stauth, J.T. Resonant-Switched Capacitor Converters for Chip-Scale Power Delivery: Design and Implementation. IEEE Trans. Power Electron. 2015, 30, 6966–6977. [Google Scholar] [CrossRef]

- Cheng, K. New generation of switched capacitor converters. In Proceedings of the 29th IEEE Annual Power Power Electronics Specialists Conference, Fukuoka, Japan, 22 May 1998; Volume 2, pp. 1529–1535. [Google Scholar]

- Zhang, Y.; Gao, Y.; Zhou, L.; Sumner, M. A Switched-Capacitor Bidirectional DC-DC Converter with Wide Voltage Gain Range for Electric Vehicles with Hybrid Energy Sources. IEEE Trans. Power Electron. 2018. [Google Scholar] [CrossRef]

- Keiser, O.; Steimer, P.K.; Kolar, J.W. High power resonant Switched-Capacitor step-down converter. In Proceedings of the 2008 IEEE Power Electronics Specialists Conference, Rhodes, Greece, 15–19 June 2008; pp. 2772–2777. [Google Scholar]

- Shang, Y.; Cui, N.; Zhang, Q.; Zhang, C. A battery equalizer with zero-current switching and zero-voltage gap among cells based on three-resonant-state LC converters. In Proceedings of the 2017 IEEE Applied Power Electronics Conference and Exposition (APEC), Tampa, FL, USA, 26–30 March 2017; pp. 1647–1651. [Google Scholar]

- Beiranvand, R. Regulating the Output Voltage of the Resonant Switched-Capacitor Converters below Their Resonant Frequencies. IEEE Trans. Ind. Electron. 2017, 64, 5236–5249. [Google Scholar] [CrossRef]

- Shen, M. A zero voltage switching switched capacitor voltage doubler. In Proceedings of the 2012 IEEE International Symposium on Industrial Electronics, Hangzhou, China, 28–31 May 2012; pp. 131–136. [Google Scholar]

- Lim, S.; Otten, D.M.; Perreault, D.J. Power conversion architecture for grid interface at high switching frequency. In Proceedings of the IEEE Applied Power Electronics Conference and Exposition, Fort Worth, TX, USA, 16–20 March 2014; pp. 1838–1845. [Google Scholar]

- Arntzen, B.; Maksimovic, D. Switched-capacitor DC/DC converters with resonant gate drive. IEEE Trans. Power Electron. 1998, 13, 892–902. [Google Scholar] [CrossRef]

- Yang, J.W.; Do, H.L. Soft-Switching Bidirectional DC-DC Converter Using a Lossless Active Snubber. IEEE Trans. Circuits Syst. I Regul. Pap. 2014, 61, 1588–1596. [Google Scholar] [CrossRef]

- Lei, Y.; Pilawa-Podgurski, R.C.N. Analysis of Switched-capacitor DC-DC Converters in Soft-charging Operation. In Proceedings of the 2013 IEEE 14th Workshop on Control and Modeling for Power Electronics (COMPEL), Salt Lake City, UT, USA, 23–26 June 2013; pp. 1–7. [Google Scholar]

- Lei, Y.; May, R.; Pilawa-Podgurski, R.C.N. Split-phase control: Achieving complete soft-charging operation of a dickson switched-capacitor converter. In Proceedings of the 2014 IEEE 15th Workshop on Control and Modeling for Power Electronics (COMPEL), Cantabria, Spain, 22–25 June 2014; pp. 1–7. [Google Scholar]

- Lei, Y.; Pilawa-Podgurski, R.C.N. A General Method for Analyzing Resonant and Soft-Charging Operation of Switched-Capacitor Converters. IEEE Trans. Power Electron. 2015, 30, 5650–5664. [Google Scholar] [CrossRef]

- May, R. Analysis of Soft Charging Switched Capacitor Power Converters. Master’s Thesis, University of Illinois, Urbana Champaign, IL, USA, August 2013. [Google Scholar]

- Lei, Y.; May, R.; Pilawa-Podgurski, R. Split-Phase Control: Achieving Complete Soft-Charging Operation of a Dickson Switched-Capacitor Converter. IEEE Trans. Power Electron. 2016, 31, 770–782. [Google Scholar] [CrossRef]

- Lei, Y. High Performance Power Converters Leveraging Capacitor-Based Energy Transfer. Ph.D. Thesis, University of Illinois, Urbana Champaign, IL, USA, 2017. [Google Scholar]

- Chua, L.O.; Desoer, C.A.; Kuh, E.S. Linear and Nonlinear Circuits; McGraw-Hill Book Company: New York, NY, USA, 1987. [Google Scholar]

- Henry, J.M.; Kimball, J.W. Switched-Capacitor Converter State Model Generator. IEEE Trans. Power Electron. 2012, 27, 2415–2425. [Google Scholar] [CrossRef]

| Elements | Equation |

|---|---|

| Parameter | Value |

|---|---|

| 10 V | |

| 200 KHz | |

| 188 µF | |

| 94 µF | |

| 188 µF | |

| 20 µF | |

| 40 µF | |

| 200 µF | |

| L of LC filter | 50 nH |

© 2018 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Alateeq, A.; Almalaq, Y.; Matin, M. A Performance of the Soft-Charging Operation in Series of Step-Up Power Switched-Capacitor Converters. J. Low Power Electron. Appl. 2018, 8, 8. https://doi.org/10.3390/jlpea8010008

Alateeq A, Almalaq Y, Matin M. A Performance of the Soft-Charging Operation in Series of Step-Up Power Switched-Capacitor Converters. Journal of Low Power Electronics and Applications. 2018; 8(1):8. https://doi.org/10.3390/jlpea8010008

Chicago/Turabian StyleAlateeq, Ayoob, Yasser Almalaq, and Mohammad Matin. 2018. "A Performance of the Soft-Charging Operation in Series of Step-Up Power Switched-Capacitor Converters" Journal of Low Power Electronics and Applications 8, no. 1: 8. https://doi.org/10.3390/jlpea8010008

APA StyleAlateeq, A., Almalaq, Y., & Matin, M. (2018). A Performance of the Soft-Charging Operation in Series of Step-Up Power Switched-Capacitor Converters. Journal of Low Power Electronics and Applications, 8(1), 8. https://doi.org/10.3390/jlpea8010008