Common-Mode Voltage Reduction Algorithm for Photovoltaic Grid-Connected Inverters with Virtual-Vector Model Predictive Control

Abstract

:1. Introduction

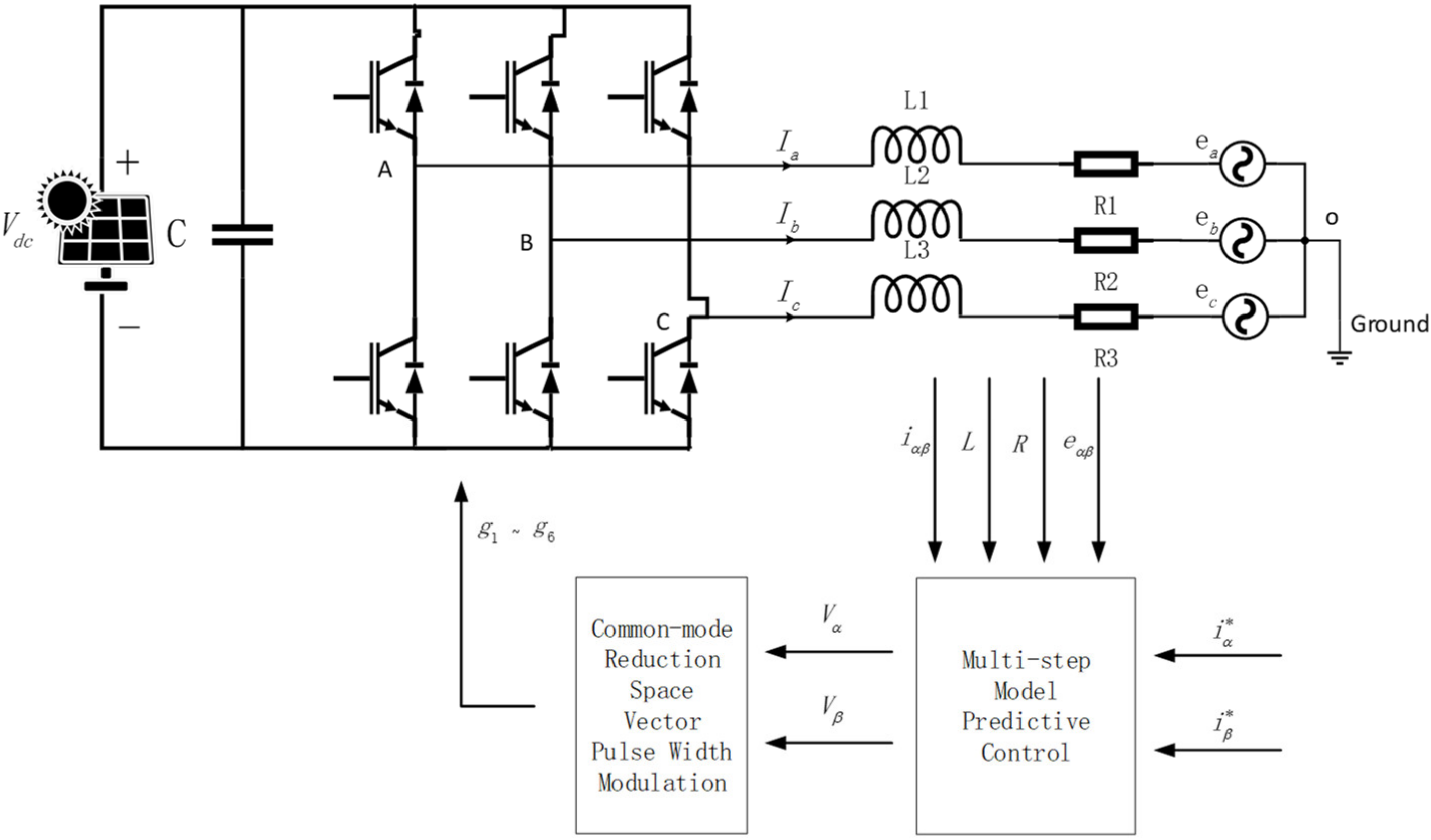

2. Virtual-Vector MPC

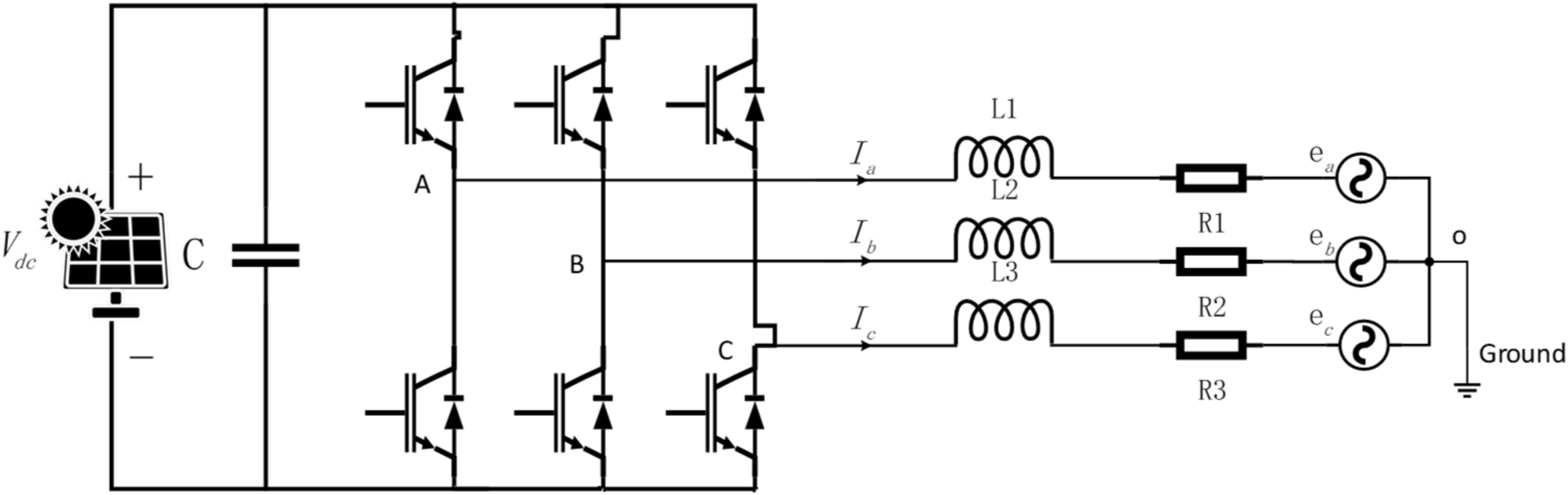

2.1. Three-Phase PV VSI Model

2.2. Model Predictive Control of VSI

2.3. CMV of Basic Voltage Vectors

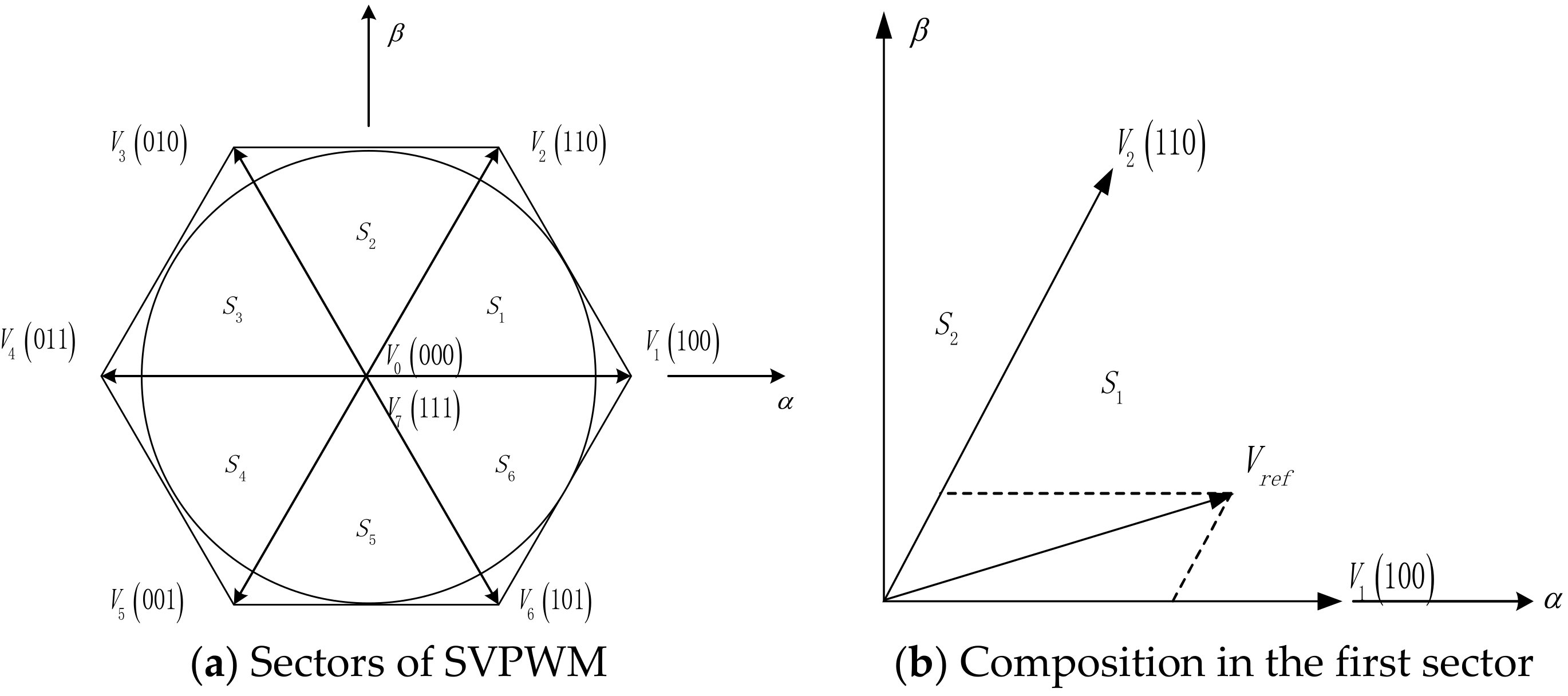

2.4. Conventional Modulation Method

3. Proposed CMRSVPWM Methods for VSI

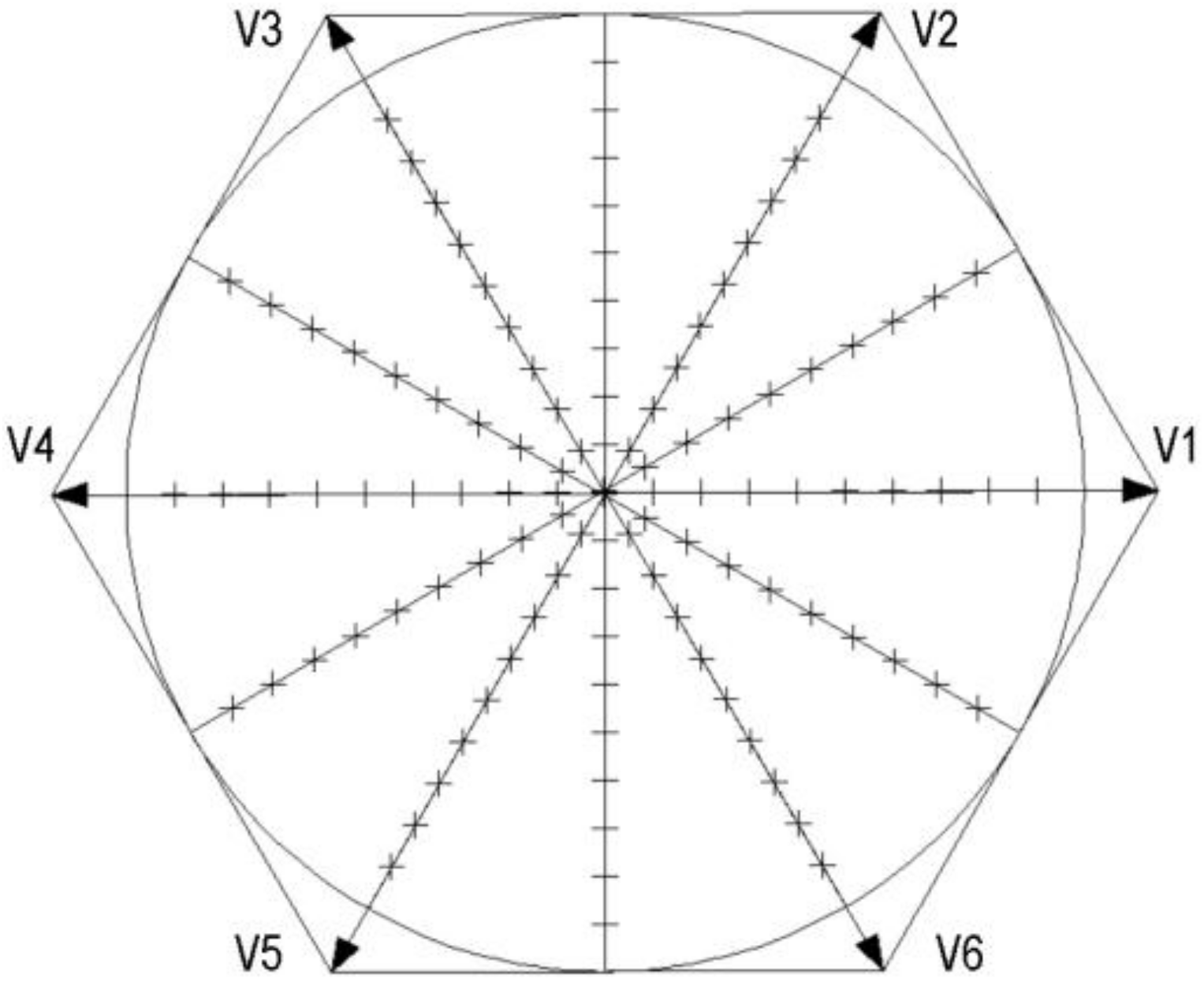

3.1. Sectors of CMRSVPWM

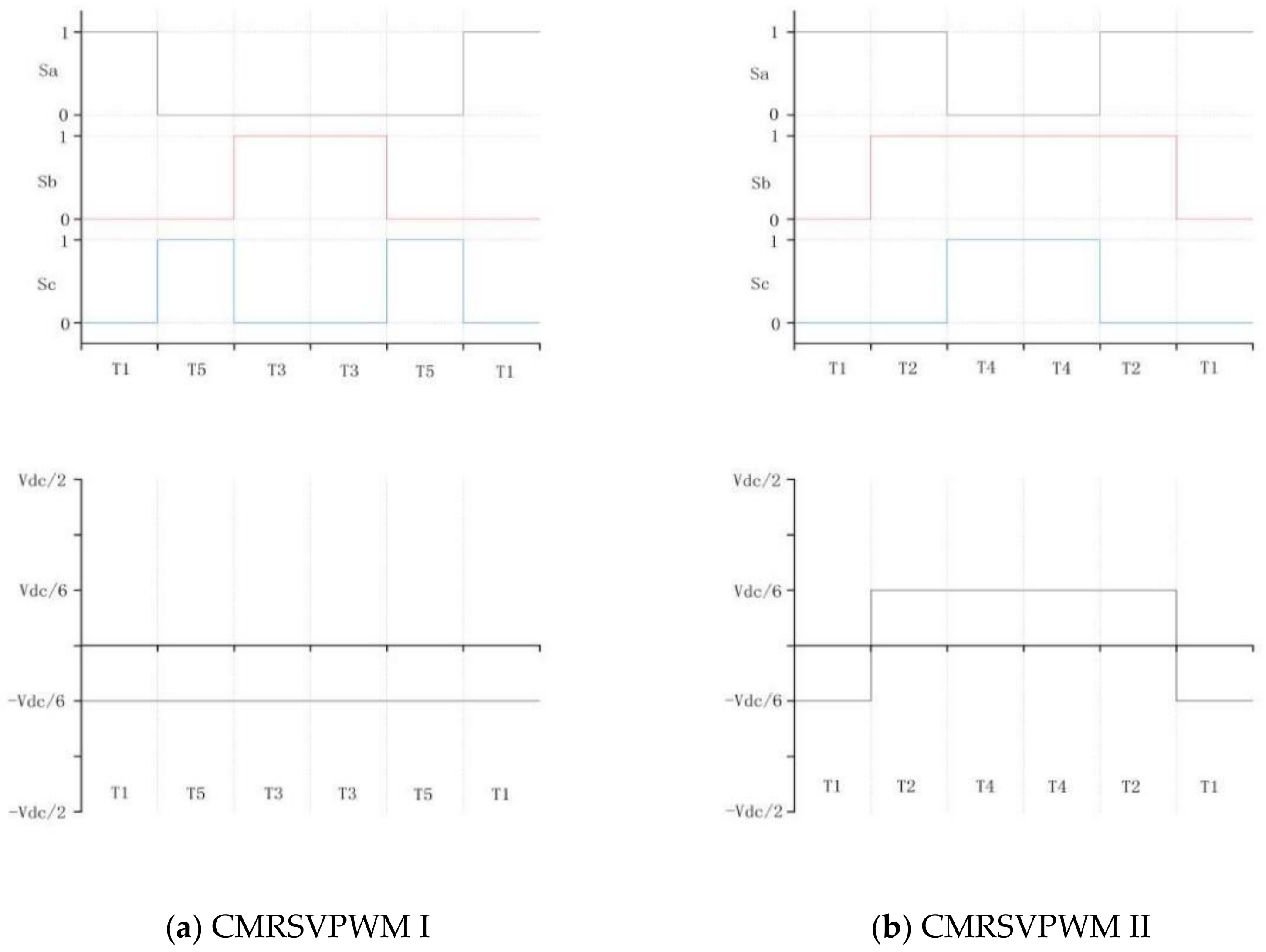

3.2. CMRSVPWM I

3.3. CMRSVPWM II

4. Experimental Result and Discussion

4.1. Virtual-Vector MPC

4.2. CMV Simulation

5. Conclusions

- (1)

- In comparison to the SVPWM, the enhanced CMRSVPWM strategy decreases the CMV amplitude from to , a reduction of 66.67%. The CMV toggling frequency is reduced to either 0 or 2.

- (2)

- In comparison with the PWM techniques with either three odd or three even vectors, the proposed CMRSVPWM I will increase the utilization rate of the DC bus by 15.47%, reaching . The utilization rate is increased further through CMRSVPWM II, up to the maximum available rate as that of SVPWM.

- (3)

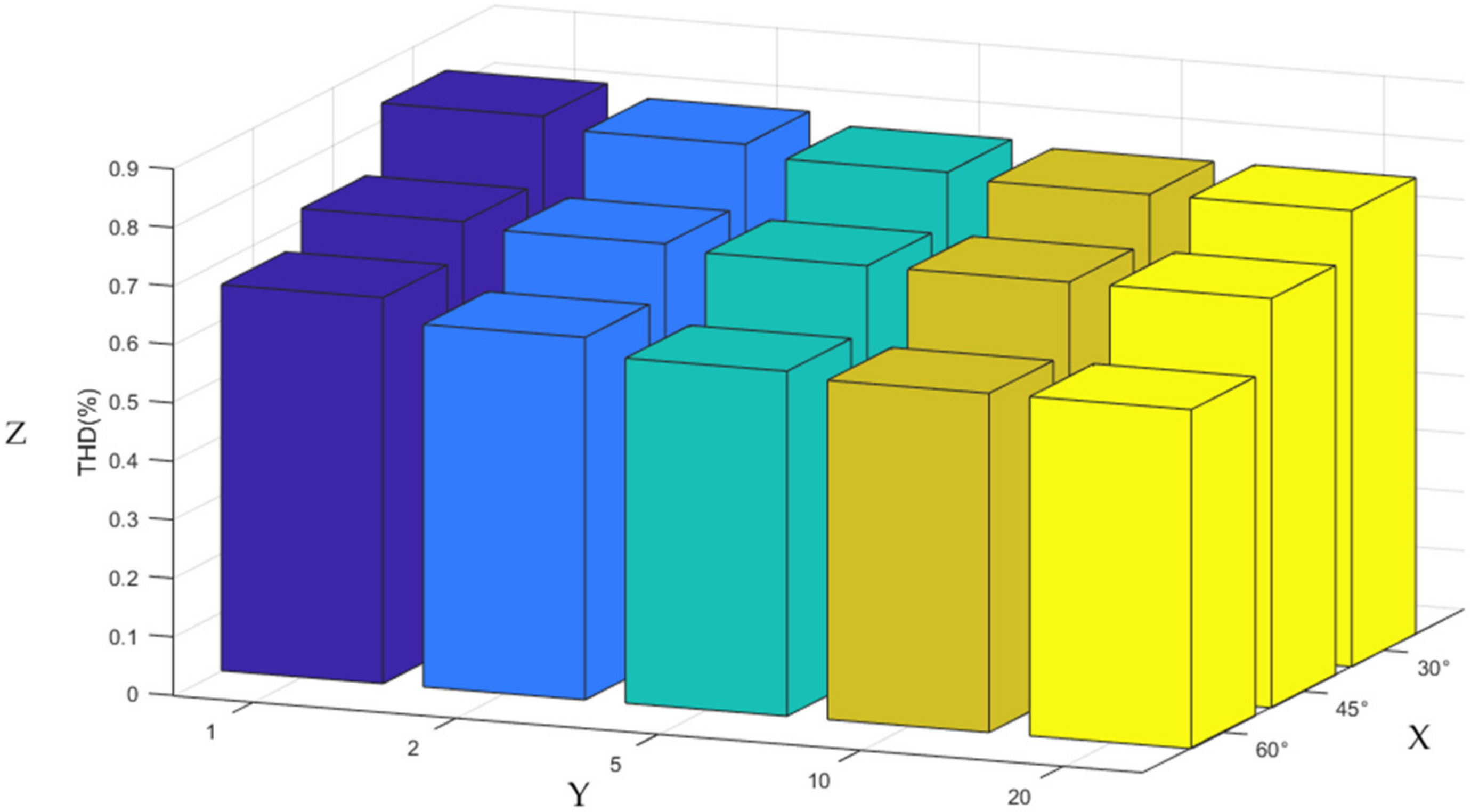

- Through virtual-vector MPC with 120 sub-vectors, the entire range of CMRSVPWM can be utilized to output switching harmonic performance.

6. Deficiencies and Prospects

Author Contributions

Funding

Conflicts of Interest

Appendix A

| VSI | Voltage Source Inverter | SVPWM | Space Vector Pulse Width Modulation |

| MPC | Model Predictive Control | AZSPWM | Zero-State Switch Pulse Width Modulation |

| CMV | Common-Mode Voltage | NSPWM | Near-State Pulse Width Modulation |

| PWM | Pulse Width Modulation | RSPWM | Remote-State Pulse Width Modulation |

| THD | Total Harmonic Distortion | CMRSVPWM | Common-Mode Reduction Space Vector Pulse Width Modulation |

| Output voltage of PV | Currents in | ||

| Inverter output voltages | Reference current values on axis | ||

| Inverter output currents | Sampling time | ||

| Grid voltages | Filter value | ||

| Output currents on coordinate system | Filter’s internal resistance | ||

| Output voltage from different switching states | Common-mode voltage value | ||

| Phase difference of | Voltage between the phase-A output of the inverter and the DC neutral point | ||

| States of switch | Sampling time of one cycle | ||

| Feedback values of axis currents at the current time | Corresponding action times of voltage vectors | ||

| Grid voltage values of axis at the current moment | Modulation index | ||

| Predicted values of axis currents at the next moment |

References

- Ferreira, S.C.; Gonzatti, R.B.; Pereira, R.R.; da Silva, C.H.; da Silva, L.E.B.; Lambert-Torres, G. Finite Control Set Model Predictive Control for Dynamic Reactive Power Compensation with Hybrid Active Power Filters. IEEE Trans. Ind. Electron. 2018, 65, 2608–2617. [Google Scholar] [CrossRef]

- Jayaraman, K.; Kumar, M. Design of Passive Common-Mode Attenuation Methods for Inverter-Fed Induction Motor Drive With Reduced Common-Mode Voltage PWM Technique. IEEE Trans. Power Electron. 2020, 35, 2861–2870. [Google Scholar] [CrossRef]

- Chen, K.; Hsieh, M. Generalized Minimum Common-Mode Voltage PWM for Two-Level Multiphase VSIs Considering Reference Order. IEEE Trans. Power Electron. 2017, 32, 6493–6509. [Google Scholar] [CrossRef]

- Chen, X.; Xu, D.; Liu, F.; Zhang, J. A Novel Inverter-Output Passive Filter for Reducing Both Differential- and Common-Mode dv/dt at the Motor Terminals in PWM Drive Systems. IEEE Trans. Ind. Electron. 2007, 54, 419–426. [Google Scholar] [CrossRef]

- Duong, T.-D.; Nguyen, M.-K.; Tran, T.-T.; Lim, Y.-C.; Choi, J.-H.; Wang, C. Modulation Techniques for a Modified Three-Phase Quasi-Switched Boost Inverter with Common-Mode Voltage Reduction. IEEE Access 2020, 8, 160670–160683. [Google Scholar] [CrossRef]

- Kwak, S.; Mun, S. Model Predictive Control Methods to Reduce Common-Mode Voltage for Three-Phase Voltage Source Inverters. IEEE Trans. Power Electron. 2015, 30, 5019–5035. [Google Scholar] [CrossRef]

- Xue, C.; Ding, L.; Li, Y.R. Model Predictive Control with Reduced Common-Mode Current for Transformerless Current-Source PMSM Drives. IEEE Trans. Power Electron. 2021, 36, 8114–8127. [Google Scholar] [CrossRef]

- Guo, L.; Jin, N.; Gan, C.; Xu, L.; Wang, Q. An Improved Model Predictive Control Strategy to Reduce Common-Mode Voltage for Two-Level Voltage Source Inverters Considering Dead-Time Effects. IEEE Trans. Ind. Electron. 2019, 66, 3561–3572. [Google Scholar] [CrossRef]

- Guo, L.; Jin, N.; Gan, C.; Luo, K. Hybrid Voltage Vector Preselection-Based Model Predictive Control for Two-Level Voltage Source Inverters to Reduce the Common-Mode Voltage. IEEE Trans. Ind. Electron. 2020, 67, 4680–4691. [Google Scholar] [CrossRef]

- Qi, C.; Chen, X.; Tu, P.; Wang, P. Cell-by-Cell-Based Finite-Control-Set Model Predictive Control for a Single-Phase Cascaded H-Bridge Rectifier. IEEE Trans. Power Electron. 2018, 33, 1654–1665. [Google Scholar] [CrossRef]

- Jeong, W.-S.; Choo, K.-M.; Lee, J.-H.; Won, C.-Y. A Common-Mode Voltage Reduction Method of FCS-MPC in H8 Inverter for SPMSM Drive System Considering Dead-Time Effect. In Proceedings of the 10th International Conference on Power Electronics and ECCE Asia (ICPE 2019-ECCE Asia), Busan, Korea, 27–31 May 2019; pp. 1–8. [Google Scholar] [CrossRef]

- Yu, B.; Song, W.; Li, J.; Li, B.; Saeed, M.S.R. Improved Finite Control Set Model Predictive Current Control for Five-Phase VSIs. IEEE Trans. Power Electron. 2021, 36, 7038–7048. [Google Scholar] [CrossRef]

- Cacciato, M.; Consoli, A.; Scarcella, G.; Testa, A. Reduction of common-mode currents in PWM inverter motor drives. IEEE Trans. Ind. Appl. 1999, 35, 469–476. [Google Scholar] [CrossRef]

- Hava, A.M.; Ün, E. Performance Analysis of Reduced Common-Mode Voltage PWM Methods and Comparison with Standard PWM Methods for Three-Phase Voltage-Source Inverters. IEEE Trans. Power Electron. 2009, 24, 241–252. [Google Scholar] [CrossRef]

- Un, E.; Hava, A.M. A Near-State PWM Method with Reduced Switching Losses and Reduced Common-Mode Voltage for Three-Phase Voltage Source Inverters. IEEE Trans. Ind. Appl. 2009, 45, 782–793. [Google Scholar] [CrossRef]

- Zheng, J.; Lyu, M.; Li, S.; Luo, Q.; Huang, K. Common-mode reduction SVPWM for three-phase motor fed by two-level voltage source inverter. Energies 2020, 13, 3884. [Google Scholar] [CrossRef]

- Vazquez, G.; Hernandez-Avila, I.; Sosa, J.M.; Limones-Pozos, C.A.; Arau, J. A Comparative Analysis of Space-Vector PWM Techniques for Transformerless Three-Phase Voltage Source Inverters. In Proceedings of the 14th International Conference on Power Electronics (CIEP), Puebla, Mexico, 24–26 October 2018; pp. 183–187. [Google Scholar] [CrossRef]

- Zhang, Y.; Li, C.; Schutten, M.; de Leon, C.F.; Prabhakaran, S. Common-Mode EMI Comparison of NSPWM, DPWM1, and SVPWM Modulation Approaches. In Proceedings of the IEEE Energy Conversion Congress and Exposition (ECCE), Baltimore, MD, USA, 29 September–3 October 2019; pp. 6430–6437. [Google Scholar] [CrossRef]

- Yun, S.-W.; Baik, J.-H.; Kim, D.-S.; Yoo, J.-Y. A new active zero state PWM algorithm for reducing the number of switchings. J. Power Electron. 2017, 17, 88–95. [Google Scholar] [CrossRef] [Green Version]

- Huang, Y.; Xu, Y.; Zhang, W.; Zou, J. Hybrid RPWM Technique Based on Modified SVPWM to Reduce the PWM Acoustic Noise. IEEE Trans. Power Electron. 2019, 34, 5667–5674. [Google Scholar] [CrossRef]

- Hou, C.-C.; Shih, C.-C.; Cheng, P.-T.; Hava, A.M. Common-mode voltage reduction modulation techniques for three-phase grid connected converters. In Proceedings of the International Power Electronics Conference—ECCE ASIA, Sapporo, Japan, 21–24 June 2010; pp. 1125–1131. [Google Scholar] [CrossRef]

- Hou, C.; Shih, C.; Cheng, P.; Hava, A.M. Common-Mode Voltage Reduction Pulsewidth Modulation Techniques for Three-Phase Grid-Connected Converters. IEEE Trans. Power Electron. 2013, 28, 1971–1979. [Google Scholar] [CrossRef]

- Dabour, S.M.; Abdel-Wahab, S.M.; Rashad, E.M. Common-Mode Voltage Reduction Algorithm with Minimum Switching Losses for Three-Phase Inverters. In Proceedings of the 21st International Middle East Power Systems Conference (MEPCON), Cairo, Egypt, 17–19 December 2019; pp. 1210–1215. [Google Scholar] [CrossRef]

- Hava, A.M.; Ün, E. A High-Performance PWM Algorithm for Common-Mode Voltage Reduction in Three-Phase Voltage Source Inverters. IEEE Trans. Power Electron. 2011, 26, 1998–2008. [Google Scholar] [CrossRef]

- An, S.; Sun, X.; Zhong, Y.; Matsui, M. Research on a new and generalized method of discontinuous PWM strategies to minimize the switching loss. In Proceedings of the IEEE PES Innovative Smart Grid Technologies, Tianjin, China, 21–24 May 2012; pp. 1–6. [Google Scholar] [CrossRef]

- Ali, S.M.; Reddy, V.V.; Kalavathi, M.S. Simplified active zero state PWM algorithms for vector controlled induction motor drives for reduced common mode voltage. In Proceedings of the International Conference on Recent Advances and Innovations in Engineering (ICRAIE-2014), Jaipur, India, 9–11 May 2014; pp. 1–7. [Google Scholar] [CrossRef]

- Wang, S.; Janabi, A.; Wang, B. Generalized Optimal SVPWM for the Switched- Capacitor Voltage Boost Converter. In Proceedings of the IEEE Energy Conversion Congress and Exposition (ECCE), Detroit, MI, USA, 11–15 October 2020; pp. 2708–2711. [Google Scholar] [CrossRef]

- Yu, B.; Song, W.; Guo, Y. A Simplified and Generalized SVPWM Scheme for Two-Level Multiphase Inverters with Common-Mode Voltage Reduction; IEEE: Piscataway, NJ, USA, 2021; p. 1. [Google Scholar] [CrossRef]

- Xiong, W.; Sun, Y.; Su, M.; Zhang, J.; Liu, Y.; Yang, J. Carrier-Based Modulation Strategies with Reduced Common-Mode Voltage for Five-Phase Voltage Source Inverters. IEEE Trans. Power Electron. 2018, 33, 2381–2394. [Google Scholar] [CrossRef]

- Aghazadeh, A.; Khodabakhshi-Javinani, N.; Nafisi, H.; Davari, M.; Pouresmaeil, E. Adapted near-state PWM for dual two-level inverters in order to reduce common-mode voltage and switching losses. IET Power Electron. 2019, 12, 676–685. [Google Scholar] [CrossRef]

- Dabour, S.M.; Abdel-Khalik, A.S.; Massoud, A.M.; Ahmed, S. Analysis of Scalar PWM Approach with Optimal Common-Mode Voltage Reduction Technique for Five-Phase Inverters. IEEE J. Emerg. Sel. Top. Power Electron. 2019, 7, 1854–1871. [Google Scholar] [CrossRef] [Green Version]

- Hassanac, M.S.; Abdelhakim, A.; Shoyama, M.; Dousoky, G.M. On-the-analysis and reduction of common-mode voltage of a single-stage inverter through control of a four-leg-based topology. Int. J. Electr. Power Energy Syst. 2021, 127, 106710. [Google Scholar] [CrossRef]

- Reddy, M.H.V.; Reddy, T.B.; Reddy, B.R.; Kalavathi, M.S. Reduced common mode voltage PWM techniques for dual inverter configuration. In Proceedings of the International Conference on Recent Advances and Innovations in Engineering (ICRAIE-2014), Jaipur, India, 9–11 May 2014; pp. 1–5. [Google Scholar] [CrossRef]

- Un, E.; Hava, A.M. A Near State PWM Method with Reduced Switching Frequency and Reduced Common Mode Voltage For Three-Phase Voltage Source Inverters. In Proceedings of the IEEE International Electric Machines & Drives Conference, Antalya, Turkey, 3–5 May 2007; pp. 235–240. [Google Scholar] [CrossRef]

- Zheng, J.; Fei, R.; Li, P.; Huang, S.; He, Y. Six-phase svpwm with common-mode voltage suppression. IET Power Electron. 2018, 11, 2461–2469. [Google Scholar] [CrossRef]

| Advantages | Disadvantages | |

|---|---|---|

| SVPWM | Lower switching losses [33] | Potentially high calculation burden [33] |

| AZSPWM | High modulation index range, high DC-bus utilization [22] | Line-to-line voltage pulse reversal [34] |

| NSPWM | Low CMV amplitude, less switching losses [34] | Higher in ripple and switching losses [33] |

| RSPWM | Theoretically non-changing CMV [16] | Low DC-bus utilization [16] |

| Voltage Vectors | Voltage Vectors | ||

| Sectors | Sequences | Sectors | Sequences | ||

|---|---|---|---|---|---|

| S1 | S1-1 | S4 | S4-1 | ||

| S1-2 | S4-2 | ||||

| S2 | S2-1 | S5 | S5-1 | ||

| S2-2 | S5-2 | ||||

| S3 | S3-1 | S6 | S6-1 | ||

| S3-2 | S6-2 | ||||

| Sectors | Sequences | Sectors | Sequences |

|---|---|---|---|

| S1 | S4 | ||

| S2 | S5 | ||

| S3 | S6 |

| Parameters | Values | Parameters | Values |

|---|---|---|---|

| DC side voltage | 750 V | DC side capacitance | μF |

| Current reference | 10 A | Switching frequency | 5 kHz |

| Filter inductance | 4 mH | MPC sampling time | s |

| Filter resistance | 0.01 Ω | Modulated sampling time | s |

| Grid voltage | 380 V | Predictive horizon (first step to overcome digital delay) | 2 |

| Grid frequency | 50 Hz | Control horizon | 1 |

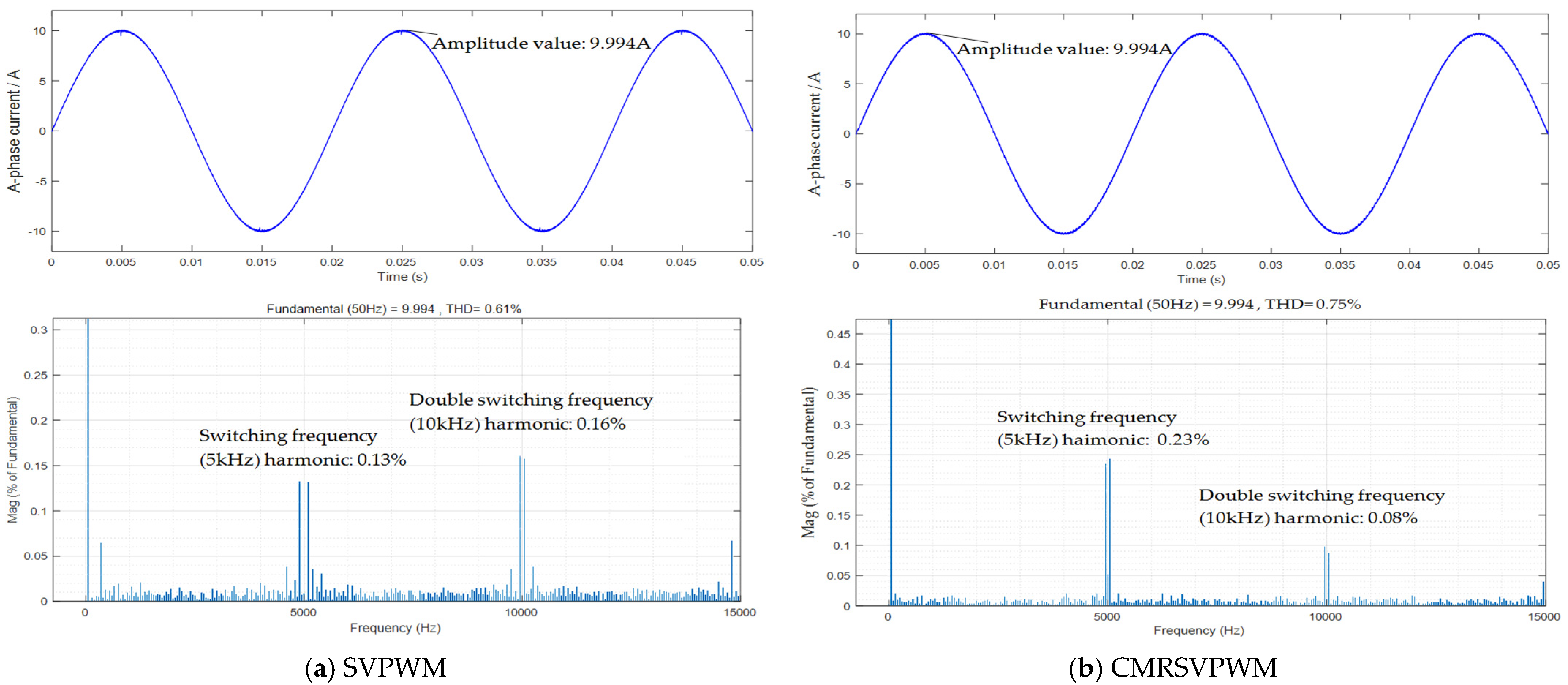

| SVPWM | AZSPWM | NSPWM | RSPWM | CMRSVPWM I | CMRSVPWM (I and II) | |

| Peak CMV | 6 | 6 | 6 | 6 | ||

| CMV frequency | 6 | 6 | 4 | 0 | 2 | 0 or 2 |

| CMV frequency at changing sectors | 0 | 1 | 1 | 0 | 1 | 1 |

| DC bus utilization | ||||||

| Phase-A current THD | 0.61% | 0.74% | 0.64% | 0.75% |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2021 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Goh, H.H.; Li, X.; Lim, C.S.; Zhang, D.; Dai, W.; Kurniawan, T.A.; Goh, K.C. Common-Mode Voltage Reduction Algorithm for Photovoltaic Grid-Connected Inverters with Virtual-Vector Model Predictive Control. Electronics 2021, 10, 2607. https://doi.org/10.3390/electronics10212607

Goh HH, Li X, Lim CS, Zhang D, Dai W, Kurniawan TA, Goh KC. Common-Mode Voltage Reduction Algorithm for Photovoltaic Grid-Connected Inverters with Virtual-Vector Model Predictive Control. Electronics. 2021; 10(21):2607. https://doi.org/10.3390/electronics10212607

Chicago/Turabian StyleGoh, Hui Hwang, Xinyi Li, Chee Shen Lim, Dongdong Zhang, Wei Dai, Tonni Agustiono Kurniawan, and Kai Chen Goh. 2021. "Common-Mode Voltage Reduction Algorithm for Photovoltaic Grid-Connected Inverters with Virtual-Vector Model Predictive Control" Electronics 10, no. 21: 2607. https://doi.org/10.3390/electronics10212607