Challenges of Overcoming Defects in Wide Bandgap Semiconductor Power Electronics

Abstract

:1. Introduction

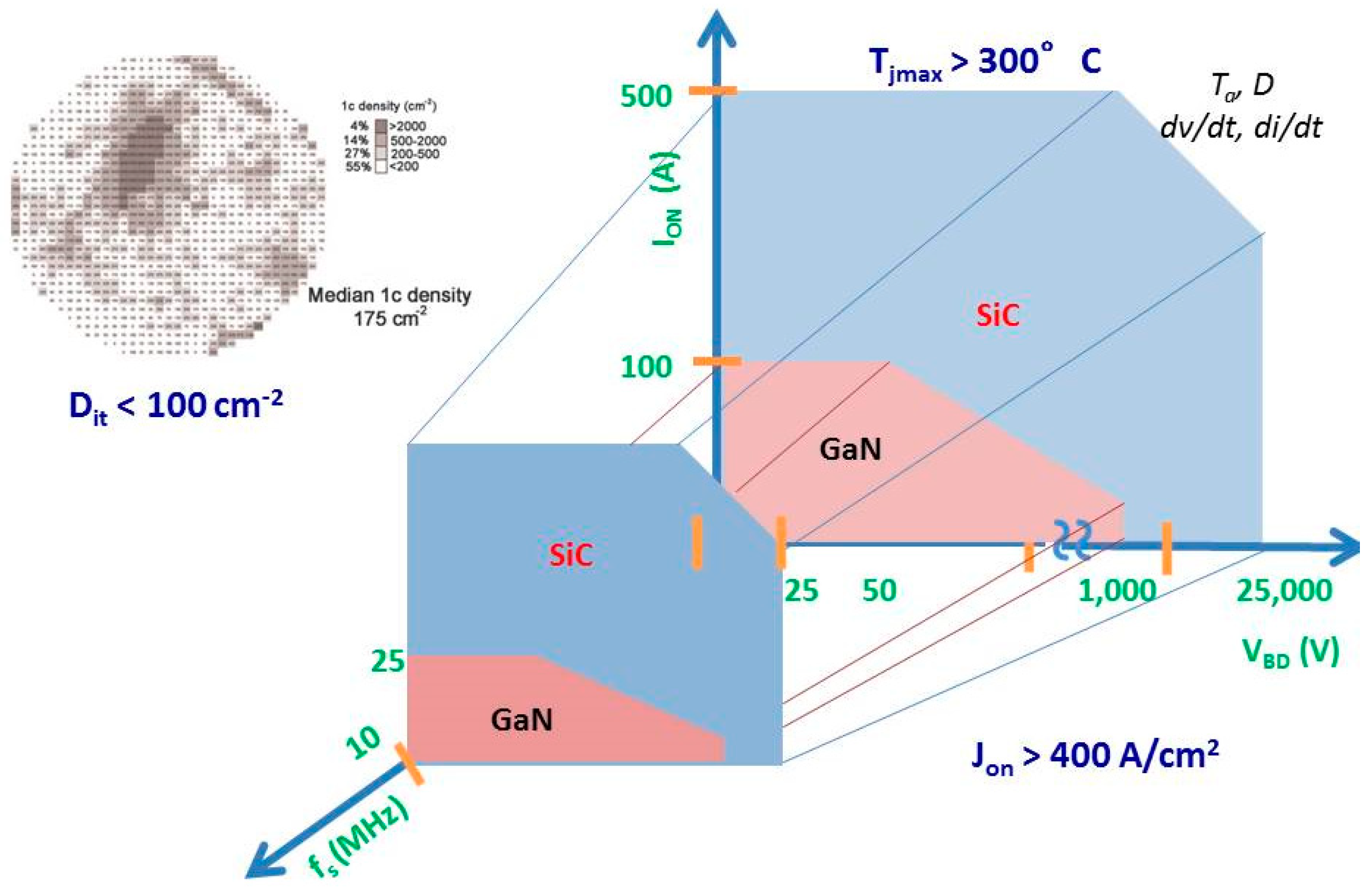

2. Results from the High Voltage/Temperature Extreme Environmental Evaluation

2.1. Effects of High-Temperature Stress on Metal–Semiconductor Interface

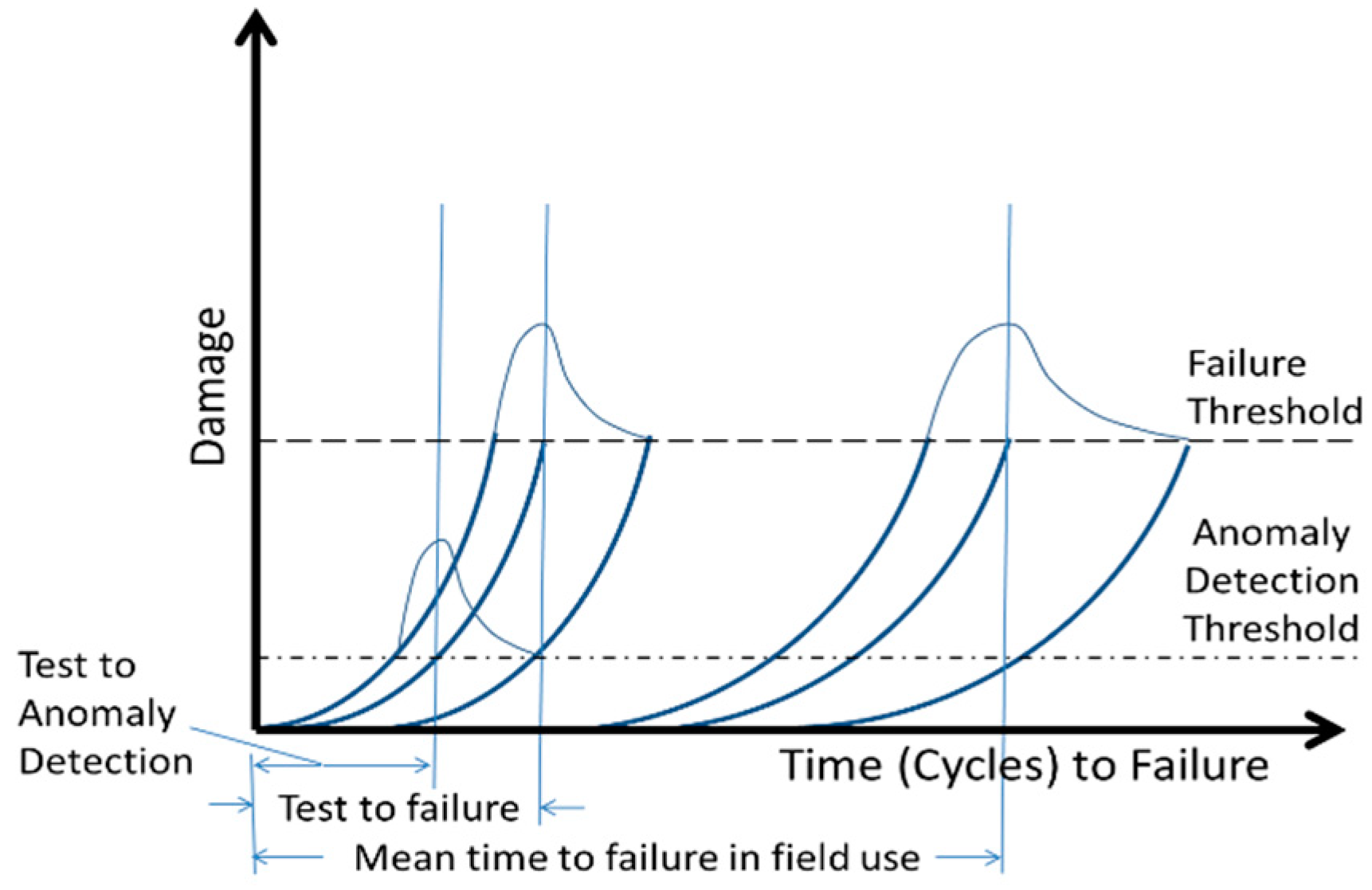

2.2. Physics of Failure Analysis for Extreme Environment Predictions

2.3. Evaluation under Extreme Radiation Environment

2.4. Accelerated Stress Testing to Quantify Cosmic-Ray Induced Failures

2.5. Defect Spectroscopy

3. Intrinsic Electrical and Thermal Stresses

3.1. On-State Static Electrical Stress

3.2. Off-State Static Electrical Stress

3.3. High-Voltage and High-Current Switching Stress

3.4. Electron Transport under High Magnetic Field Stress

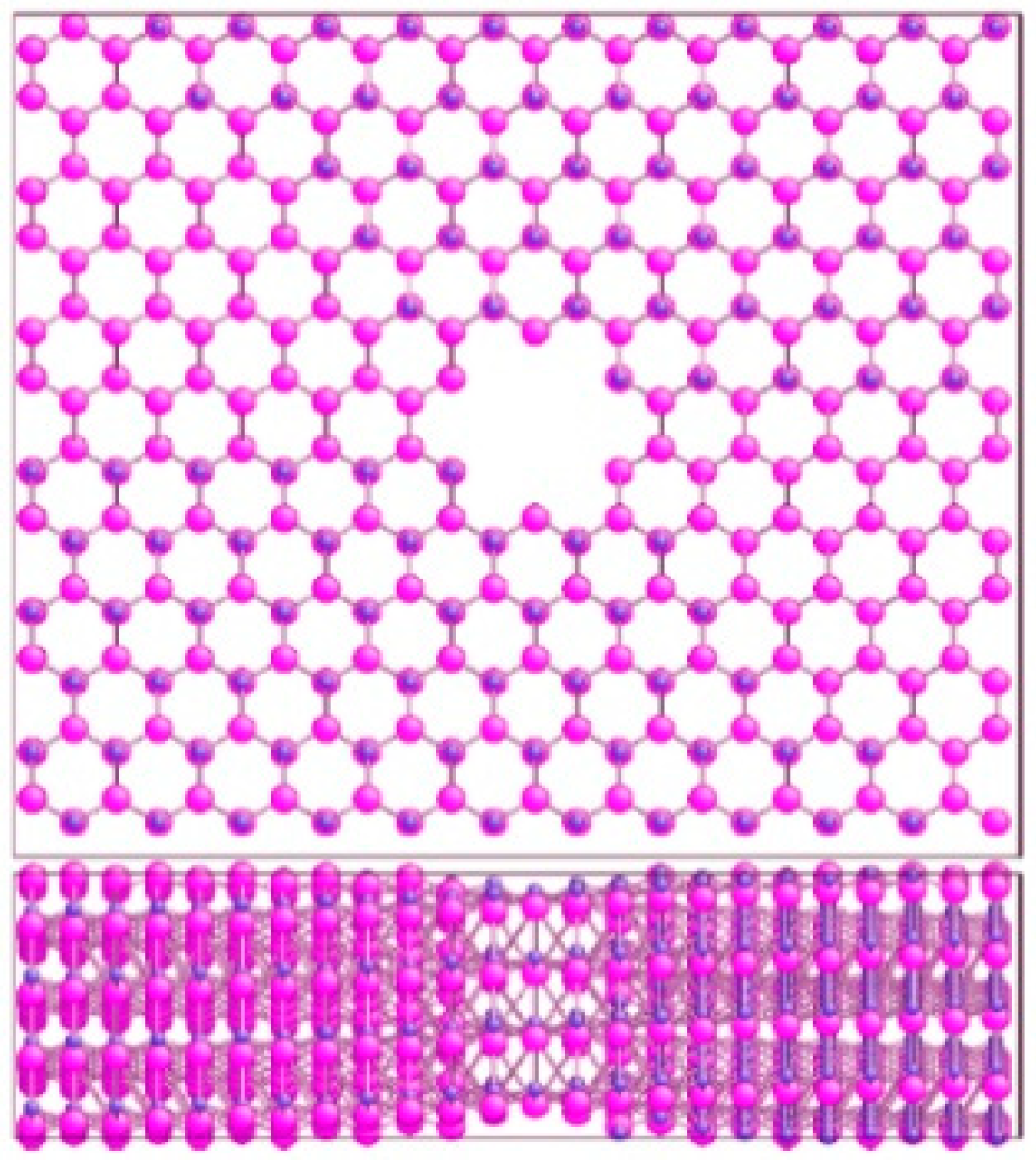

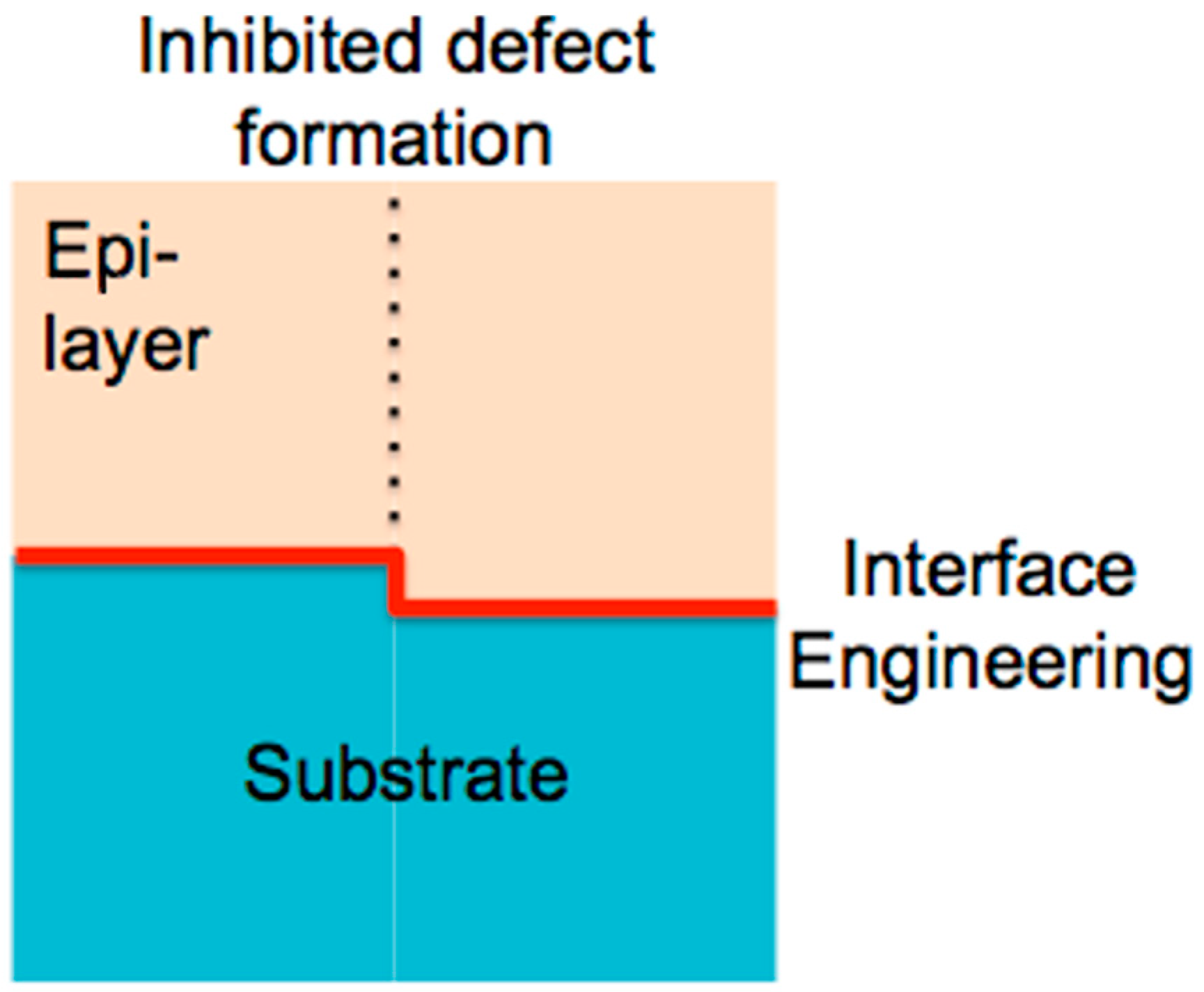

4. Material Theory and Simulation

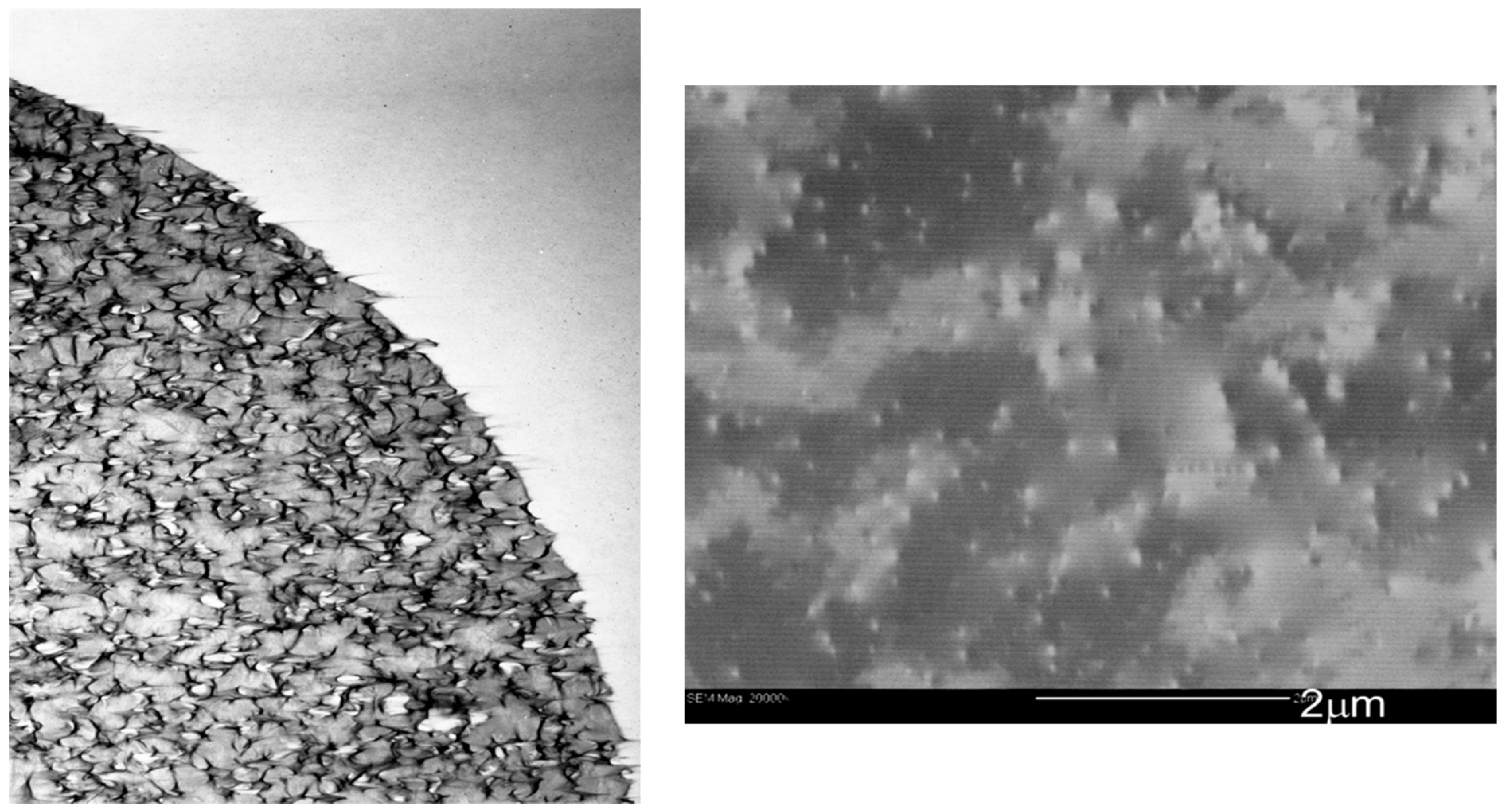

4.1. Defects with Atomic Resolution at Interfaces and Surfaces

4.2. Accurate Electronic Structure and Excited States of Defects

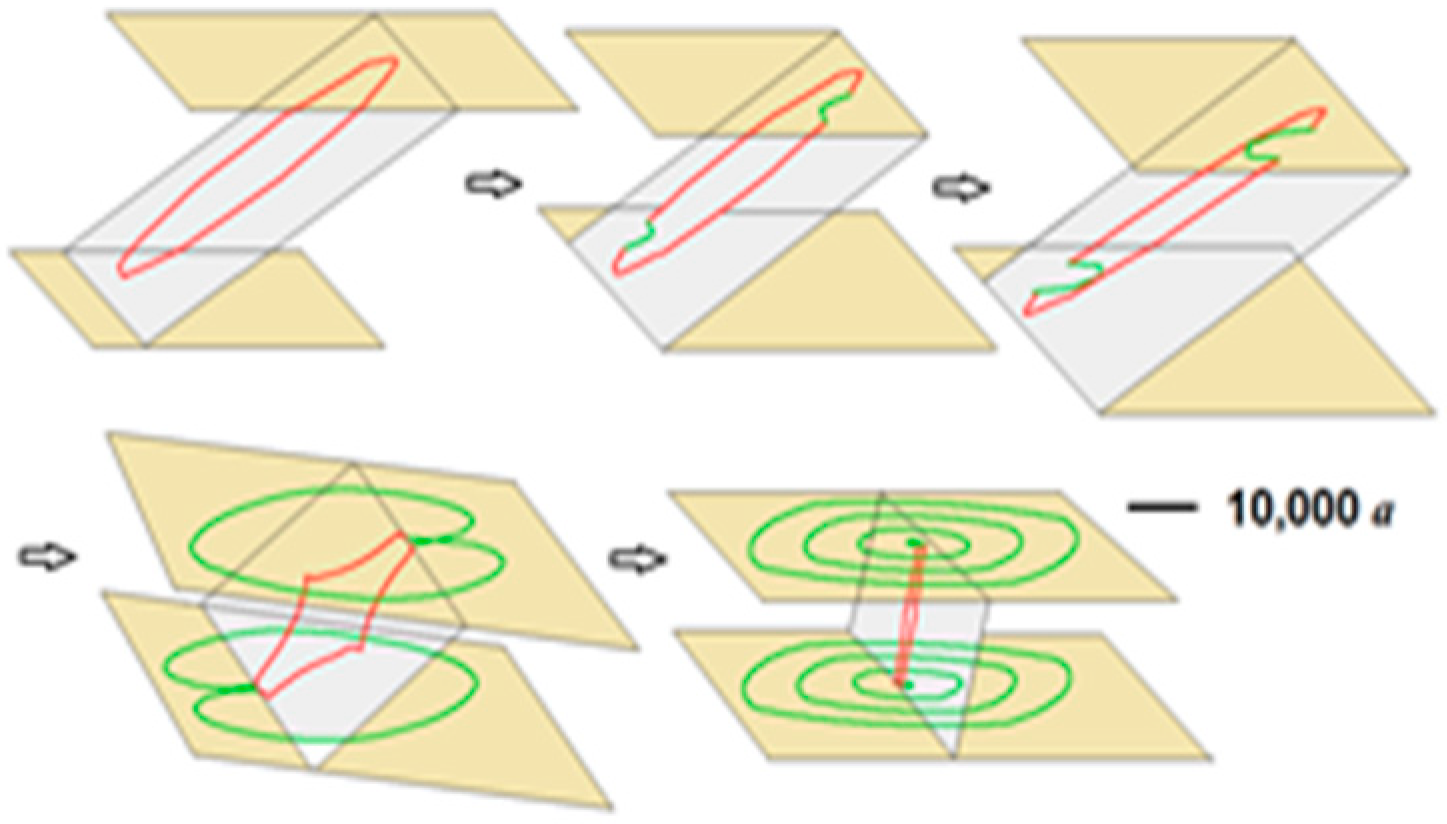

4.3. Interface Interactions with Dislocations

5. Defects in the Epitaxial Layer

5.1. Impact of Defects on Electron Transport

5.2. Defect Evolution under Stresses and Large Temperatures

5.3. Defects in GaN and Related Compounds

6. Summary

Author Contributions

Funding

Conflicts of Interest

References

- USAF. Avionics Integrity Program (AVIP); MIL-STD-1796A; USAF: Washington, DC, USA, 2011.

- Shenai, K.; Scott, R.; Baliga, B. Optimum semiconductors for high-power electronics. IEEE Trans. Electron Devices 1989, 36, 1811–1823. [Google Scholar] [CrossRef]

- Shenai, K.; Dudley, M.; Davis, R. Current Status and Emerging Trends in Wide Bandgap (WBG) Semiconductor Power Switching Devices. ECS J. Solid State Sci. Technol. 2013, 2, N3055–N3063. [Google Scholar] [CrossRef]

- Hemminger, J.; Fleming, G.; Ratner, M. Directing Matter and Energy: Five Challenges for Science and the Imagination; Office of Scientific and Technical Information, U.S. Department of Energy: Oak Ridge, TN, USA, 2007. [CrossRef] [Green Version]

- Ahmed, R.; Siddique, A.; Anderson, J.; Gautam, C.; Holtz, M.; Piner, E. Integration of GaN and Diamond Using Epitaxial Lateral Overgrowth. ACS Appl. Mater. Interfaces 2020, 12, 39397–39404. [Google Scholar] [CrossRef] [PubMed]

- Wileman, A.; Aslam, S.; Perinpanayagam, S. A road map for reliable power electronics for more electric aircraft. Prog. Aerosp. Sci. 2021, 127, 100739. [Google Scholar] [CrossRef]

- Hirth Lothe Jens, J.P. Theory of Dislocations; Krieger Pub. Co.: Malabar, FL, USA, 1992. [Google Scholar]

- Weingarten, N.S.; Chung, P.W. A-Type edge dislocation mobility in wurtzite GaN using molecular dynamics. Scr. Mater. 2013, 69, 311–314. [Google Scholar] [CrossRef]

- Tanaka, A.; Choi, W.; Chen, R.; Liu, R.; Mook, W.M.; Jungjohann, K.L.; Yu, P.K.L.; Dayeh, S.A. Structural and electrical characterization of thick GaN layers on Si, GaN, and engineered substrates. J. Appl. Phys. 2019, 125, 082517. [Google Scholar] [CrossRef]

- Belov, A.Y.; Chamrov, V.A.; Indenbom, V.L.; Lothe, J. Elastic fields of dislocations piercing the interface of an anisotropic bicrystal. Phys. Status Solidi (B) 1983, 119, 565–578. [Google Scholar] [CrossRef]

- Crabtree, G.; Glotzer, S.; McCurdy, B.; Roberto, J. Computational Materials Science and Chemistry: Accelerating Discovery and Innovation through Simulation-Based Engineering and Science, United States. 2010. Available online: https://www.osti.gov/biblio/1294275 (accessed on 20 November 2021).

- Loboda, M.; Chung, E.G.; Carlson, E.; Drachev, R.; Hansen, D.; Sanchez, E.; Wan, J.; Zhang, J. Advances in SiC substrates for power and energy applications. In Proceedings of the 2011 International Conference on Compound Semiconductor Manufacturing Technology, CS MANTECH 2011, Palm Springs, CA, USA, 16–19 May 2011. [Google Scholar]

- Kim, J.; Seo, O.; Kumara, L.S.R.; Nabatame, T.; Koide, Y.; Sakata, O. Highly-Crystalline 6 inch free-standing GaN observed using X-ray diffraction topography. CrystEngComm 2021, 23, 1628–1633. [Google Scholar] [CrossRef]

- Office of Scientific and Technical Information, U.S. Department of Energy. Electrical and Electronics Technical Team Roadmap; Office of Scientific and Technical Information, U.S. Department of Energy: Oak Ridge, TN, USA, 2013. [CrossRef]

- United States Department of Defense. Defense-Wide Manufacturing Science & Technology (DMS&T) Program: Silicon Car-bide (SiC) High Efficiency Power Switches. 2016. Available online: https://apps.dtic.mil/descriptivesum/Y2017/OSD/stamped/U_0603680D8Z_3_PB_2017.pdf (accessed on 20 November 2021).

- Electric Ships Office, United States Department of Defense. Electric Ships Office–Naval Power Systems Technology Development Roadmap. 2013. Available online: https://defenseinnovationmarketplace.dtic.mil/wp-content/uploads/2018/02/NavalPowerSystemsTechnologyRoadmap.pdf (accessed on 20 November 2021).

- Whaling, C. Technology Roadmap Analysis 2013: Assessing Automotive Technology R&D Relevant to DOE Power Electronics Cost Targets. In Proceedings of the DOE AMR Conference, Vehicle Technologies Program, Arlington, VA, USA, 14 May 2013; Available online: https://www.energy.gov/sites/prod/files/2014/03/f13/ape032_whaling_2013_o.pdf (accessed on 20 November 2021).

- European Center for Power Electronics (ECPE). Available online: www.ecpe.org (accessed on 20 November 2021).

- Lendenmann, H.; Dahlquist, F.; Bergman, P.; Bleichner, H.; Hallin, C. High-Power SiC Diodes: Characteristics, Reliability and Relation to Material Defects. Mater. Sci. Forum 2002, 389–393, 1259–1264. [Google Scholar] [CrossRef]

- Skowronski, M.; Ha, S. Degradation of hexagonal silicon-carbide-based bipolar devices. J. Appl. Phys. 2006, 99, 011101. [Google Scholar] [CrossRef]

- Kimoto, T.; Suda, J.; Feng, G.; Miyake, H.; Kawahara, K.; Niwa, H.-Y.; Okuda, T.; Ichikawa, S.; Nishi, Y. Defect Electronics in SiC and Fabrication of Ultrahigh-Voltage Bipolar Devices. ECS Trans. 2013, 50, 25–35. [Google Scholar] [CrossRef]

- Myers-Ward, R.; Gaskill, D.K.; Stahlbush, R.S.; Mahadik, N.A.; Wheeler, V.; Nyakiti, L.O.; Eddy, C.R. Managing Basal Plane Dislocations in SiC: Perspective and Prospects. ECS Trans. 2013, 50, 103–108. [Google Scholar] [CrossRef]

- Acharya, K.; Shenai, K. On the dV/dt Rating of SiC Schottky Power Rectifiers. In Proceedings of the Power Electronics Technology Conference, Rosemont, IL, USA, 29–31 October 2002; pp. 672–677. [Google Scholar]

- Schafft, H.A.; Erhart, D.L.; Gladden, W.K. Toward a building-in reliability approach. Microelectron. Reliab. 1997, 37, 3–18. [Google Scholar] [CrossRef]

- Trivedi, M.; Shenai, K. Failure mechanisms of IGBTs under short-circuit and clamped inductive switching stress. IEEE Trans. Power Electron. 1999, 14, 108–116. [Google Scholar] [CrossRef]

- Shenai, K.; Dudley, M.; Davis, R. Rugged Electrical Power Switching in Semiconductors: A Systems Approach. Proc. IEEE 2014, 102, 35–52. [Google Scholar] [CrossRef]

- Li, M.; Ahyi, A.C.; Zhu, X.; Chen, Z.; Isaacs-Smith, T.; Williams, J.R.; Crofton, J. Nickel Ohmic Contacts to N-Implanted (0001) 4H-SiC. J. Electron. Mater. 2010, 39, 540–544. [Google Scholar] [CrossRef]

- Rackauskas, B.; Uren, M.J.; Stoffels, S.; Zhao, M.; Bakeroot, B.; Decoutere, S.; Kuball, M. The Impact of Ti/Al Contacts on AlGaN/GaN HEMT Vertical Leakage and Breakdown. IEEE Electron Device Lett. 2018, 39, 1580–1583. [Google Scholar] [CrossRef] [Green Version]

- Wojciech, M.; Indykiewicz, K.; Paszkiewicz, B. Chemical analysis of Ti/Al/Ni/Au ohmic contacts to AlGaN/GaN hetero-structures. Opt. Appl. 2013, 43, 67–72. [Google Scholar] [CrossRef]

- Maeda, M.; Yamasaki, T.; Takahashi, Y. Ohmic Contact Mechanism of Titanium-based Electrodes on n-type Gallium Nitride. Trans. JWRI 2012, 41, 45–48. Available online: https://ci.nii.ac.jp/naid/120004921918/en/ (accessed on 20 November 2021).

- As, D.J.; Tschumak, E.; Laubenstein, I.; Kemper, R.M.; Lischka, K. Schottky and Ohmic Contacts on Non-Polar Cubic GaN Epilayers. Mater. Res. Soc. Symp. Proc. 2008, 1108, 3–8. [Google Scholar] [CrossRef]

- Zhang, R.; Johnson, R.W.; Vert, A.; Zhang, T.; Shaddock, D. Assembly Materials and Processes for High-Temperature Geothermal Electronic Modules. IEEE Trans. Compon. Packag. Manuf. Technol. 2012, 2, 1739–1749. [Google Scholar] [CrossRef]

- Hagler, P.; Johnson, R.W.; Chen, L.-Y. SiC Die Attach Metallurgy and Processes for Applications up to 500 °C. IEEE Trans. Compon. Packag. Manuf. Technol. 2011, 1, 630–639. [Google Scholar] [CrossRef]

- Johnson, R.W.; Wang, C.; Liu, Y.; Scofield, J.D. Power Device Packaging Technologies for Extreme Environments. IEEE Trans. Electron. Packag. Manuf. 2007, 30, 182–193. [Google Scholar] [CrossRef]

- Shen, Z.; Fang, K.; Hamilton, M.C.; Johnson, R.W.; Snipes, E.K.; Bozack, M.J. Lead-free Solder Attach for 200 °C Applications. Addit. Pap. Present. 2013, 2013, 000260–000267. [Google Scholar] [CrossRef]

- Griffoni, A.; Van Duivenbode, J.; Linten, D.; Simoen, E.; Rech, P.; DiLillo, L.; Wrobel, F.; Verbist, P.; Groeseneken, G. Neutron-Induced Failure in Silicon IGBTs, Silicon Super-Junction and SiC MOSFETs. IEEE Trans. Nucl. Sci. 2012, 59, 866–871. [Google Scholar] [CrossRef]

- Shenai, K. Reliability of wide bandgap semiconductor power switching devices. In Proceedings of the IEEE 2010 National Aerospace & Electronics Conference, Dayton, OH, USA, 14–16 July 2010; pp. 322–327. [Google Scholar] [CrossRef]

- Pearton, S.; Deist, R.; Ren, F.; Liu, L.; Polyakov, A.Y.; Kim, J. Review of radiation damage in GaN-based materials and devices. J. Vac. Sci. Technol. A 2013, 31, 050801. [Google Scholar] [CrossRef] [Green Version]

- Thomé, L.; Moll, S.; Debelle, A.; Garrido, F.; Sattonnay, G.; Jagielski, J. Radiation Effects in Nuclear Ceramics. Adv. Mater. Sci. Eng. 2012, 2012, 905474. [Google Scholar] [CrossRef] [Green Version]

- Bellotti, E.; Bertazzi, F.; Shishehchi, S.; Matsubara, M.; Goano, M. Theory of Carriers Transport in III-Nitride Materials: State of the Art and Future Outlook. IEEE Trans. Electron Devices 2013, 60, 3204–3215. [Google Scholar] [CrossRef]

- Krieger, J.B.; Iafrate, G.J. Time evolution of Bloch electrons in a homogeneous electric field. Phys. Rev. B 1986, 33, 5494–5500. [Google Scholar] [CrossRef]

- Amano, H.; Sawaki, N.; Akasaki, I.; Toyoda, Y. Metalorganic vapor phase epitaxial growth of a high quality GaN film using an AlN buffer layer. Appl. Phys. Lett. 1986, 48, 353–355. [Google Scholar] [CrossRef] [Green Version]

- Law, J.J.M.; Yu, E.T.; Koblmüller, G.; Wu, F.; Speck, J.S. Low defect-mediated reverse-bias leakage in (0001) GaN via high-temperature molecular beam epitaxy. Appl. Phys. Lett. 2010, 96, 102111. [Google Scholar] [CrossRef]

- Northrup, J.E. Theory of intrinsic and H-passivated screw dislocations in GaN. Phys. Rev. B 2002, 66, 045204. [Google Scholar] [CrossRef]

- Yakunin, A.M.; Silov, A.Y.; Koenraad, P.M.; Tang, J.-M.; Flatté, M.E.; Van Roy, W.; De Boeck, J.; Wolter, J.H. Spatial Structure of Mn-Mn Acceptor Pairs in GaAs. Phys. Rev. Lett. 2005, 95, 256402. [Google Scholar] [CrossRef] [Green Version]

- Parr, R.G. Density Functional Theory. Annu. Rev. Phys. Chem. 1983, 34, 631–656. [Google Scholar] [CrossRef]

- Yao, Y.; Ishikawa, Y.; Sudo, M.; Sugawara, Y.; Yokoe, D. Characterization of threading dislocations in GaN (0001) substrates by photoluminescence imaging, cathodoluminescence mapping and etch pits. J. Cryst. Growth 2017, 468, 484–488. [Google Scholar] [CrossRef]

- Łażewski, J.; Jochym, P.T.; Piekarz, P.; Sternik, M.; Parlinski, K.; Cholewiński, J.; Dłużewski, P.; Krukowski, S. DFT modelling of the edge dislocation in 4H-SiC. J. Mater. Sci. 2019, 54, 10737–10745. [Google Scholar] [CrossRef] [Green Version]

- Zhang, Z.; Sudarshan, T.S. Basal plane dislocation-free epitaxy of silicon carbide. Appl. Phys. Lett. 2005, 87, 151913. [Google Scholar] [CrossRef]

- Belabbas, I.; Béré, A.; Chen, J.; Petit, S.; Belkhir, M.A.; Ruterana, P.; Nouet, G. Atomistic modeling of the(a + c)-mixed dislocation core in wurtzite GaN. Phys. Rev. B 2007, 75, 115201. [Google Scholar] [CrossRef]

- Heyd, J.; Scuseria, G.E.; Ernzerhof, M. Hybrid functionals based on a screened Coulomb potential. J. Chem. Phys. 2003, 118, 8207, Erratum in J. Chem. Phys. 2006, 124, 219906. [Google Scholar] [CrossRef] [Green Version]

- Kresse, G.; Furthmüller, J. Efficient iterative schemes forab initiototal-energy calculations using a plane-wave basis set. Phys. Rev. B 1996, 54, 11169–11186. [Google Scholar] [CrossRef]

- Tang, J.-M.; Flatté, M.E. Multiband Tight-Binding Model of Local Magnetism in Ga1-xMnxAs. Phys. Rev. Lett. 2004, 92, 047201. [Google Scholar] [CrossRef] [Green Version]

- Yakunin, A.M.; Silov, A.Y.; Koenraad, P.M.; Wolter, J.H.; Van Roy, W.; De Boeck, J.; Tang, J.-M.; Flatté, M.E. Spatial Structure of an Individual Mn Acceptor in GaAs. Phys. Rev. Lett. 2004, 92, 216806. [Google Scholar] [CrossRef] [PubMed] [Green Version]

- Castleton, C.; Hoglund, A.; Mirbt, S. Density functional theory calculations of defect energies using supercells. Model. Simul. Mater. Sci. Eng. 2009, 17, 084003. [Google Scholar] [CrossRef]

- Aryasetiawan, F.; Gunnarsson, O. TheGWmethod. Rep. Prog. Phys. 1998, 61, 237–312. [Google Scholar] [CrossRef] [Green Version]

- Car, R.; Parrinello, M. Unified Approach for Molecular Dynamics and Density-Functional Theory. Phys. Rev. Lett. 1985, 55, 2471–2474. [Google Scholar] [CrossRef] [PubMed] [Green Version]

- Ning, X.J.; Chien, F.R.; Pirouz, P.; Yang, J.W.; Khan, M.A. Growth defects in GaN films on sapphire: The probable origin of threading dislocations. J. Mater. Res. 1996, 11, 580–592. [Google Scholar] [CrossRef]

- Oliver, R.A.; Kappers, M.J.; McAleese, C.; Datta, R.; Sumner, J.; Humphreys, C.J. The origin and reduction of dislocations in Gallium Nitride. J. Mater. Sci. Mater. Electron. 2008, 19, 208–214. [Google Scholar] [CrossRef]

- Liu, L.; Edgar, J. Substrates for gallium nitride epitaxy. Mater. Sci. Eng. R Rep. 2002, 37, 61–127. [Google Scholar] [CrossRef]

- Setera, B.; Christou, A. Impact of Threading Dislocations in GaN Power Switching Devices. ECS Trans. 2021, 102, 25–32. [Google Scholar] [CrossRef]

- Tanaka, A.; Nagamatsu, K.; Usami, S.; Kushimoto, M.; Deki, M.; Nitta, S.; Honda, Y.; Bockowski, M.; Amano, H. V-shaped dislocations in a GaN epitaxial layer on GaN substrate. AIP Adv. 2019, 9, 095002. [Google Scholar] [CrossRef]

- Neudeck, P.; Huang, W.; Dudley, M. Study of bulk and elementary screw dislocation assisted reverse breakdown in low-voltage (>250 V) 4H-SiC p/sup +/−n junction diodes. I. DC properties. IEEE Trans. Electron Devices 1999, 46, 478–484. [Google Scholar] [CrossRef]

- Skowronski, M.; Liu, J.Q.; Vetter, W.M.; Dudley, M.; Hallin, C.; Lendenmann, H. Recombination-enhanced defect motion in forward-biased 4H–SiC p-n diodes. J. Appl. Phys. 2002, 92, 4699–4704. [Google Scholar] [CrossRef]

- Setera, B.; Christou, A. Threading dislocations in GaN high-voltage switches. Microelectron. Reliab. 2021, 124, 114336. [Google Scholar] [CrossRef]

- Kirste, L.; Grabianska, K.; Kucharski, R.; Sochacki, T.; Lucznik, B.; Bockowski, M. Structural Analysis of Low Defect Ammonothermally Grown GaN Wafers by Borrmann Effect X-ray Topography. Materials 2021, 14, 5472. [Google Scholar] [CrossRef]

| Characteristic | Challenges |

|---|---|

| Effects of high-temperature stress on metal–semiconductor interface |

|

| Cosmic ray-induced failures |

|

| On-state static electrical stress |

|

| Off-state static electrical stress |

|

| High-voltage and high-current switching stress |

|

| Electron transport under high magnetic field stress |

|

| Impact of epitaxial defects on electron transport |

|

| Defect evolution under stresses and large temperatures |

|

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2021 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Setera, B.; Christou, A. Challenges of Overcoming Defects in Wide Bandgap Semiconductor Power Electronics. Electronics 2022, 11, 10. https://doi.org/10.3390/electronics11010010

Setera B, Christou A. Challenges of Overcoming Defects in Wide Bandgap Semiconductor Power Electronics. Electronics. 2022; 11(1):10. https://doi.org/10.3390/electronics11010010

Chicago/Turabian StyleSetera, Brett, and Aristos Christou. 2022. "Challenges of Overcoming Defects in Wide Bandgap Semiconductor Power Electronics" Electronics 11, no. 1: 10. https://doi.org/10.3390/electronics11010010