Design for the Package-Board Transition and Its Testability Design in the Fan-Out Wafer-Level Package

Abstract

:1. Introduction

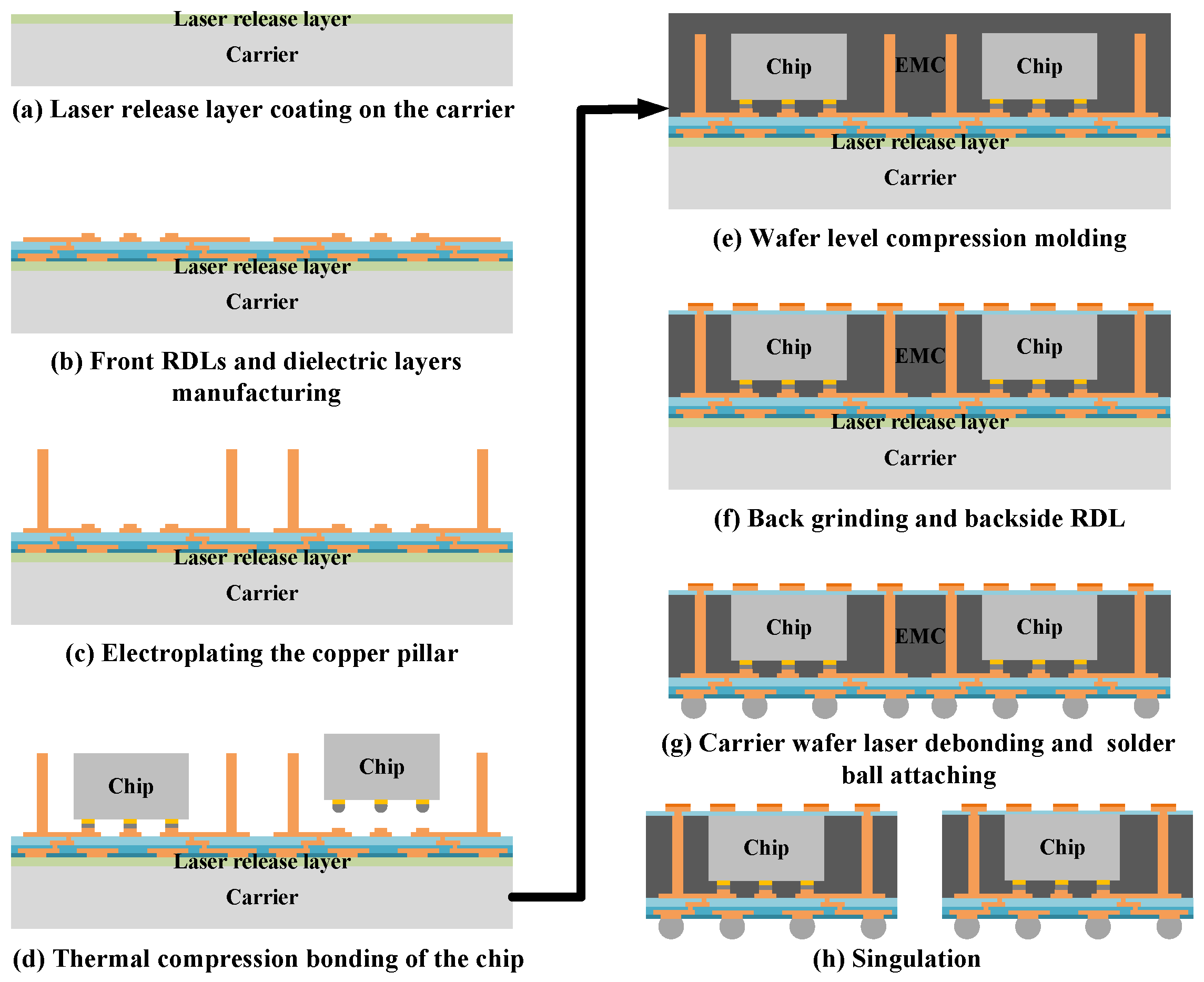

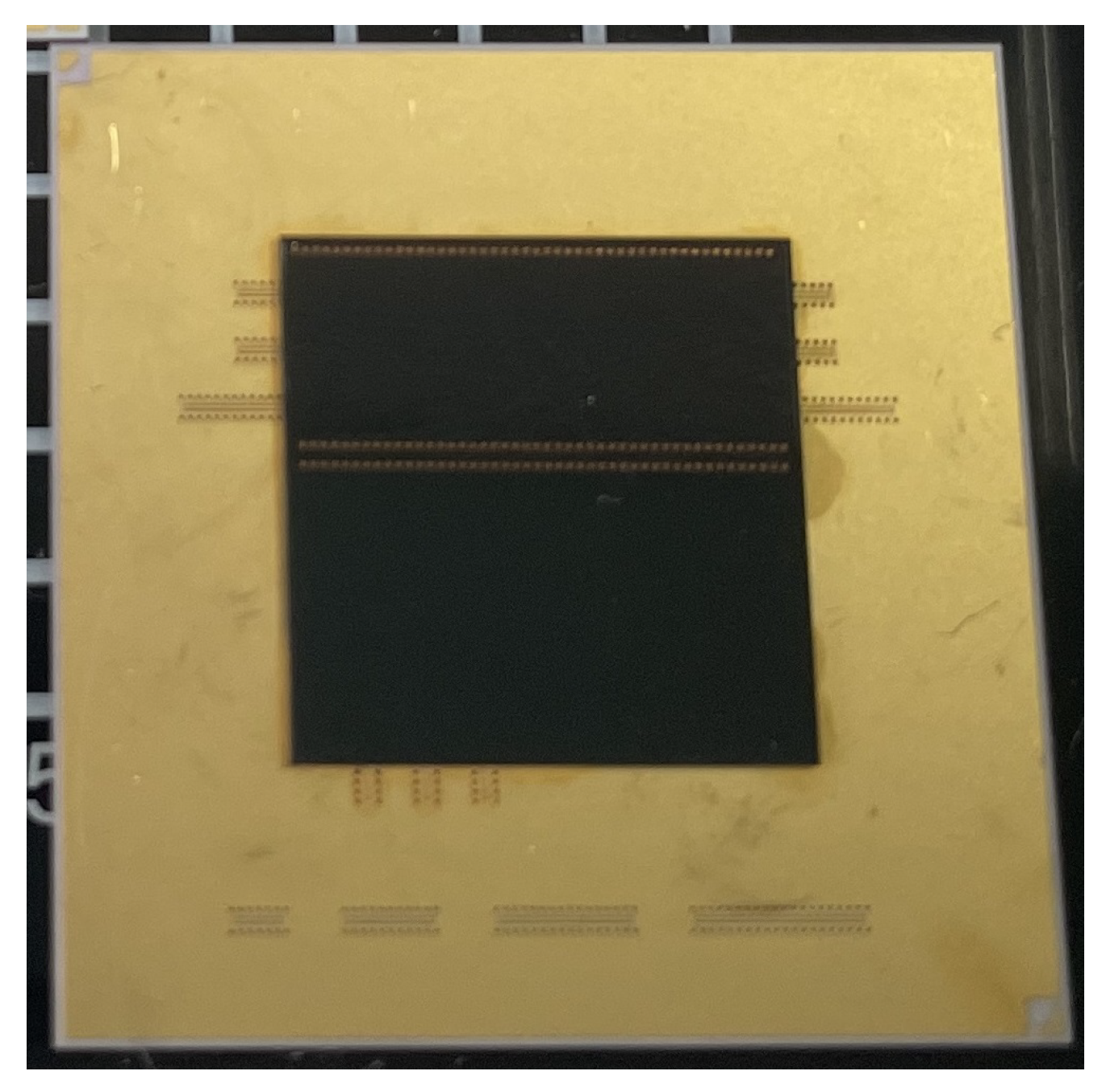

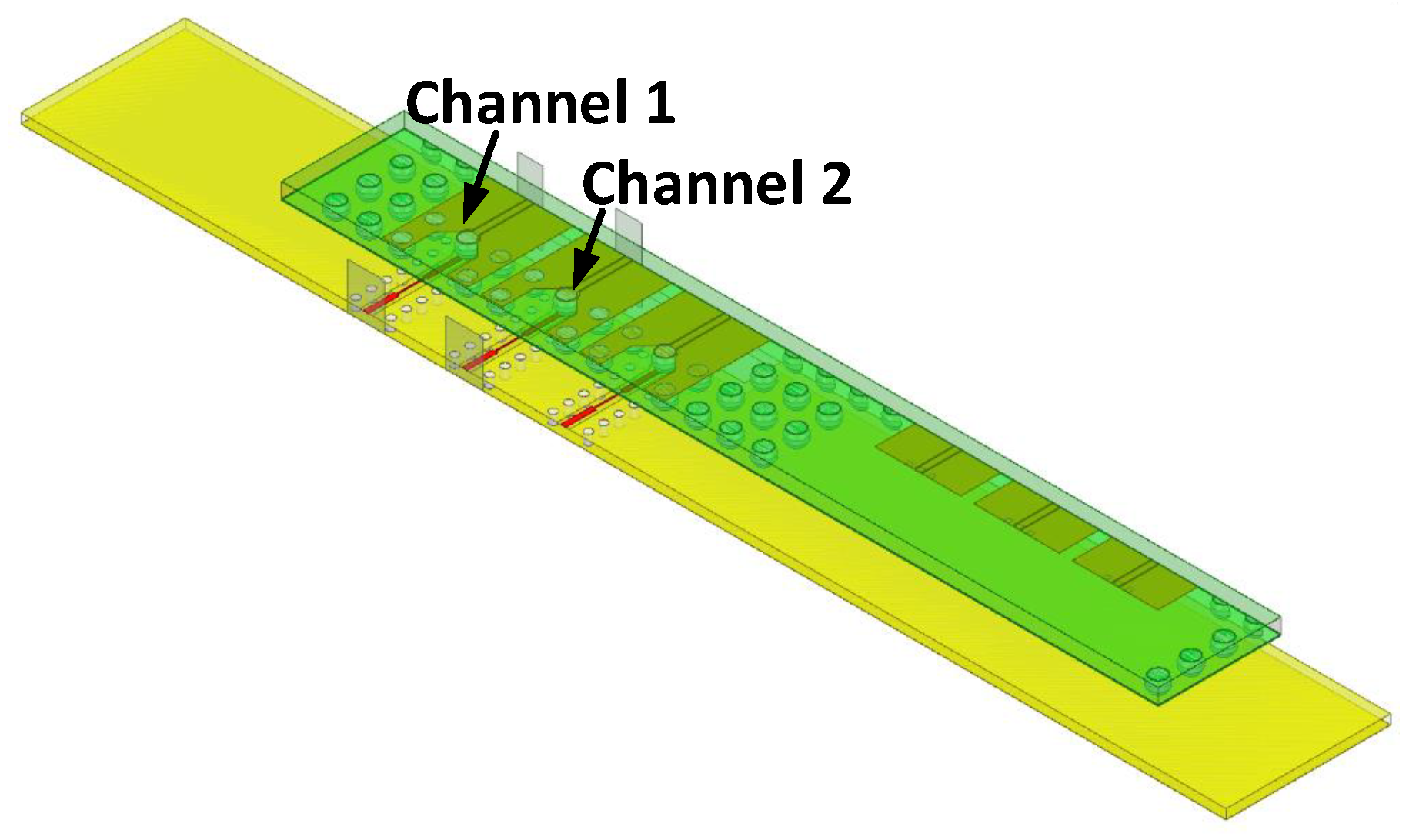

2. Structure and Process of the FOWLP

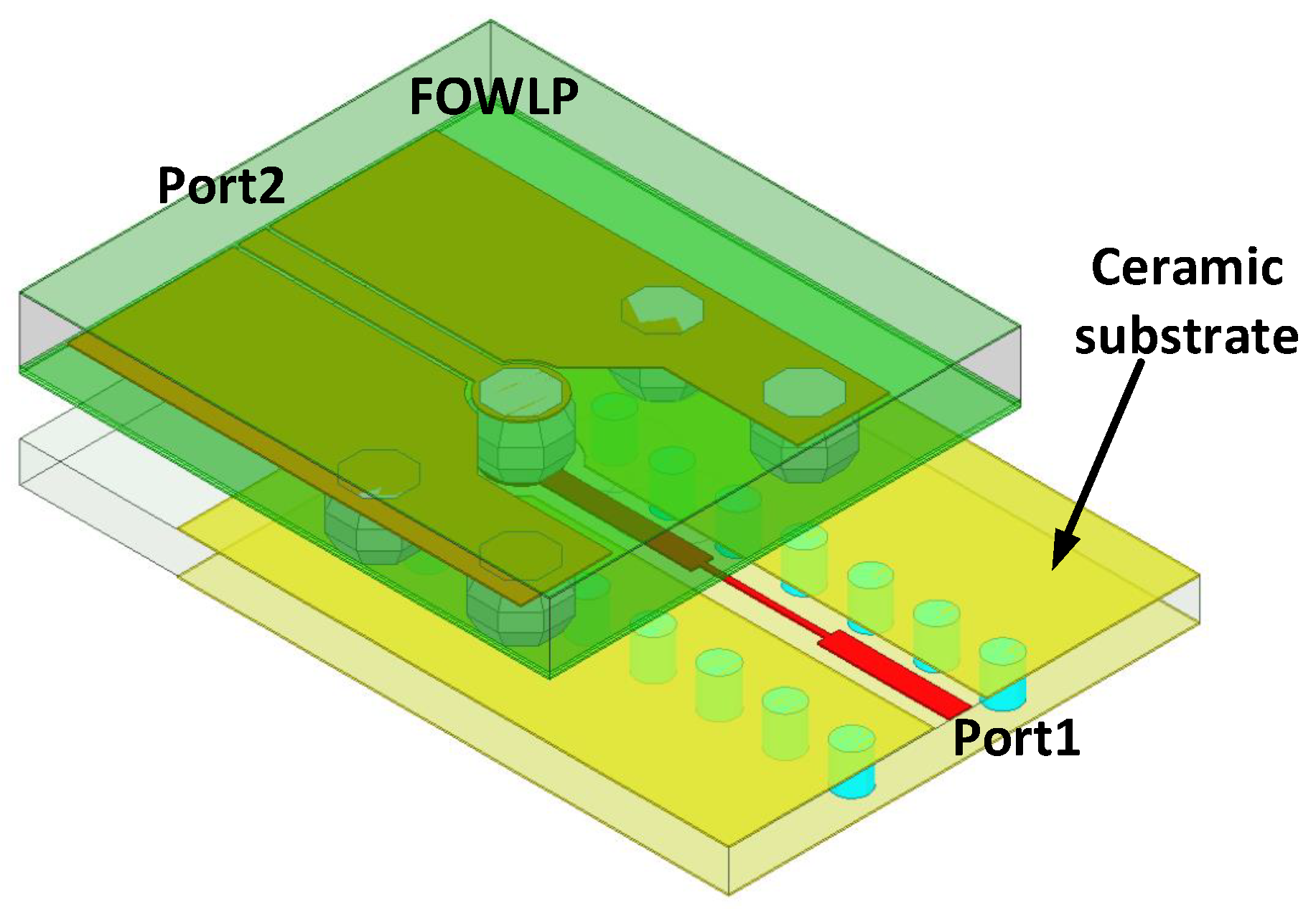

3. Package-Board Transition in FOWLP

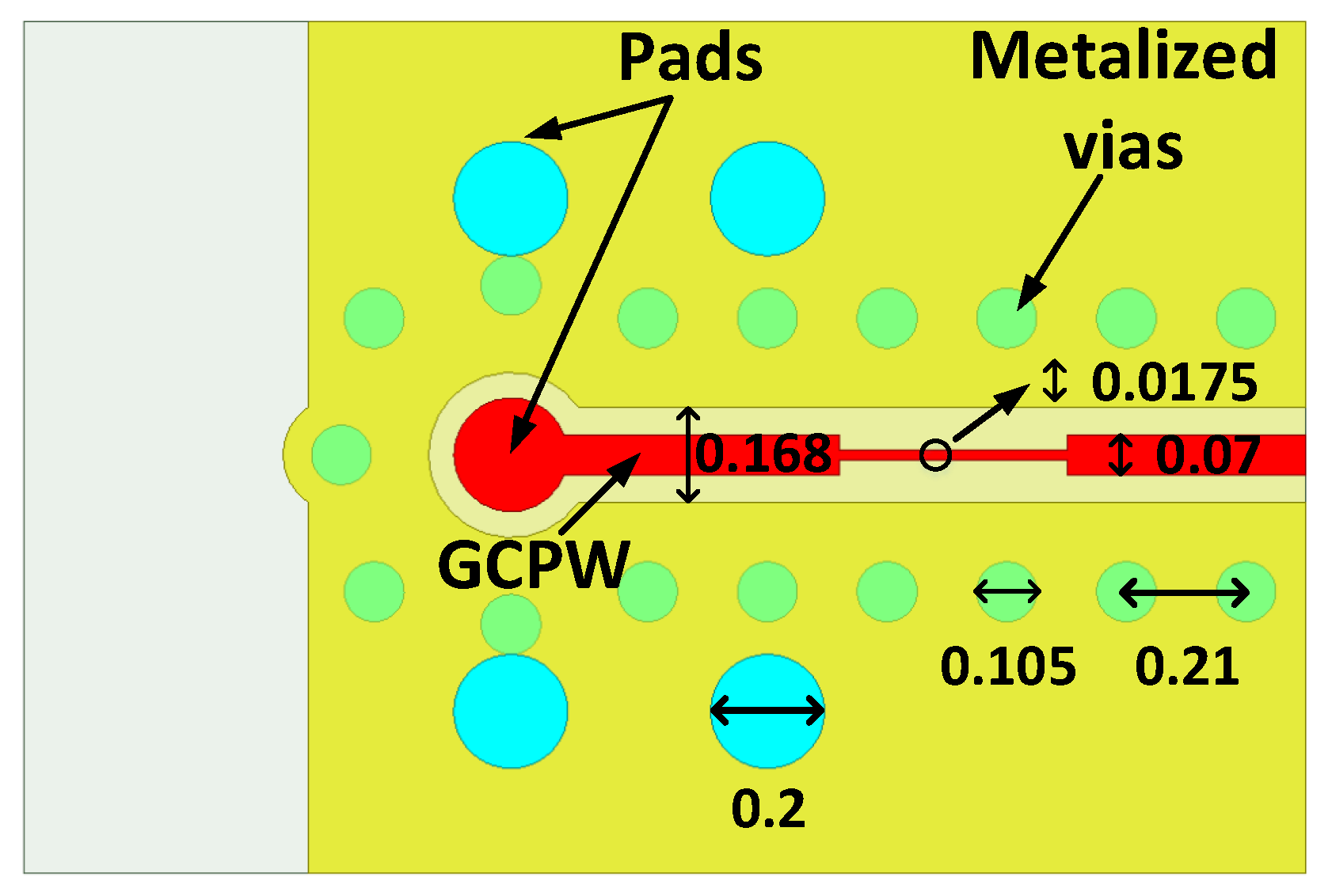

3.1. Selection of the Test Board

3.2. Design for the Package-Board Transition

4. Measurement Methods for the Package-Board Transition

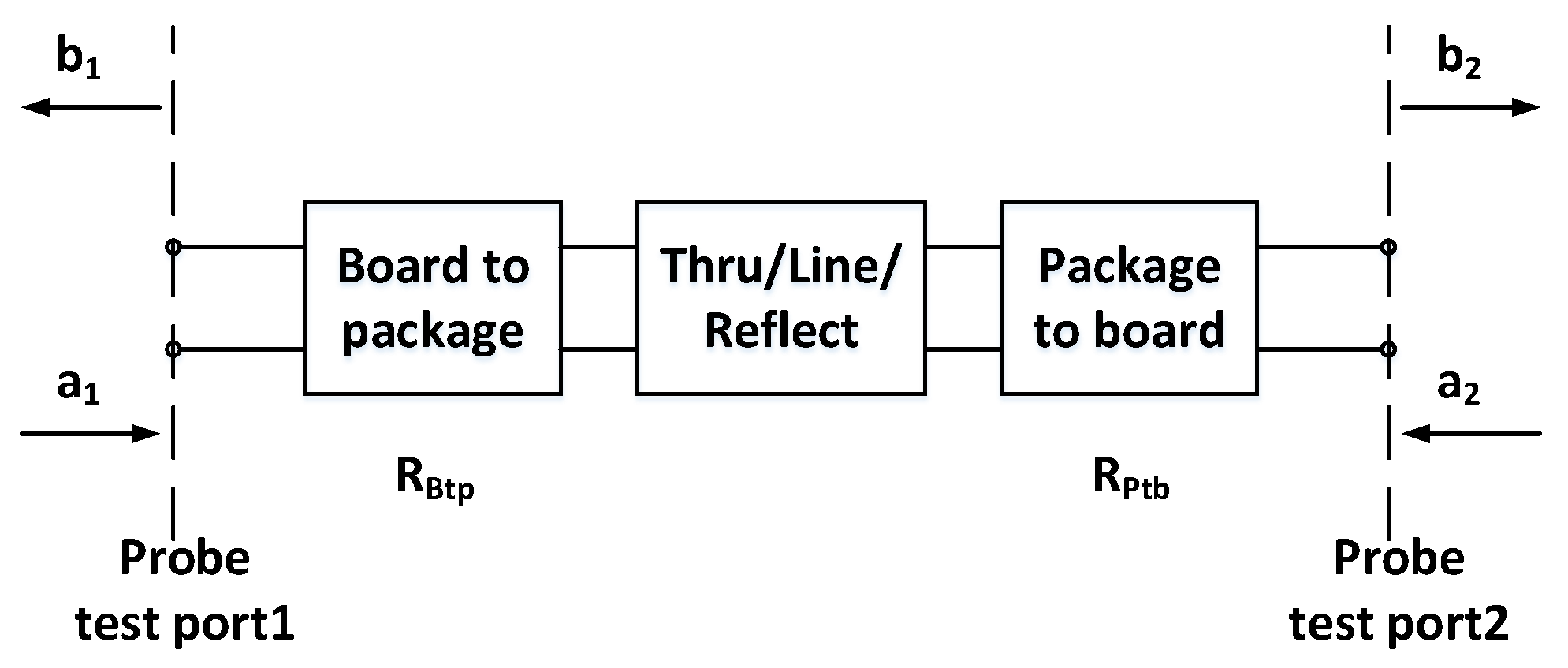

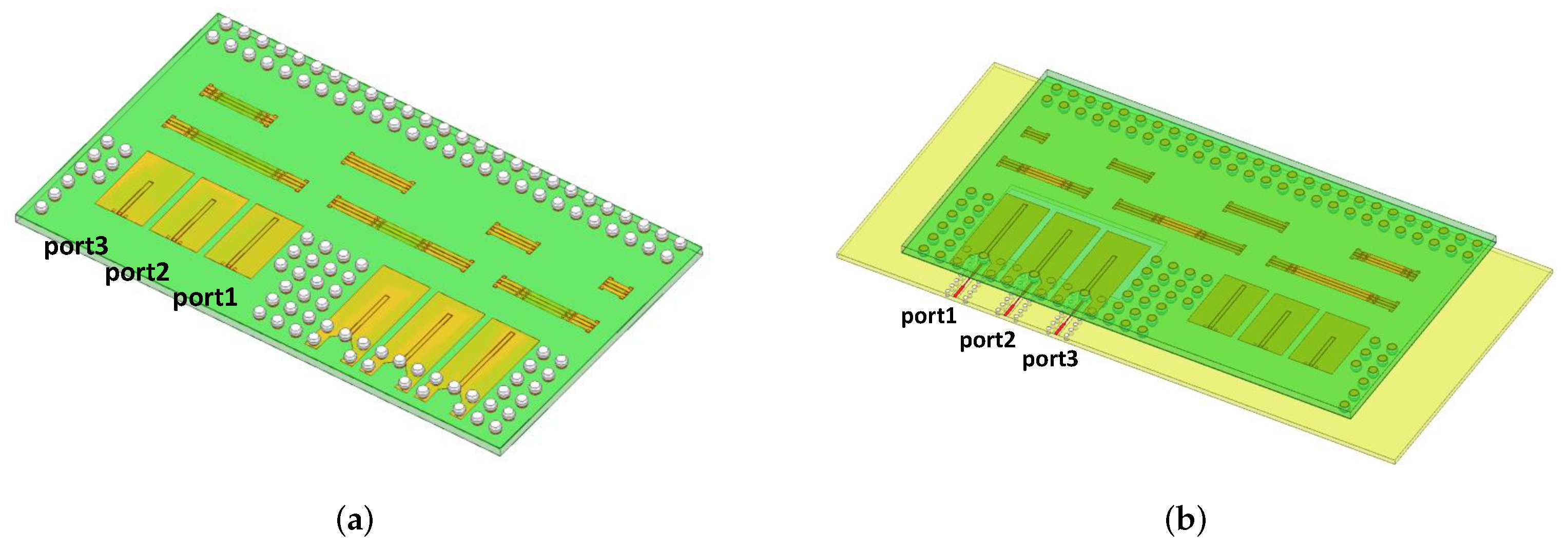

4.1. Measurement Method Based on the Port Reduction Technique

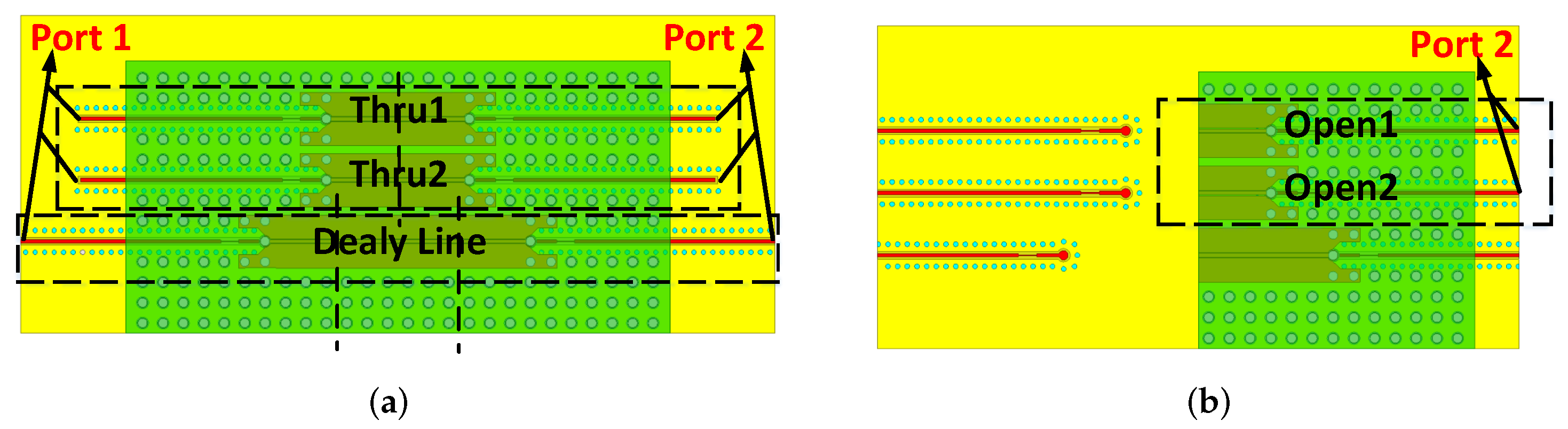

4.2. Measurement Method Based on the TRL Technique

5. Discussion

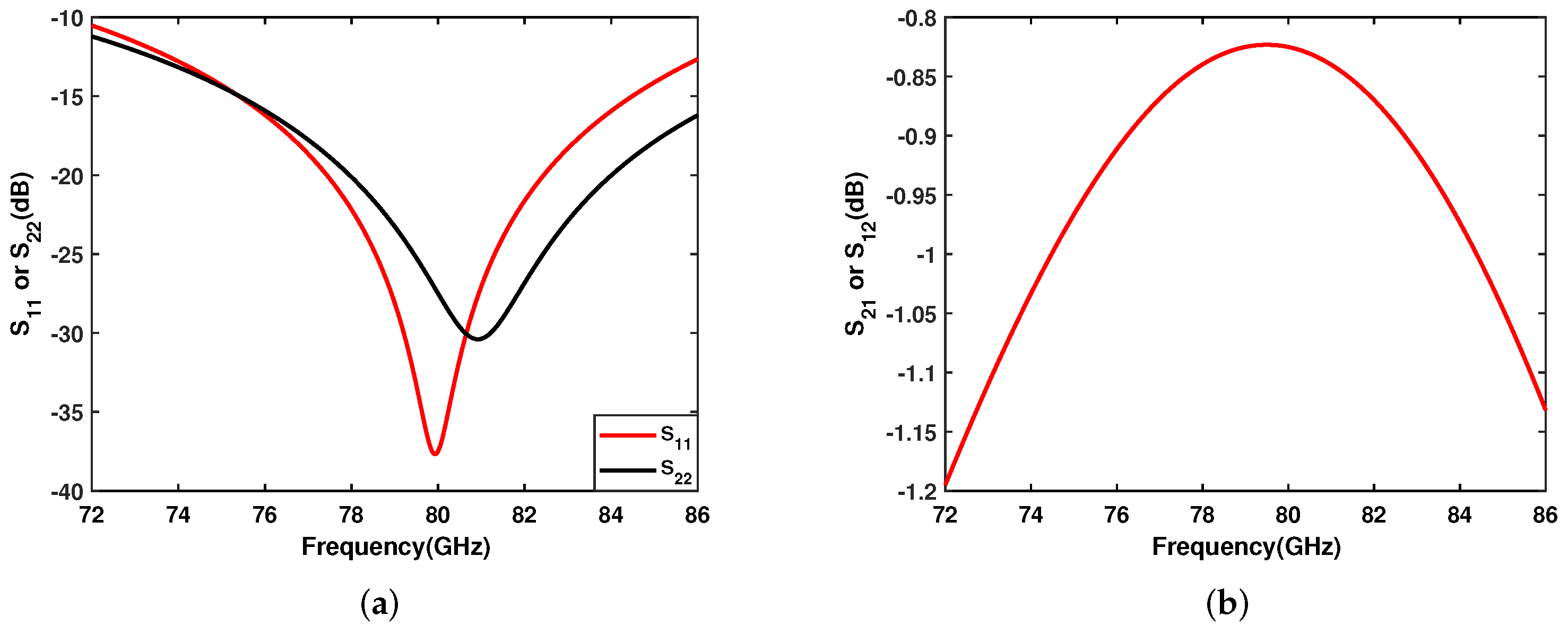

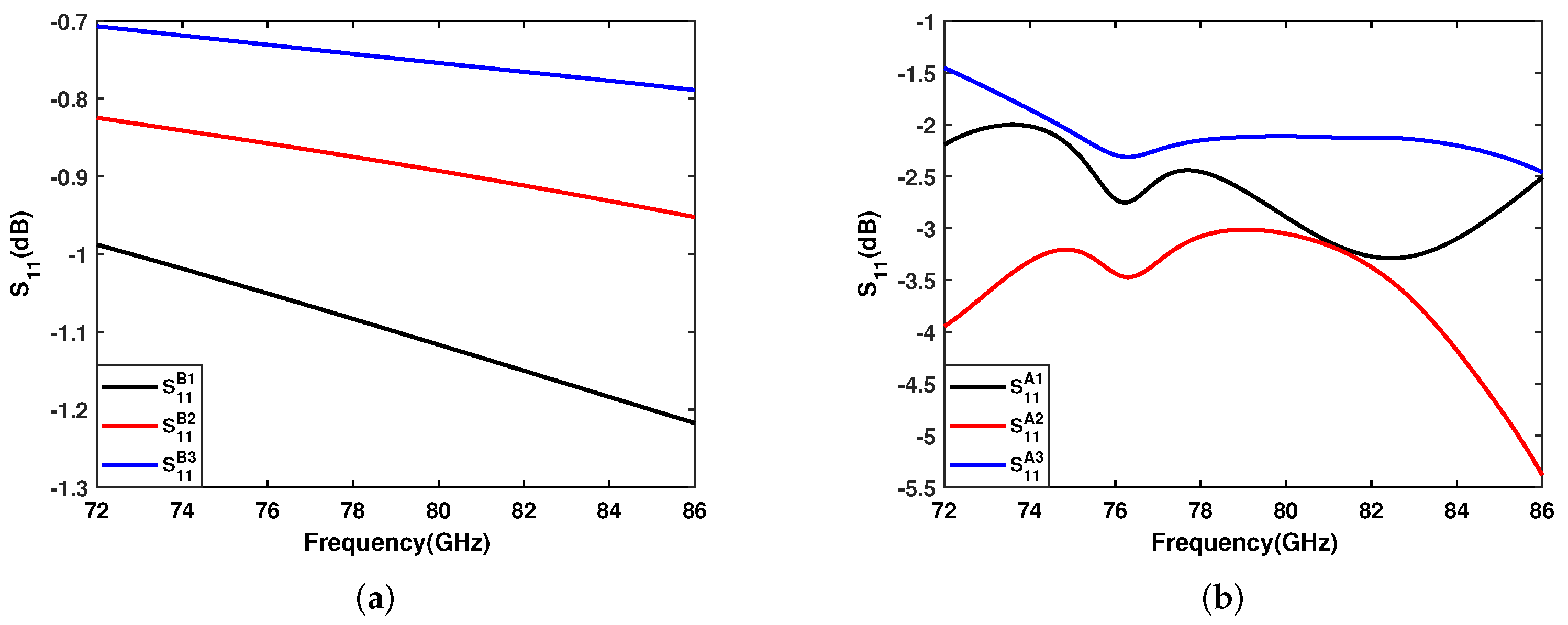

5.1. Simulation Results Based on Port Reduction Technology

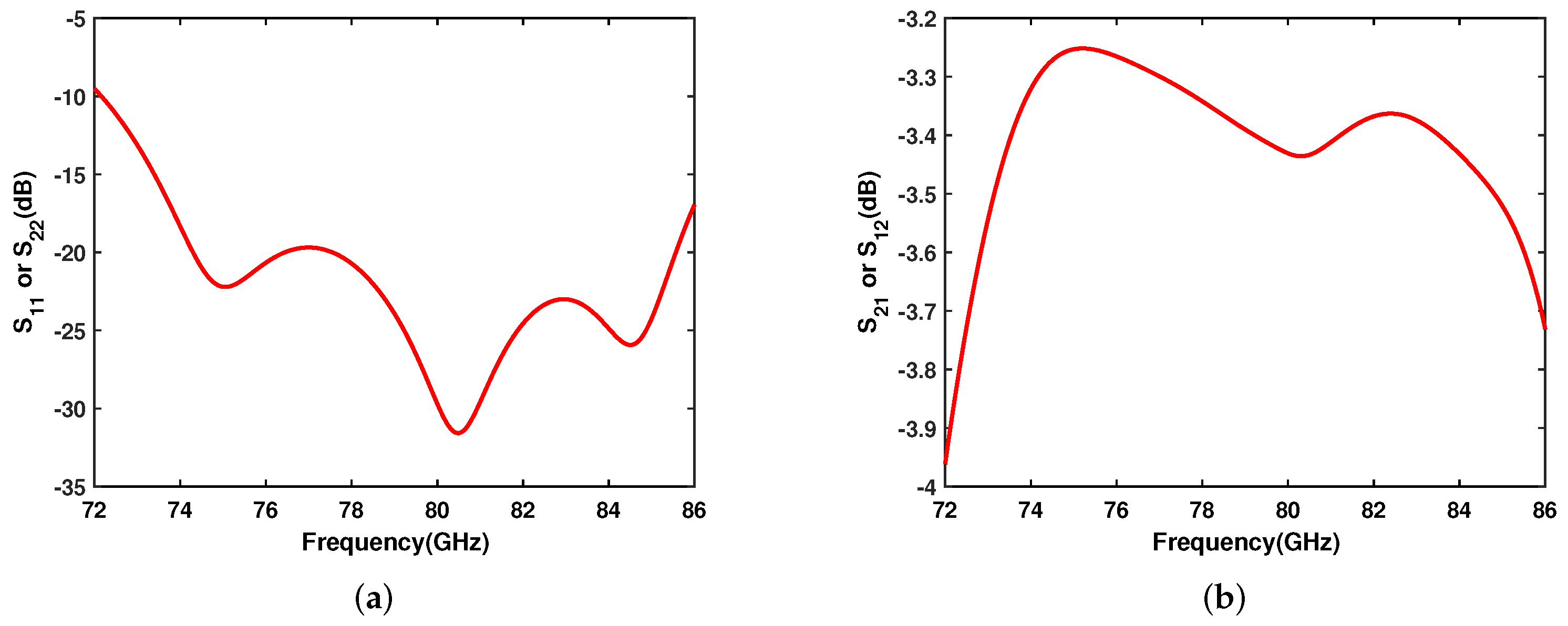

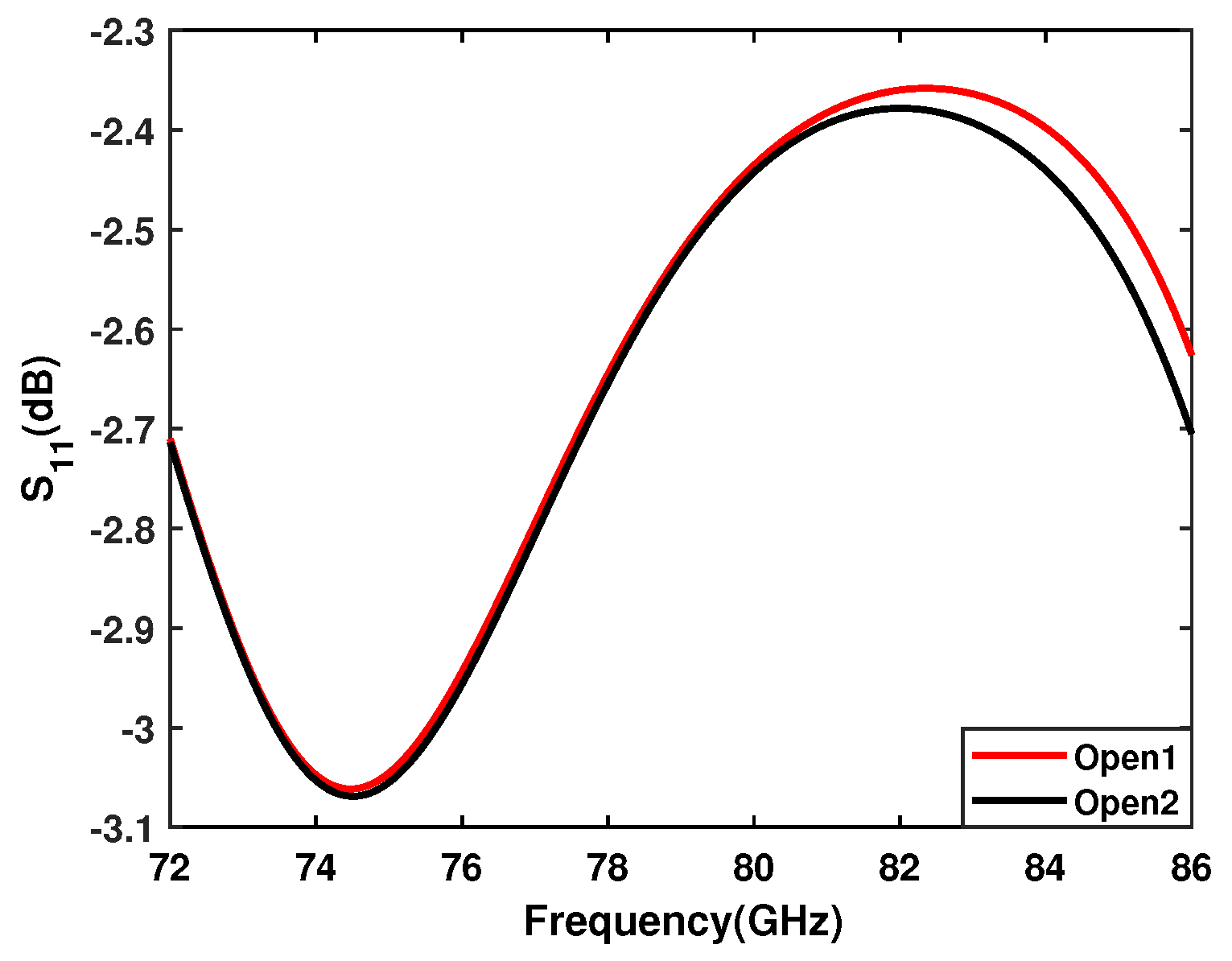

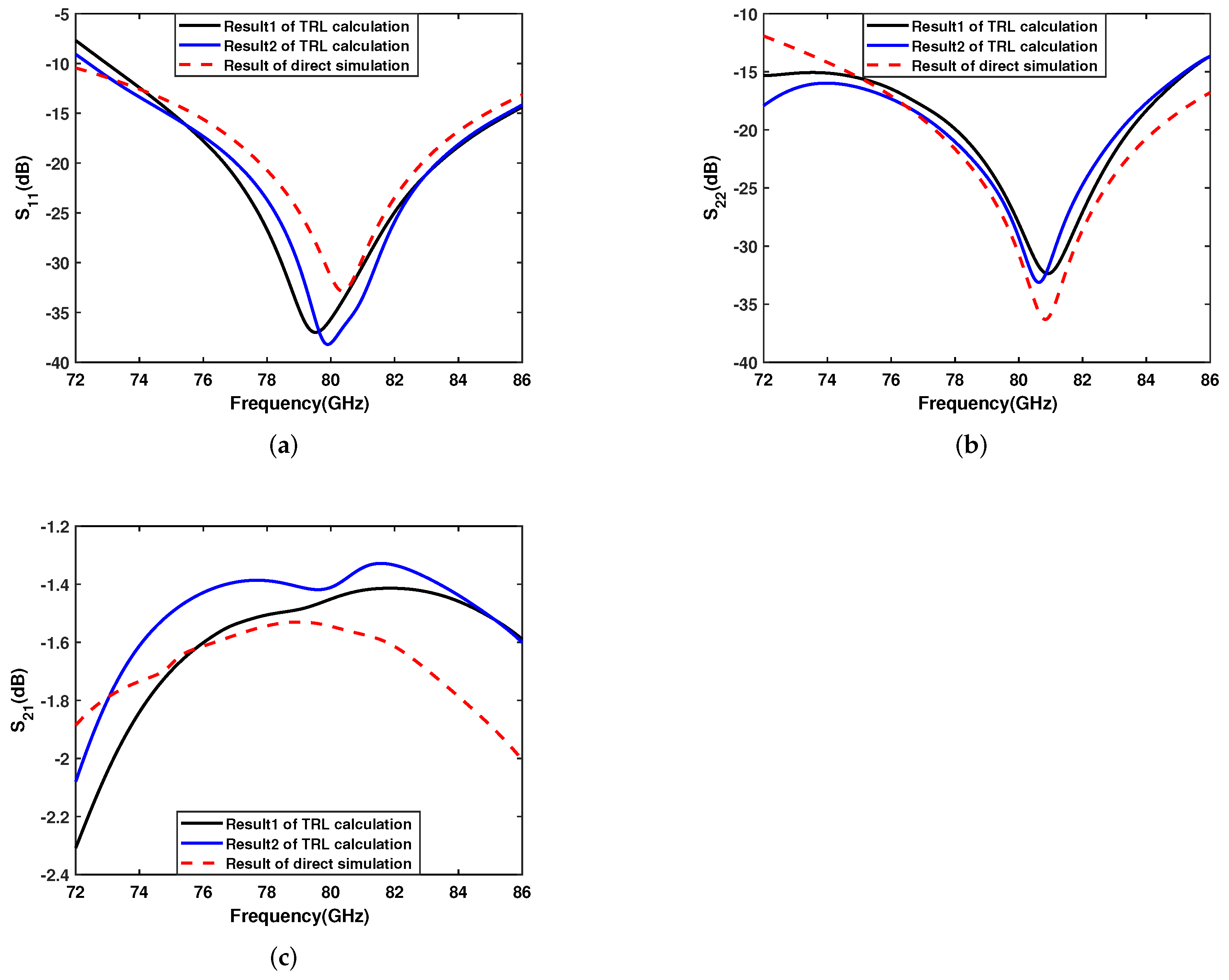

5.2. Simulation Results Based on TRL Technology

6. Conclusions

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

References

- Hedler, H.; Meyer, T.; Vasquez, B. Transfer Wafer Level Packaging. U.S. Patent US6727576 B2, 27 April 2004. [Google Scholar]

- Keser, B.; Kroehnert, S. Advances in Embedded and Fan-Out Wafer Level Packaging Technologies; Wiley-IEEE Press: Piscataway, NJ, USA, 2019; p. 51. [Google Scholar]

- Liu, D.; Zhang, Y. Antenna-in-Package Technology and Applications; Wiley-IEEE Press: Piscataway, NJ, USA, 2020; p. 219. [Google Scholar]

- Wu, D.; Dahlback, R.; Ojefors, E.; Carlsson, M.; Yoon, S.W. Advanced Wafer Level PKG Solutions for 60 GHz WiGig (802.11ad) Telecom Infrastructure. In Proceedings of the 2019 IEEE 69th Electronic Components and Technology Conference (ECTC), Las Vegas, NV, USA, 28–31 May 2019; pp. 968–971. [Google Scholar]

- Hartner, W.; Niessner, M.; Arcioni, F.; Fink, M.; Wojnowski, M. Reliability and Performance of Wafer Level Fan Out Package for Automotive Radar. In Proceedings of the 2019 International Wafer Level Packaging Conference (IWLPC), San Jose, CA, USA, 22–24 October 2019; pp. 1–11. [Google Scholar]

- Agethen, R.; PourMousavi, M.; Forstner, H.P.; Wojnowski, M.; Pressel, K.; Weigel, R.; Kissinger, D. 60 GHz industrial radar systems in silicon-germanium technology. In Proceedings of the 2013 IEEE MTT-S International Microwave Symposium Digest (MTT), Seattle, WA, USA, 2–7 June 2013; pp. 1–3. [Google Scholar]

- Beck, C.; Ng, H.J.; Agethen, R.; Pourmousavi, M.; Forstner, H.P.; Wojnowski, M.; Pressel, K.; Weigel, R.; Hagelauer, A.; Kissinger, D. Industrial mmWave Radar Sensor in Embedded Wafer-Level BGA Packaging Technology. IEEE Sens. J. 2016, 16, 6566–6578. [Google Scholar] [CrossRef]

- Nasr, I.; Jungmaier, R.; Baheti, A.; Noppeney, D.; Trotta, S. A Highly Integrated 60 GHz 6-Channel Transceiver with Antenna in Package for Smart Sensing and Short-Range Communications. IEEE J. Solid-State Circuits 2016, 51, 2066–2077. [Google Scholar] [CrossRef]

- Keser, B.; Amrine, C.; Duong, T.; Fay, O.; Wenzel, R. The Redistributed Chip Package: A Breakthrough for Advanced Packaging. In Proceedings of the 2007 IEEE 57th Electronic Components and Technology Conference (ECTC), Sparks, NV, USA, 29 May–1 June 2007; pp. 286–291. [Google Scholar]

- Kripesh, V.; Rao, V.S.; Kumar, A.; Sharma, G.; Lau, J. Design and development of a multi-die embedded micro wafer level package. In Proceedings of the 2008 IEEE 58th Electronic Components and Technology Conference (ECTC), Lake Buena Vista, FL, USA, 27–30 May 2008; pp. 1544–1549. [Google Scholar]

- Kumar, A.; Xia, D.; Sekhar, V.N.; Lim, S.; Keng, C.; Sharma, G.; Rao, V.S.; Kripesh, V.; Lau, J.H.; Kwong, D.L. Wafer level embedding technology for 3D wafer level embedded package. In Proceedings of the 2009 IEEE 59th Electronic Components and Technology Conference (ECTC), San Diego, CA, USA, 26–29 May 2009; pp. 1289–1296. [Google Scholar]

- Yoon, S.W.; Caparas, J.A.; Lin, Y.; Marimuthu, P.C. Advanced low profile PoP solution with embedded wafer level PoP (eWLB-PoP) technology. In Proceedings of the 2012 IEEE 62nd Electronic Components and Technology Conference (ECTC), San Diego, CA, USA, 29 May–1 June 2012; pp. 1250–1254. [Google Scholar]

- Tseng, C.F.; Liu, C.S.; Wu, C.H.; Yu, D. InFO (Wafer Level Integrated Fan-Out) Technology. In Proceedings of the 2016 IEEE 66th Electronic Components and Technology Conference (ECTC), Las Vegas, NV, USA, 31 May–3 June 2016; pp. 1–6. [Google Scholar]

- Hsieh, C.C.; Wu, C.H.; Yu, D. Analysis and Comparison of Thermal Performance of Advanced Packaging Technologies for State-of-the-Art Mobile Applications. In Proceedings of the 2016 IEEE 66th Electronic Components and Technology Conference (ECTC), Las Vegas, NV, USA, 31 May–3 June 2016; pp. 1430–1438. [Google Scholar]

- Wojnowski, M.; Pressel, K.; Beer, G.; Heinig, A. Vertical interconnections using through encapsulant via (TEV) and through silicon via (TSV) for high-frequency system-in-package integration. In Proceedings of the 2014 IEEE 16th Electronics Packaging Technology Conference (EPTC), Singapore, 3–5 December 2014; pp. 122–127. [Google Scholar]

- Lau, J.H.; Li, M.; Li, Q.M.; Chen, T.; Xu, I.; Yong, Q.X. Fan-Out Wafer-Level Packaging for Heterogeneous Integration. IEEE Trans. Compon. Packag. Manuf. Technol. 2018, 8, 1544–1560. [Google Scholar] [CrossRef]

- Chen, C.; Yu, D.; Wang, T.; Xiao, Z.; Wan, L. Warpage Prediction and Optimization for Embedded Silicon Fan-Out Wafer-Level Packaging Based on an Extended Theoretical Model. IEEE Trans. Compon. Packag. Manuf. Technol. 2019, 9, 845–853. [Google Scholar] [CrossRef]

- Fowler, M.; Massey, J.P.; Braun, T.; Voges, S.; Wohrmann, M. Investigation and Methods Using Various Release and Thermoplastic Bonding Materials to Reduce Die Shift and Wafer Warpage for eWLB Chip-First Processes. In Proceedings of the 2019 IEEE 69th Electronic Components and Technology Conference (ECTC), Las Vegas, NV, USA, 28–31 May 2019; pp. 363–369. [Google Scholar]

- Wu, M.L.; Lan, J.S. Simulation and Experimental Study of the Warpage of Fan-Out Wafer-Level Packaging: The Effect of the Manufacturing Process and Optimal Design. IEEE Trans. Compon. Packag. Manuf. Technol. 2019, 9, 1396–1405. [Google Scholar] [CrossRef]

- Lau, J.H.; Li, M.; Yang, L.; Li, M.; Xu, I.; Chen, T.; Chen, S.; Yong, Q.X.; Madhukumar, J.P.; Kai, W.; et al. Warpage Measurements and Characterizations of Fan-Out Wafer-Level Packaging With Large Chips and Multiple Redistributed Layers. IEEE Trans. Compon. Packag. Manuf. Technol. 2018, 8, 1729–1737. [Google Scholar] [CrossRef]

- Shih, M.K.; Huang, C.Y.; Chen, T.H.; Wang, C.C.; Tarng, D.; Hung, C.P. Electrical, Thermal, and Mechanical Characterization of eWLB, Fully Molded Fan-Out Package, and Fan-Out Chip Last Package. IEEE Trans. Compon. Packag. Manuf. Technol. 2019, 9, 1765–1775. [Google Scholar] [CrossRef]

- Lau, J.H.; Ming, L.; Tian, D.; Fan, N.; Yong, Q. Warpage and Thermal Characterization of Fan-Out Wafer-Level Packaging. IEEE Trans. Compon. Packag. Manuf. Technol. 2017, 7, 1729–1738. [Google Scholar] [CrossRef]

- Dong, H.; Chen, J.; Hou, D.; Xiang, Y.; Hong, W. A Low-Loss Fan-Out Wafer-Level Package with a Novel Redistribution Layer Pattern and Its Measurement Methodology for Millimeter-Wave Application. IEEE Trans. Compon. Packag. Manuf. Technol. 2020, 10, 1073–1078. [Google Scholar] [CrossRef]

- Wojnowski, M.; Pressel, K.; Beer, G.; Heinig, A. Co-Design of High-Isolation Chip-Package-Board in eWLB Package for 77 GHz Automotive Radar Application. In Proceedings of the 2019 IEEE 21st Electronics Packaging Technology Conference (EPTC), Singapore, 4–6 December 2019; pp. 519–522. [Google Scholar]

- Zhu, C.; Duan, Z.; Dai, Y. Design of CMOS Chip to Waveguide Transition in eWLB Package for Full W-band Applications. In Proceedings of the 2020 IEEE MTT-S International Microwave Workshop Series on Advanced Materials and Processes for RF and THz Applications (IMWS-AMP), Suzhou, China, 29–31 July 2020; pp. 1–3. [Google Scholar]

- Huynh, N.H.; Saverio, T.; Wojnowski, M.; Haubner, G. eWLB package for millimeter wave application. In Proceedings of the 2015 European Microelectronics Packaging Conference (EMPC), Friedrichshafen, Germany, 14–16 September 2015; pp. 1–5. [Google Scholar]

- Henawy, M.A.; Schneider, M. Integrated antennas in eWLB packages for 77 GHz and 79 GHz automotive radar sensors. In Proceedings of the 2011 41st European Microwave Conference, Manchester, UK, 10–13 October 2011; pp. 1312–1315. [Google Scholar]

- Wojnowski, M.; Sommer, G.; Klumpp, A.; Weber, W. Electrical Characterization of 3D Interconnection Structures up to Millimeter Wave Frequencies. In Proceedings of the 2008 10th Electronics Packaging Technology Conference, Singapore, 9–12 December 2008; pp. 1393–1402. [Google Scholar]

- Hernandez-Sosa, G.; Romo, G.; Torres-Torres, R. Characterization and modeling of electronic packages using S-parameters. In Proceedings of the 2008 7th International Caribbean Conference on Devices, Circuits and Systems, Cancun, Mexico, 28–30 April 2008; pp. 1–6. [Google Scholar]

- Engl, M.; Schiller, K.; Eurskens, W.; Weigel, R. High resolution time domain and frequency domain package characterization up to 65 GHz. In Proceedings of the 56th Electronic Components and Technology Conference 2006 (ECTC), San Diego, CA, USA, 30 May–2 June 2006; pp. 7–13. [Google Scholar]

- Lu, H.C.; Chu, T.H. Port reduction methods for scattering matrix measurement of an n-port network. IEEE Trans. Microw. Theory Tech. 2000, 48, 959–968. [Google Scholar]

- Engen, G.F.; Hoer, C.A. Thru-Reflect-Line: An Improved Technique for Calibrating the Dual Six-Port Automatic Network Analyzer. IEEE Trans. Microw. Theory Tech. 1979, 27, 987–993. [Google Scholar] [CrossRef] [Green Version]

- Marks, R.B. A multiline method of network analyzer calibration. IEEE Trans. Microw. Theory Tech. 1991, 39, 1205–1215. [Google Scholar] [CrossRef] [Green Version]

- Chen, Y.; Li, J.; Ding, F.; Cao, L. Antenna in package design and measurement for millimeter-wave applications in fan-out wafer-level package. IEICE Electron. Express 2022. advance online publication. [Google Scholar] [CrossRef]

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2022 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Chen, Y.; Li, J.; Cao, L. Design for the Package-Board Transition and Its Testability Design in the Fan-Out Wafer-Level Package. Electronics 2022, 11, 1922. https://doi.org/10.3390/electronics11121922

Chen Y, Li J, Cao L. Design for the Package-Board Transition and Its Testability Design in the Fan-Out Wafer-Level Package. Electronics. 2022; 11(12):1922. https://doi.org/10.3390/electronics11121922

Chicago/Turabian StyleChen, Ying, Jun Li, and Liqiang Cao. 2022. "Design for the Package-Board Transition and Its Testability Design in the Fan-Out Wafer-Level Package" Electronics 11, no. 12: 1922. https://doi.org/10.3390/electronics11121922