A High Performance 0.18 μm RF Switch for Multi-Standard

Abstract

:1. Introduction

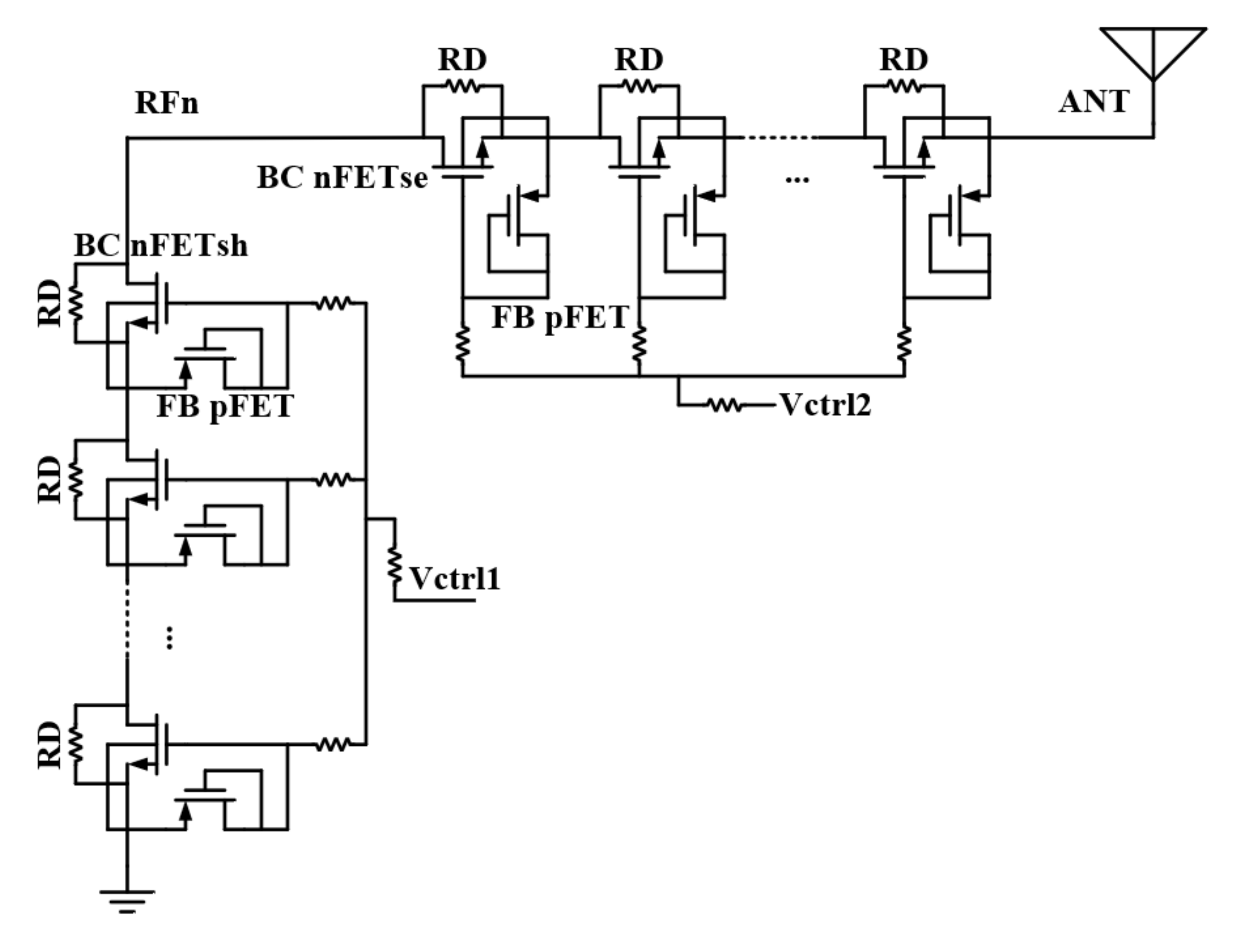

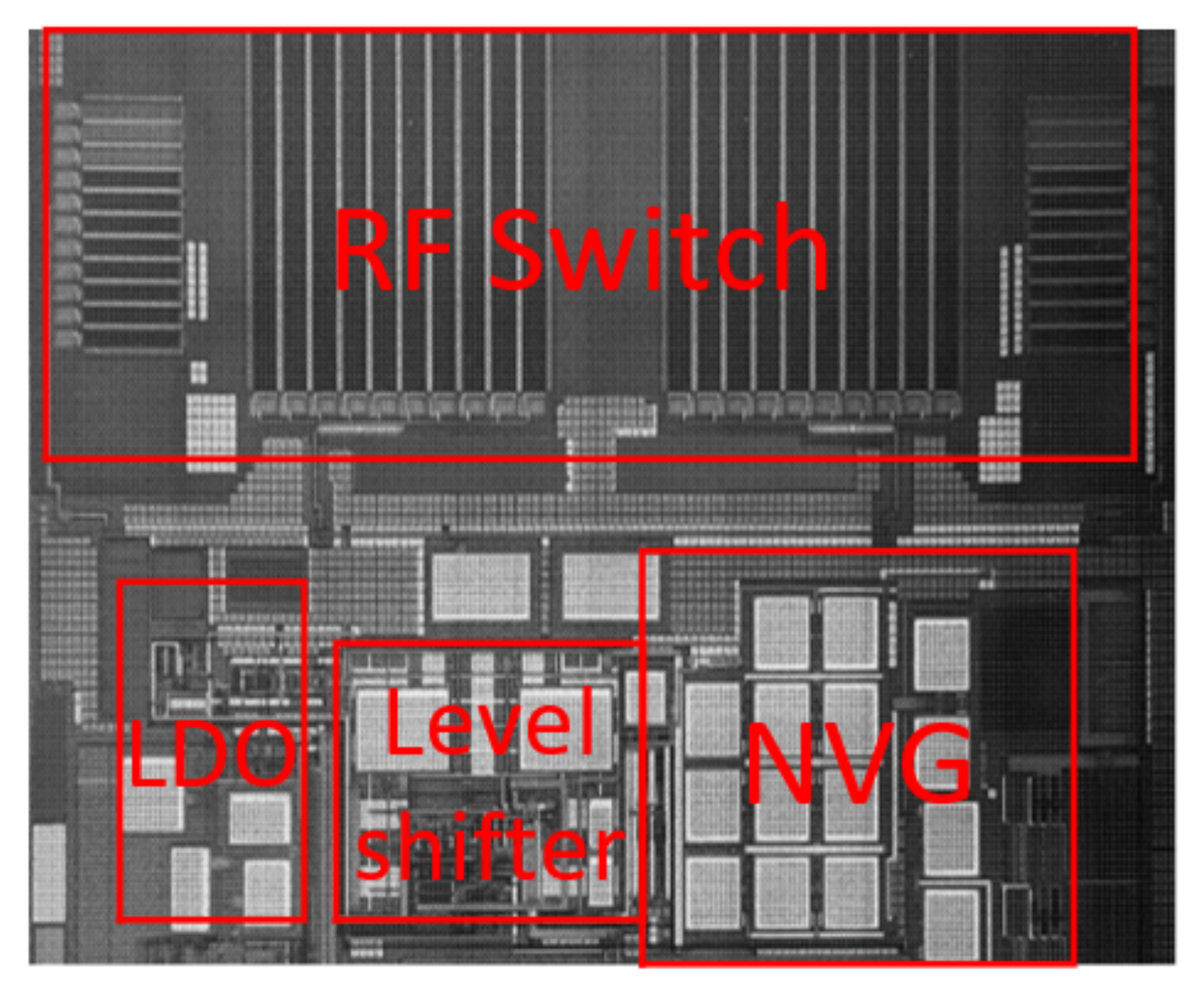

2. SOI SPDT Switch Design

2.1. Biasing Strategy

2.2. Circuit of NVG

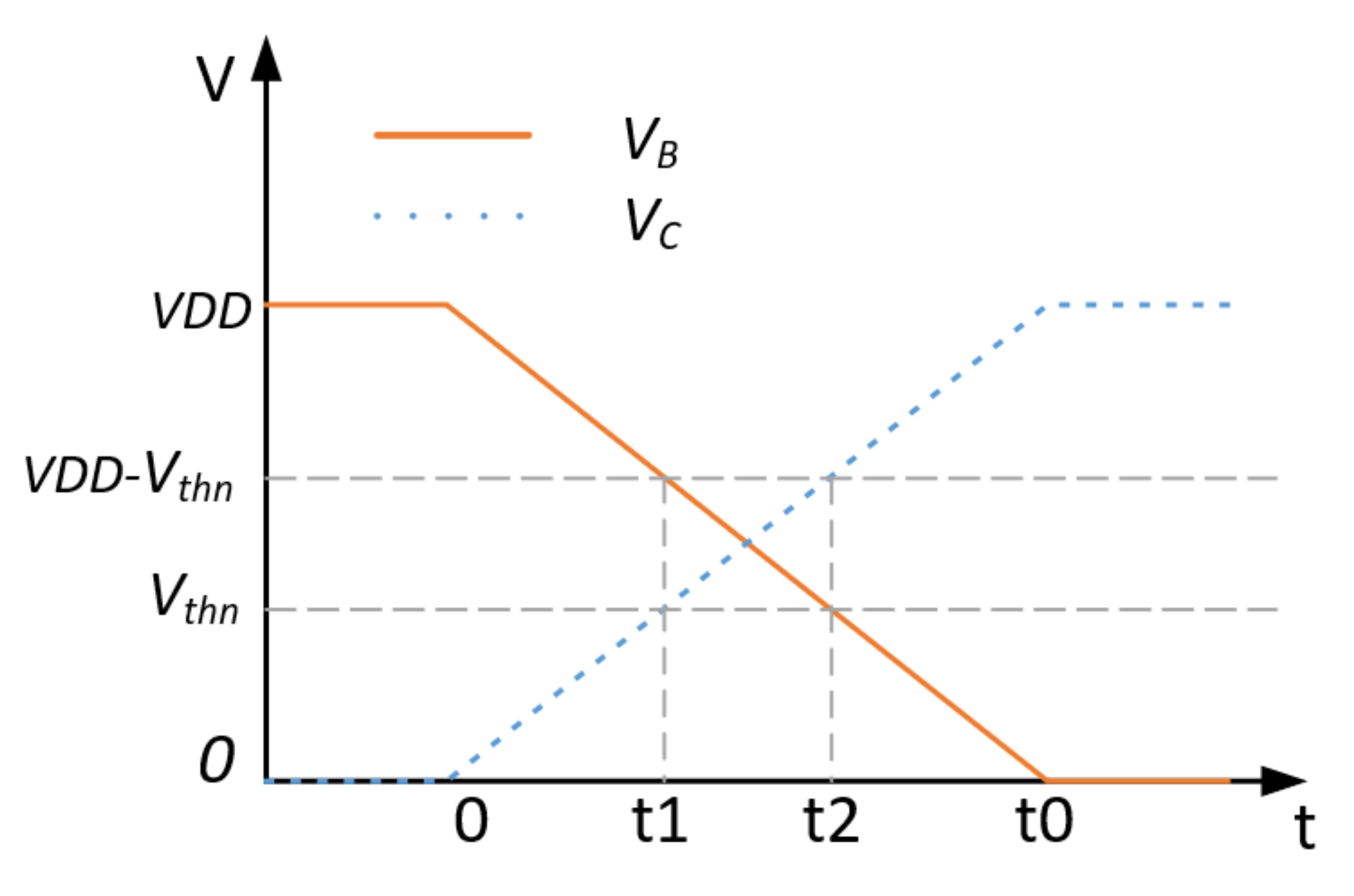

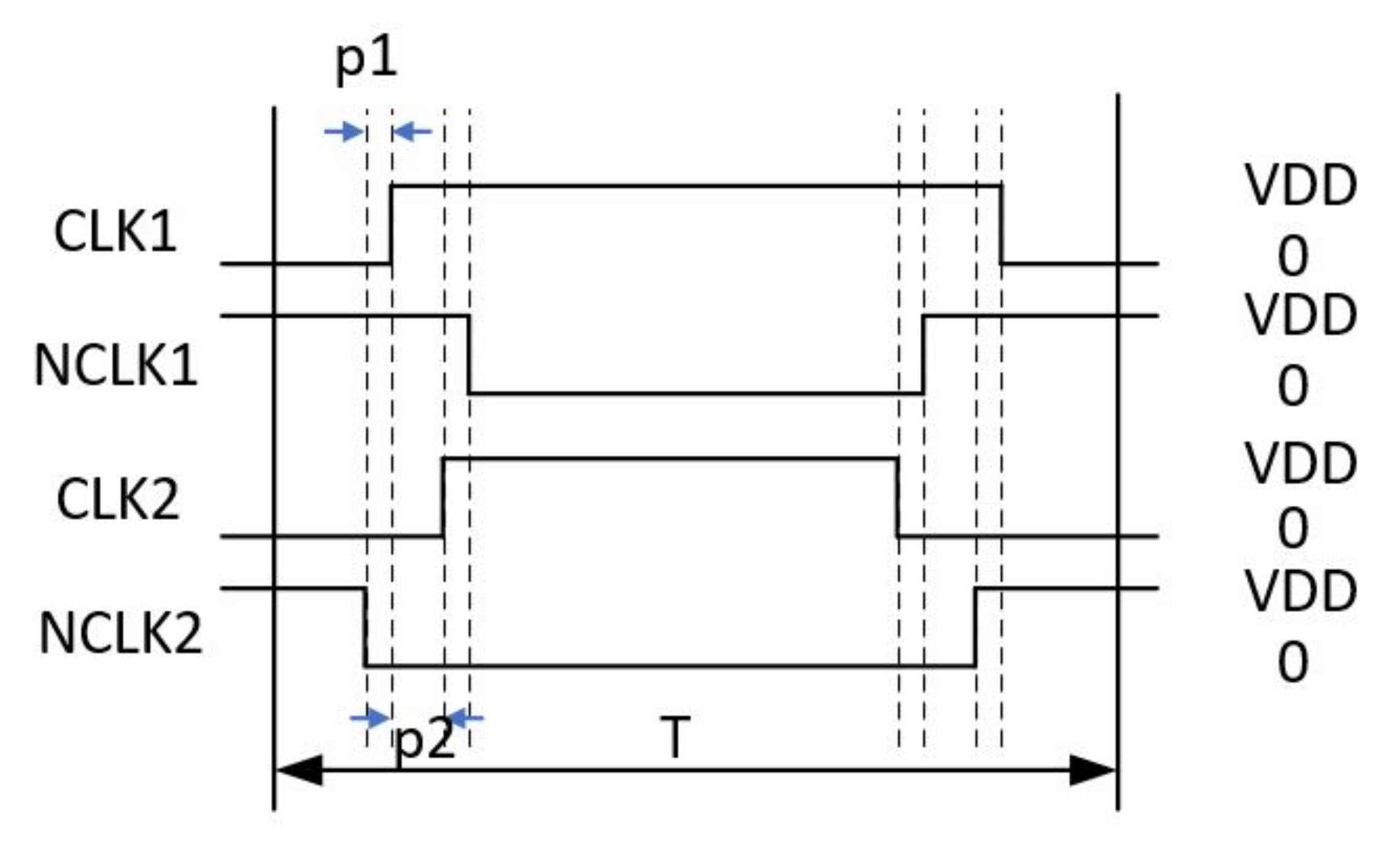

2.3. Reduced Time Constant

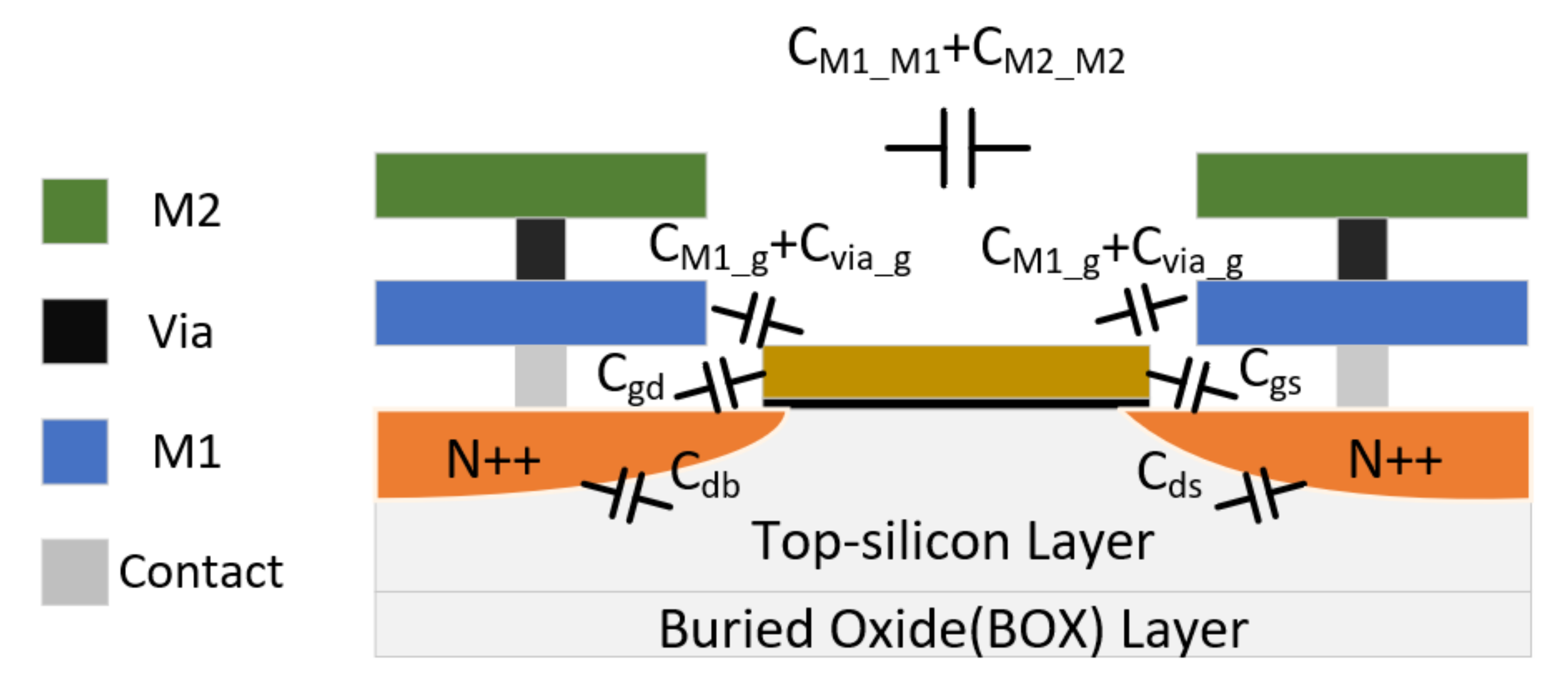

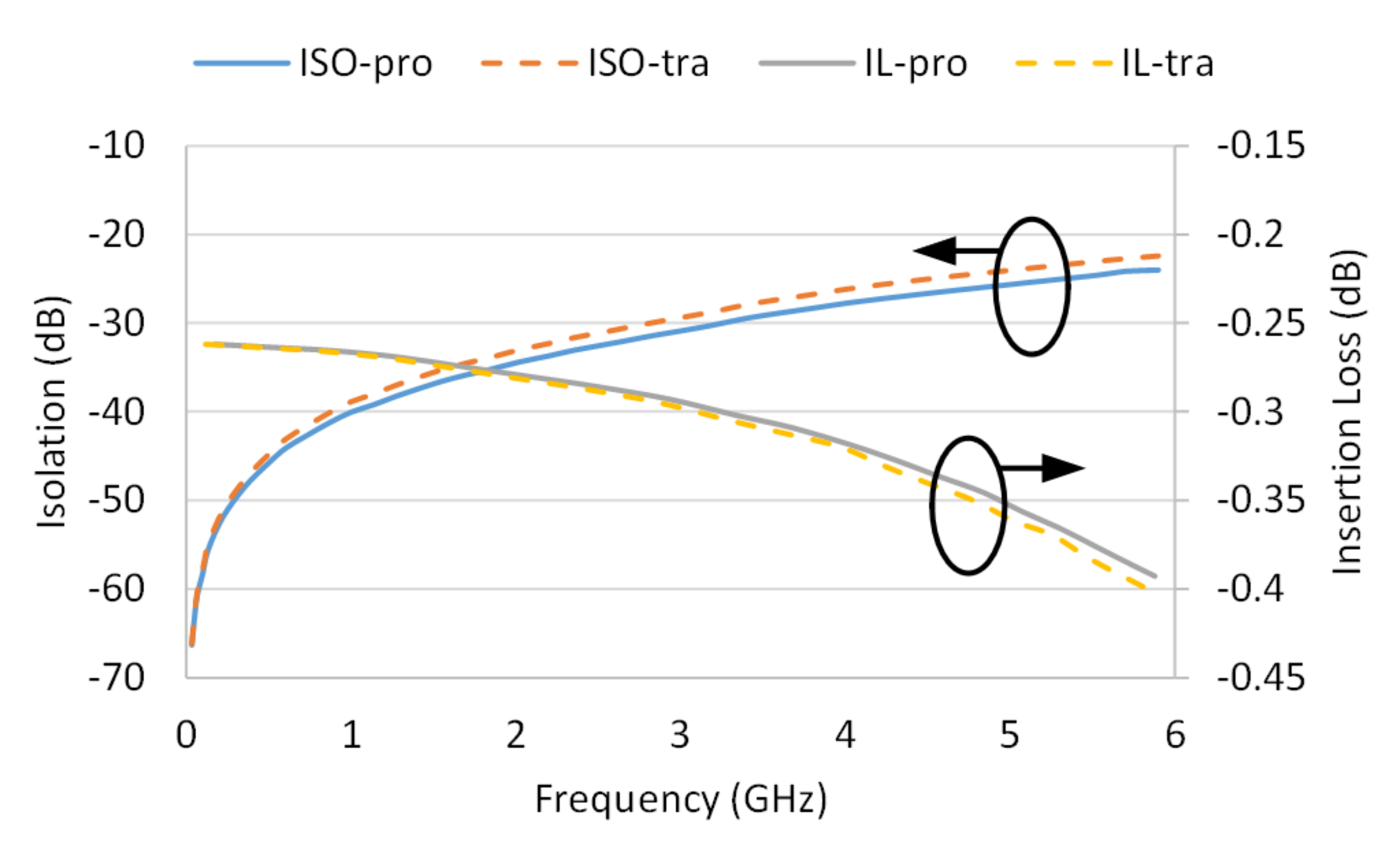

2.3.1. Analysis of IL and ISO

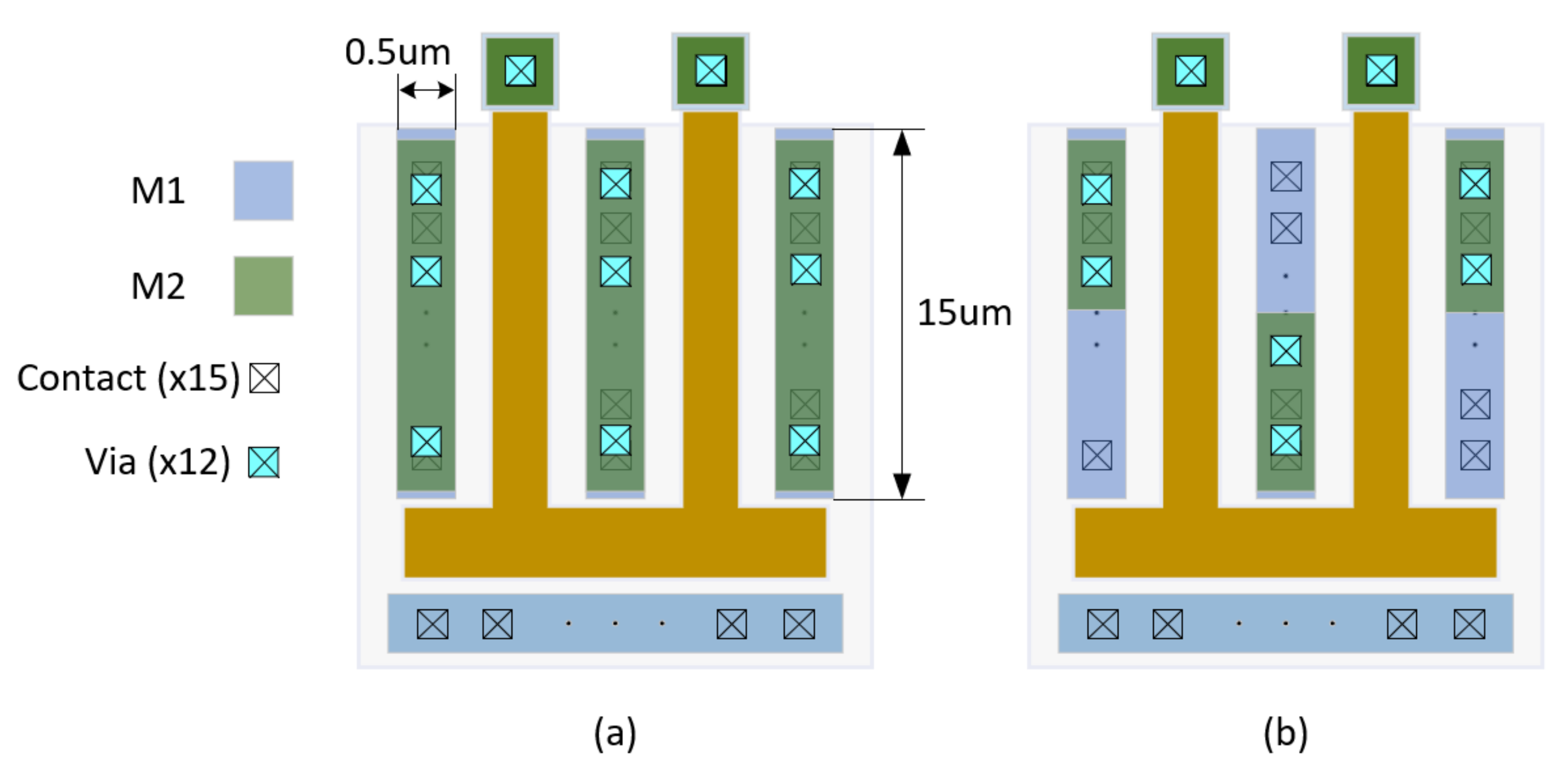

2.3.2. FET with Reduced Time Constant

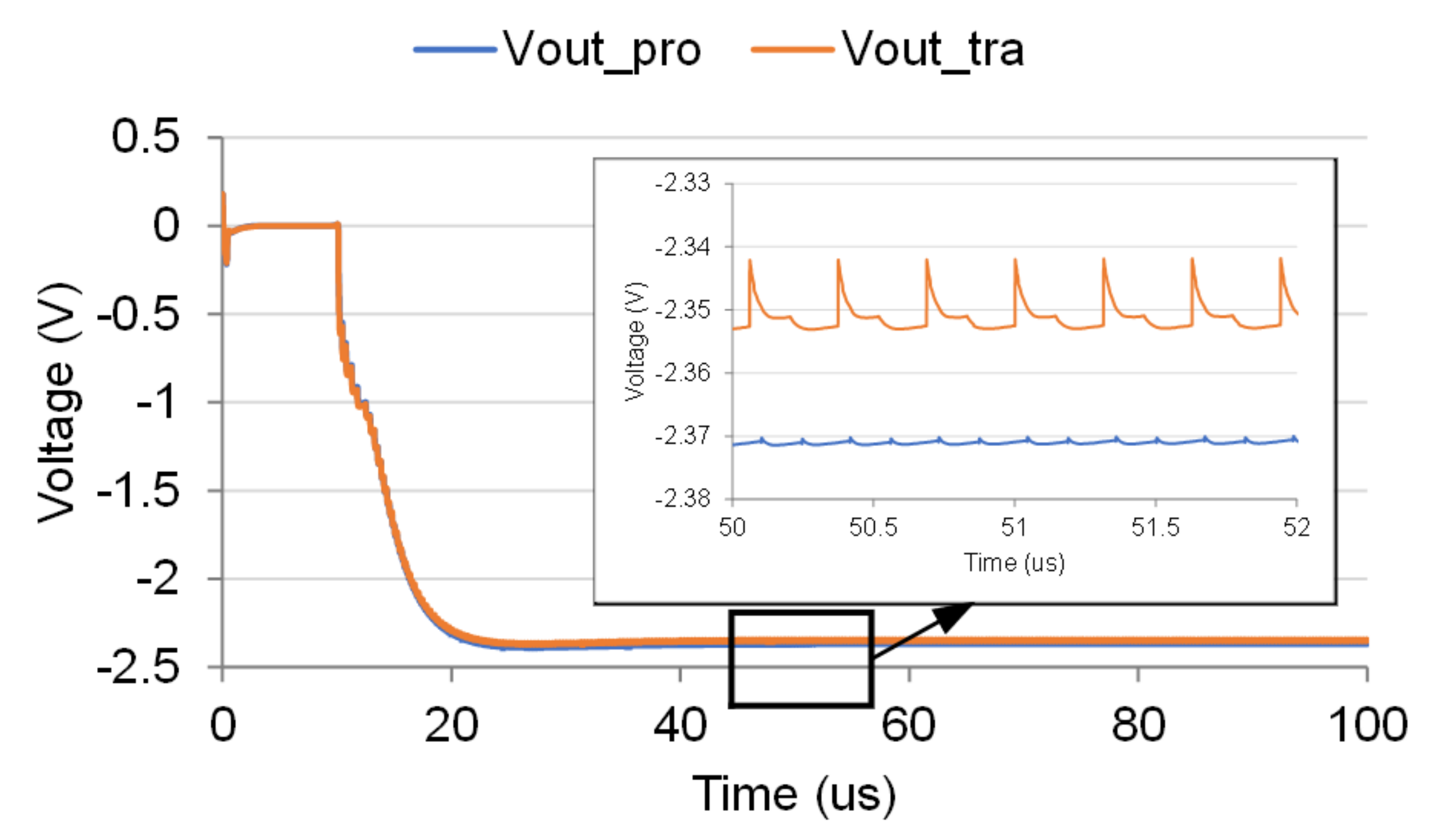

3. Measured Results

4. Conclusions

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

References

- Truong, T.K.N.; Lee, D.S.; Lee, K.Y. A Low Insertion-Loss, High-Isolation Switch Based on Single Pole Double Throw for 2.4 GHz BLE Applications. IEIE Trans. Smart Process. Comput. 2016, 5, 164–168. [Google Scholar] [CrossRef] [Green Version]

- Yeh, M.-C.; Tsai, Z.-M.; Liu, R.-C.; Lin, K.Y.; Chang, Y.-T.; Wang, H. Design and analysis for a miniature CMOS SPDT switch using body-floating technique to improve power performance. IEEE Trans. Microw. Theory Tech. 2006, 54, 31–39. [Google Scholar] [CrossRef]

- Zhang, T.; Subramanian, V.; Boeck, G. Comparison of regular and floating bulk transistors in ultra-wideband CMOS T/R switches. In Proceedings of the 2012 19th International Conference on Microwaves, Radar & Wireless Communications, Warsaw, Poland, 21–23 May 2012; Volume 1, pp. 293–296. [Google Scholar] [CrossRef]

- Li, Z.; O, K. 15-GHz fully integrated nMOS switches in a 0.13-/spl mu/m CMOS process. IEEE J. Solid-State Circuits 2005, 40, 2323–2328. [Google Scholar] [CrossRef]

- Marian, V.; Verdier, J.; Allard, B.; Vollaire, C. Design of a wideband multi-standard antenna switch for wireless communication devices. Microelectron. J. 2011, 42, 790–797. [Google Scholar] [CrossRef]

- Wang, X.S.; Yue, C.P. A Dual-Band SP6T T/R Switch in SOI CMOS With 37-dBm P-0.1 dB for GSM/W-CDMA Handsets. IEEE Trans. Microw. Theory Tech. 2014, 62, 861–870. [Google Scholar] [CrossRef]

- Zhang, Z.; Zhang, G.; Yu, K.; Lin, J.; Huang, L. Effects and contrasts of silicon-on-insulator floating-body and body-contacted field-effect transistors to the design of high-performance antenna switches. IET Microwaves Antennas Propag. 2016, 10, 507–516. [Google Scholar] [CrossRef]

- Zhang, H.; Cui, Q.; Yan, X.; Shi, J.; Lin, F. A 0.5–3.0 GHz SP4T RF switch with improved body self-biasing technique in 130-nm SOI CMOS. J. Semicond. 2020, 41, 102404. [Google Scholar] [CrossRef]

- Im, D.; Lee, K. Characterization and optimization of partially depleted SOI MOSFETs for high power RF switch applications. Solid-State Electron. 2013, 90, 94–98. [Google Scholar] [CrossRef]

- Guan, H.; Sun, H.; Bao, J.; Wang, Z.; Zhou, S.; Zhu, H. High-performance RF Switch in 0.13 μm RF SOI process. J. Semicond. 2019, 40, 022401. [Google Scholar] [CrossRef]

- Zhang, Z.; Huang, L.; Yu, K.; Zhang, G. A novel body self-biased technique for enhanced RF performance of a SP8T antenna switch in partially depleted CMOS-SOI technology. In Proceedings of the 2014 12th IEEE International Conference on Solid-State and Integrated Circuit Technology (ICSICT), Guilin, China, 28–31 October 2014; pp. 1–3. [Google Scholar] [CrossRef]

- Kim, H.W.; Ahn, M.; Lee, O.; Kim, H.; Kim, H.; Lee, C.H. Analysis and Design of a Fully-Integrated High-Power Differential CMOS T/R Switch and Power Amplifier Using Multi-Section Impedance Transformation Technique. Electronics 2021, 10, 1028. [Google Scholar] [CrossRef]

- Zhang, Y.; Wang, J.; Li, Q.; Li, X. Antenna-in-Package and Transmit–Receive Switch for Single-Chip Radio Transceivers of Differential Architecture. IEEE Trans. Circuits Syst. I Regul. Pap. 2008, 55, 3564–3570. [Google Scholar] [CrossRef]

- Chen, L.; Gan, Y.B. An asymmetrical bulk cmos switch for 2.4 GHZ application. Prog. Electromagn. Res. Lett. 2017, 66, 99–104. [Google Scholar] [CrossRef] [Green Version]

- Bhandarkar, S.; Nakhate, S. Asymmetric Inductive Substrate bias RF SPDT Switch. Mater. Today Proc. 2017, 4, 10351–10355. [Google Scholar] [CrossRef]

- Li, Q.; Zhang, Y.P.; Yeo, K.S.; Lim, W.M. 16.6- and 28-GHz Fully Integrated CMOS RF Switches With Improved Body Floating. IEEE Trans. Microw. Theory Tech. 2008, 56, 339–345. [Google Scholar] [CrossRef]

- Ahn, M.; Kim, H.W.; Lee, C.H.; Laskar, J. A 1.8-GHz 33-dBm P 0.1-dB CMOS T/R Switch Using Stacked FETs With Feed-Forward Capacitors in a Floated Well Structure. IEEE Trans. Microw. Theory Tech. 2009, 57, 2661–2670. [Google Scholar] [CrossRef]

- Malladi, V.N.; Miller, M. A 48 dBm peak power RF switch in SOI process for 5G mMIMO applications. In Proceedings of the 2019 IEEE 19th Topical Meeting on Silicon Monolithic Integrated Circuits in RF Systems (SiRF), Orlando, FL, USA, 20–23 January 2019; pp. 1–3. [Google Scholar] [CrossRef]

- Cheon, C.D.; Cho, M.K.; Rao, S.G.; Cardoso, A.S.; Connor, J.D.; Cressler, J.D. A New Wideband, Low Insertion Loss SiGe Digital Step Attenuator A New Wideband, Low Insertion Loss SiGe Digital Step Attenuator. In Proceedings of the 2020 IEEE BiCMOS and Compound Semiconductor Integrated Circuits and Technology Symposium (BCICTS), Monterey, CA, USA, 16–19 November 2020; Volume 30, pp. 1–5. [Google Scholar] [CrossRef]

- Bansal, D.; Bajpai, A.; Kumar, P.; Kaur, M.; Kumar, A.; Chandran, A.; Rangra, K. Low voltage driven RF MEMS capacitive switch using reinforcement for reduced buckling. J. Micromechanics Microengineering 2017, 27, 024001. [Google Scholar] [CrossRef]

- Yamane, D.; Sun, W.; Seita, H.; Kawasaki, S.; Fujita, H.; Toshiyoshi, H. A Ku-band Dual-SPDT RF-MEMS Switch by Double-Side SOI Bulk Micromachining. J. Microelectromechanical Syst. 2011, 20, 1211–1221. [Google Scholar] [CrossRef]

- Li, Q.; Zhang, Y.P. CMOS T/R Switch Design: Towards Ultra-Wideband and Higher Frequency. IEEE J. Solid-State Circuits 2007, 42, 563–570. [Google Scholar] [CrossRef]

- Wang, X.S.; Wang, X.; Lu, F.; Zhang, C.; Dong, Z.; Wang, L.; Ma, R.; Shi, Z.; Wang, A.; Chang, M.C.F.; et al. Concurrent Design Analysis of High-Linearity SP10T Switch With 8.5 kV ESD Protection. IEEE J. Solid-State Circuits 2014, 49, 1927–1941. [Google Scholar] [CrossRef]

- Chen, A. Highly integrated CMOS RF SPDT switch with ESD and unit cell optimisation in MCM. Electron. Lett. 2013, 49, 549–551. [Google Scholar] [CrossRef] [Green Version]

- Rikan, B.S.; Kim, D.; Choi, K.D.; Hejazi, A.; Yoo, J.M.; Pu, Y.; Kim, S.; Huh, H.; Jung, Y.; Lee, K.Y. T/R RF Switch with 150 ns Switching Time and over 100 dBc IMD for Wideband Mobile Applications in Thick Oxide SOI Process. Sensors 2022, 22, 507. [Google Scholar] [CrossRef] [PubMed]

- Yu, K.; Li, S.; Zhang, G.; Zhang, Z.; Tong, Q.; Zou, X. Design Considerations of Charge Pump for Antenna Switch Controller With SOI CMOS Technology. IEEE Trans. Circuits Syst. II Express Briefs 2017, 64, 229–233. [Google Scholar] [CrossRef]

- Eid, M.H.; Rodriguez-Villegas, E. Analysis of reversion losses in charge pumps and its impact on efficiency for low power design. In Proceedings of the 2017 15th IEEE International New Circuits and Systems Conference (NEWCAS), Strasbourg, France, 25–28 June 2017; pp. 9–12. [Google Scholar] [CrossRef]

- Li, X.J.; Zhang, Y.P. An overview of recent advances in CMOS T/R switch designs. In Proceedings of the APMC 2009—Asia Pacific Microwave Conference 2009, Singapore, 7–10 December 2009; pp. 1747–1750. [Google Scholar] [CrossRef]

- Im, D.; Kim, B.K.; Im, D.K.; Lee, K. A Stacked-FET Linear SOI CMOS Cellular Antenna Switch With an Extremely Low-Power Biasing Strategy. IEEE Trans. Microw. Theory Tech. 2015, 63, 1964–1977. [Google Scholar] [CrossRef]

- Shi, S.; Meng, F.; Hu, J.; Mou, S.; Ma, K. A 10-Watts 0.5-6 GHz SPDT Switch in 0.13-um CMOS SOI for 5G-Compatible IoT Applications. In Proceedings of the 2020 Cross Strait Radio Science and Wireless Technology Conference, CSRSWTC 2020—Proceedings, Fuzhou, China, 13–16 December 2020; pp. 1–3. [Google Scholar] [CrossRef]

- Zhu, H.; Li, Q.; Sun, H.; Wang, Z.; Liu, R.; Liu, Y. Ultra low loss and high linearity RF switch using 130 nm SOI CMOS process. In Proceedings of the 2017 IEEE 12th International Conference on ASIC (ASICON), Guiyang, China, 25–28 October 2017; pp. 698–701. [Google Scholar] [CrossRef]

| Wireless Standard | Peak Power (dBm) | Band (GHz) | IL (dB) | ISO (dB) | IIP3 (dBm) |

|---|---|---|---|---|---|

| GSM | 35 | 0.95/1.95 | <1 | 35 | 65 |

| 802.11x | 18 | 2.4/5.8 | <1 | 25 | 58 |

| WCDMA | 25 | 0.85/1.9/2.1 | <1 | 25 | 65 |

| Parameter | Value | Parameter | Value |

|---|---|---|---|

| 90.0 pF/m | (0.24 μm × 0.24 μm) | 10 | |

| 85.2 pF/m | 0.085 | ||

| 0.547 nF/m | (0.285 μm × 0.285 μm) | 3.9 | |

| 1.03 × 10 F/m | 0.080 |

| Parameter | [10] | [6] | [30] | [31] | [5] | This Work |

|---|---|---|---|---|---|---|

| RF switch | SPDT | SP8T | SP6T | SP4T | SP4T | SPDT |

| Band (GHz) | 1/3 | 0.9/1.9 | 0.9/1.9 | DC/6 | 0.55/2.5 | DC/6 |

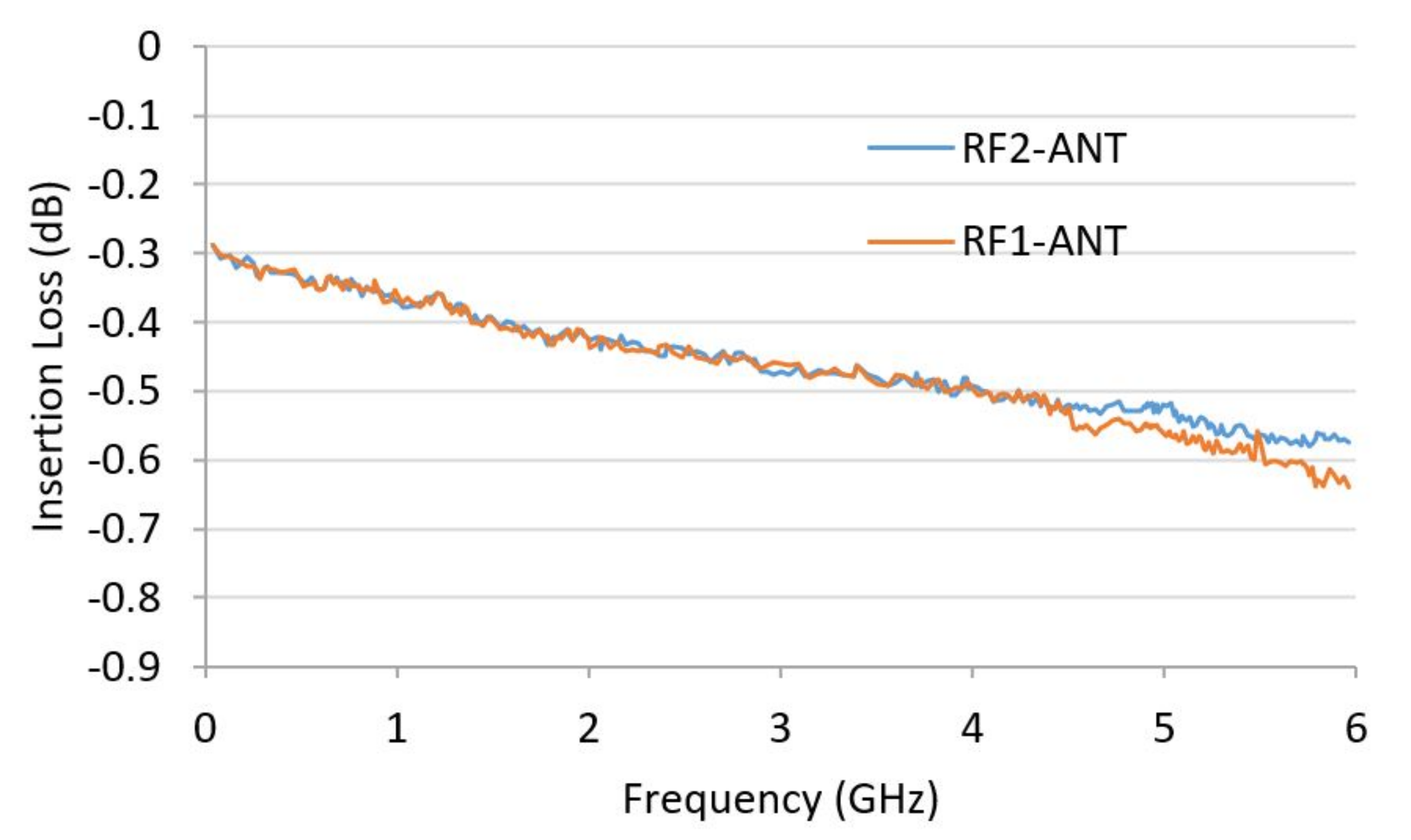

| IL (@1/2 GHz) | 0.7/0.9 | 0.45/0.52 | 0.82/0.88 | 0.3/0.4 | 0.55/0.75 | 0.36/0.43 |

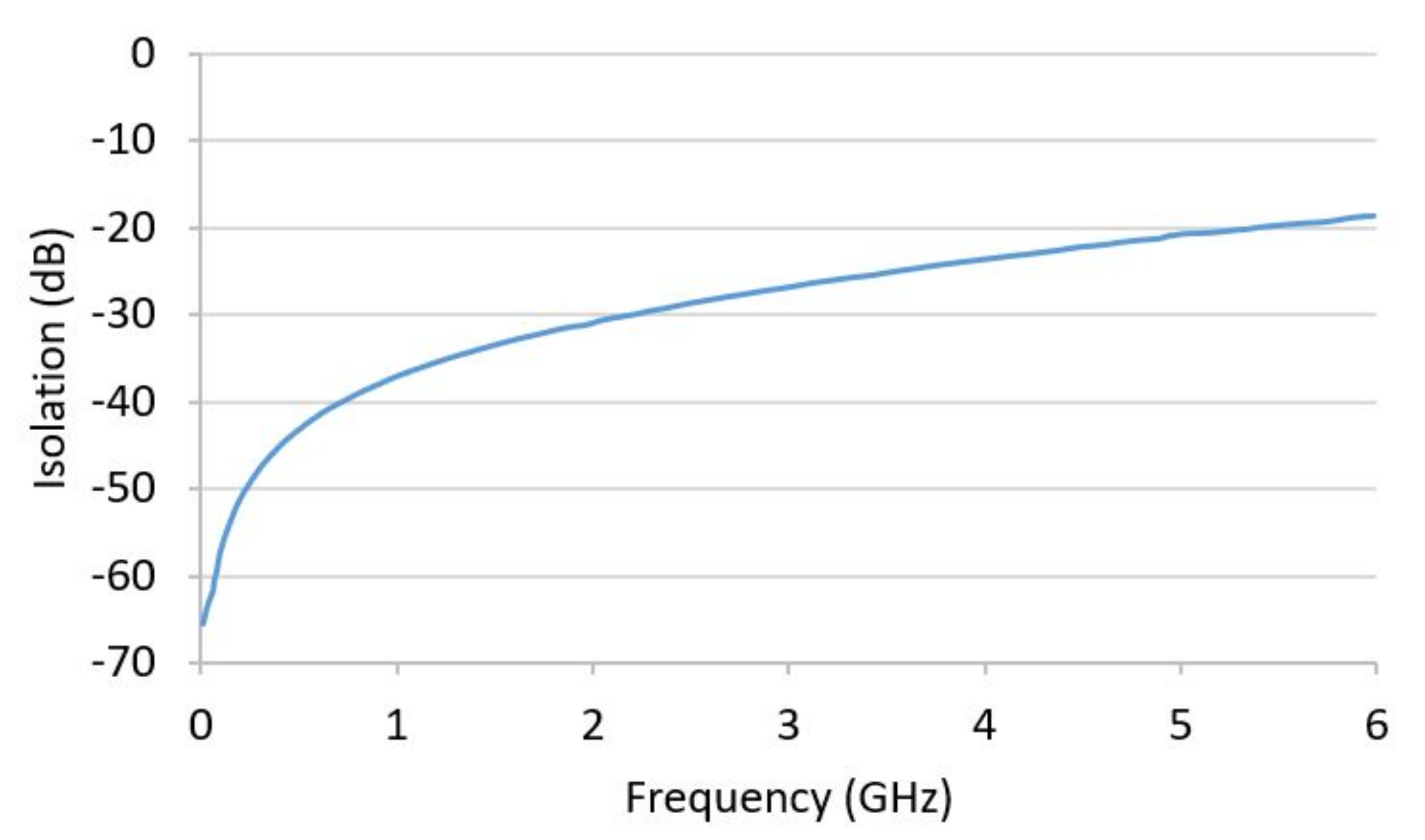

| ISO (@1/2 GHz) | 23/27 | 46.7/22.7 | 32/28 | 38/32 | 39.4/32 | 37/31 |

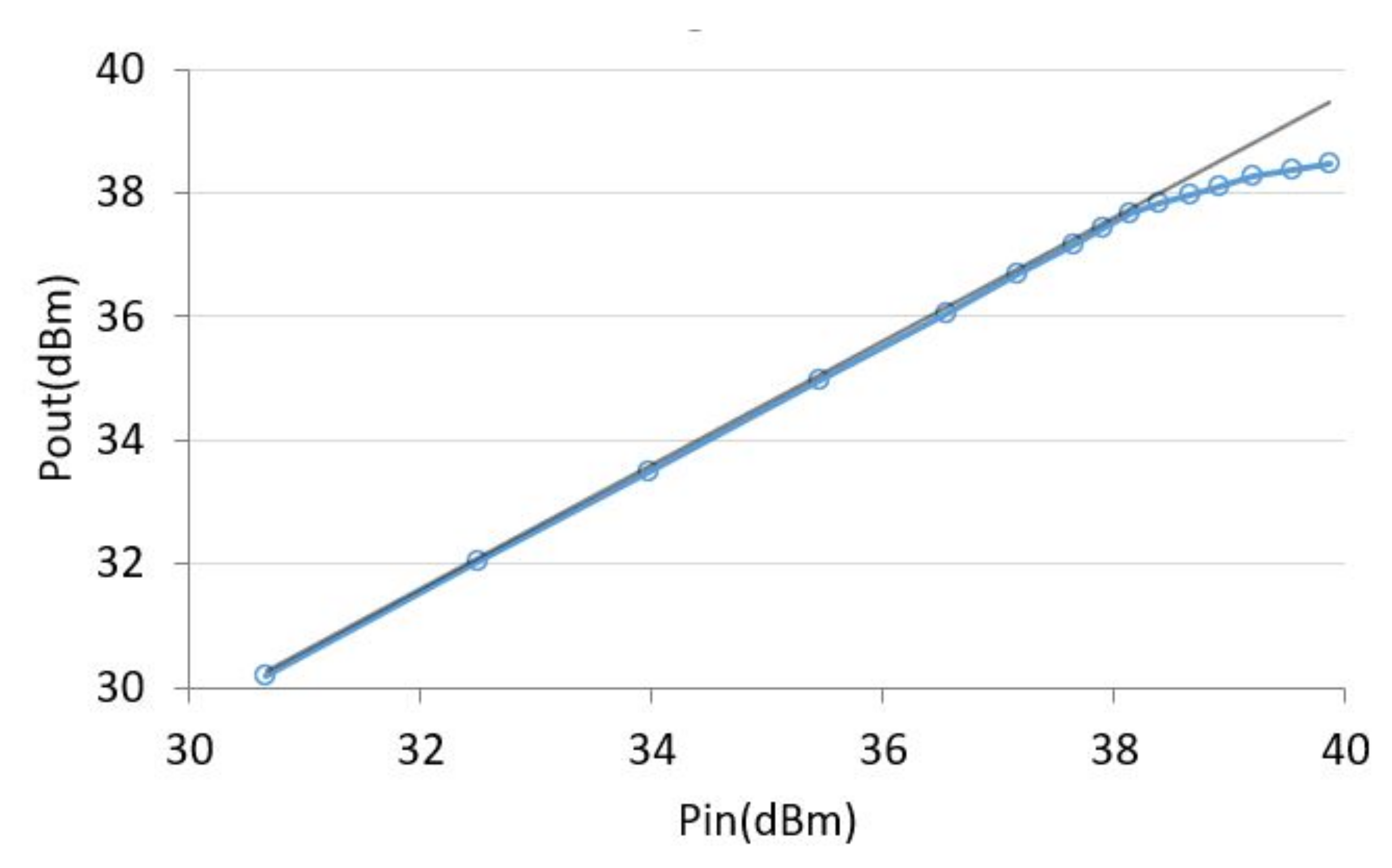

| P1 dB (dBm) | 20.5 | 39.2 | 42.2 | 37.2 | 35 | 39.5 |

| Supply current (μA) | - | 50.4 | - | 80 | <1 | 37 |

| Size (mm) | 0.26 | 1.1 | 0.57 × 0.82 | - | 1.15 × 0.85 | 0.71 × 0.82 |

| Biasing technique | floating-body | negative biasing | negative biasing | negative biasing | dc-lifting | negative biasing |

| Technology | 0.18 μm CMOS | 0.18 μm SOI | 0.18 μm SOI | 0.18 μm SOI | 0.18 μm SOI | 0.18 μm SOI |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2022 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Liang, W.; Gan, Y. A High Performance 0.18 μm RF Switch for Multi-Standard. Electronics 2022, 11, 2046. https://doi.org/10.3390/electronics11132046

Liang W, Gan Y. A High Performance 0.18 μm RF Switch for Multi-Standard. Electronics. 2022; 11(13):2046. https://doi.org/10.3390/electronics11132046

Chicago/Turabian StyleLiang, Weishuang, and Yebing Gan. 2022. "A High Performance 0.18 μm RF Switch for Multi-Standard" Electronics 11, no. 13: 2046. https://doi.org/10.3390/electronics11132046