Recent Progresses and Perspectives of UV Laser Annealing Technologies for Advanced CMOS Devices

Abstract

:1. Introduction

2. FEOL Applications

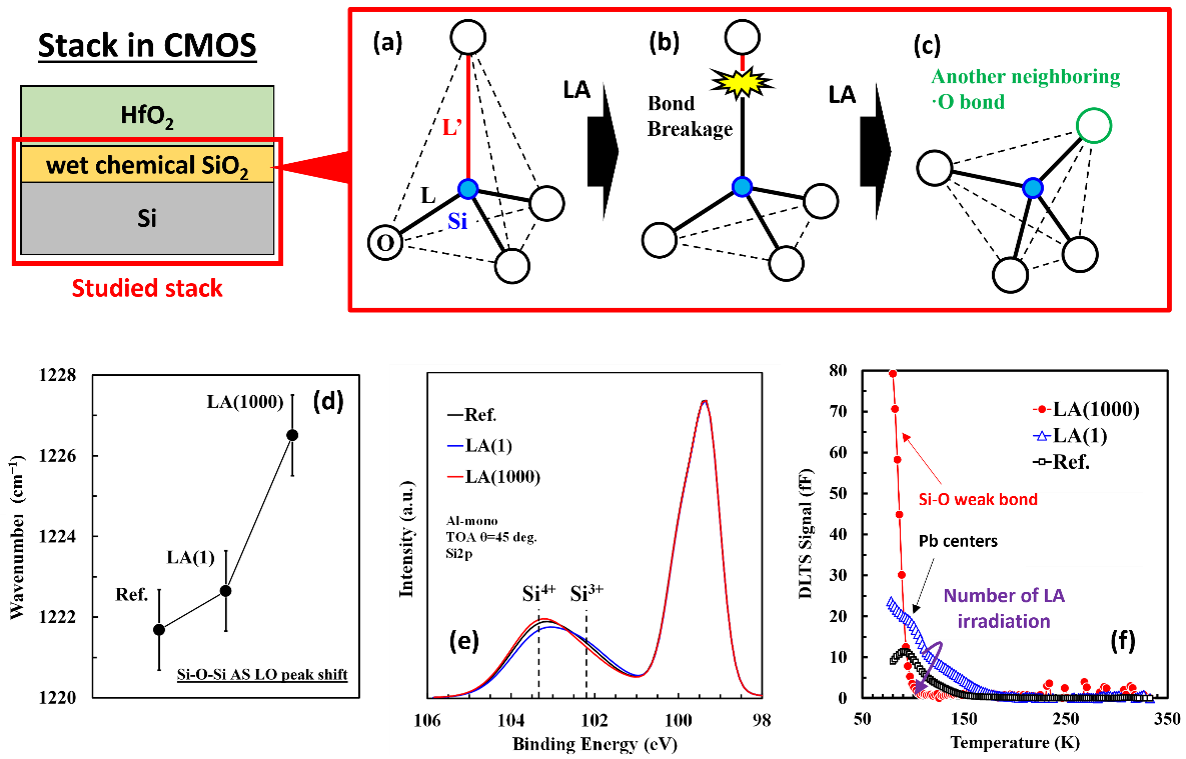

2.1. Reliability Annealing for High-k/SiO2/Si Gate Stacks

2.2. Channel Doping Engineering to Mitigate Short Channel Effects

3. MOL Applications

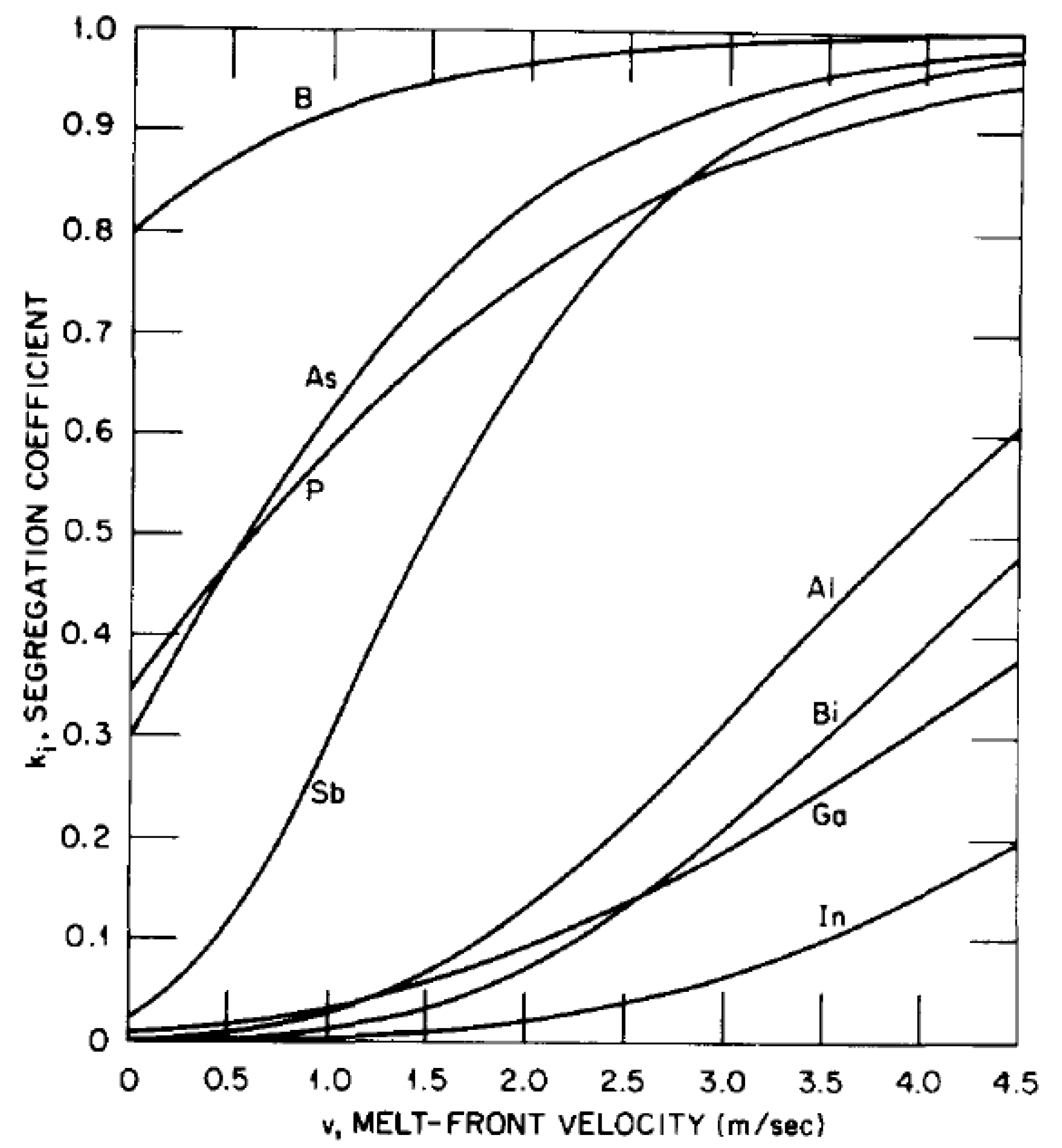

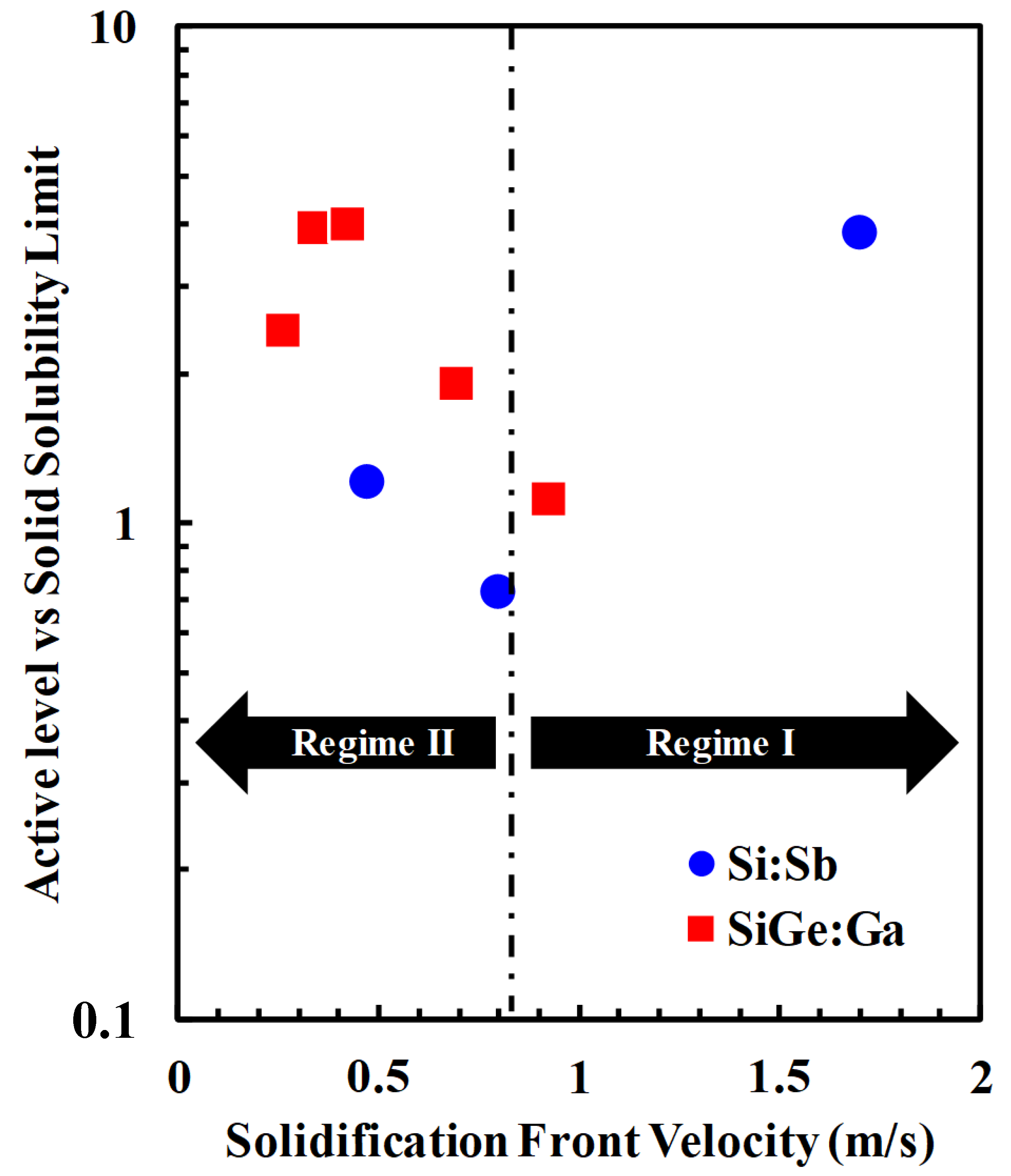

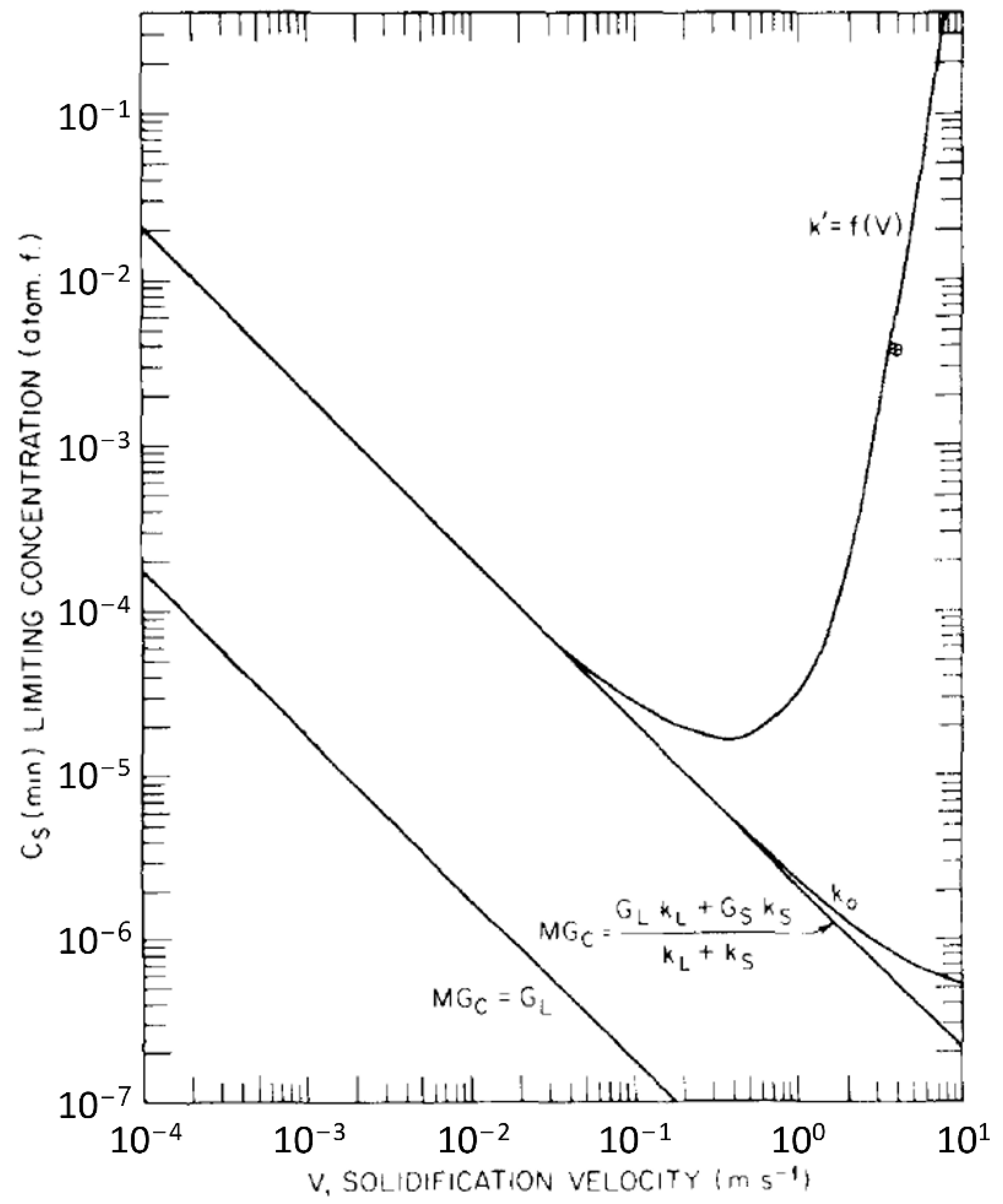

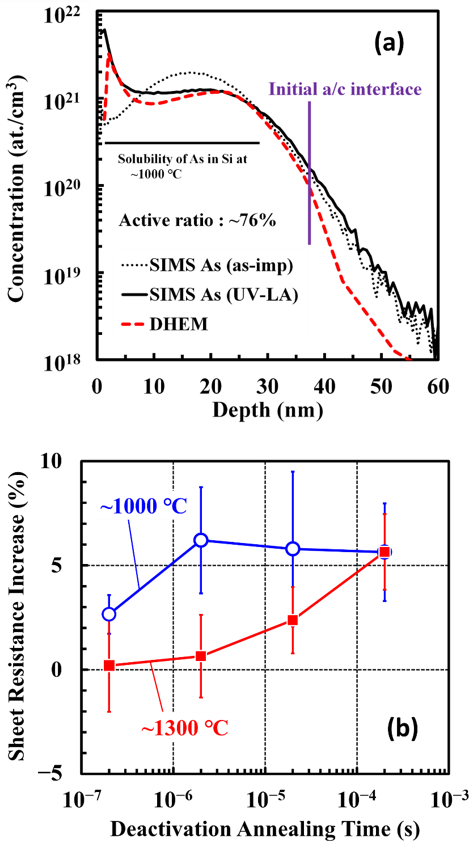

3.1. Dopant Activation by Liquid Phase Epitaxial Regrowth (LPER)

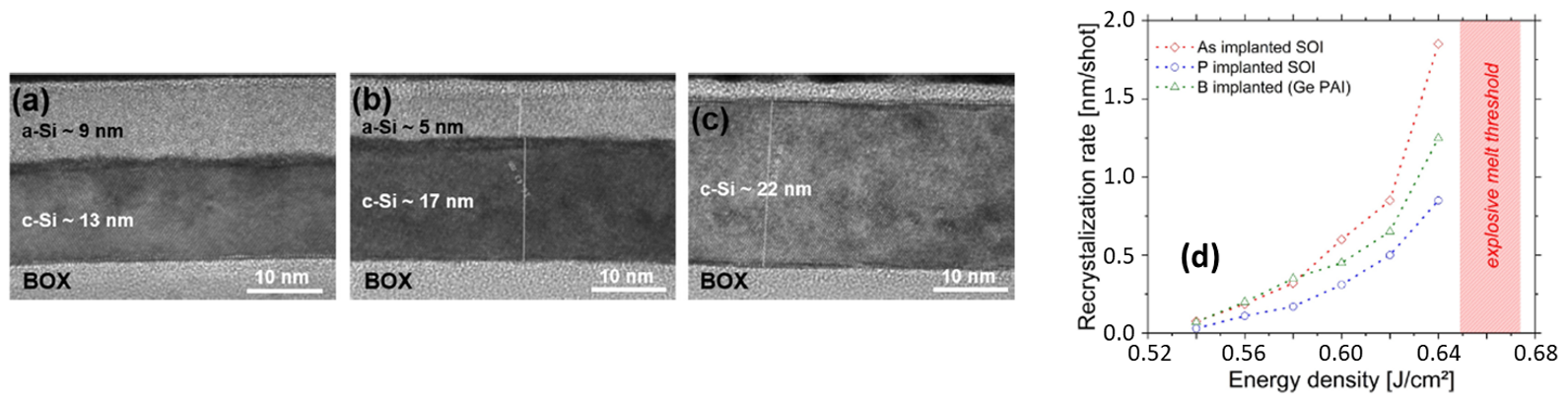

3.2. Dopant Activation by Solid Phase Epitaxial Regrowth (SPER)

4. BEOL Applications

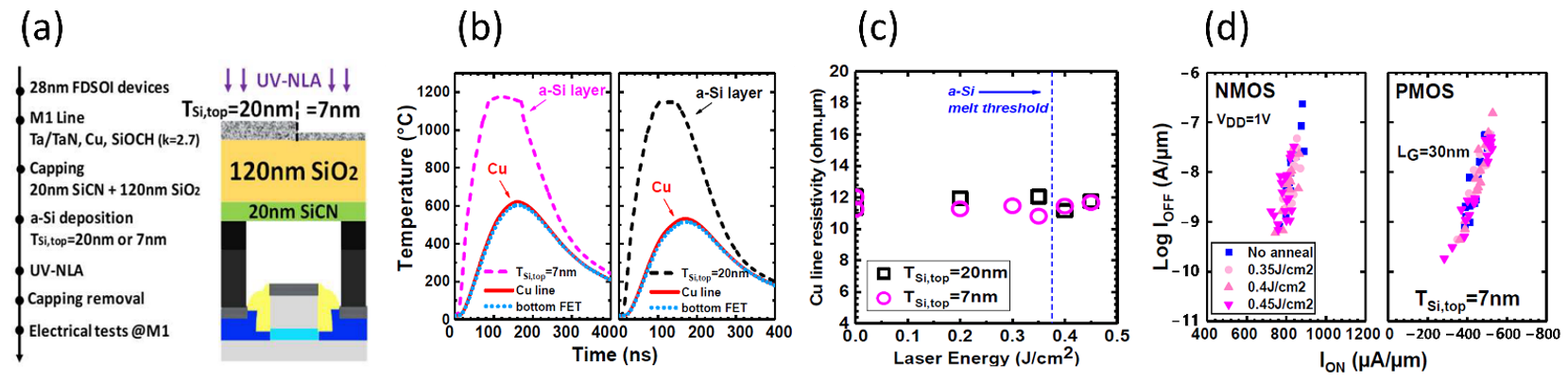

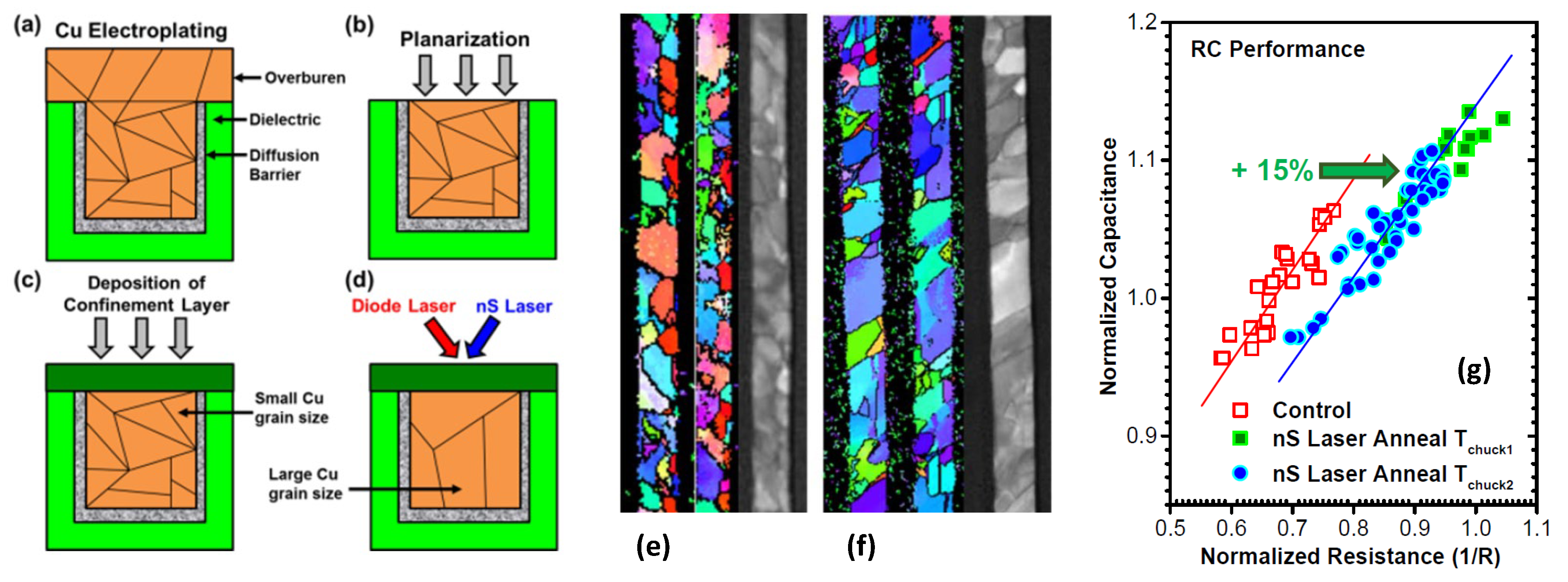

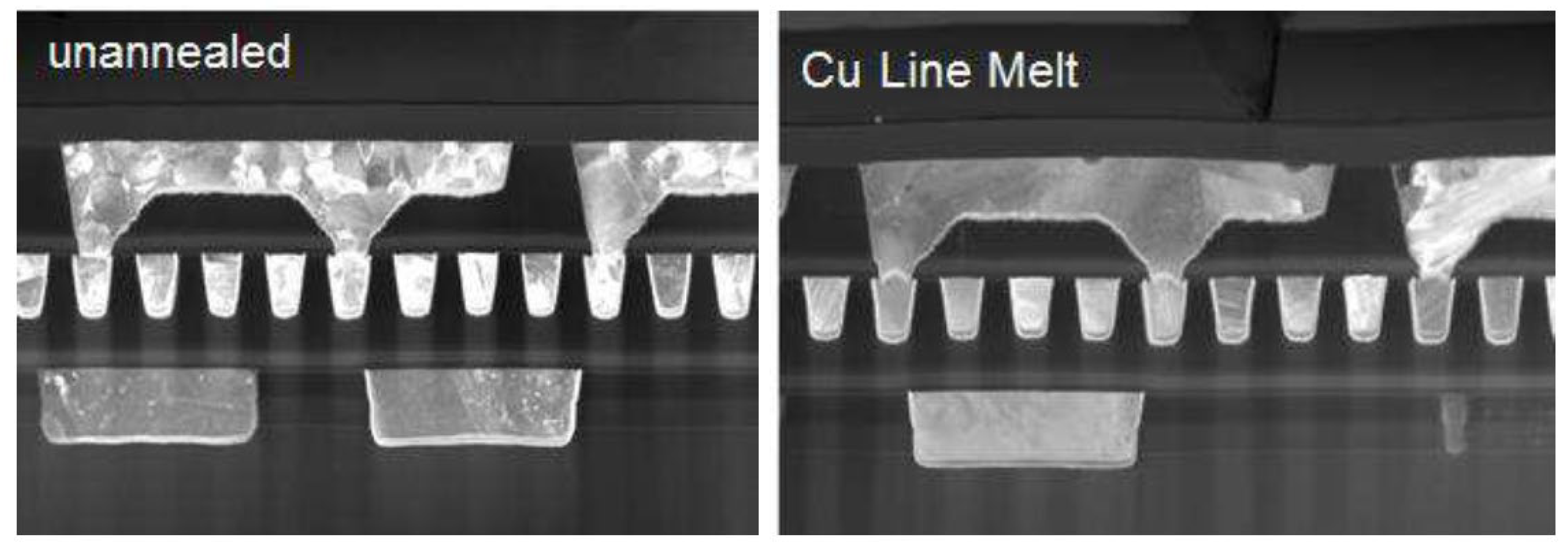

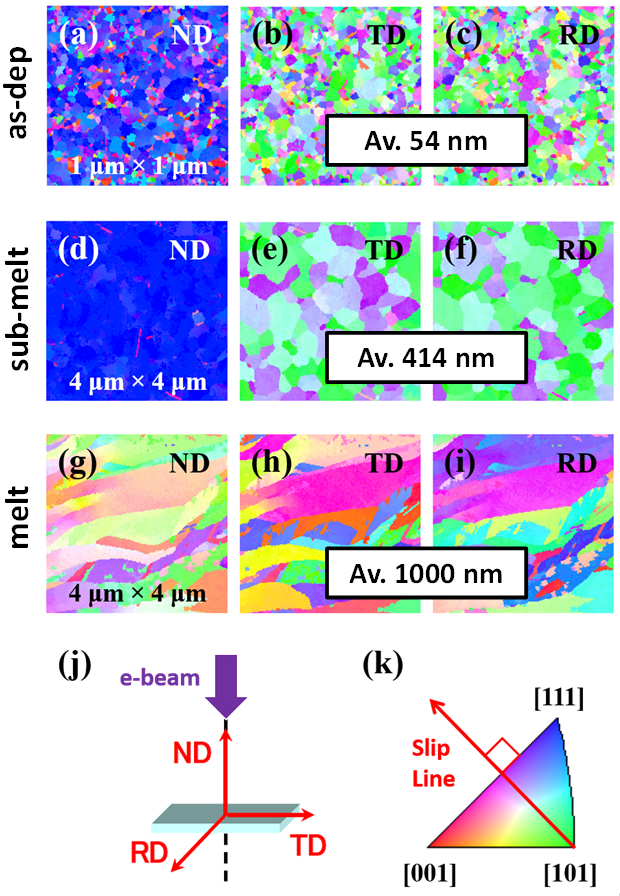

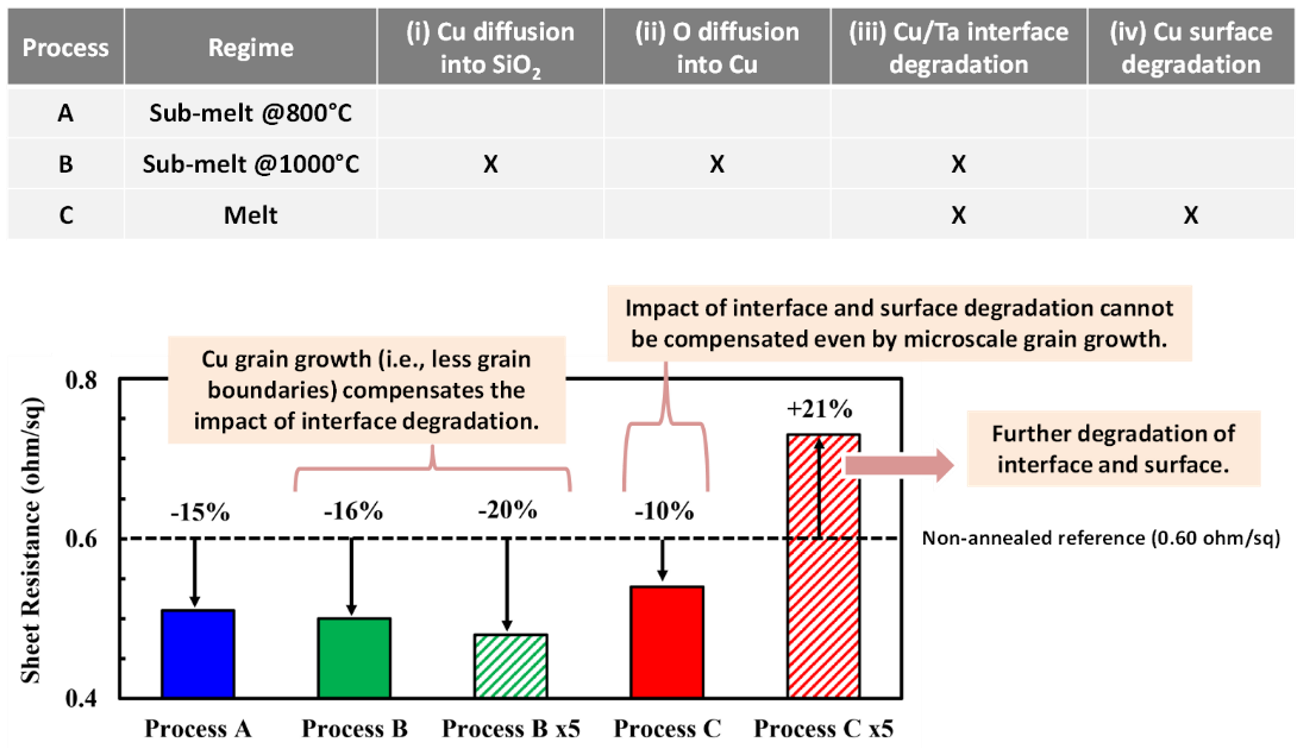

4.1. Cu Interconnect

4.2. Ru Interconnect

5. “More Than Moore” Applications

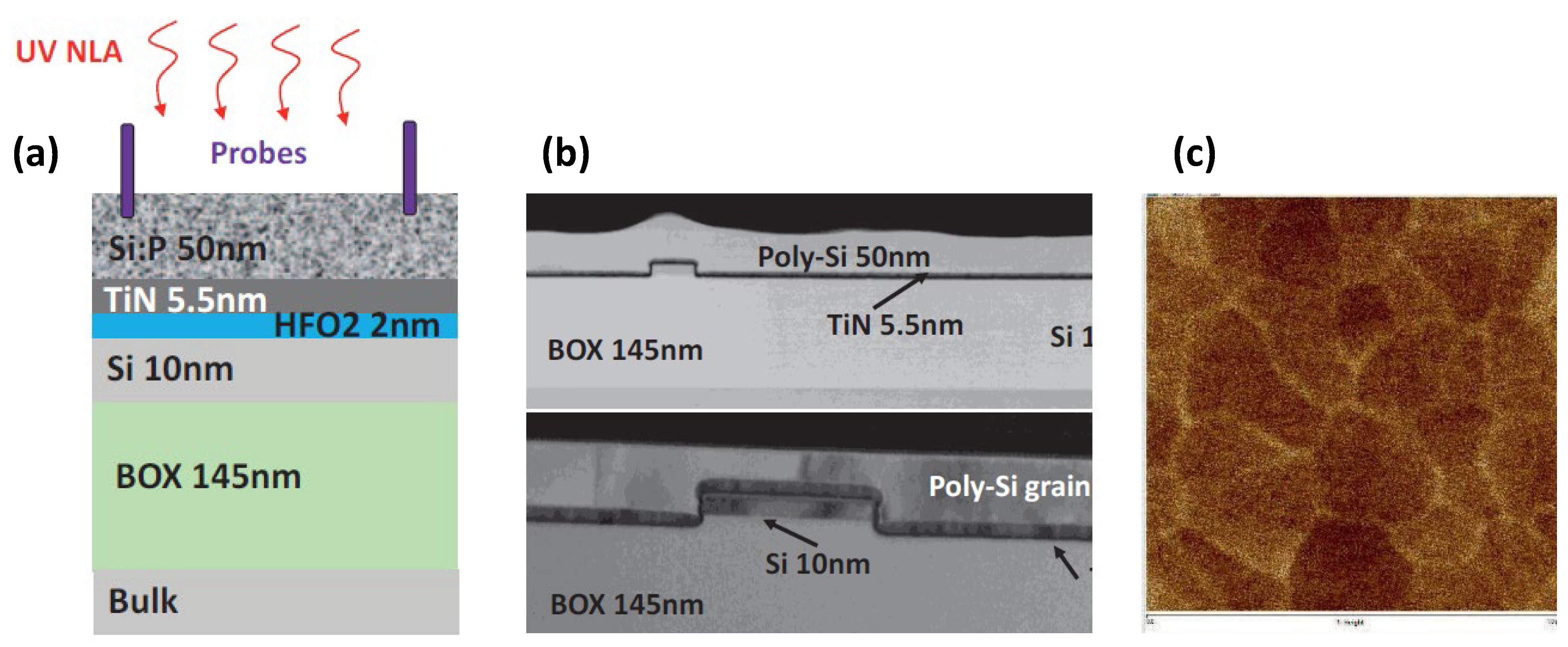

5.1. Large Poly-Si Grain Formation from Amorphous Si Thin Film

5.2. Hf-Based Ferroelectric Layer Formation

6. Conclusions

Author Contributions

Funding

Institutional Review Board Statement

Informed Consent Statement

Data Availability Statement

Acknowledgments

Conflicts of Interest

References

- Brunet, L.; Fenouillet-Beranger, C.; Batude, P.; Beaurepaire, S.; Ponthenier, F.; Rambal, N.; Mazzocchi, V.; Pin, J.-B.; Acosta-Alba, P.; Kerdilès, S.; et al. Breakthroughs in 3D Sequential technology. In Proceedings of the 2018 IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 1–5 December 2018; pp. 7.2.1–7.2.4. [Google Scholar] [CrossRef]

- Hsieh, P.-Y.; Chang, Y.-J.; Chen, P.-J.; Chen, C.-L.; Yang, C.-C.; Huang, P.-T.; Chen, Y.-J.; Shen, C.-M.; Liu, Y.-W.; Huang, C.-C.; et al. Monolithic 3D BEOL FinFET switch arrays using location-controlled-grain technique in voltage regulator with better FOM than 2D regulators. In Proceedings of the 2019 IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 7–11 December 2019; pp. 3.1.1–3.1.4. [Google Scholar] [CrossRef]

- Batude, P.; Brunet, L.; Fenouillet-Beranger, C.; Andrieu, F.; Colinge, J.-P.; Lattard, D.; Vianello, E.; Thuries, S.; Billoint, O.; Vivet, P.; et al. 3D Sequential Integration: Application-driven technological achievements and guidelines. In Proceedings of the 2017 IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 2–6 December 2017; pp. 3.1.1–3.1.4. [Google Scholar] [CrossRef]

- Cavalcante, C.; Fenouillet-Beranger, C.; Batude, P.; Garros, X.; Federspiel, X.; Lacord, J.; Kerdilès, S.; Royet, A.S.; Acosta-Alba, P.; Rozeau, O.; et al. 28nm FDSOI CMOS Technology (FEOL and BEOL) Thermal Stability for 3D Sequential Integration: Yield and Reliability Analysis. In Proceedings of the 2020 IEEE Symposium on VLSI Technology, Honolulu, HI, USA, 16–19 June 2020; pp. 1–2. [Google Scholar] [CrossRef]

- Huet, K.; Mazzamuto, F.; Tabata, T.; Toqué-Tresonne, I.; Mori, Y. Doping of semiconductor devices by Laser Thermal Annealing. Mater. Sci. Semicond. Process. 2017, 62, 92–102. [Google Scholar] [CrossRef]

- Lombardo, S.F.; Fisicaro, G.; Deretzis, I.; La Magna, A.; Curver, B.; Lespinasse, B.; Huet, K. Theoretical study of the laser annealing process in FinFET structures. Appl. Surf. Sci. 2019, 467–468, 666–672. [Google Scholar] [CrossRef]

- Shen, C.-H.; Shieh, J.-M.; Wu, T.-T.; Huang, W.-H.; Yang, C.-C.; Wan, C.-J.; Lin, C.-D.; Wang, H.-H.; Chen, B.-Y.; Huang, G.-W.; et al. Monolithic 3D chip integrated with 500ns NVM, 3ps logic circuits and SRAM. In Proceedings of the 2013 IEEE International Electron Devices Meeting, Washington, DC, USA, 9–11 December 2013; pp. 9.3.1–9.3.4. [Google Scholar] [CrossRef]

- Shulaker, M.M.; Wu, T.F.; Pal, A.; Zhao, L.; Nishi, Y.; Saraswat, K.; Wong, H.-S.P.; Mitra, S. Monolithic 3D integration of logic and memory: Carbon nanotube FETs, resistive RAM, and silicon FETs. In Proceedings of the 2014 IEEE International Electron Devices Meeting, San Francisco, CA, USA, 15–17 December 2014; pp. 27.4.1–27.4.4. [Google Scholar] [CrossRef]

- Wu, T.-T.; Shen, C.-H.; Shieh, J.-M.; Huang, W.-H.; Wang, H.-H.; Hsueh, F.-K.; Chen, H.-C.; Yang, C.-C.; Hsieh, T.-Y.; Chen, B.-Y.; et al. Low-cost and TSV-free monolithic 3D-IC with heterogeneous integration of logic, memory and sensor analogy circuitry for Internet of Things. In Proceedings of the 2015 IEEE International Electron Devices Meeting (IEDM), Washington, DC, USA, 7–9 December 2015; pp. 25.4.1–25.4.4. [Google Scholar] [CrossRef]

- Yang, C.-C.; Hsieh, T.-Y.; Huang, P.-T.; Chen, K.-N.; Wu, W.-C.; Chen, S.-W.; Chang, C.-H.; Shen, C.-H.; Shieh, J.-M.; Hu, C.; et al. Location-controlled-grain Technique for Monolithic 3D BEOL FinFET Circuits. In Proceedings of the 2018 IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 1–5 December 2018; pp. 11.3.1–11.3.4. [Google Scholar] [CrossRef]

- Francois, T.; Grenouillet, L.; Coignus, J.; Blaise, P.; Carabasse, C.; Vaxelaire, N.; Magis, T.; Aussenac, F.; Loup, V.; Pellissier, C.; et al. Demonstration of BEOL-compatible ferroelectric Hf0.5Zr0.5O2 scaled FeRAM co-integrated with 130 nm CMOS for embedded NVM applications. In Proceedings of the 2019 IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 7–11 December 2019; pp. 15.7.1–15.7.4. [Google Scholar] [CrossRef]

- Grenouillet, L.; Francois, T.; Coignus, J.; Kerdilès, S.; Vaxelaire, N.; Carabasse, C.; Mehmood, F.; Chevalliez, S.; Pellissier, C.; Triozon, F.; et al. Nanosecond Laser Anneal (NLA) for Si-Implanted HfO2 Ferroelectric Memories Integrated in Back-End of Line (BEOL). In Proceedings of the 2020 IEEE Symposium on VLSI Technology, Honolulu, HI, USA, 16–19 June 2020; pp. 1–2. [Google Scholar] [CrossRef]

- Srimani, T.; Hills, G.; Bishop, M.; Lau, C.; Kanhaiya, P.; Ho, R.; Amer, A.; Chao, M.; Yu, A.; Wright, A.; et al. Heterogeneous Integration of BEOL Logic and Memory in a Commercial Foundry: Multi-Tier Complementary Carbon Nanotube Logic and Resistive RAM at a 130 nm node. In Proceedings of the 2020 IEEE Symposium on VLSI Technology, Honolulu, HI, USA, 16–19 June 2020; pp. 1–2. [Google Scholar] [CrossRef]

- Morin, P.; Tabata, T.; Rozé, F.; Saib, M.; Thielens, H.; Thuries, L.; Huet, K.; Mazzamuto, F. Impact of the buried oxide thickness in UV laser heated 3D stacks. In Proceedings of the 2021 Solid State Devices and Materials (SSDM), Virtual, 6–9 September 2021; p. A-6-03. [Google Scholar]

- Ragnarsson, L.-Å.; Dekkers, H.; Matagne, P.; Schram, T.; Conard, T.; Horiguchi, N.; Thean, A.V.-Y. Zero-thickness multi work function solutions for N7 bulk FinFETs. In Proceedings of the 2016 IEEE Symposium on VLSI Technology, Honolulu, HI, USA, 14–16 June 2016; pp. 1–2. [Google Scholar] [CrossRef]

- Bury, E.; Kaczer, B.; Arimura, H.; Toledano Luque, M.; Ragnarsson, L.Å.; Roussel, P.; Veloso, A.; Chew, S.A.; Togo, M.; Schram, T.; et al. Reliability in gate first and gate last ultra-thin-EOT gate stacks assessed with CV-eMSM BTI characterization. In Proceedings of the 2013 IEEE International Reliability Physics Symposium (IRPS), Monterey, CA, USA, 14–18 April 2013; pp. GD.3.1–GD.3.5. [Google Scholar] [CrossRef]

- Rzepa, G.; Franco, J.; Subirats, A.; Jech, M.; Chasin, A.; Grill, A.; Waltl, M.; Knobloch, T.; Stampfer, B.; Chiarella, T.; et al. Efficient physical defect model applied to PBTI in high-κ stacks. In Proceedings of the 2017 IEEE International Reliability Physics Symposium (IRPS), Monterey, CA, USA, 2–6 April 2017; pp. XT-11.1–XT-11.6. [Google Scholar] [CrossRef]

- Franco, J.; Wu, Z.; Rzepa, G.; Vandooren, A.; Arimura, H.; Ragnarsson, L.-Å.; Hellings, G.; Brus, S.; Cott, D.; De Heyn, V.; et al. BTI Reliability Improvement Strategies in Low Thermal Budget Gate Stacks for 3D Sequential Integration. In Proceedings of the 2018 IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 1–5 December 2018; pp. 34.2.1–34.2.4. [Google Scholar] [CrossRef]

- Denais, M.; Huard, V.; Parthasarathy, C.; Ribes, G.; Perrier, F.; Revil, N.; Bravaix, A. Interface trap generation and hole trapping under NBTI and PBTI in advanced CMOS technology with a 2-nm gate oxide. IEEE Trans. Device Mater. Reliab. 2004, 4, 715–722. [Google Scholar] [CrossRef]

- Franco, J.; Arimura, H.; de Marneffe, J.-F.; Wu, Z.; Vandooren, A.; Ragnarsson, L.-Å.; Dentoni Litta, E.; Horiguchi, N.; Croes, K.; Linten, D.; et al. Low-temperature atomic and molecular hydrogen anneals for enhanced chemical SiO2 IL quality in low thermal budget RMG stacks. In Proceedings of the 2021 IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 11–16 December 2021; pp. 31.4.1–31.4.4. [Google Scholar] [CrossRef]

- Franco, J.; de Marneffe, J.-F.; Vandooren, A.; Arimura, H.; Ragnarsson, L.-Å.; Claes, D.; Dentoni Litta, E.; Horiguchi, N.; Croes, K.; Linten, D.; et al. Low Temperature Atomic Hydrogen Treatment for Superior NBTI Reliability—Demonstration and Modeling across SiO2 IL Thicknesses from 1.8 to 0.6 nm for I/O and Core Logic. In Proceedings of the 2021 Symposium on VLSI Technology, Kyoto, Japan, 13–19 June 2021; pp. 1–2. [Google Scholar]

- Sometani, M.; Hasunuma, R.; Ogino, M.; Kuribayashi, H.; Sugahara, Y.; Uedono, A.; Yamabe, K. Variation of Chemical Vapor Deposited SiO2 Density Due to Generation and Shrinkage of Open Space During Thermal Annealing. Jpn. J. Appl. Phys. 2012, 51, 021101. [Google Scholar] [CrossRef]

- Tabata, T.; Inoue, K.; Yoshida, Y.; Takahashi, H. Non-equilibrium engineering of chemically grown SiO2/Si by UV nanosecond pulsed laser annealing from the viewpoint of bias temperature instability sources. Appl. Phys. Express 2020, 14, 011003. [Google Scholar] [CrossRef]

- Khanna, V.K. Short-Channel Effects in MOSFETs. In Integrated Nanoelectronics. NanoScience and Technology, 1st ed.; Springer: New Delhi, India, 2016; pp. 73–93. [Google Scholar] [CrossRef]

- Yau, L.D. A simple theory to predict the threshold voltage of short-channel IGFET’s. Solid-State Electron. 1974, 17, 1059–1063. [Google Scholar] [CrossRef]

- Bracht, H. Advanced dopant and self-diffusion studies in silicon. Nucl. Instrum. Methods Phys. Res. Sect. B Beam Interact. Mater. At. 2006, 253, 105–112. [Google Scholar] [CrossRef]

- Kodera, H. Diffusion Coefficients of Impurities in Silicon Melt. Jpn. J. Appl. Phys. 1963, 2, 212–219. [Google Scholar] [CrossRef]

- Huet, K.; Boniface, C.; Fisicaro, G.; Desse, F.; Variam, N.; Erokhin, Y.; La Magna, A.; Privitera, V.; Schuhmacher, M.; Besaucele, H.; et al. Experimental and theoretical analysis of dopant activation in double implanted silicon by pulsed laser thermal annealing. In Proceedings of the 17th International Conference on Advanced Thermal Processing of Semiconductors, Albany, NY, USA, 29 September–2 October 2009; pp. 1–16. [Google Scholar] [CrossRef]

- Venturini, J. Laser Thermal Annealing: Enabling ultra-low thermal budget processes for 3D junctions formation and devices. In Proceedings of the 12th International Workshop on Junction Technology, Shanghai, China, 14–15 May 2012; pp. 57–62. [Google Scholar] [CrossRef]

- Qiu, Y.; Cristiano, F.; Huet, K.; Mazzamuto, F.; Fisicaro, G.; La Magna, A.; Quillec, M.; Cherkashin, N.; Wang, H.; Duguay, S.; et al. Extended Defects Formation in Nanosecond Laser-Annealed Ion Implanted Silicon. Nano Lett. 2014, 14, 1769–1775. [Google Scholar] [CrossRef]

- Lombardo, S.F.; Lombardo, S.F.; Boninelli, S.; Cristiano, F.; Deretzis, I.; Grimaldi, M.G.; Huet, K.; Napolitani, E.; La Magna, A. Phase field model of the nanoscale evolution during the explosive crystallization phenomenon. J. Appl. Phys. 2018, 123, 105105. [Google Scholar] [CrossRef]

- Vandooren, A.; Wu, Z.; Parihar, N.; Franco, J.; Parvais, B.; Matagne, P.; Debruyn, H.; Mannaert, G.; Devriendt, K.; Teugels, L.; et al. 3D Sequential Low Temperature Top Tier Devices using Dopant Activation with Excimer Laser Anneal and Strained Silicon as Performance Boosters. In Proceedings of the 2020 IEEE Symposium on VLSI Technology, Honolulu, HI, USA, 16–19 June 2020; pp. 1–2. [Google Scholar] [CrossRef]

- Ni, C.-N.; Rao, K.V.; Khaja, F.; Sharma, S.; Tang, S.; Chen, J.J.; Hollar, K.E.; Breil, N.; Li, X.; Jin, M.; et al. Ultra-low NMOS contact resistivity using a novel plasma-based DSS implant and laser anneal for post 7 nm nodes. In Proceedings of the 2016 IEEE Symposium on VLSI Technology, Honolulu, HI, USA, 14–16 June 2016; pp. 1–2. [Google Scholar] [CrossRef]

- Van Dal, M.J.H.; Vellianitis, G.; Doornbos, G.; Duriez, B.; Holland, M.C.; Vasen, T.; Afzalian, A.; Chen, E.; Su, S.K.; Chen, T.K.; et al. Ge CMOS gate stack and contact development for Vertically Stacked Lateral Nanowire FETs. In Proceedings of the 2018 IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 1–5 December 2018; pp. 21.1.1–21.1.4. [Google Scholar] [CrossRef]

- Yu, H.; Schaekers, M.; Hikavyy, A.; Rosseel, E.; Peter, A.; Hollar, K.; Khaja, F.A.; Aderhold, W.; Date, L.; Mayur, A.J.; et al. Ultralow-resistivity CMOS contact scheme with pre-contact amorphization plus Ti (germano-)silicidation. In Proceedings of the 2016 IEEE Symposium on VLSI Technology, Honolulu, HI, USA, 14–16 June 2016; pp. 1–2. [Google Scholar] [CrossRef]

- Wang, L.-L.; Yu, H.; Schaekers, M.; Everaert, J.-L.; Franquet, A.; Douhard, B.; Date, L.; del Agua Borniquel, J.; Hollar, K.; Khaja, F.A.; et al. Comprehensive study of Ga activation in Si, SiGe and Ge with 5 × 10−10 Ω·cm2 contact resistivity achieved on Ga doped Ge using nanosecond laser activation. In Proceedings of the 2017 IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 2–6 December 2017; pp. 22.4.1–22.4.4. [Google Scholar] [CrossRef]

- Niimi, H.; Liu, Z.; Gluschenkov, O.; Mochizuki, S.; Fronheiser, J.; Li, J.; Demarest, J.; Zhang, C.; Liu, B.; Yang, J.; et al. Sub-10-9 Ω-cm2 n-Type Contact Resistivity for FinFET Technology. IEEE Electron Device Lett. 2016, 37, 1371–1374. [Google Scholar] [CrossRef]

- Schroder, D.K. Contact Resistance and Schottky Barriers. In Semiconductor Material and Device Characterization, 3rd ed.; John Wiley & Sons, Inc.: Hoboken, NJ, USA, 2006; pp. 127–184. [Google Scholar] [CrossRef]

- Everaert, J.-L.; Schaekers, M.; Yu, H.; Wang, L.-L.; Hikavyy, A.; Date, L.; del Agua Borniquel, J.; Hollar, K.; Khaja, F.A.; Aderhold, W.; et al. Sub-10−9 Ω·cm2 contact resistivity on p-SiGe achieved by Ga doping and nanosecond laser activation. In Proceedings of the 2017 Symposium on VLSI Technology, Kyoto, Japan, 5–8 June 2017; pp. T214–T215. [Google Scholar] [CrossRef]

- Tabata, T.; Aubin, J.; Huet, K.; Mazzamuto, F. Segregation and activation of Ga in high Ge content SiGe by UV melt laser anneal. J. Appl. Phys. 2019, 125, 215702. [Google Scholar] [CrossRef]

- Tabata, T.; Huet, K.; Mazzamuto, F.; La Magna, A. Surface segregated Ga, In, and Al activation in high Ge content SiGe during UV melt laser induced non-equilibrium solidification. Jpn. J. Appl. Phys. 2020, 58, 120911. [Google Scholar] [CrossRef]

- Tabata, T.; Raynal, P.-E.; Huet, K.; Everaert, J.-L. Segregation and activation of Sb implanted in Si by UV nanosecond-laser-anneal-induced non-equilibrium solidification. J. Appl. Phys. 2020, 127, 135701. [Google Scholar] [CrossRef]

- Tabata, T.; Aubin, J.; Mazzamuto, F. Multilayered highly-active dopant distribution by UV nanosecond melt laser annealing in Ga and B co-implanted high Ge content SiGe:B epilayers. Jpn. J. Appl. Phys. 2020, 59, 050903. [Google Scholar] [CrossRef]

- Tabata, T.; Huet, K.; Rozé, F.; Mazzamuto, F.; Sermage, B.; Kopalidis, P.; Roh, D. Dopant Redistribution and Activation in Ga Ion-Implanted High Ge Content SiGe by Explosive Crystallization during UV Nanosecond Pulsed Laser Annealing. ECS J. Solid State Sci. Technol. 2021, 10, 023005. [Google Scholar] [CrossRef]

- Albenze, E.J.; Thompson, M.O.; Clancy, P. Atomistic computer simulation of explosive crystallization in pure silicon and germanium. Phys. Rev. B 2004, 70, 094110. [Google Scholar] [CrossRef]

- Acosta Alba, P.; Aubin, J.; Perrot, S.; Mazzamuto, F.; Grenier, A.; Kerdilès, S. Solid phase recrystallization induced by multi-pulse nanosecond laser annealing. Appl. Surf. Sci. Adv. 2021, 3, 100053. [Google Scholar] [CrossRef]

- Tabata, T.; Rozé, F.; Thuries, L.; Halty, S.; Raynal, P.-E.; Huet, K.; Mazzamuto, F.; Joshi, A.; Basol, B.M.; Acosta Alba, P. Microsecond non-melt UV laser annealing for future 3D-stacked CMOS. Appl. Phys. Express 2022, 15, 061002. [Google Scholar] [CrossRef]

- Wood, R.F. Model for nonequilibrium segregation during pulsed laser annealing. Appl. Phys. Lett. 1980, 37, 302. [Google Scholar] [CrossRef]

- Galenko, P. Solute trapping and diffusionless solidification in a binary system. Phys. Rev. E 2007, 76, 031606. [Google Scholar] [CrossRef]

- Poulton, J.T.L.; Bowler, D.R. An Ab Initio Study of Aluminium self-compensation in Bulk Silicon. arXiv 2019, arXiv:1907.03636. [Google Scholar] [CrossRef]

- Narayan, J. Interface instability and cell formation in ion-implanted and laser-annealed silicon. J. Appl. Phys. 1981, 52, 1289. [Google Scholar] [CrossRef]

- Tabata, T.; Curvers, B.; Huet, K.; Chew, S.A.; Everaert, J.-L.; Horiguchi, N. 3D Simulation for Melt Laser Anneal Integration in FinFET’s Contact. IEEE J. Electron Devices Soc. 2020, 8, 1323–1327. [Google Scholar] [CrossRef]

- Trumbore, F.A. Solid solubilities of impurity elements in germanium and silicon. Bell Syst. Tech. J. 1960, 39, 205–233. [Google Scholar] [CrossRef]

- Vandooren, A.; Tabata, T.; Eyben, P.; Roseel, E.; Hikavyy, A.; Huet, K.; Mazzamuto, F.; Dentoni Litta, E.; Horiguchi, N. Potential benefits of S/D HDD activation by melt laser annealing in 3D-inte-grated top-tier FDSOI FETs. In Proceedings of the 2021 Solid State Devices and Materials (SSDM), Virtual, 6–9 September 2021; p. A-6-02. [Google Scholar]

- Dagault, L.; Acosta-Alba, P.; Kerdilès, S.; Barnes, J.P.; Hartmann, J.M.; Gergaud, P.; Nguyen, T.T.; Grenier, A.; Papon, A.M.; Bernier, N.; et al. Impact of UV Nanosecond Laser Annealing on Composition and Strain of Undoped Si0.8Ge0.2 Epitaxial Layers. ECS J. Solid State Sci. Technol. 2019, 8, P202. [Google Scholar] [CrossRef]

- Dagault, L.; Kerdilès, S.; Acosta Alba, P.; Hartmann, J.-M.; Barnes, J.-P.; Gergaud, P.; Scheid, E.; Cristiano, F. Investigation of recrystallization and stress relaxation in nanosecond laser annealed Si1−xGex/Si epilayers. Appl. Surf. Sci. 2020, 527, 146752. [Google Scholar] [CrossRef]

- Tabata, T.; Roze, F.; Alba, P.A.; Halty, S.; Raynal, P.-E.; Karmous, I.; Kerdiles, S.; Mazzamuto, F. Solid Phase Recrystallization in Arsenic Ion-Implanted Silicon-On-Insulator by Microsecond UV Laser Annealing. arXiv 2022, arXiv:2204.12167. [Google Scholar] [CrossRef]

- Hopstaken, M.J.P.; Tamminga, Y.; Verheijen, M.A.; Duffy, R.; Venezia, V.C.; Heringa, A. Effects of crystalline regrowth on dopant profiles in preamorphized silicon. Appl. Surf. Sci. 2004, 231–232, 688–692. [Google Scholar] [CrossRef]

- Joshi, A.; Basol, B.M. Sub-nm Near-Surface Activation Profiling for Highly Doped Si and Ge Using Differential Hall Effect Metrology (DHEM). ECS Trans. 2020, 98, 405. [Google Scholar] [CrossRef]

- Lietoila, A.; Gibbons, J.F.; Sigmon, T.W. The solid solubility and thermal behavior of metastable concentrations of As in Si. Appl. Phys. Lett. 1980, 36, 765. [Google Scholar] [CrossRef]

- Nogami, T.; Zhang, X.; Kelly, J.; Briggs, B.; You, H.; Patlolla, R.; Huang, H.; McLaughlin, P.; Lee, J.; Shobha, H.; et al. Comparison of key fine-line BEOL metallization schemes for beyond 7 nm node. In Proceedings of the 2017 Symposium on VLSI Technology, Kyoto, Japan, 5–8 June 2017; pp. T148–T149. [Google Scholar] [CrossRef]

- Nogami, T. Overview of interconnect technology for 7nm node and beyond-New materials and technologies to extend Cu and to enable alternative conductors. In Proceedings of the 2019 Electron Devices Technology and Manufacturing Conference (EDTM), Singapore, 12–15 March 2019; pp. 38–40. [Google Scholar] [CrossRef]

- Nogami, T.; Gluschenkov, O.; Sulehria, Y.; Nguyen, S.; Huang, H.; Lanzillo, N.A.; DeSilva, A.; Mignot, Y.; Church, J.; Lee, J.; et al. Advanced BEOL Interconnects. In Proceedings of the 2020 IEEE International Interconnect Technology Conference (IITC), San Jose, CA, USA, 5–8 October 2020; pp. 1–3. [Google Scholar] [CrossRef]

- Simon, A.; van der Straten, O.; Lanzillo, N.A.; Yang, C.-C.; Nogami, T.; Edelstein, D.C. Role of high aspect-ratio thin-film metal deposition in Cu back-end-of-line technology. J. Vac. Sci. Technol. A 2020, 38, 053402. [Google Scholar] [CrossRef]

- Murdoch, G.; Tokei, Z.; Paolillo, S.; Varela Pedreira, O.; Vanstreels, K.; Wilson, C.J. Semidamascene Interconnects for 2nm node and Beyond. In Proceedings of the 2020 IEEE International Interconnect Technology Conference (IITC), San Jose, CA, USA, 5–8 October 2020; pp. 4–6. [Google Scholar] [CrossRef]

- Hu, C.-K.; Kelly, J.; Chen, J.H.-C.; Huang, H.; Ostrovski, Y.; Patlolla, R.; Peethala, B.; Adusumilli, P.; Spooner, T.; Gignac, L.M.; et al. Electromigration and resistivity in on-chip Cu, Co and Ru damascene nanowires. In Proceedings of the 2017 IEEE International Interconnect Technology Conference (IITC), Hsinchu, Taiwan, 16–18 May 2017; pp. 1–3. [Google Scholar] [CrossRef]

- Bhosale, P.; Parikh, S.; Lanzillo, N.; Tao, R.; Nogami, T.; Gage, M.; Shaviv, R.; Huang, H.; Simon, A.; Stolfi, M.; et al. Composite Interconnects for High-Performance Computing beyond the 7 nm Node. In Proceedings of the 2020 IEEE Symposium on VLSI Technology, Honolulu, HI, USA, 16–19 June 2020; pp. 1–2. [Google Scholar] [CrossRef]

- Nogami, T.; Briggs, B.D.; Korkmaz, S.; Chae, M.; Penny, C.; Li, J.; Wang, W.; McLaughlin, P.S.; Kane, T.; Parks, C.; et al. Through-Cobalt Self Forming Barrier (tCoSFB) for Cu/ULK BEOL: A novel concept for advanced technology nodes. In Proceedings of the 2015 IEEE International Electron Devices Meeting (IEDM), Washington, DC, USA, 7–9 December 2015; pp. 8.1.1–8.1.4. [Google Scholar] [CrossRef]

- Lanzillo, N.A.; Yang, C.-C.; Motoyama, K.; Huang, H.; Cheng, K.; Maniscalco, J.; Van Der Straten, O.; Penny, C.; Standaert, T.; Choi, K. Exploring the Limits of Cobalt Liner Thickness in Advanced Copper Interconnects. IEEE Electron Device Lett. 2019, 40, 1804–1807. [Google Scholar] [CrossRef]

- Ezz-Eldin, R.; El-Moursy, M.A.; Hamed, H.F.A. Interconnection. In Analysis and Design of Networks-on-Chip Under High Process Variation, 1st ed.; Springer: Berlin/Heidelberg, Germany, 2015; pp. 45–56. [Google Scholar] [CrossRef]

- Yang, C.-C.; Witt, C.; Wang, P.-C.; Edelstein, D.; Rosenberg, R. Stress control during thermal annealing of copper interconnects. Appl. Phys. Lett. 2011, 98, 051911. [Google Scholar] [CrossRef]

- Yang, C.-C.; Spooner, T.; McLaughlin, P.; Hu, C.K.; Huang, H.; Mignot, Y.; Ali, M.; Lian, G.; Quon, R.; Standaert, T.; et al. Microstructure modulation for resistance reduction in copper interconnects. In Proceedings of the 2017 IEEE International Interconnect Technology Conference (IITC), Hsinchu, Taiwan, 16–18 May 2017; pp. 1–3. [Google Scholar] [CrossRef]

- Dutta, S.; Moors, K.; Vandemaele, M.; Adelmann, C. Finite Size Effects in Highly Scaled Ruthenium Interconnects. IEEE Electron Device Lett. 2018, 39, 268–271. [Google Scholar] [CrossRef]

- Sil, D.; Sulehria, Y.; Gluschenkov, O.; Nogami, T.; Cornell, R.; Simon, A.; Li, J.; Demarest, J.; Haran, B.; Lavoie, C.; et al. Impact of Nanosecond Laser Anneal on PVD Ru Films. In Proceedings of the 2021 IEEE International Interconnect Technology Conference (IITC), Kyoto, Japan, 6–9 July 2021; pp. 1–3. [Google Scholar] [CrossRef]

- Lee, R.T.P.; Petrov, N.; Kassim, J.; Gribelyuk, M.; Yang, J.; Cao, L.; Yeap, K.B.; Shen, T.; Zainuddin, A.N.; Chandrashekar, A.; et al. Nanosecond Laser Anneal for BEOL Performance Boost in Advanced FinFETs. In Proceedings of the 2018 IEEE Symposium on VLSI Technology, Honolulu, HI, USA, 18–22 June 2018; pp. 61–62. [Google Scholar] [CrossRef]

- Gluschenkov, O.; Jagannathan, H. Laser Annealing in CMOS Manufacturing. ECS Trans. 2018, 85, 11. [Google Scholar] [CrossRef]

- Sun, T.; Yao, B.; Warren, A.P.; Barmak, K.; Toney, M.F.; Peale, R.E.; Coffey, K.R. Surface and grain-boundary scattering in nanometric Cu films. Phys. Rev. B 2010, 81, 155454. [Google Scholar] [CrossRef]

- Chawla, J.S.; Gstrein, F.; O’Brien, K.P.; Clarke, J.S.; Gall, D. Electron scattering at surfaces and grain boundaries in Cu thin films and wires. Phys. Rev. B 2011, 84, 235423. [Google Scholar] [CrossRef]

- Tabata, T.; Raynal, P.-E.; Rozé, F.; Halty, S.; Thuries, L.; Cristiano, F.; Scheid, E.; Mazzamuto, F. Copper Large-Scale Grain Growth by UV Nanosecond Pulsed Laser Annealing. In Proceedings of the 2021 IEEE International Interconnect Technology Conference (IITC), Kyoto, Japan, 6–9 July 2021; pp. 1–3. [Google Scholar] [CrossRef]

- Demoulin, R.; Daubriac, R.; Thuries, L.; Scheid, E.; Rozé, F.; Cristiano, F.; Tabata, T.; Mazzamuto, F. Failure Mode Analysis in Microsecond UV Laser Annealing of Cu Thin Films. In Proceedings of the 2022 IEEE International Interconnect Technology Conference (IITC), San Jose, CA, USA, 27–30 June 2022; p. 5.5. [Google Scholar]

- Croes, K.; Adelmann, C.; Wilson, C.J.; Zahedmanesh, H.; Varela Pedreira, O.; Wu, C.; Leśniewska, A.; Oprins, H.; Beyne, S.; Ciofi, I.; et al. Interconnect metals beyond copper: Reliability challenges and opportunities. In Proceedings of the 2018 IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 1–5 December 2018; pp. 5.3.1–5.3.4. [Google Scholar] [CrossRef]

- Motoyama, K.; van der Straten, O.; Maniscalco, J.; Huang, H.; Kim, Y.B.; Choi, J.K.; Lee, J.H.; Hu, C.-K.; McLaughlin, P.; Standaert, T.; et al. Ru Liner Scaling with ALD TaN Barrier Process for Low Resistance 7 nm Cu Interconnects and Beyond. In Proceedings of the 2018 IEEE International Interconnect Technology Conference (IITC), Santa Clara, CA, USA, 4–7 June 2018; pp. 40–42. [Google Scholar] [CrossRef]

- Jourdan, N.; Rozé, F.; Tabata, T.; Lariviere, S.; Contino, A.; Mazzamuto, F.; Zsolt, T. UV nanosecond laser annealing for Ru interconnects. In Proceedings of the 2020 IEEE International Interconnect Technology Conference (IITC), San Jose, CA, USA, 5–8 October 2020; pp. 163–165. [Google Scholar] [CrossRef]

- Wan, D.; Paolillo, S.; Rassoul, N.; Kutrzeba Kotowska, B.; Blanco, V.; Adelmann, C.; Lazzarino, F.; Ercken, M.; Murdoch, G.; Bömmels, J.; et al. Subtractive Etch of Ruthenium for Sub-5nm Interconnect. In Proceedings of the 2018 IEEE International Interconnect Technology Conference (IITC), Santa Clara, CA, USA, 4–7 June 2018; pp. 10–12. [Google Scholar] [CrossRef]

- Na, M.H.; Jang, D.; Baert, R.; Sarkar, S.; Patli, S.; Zografos, O.; Chehab, B.; Spessot, A.; Sisto, G.; Schuddinck, P.; et al. Disruptive Technology Elements, and Rapid and Accurate Block-Level Performance Evaluation for 3nm and Beyond. In Proceedings of the 5th IEEE Electron Devices Technology & Manufacturing Conference (EDTM), Chengdu, China, 8–11 April 2021; pp. 1–3. [Google Scholar] [CrossRef]

- Nogami, T.; Gluschenkov, O.; Sulehria, Y.; Nguyen, S.; Peethala, B.; Huang, H.; Shobha, H.; Lanzillo, N.; Patlolla, R.; Sil, D.; et al. Advanced BEOL Materials, Processes, and Integration to Reduce Line Resistance of Damascene Cu, Co, and Subtractive Ru Interconnects. In Proceedings of the 2022 Symposium on VLSI Technology, Honolulu, HI, USA, 13–17 June 2022; p. TFS2-1. [Google Scholar]

- Shimizu, T.; Ishihara, S. Effect of SiO2 Surface Treatment on the Solid-Phase Crystallization of Amorphous Silicon Films. J. Electrochem. Soc. 1995, 142, 298. [Google Scholar] [CrossRef]

- Ryu, M.-K.; Hwang, S.-M.; Kim, T.-H.; Kim, K.-B. The effect of surface nucleation on the evolution of crystalline microstructure during solid phase crystallization of amorphous Si films on SiO2. Appl. Phys. Lett. 1997, 71, 3063. [Google Scholar] [CrossRef]

- Lee, Y.H.D.; Lipson, M. Back-End Deposited Silicon Photonics for Monolithic Integration on CMOS. IEEE J. Sel. Top. Quantum Electron. 2013, 19, 8200207. [Google Scholar] [CrossRef]

- He, M.; Metselaar, W.; Beenakker, K. ⟨100⟩-textured self-assembled square-shaped polycrystalline silicon grains by multiple shot excimer laser crystallization. J. Appl. Phys. 2006, 100, 083103. [Google Scholar] [CrossRef]

- Eustathopoulos, N.; Drevet, B. Surface tension of liquid silicon: High or low value? J. Cryst. Growth 2013, 371, 77–83. [Google Scholar] [CrossRef]

- Choi, D.; Shin, J. Study of phosphorus-doped Si annealed by a multi-wavelength laser. Results Phys. 2022, 38, 105632. [Google Scholar] [CrossRef]

- Huang, R.; Im, S.H. Dynamics of wrinkle growth and coarsening in stressed thin films. Phys. Rev. E 2006, 74, 026214. [Google Scholar] [CrossRef]

- Karmous, I.; Rozé, F.; Raynal, P.-E.; Huet, K.; Acosta-Alba, P.; Tabata, T.; Kerdilès, S. Wrinkles Emerging in SiO2/Si Stack during UV Nanosecond Laser Anneal. ECS Trans. 2021, 102, 125–137. [Google Scholar] [CrossRef]

- Böscke, T.S.; Müller, J.; Bräuhaus, D.; Schröder, U.; Böttger, U. Ferroelectricity in hafnium oxide: CMOS compatible ferroelectric field effect transistors. In Proceedings of the 2011 International Electron Devices Meeting, Washington, DC, USA, 5–7 December 2011; pp. 24.5.1–24.5.4. [Google Scholar] [CrossRef]

- Müller, J.; Schröder, U.; Böscke, T.S.; Müller, I.; Böttger, U.; Wilde, L.; Sundqvist, J.; Lemberger, M.; Kücher, P.; Mikolajick, T.; et al. Ferroelectricity in yttrium-doped hafnium oxide. J. Appl. Phys. 2011, 110, 114113. [Google Scholar] [CrossRef]

- Huan, T.D.; Sharma, V.; Rossetti, G.A.; Ramprasad, R. Pathways towards ferroelectricity in hafnia. Phys. Rev. B 2014, 90, 064111. [Google Scholar] [CrossRef]

- Park, M.H.; Schenk, T.; Fancher, C.M.; Grimley, E.D.; Zhou, C.; Richter, C.; LeBeau, J.M.; Jones, J.L.; Mikolajick, T.; Schroeder, U. A comprehensive study on the structural evolution of HfO2 thin films doped with various dopants. J. Mater. Chem. C 2017, 5, 4677–4690. [Google Scholar] [CrossRef]

- Nakajima, Y.; Kita, K.; Nishimura, T.; Nagashio, K.; Toriumi, A. Phase transformation kinetics of HfO2 polymorphs in ultra-thin region. In Proceedings of the 2011 Symposium on VLSI Technology, Kyoto, Japan, 14–16 June 2011; pp. 84–85. [Google Scholar]

- Mori, Y.; Nishimura, T.; Yajima, T.; Migita, S.; Toriumi, A. Impacts of doped element on ferroelectric phase stabilization in HfO2 through non-equilibrium PDA. In Proceedings of the 2018 Solid State Devices and Materials (SSDM), Tokyo, Japan, 9–13 September 2018; p. PS-10-18. [Google Scholar]

- Tabata, T. Nucleation and crystal growth in HfO2 thin films by UV nanosecond pulsed laser annealing. Appl. Phys. Express 2019, 13, 015509. [Google Scholar] [CrossRef]

- Tabata, T.; Halty, S.; Rozé, F.; Huet, K.; Mazzamuto, F. Non-doped HfO2 crystallization controlled by dwell time in laser annealing. Appl. Phys. Express 2021, 14, 115503. [Google Scholar] [CrossRef]

- Fina, I.; Fàbrega, L.; Langenberg, E.; Martí, X.; Sánchez, F.; Varela, M.; Fontcuberta, J. Nonferroelectric contributions to the hysteresis cycles in manganite thin films: A comparative study of measurement techniques. J. Appl. Phys. 2011, 109, 074105. [Google Scholar] [CrossRef]

- Xu, L.; Shibayama, S.; Izukashi, K.; Nishimura, T.; Yajima, T.; Migita, S.; Toriumi, A. General relationship for cation and anion doping effects on ferroelectric HfO2 formation. In Proceedings of the 2016 IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 3–7 December 2016; pp. 25.2.1–25.2.4. [Google Scholar] [CrossRef]

- Xu, L.; Nishimura, T.; Shibayama, S.; Yajima, T.; Migita, S.; Toriumi, A. Kinetic pathway of the ferroelectric phase formation in doped HfO2 films. J. Appl. Phys. 2017, 122, 124104. [Google Scholar] [CrossRef]

- Sundaram, S.K.; Mazur, E. Inducing and probing non-thermal transitions in semiconductors using femtosecond laser pulses. Nat. Mater. 2002, 1, 217–224. [Google Scholar] [CrossRef]

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2022 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Tabata, T.; Rozé, F.; Thuries, L.; Halty, S.; Raynal, P.-E.; Karmous, I.; Huet, K. Recent Progresses and Perspectives of UV Laser Annealing Technologies for Advanced CMOS Devices. Electronics 2022, 11, 2636. https://doi.org/10.3390/electronics11172636

Tabata T, Rozé F, Thuries L, Halty S, Raynal P-E, Karmous I, Huet K. Recent Progresses and Perspectives of UV Laser Annealing Technologies for Advanced CMOS Devices. Electronics. 2022; 11(17):2636. https://doi.org/10.3390/electronics11172636

Chicago/Turabian StyleTabata, Toshiyuki, Fabien Rozé, Louis Thuries, Sébastien Halty, Pierre-Edouard Raynal, Imen Karmous, and Karim Huet. 2022. "Recent Progresses and Perspectives of UV Laser Annealing Technologies for Advanced CMOS Devices" Electronics 11, no. 17: 2636. https://doi.org/10.3390/electronics11172636