Study on Single Event Upsets in a 28 nm Technology Static Random Access Memory Device Based on Micro-Beam Irradiation

Abstract

:1. Introduction

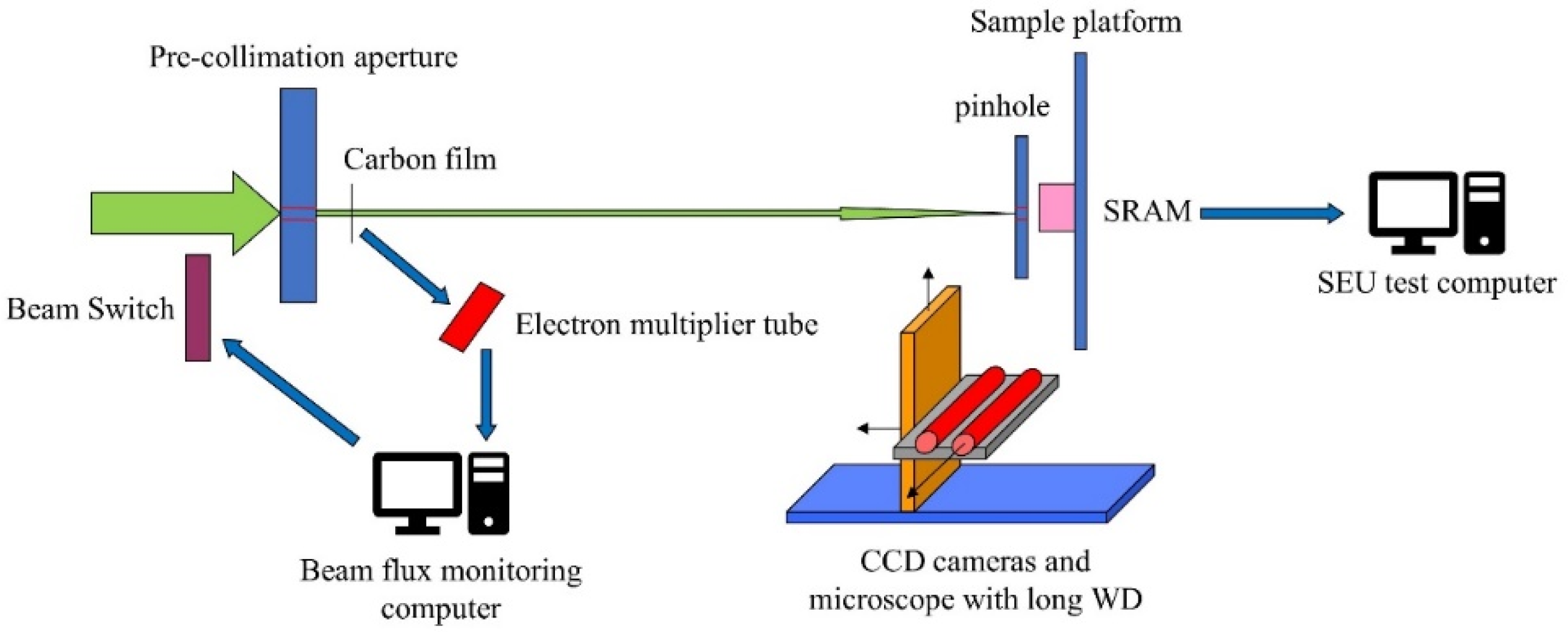

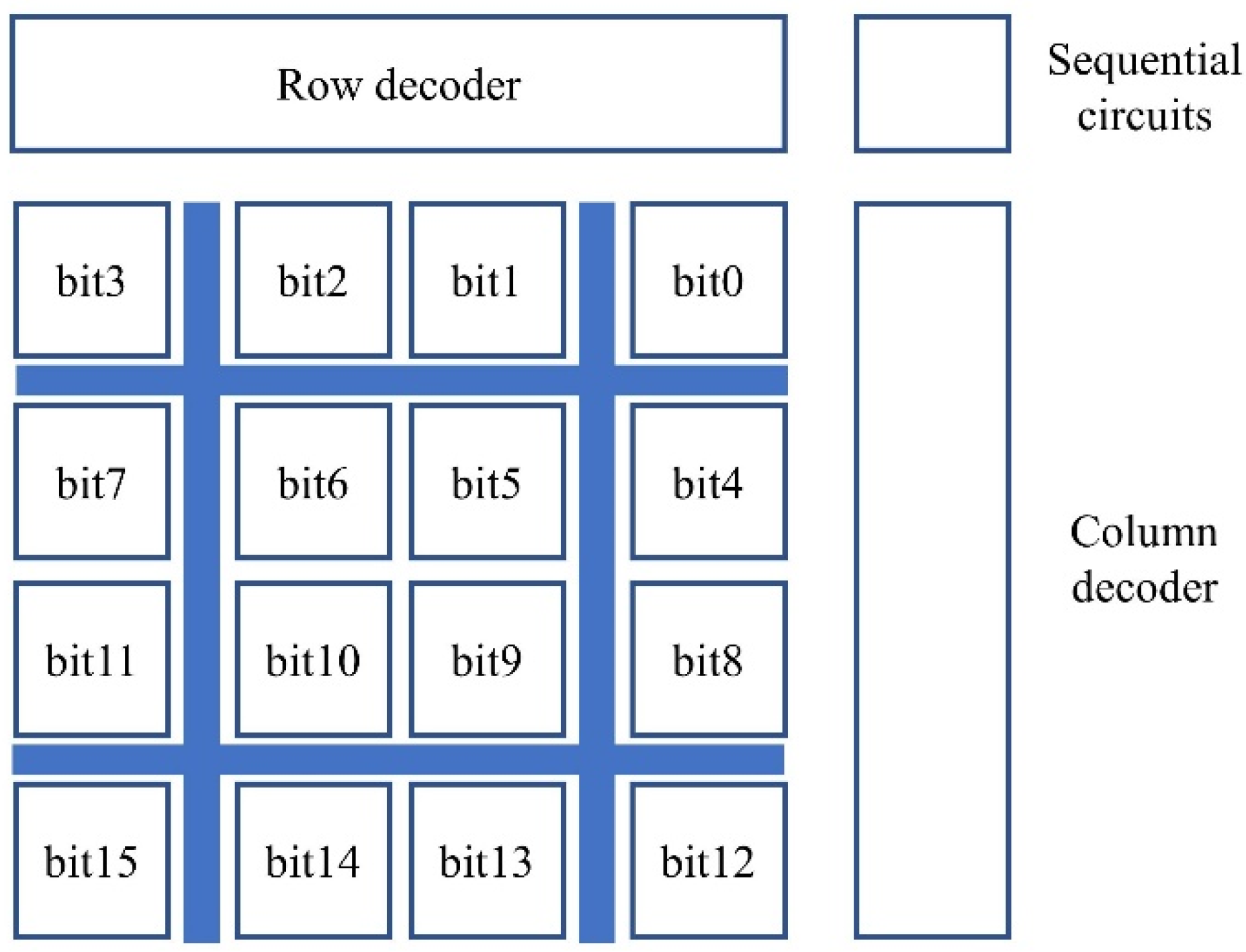

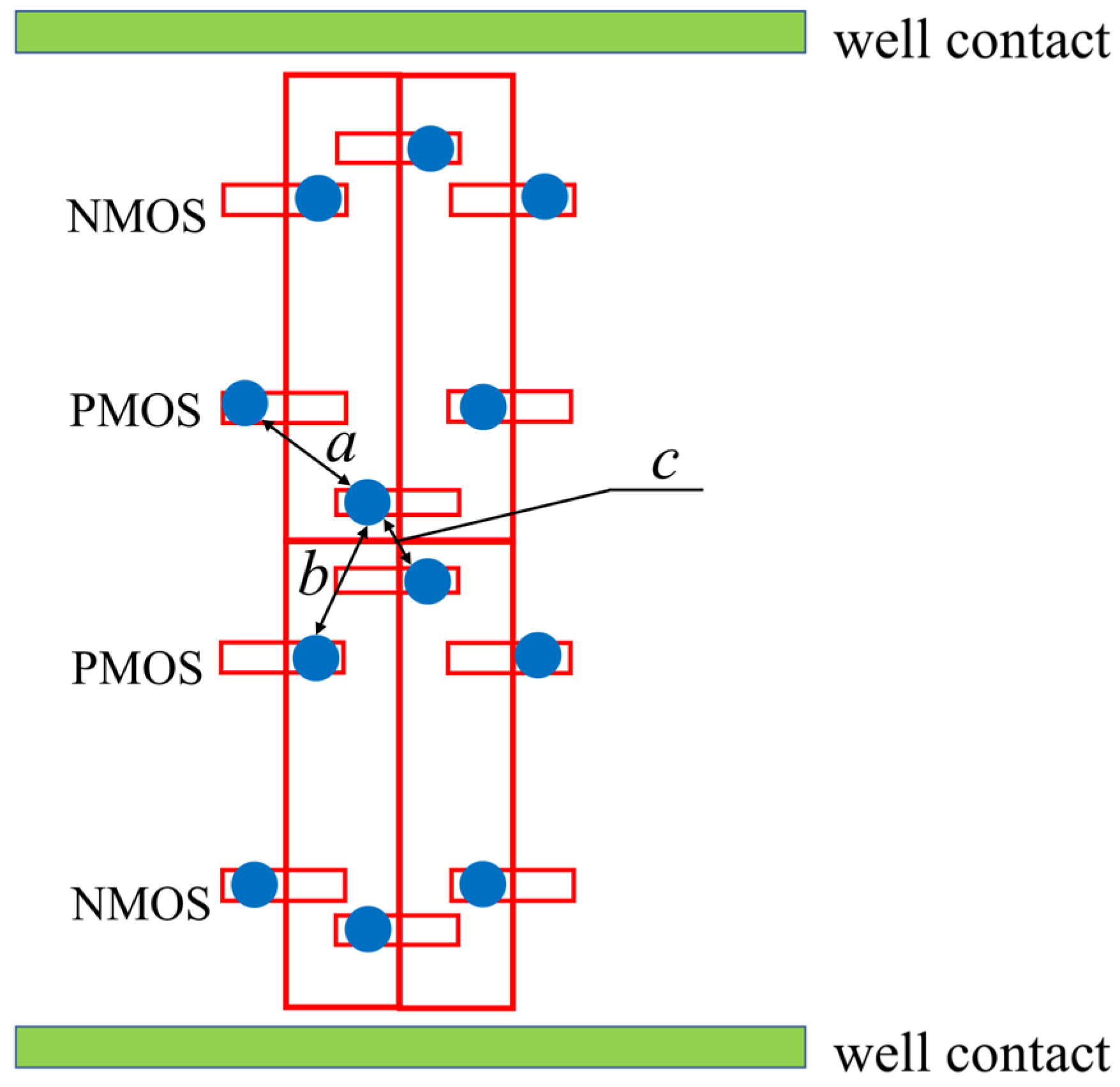

2. Experimental Setup

3. Results and Discussion

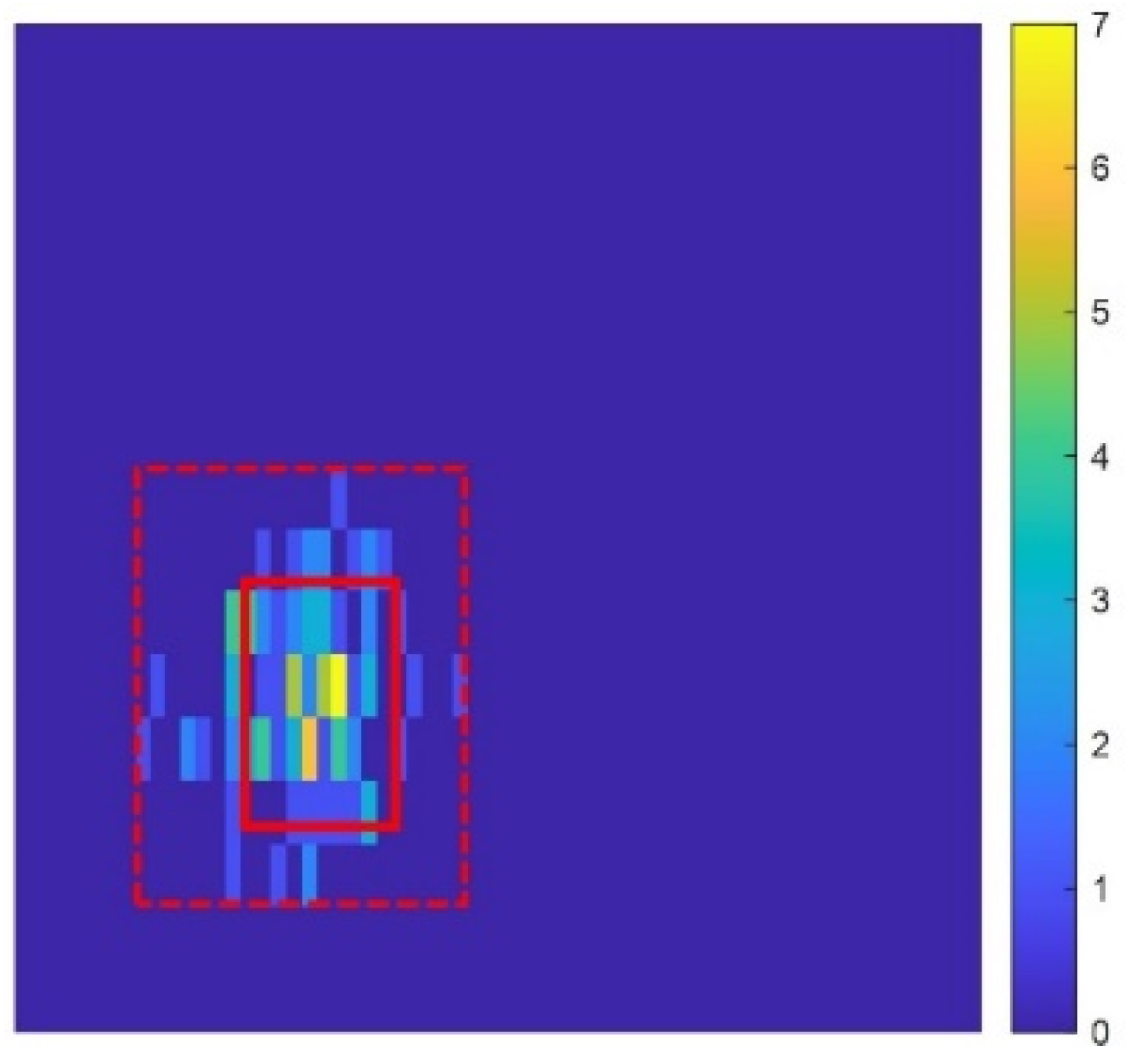

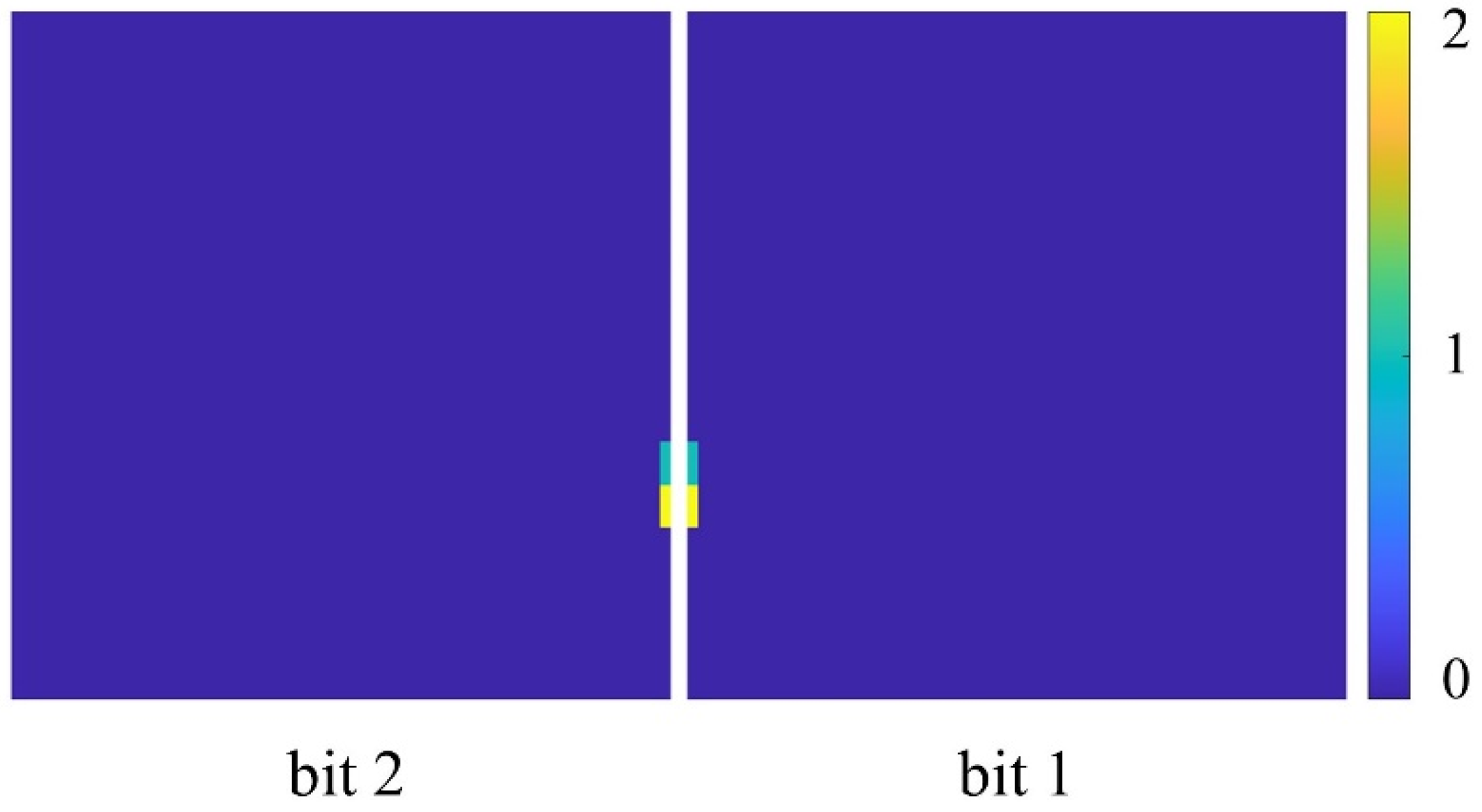

3.1. Evaluation of the Micro-Beam Spot Size

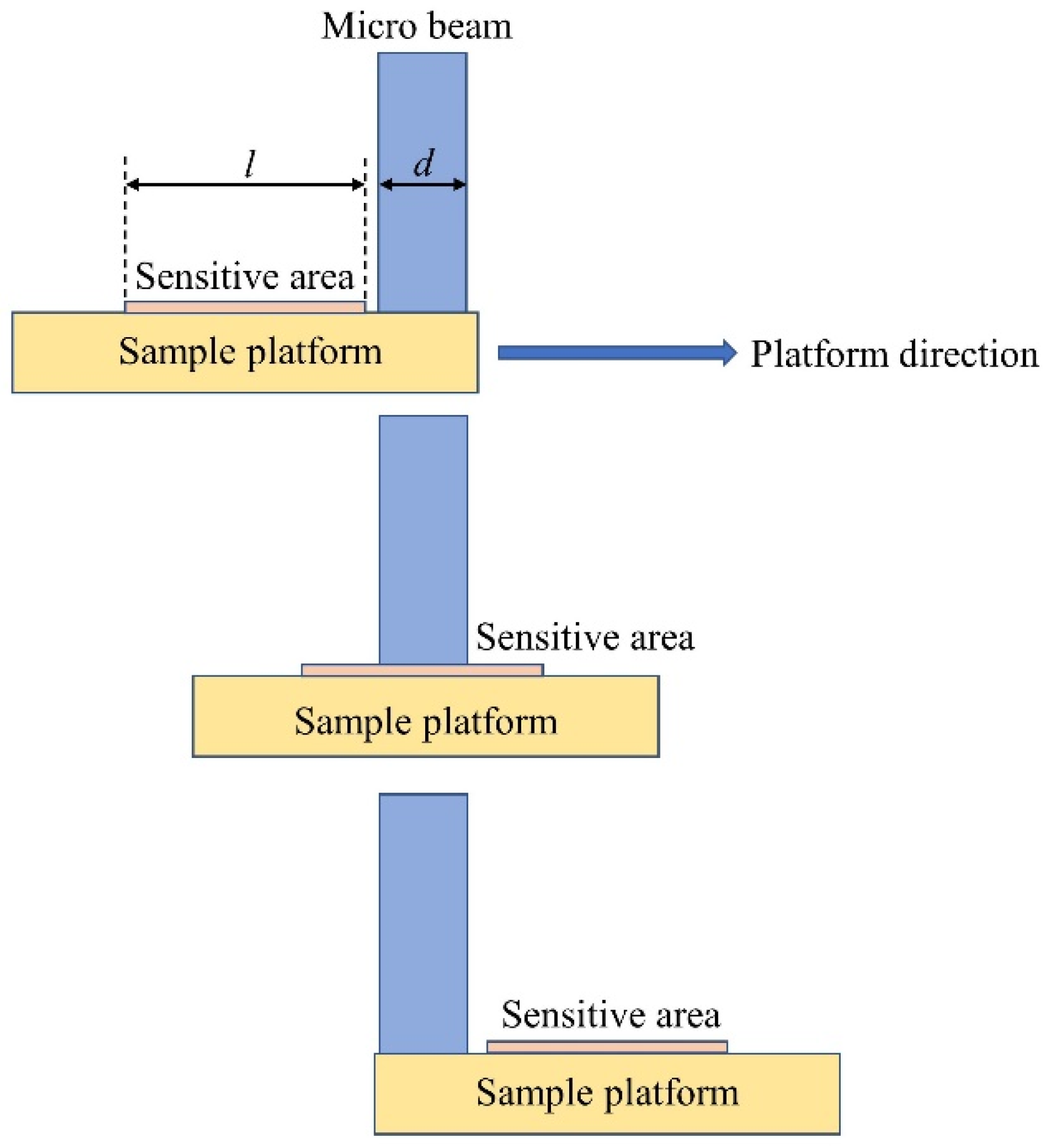

3.2. One-Dimensional SEU Sensitive Area Positioning

3.3. MCU/MBU Characteristics

4. Conclusions

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

References

- Fleetwood, D.M. Radiation effects in a post-Moore world. IEEE Trans. Nucl. Sci. 2021, 68, 509–545. [Google Scholar] [CrossRef]

- Kobayashi, D. Scaling trends of digital single-event effects: A survey of SEU and SET parameters and comparison with transistor performance. IEEE Trans. Nucl. Sci. 2020, 68, 124–148. [Google Scholar] [CrossRef]

- Dodd, P.; Massengill, L. Basic mechanisms and modeling of single-event upset in digital microelectronics. IEEE Trans. Nucl. Sci. 2003, 50, 583–602. [Google Scholar] [CrossRef]

- Saiz-Adalid, L.-J.; Reviriego, P.; Gil, P.; Pontarelli, S.; Maestro, J.A. MCU Tolerance in SRAMs through Low-Redundancy Triple Adjacent Error Correction. IEEE Trans. Very Large Scale Integr. (VLSI) Syst. 2014, 23, 2332–2336. [Google Scholar] [CrossRef] [Green Version]

- Baeg, S.; Wen, S.; Wong, R. SRAM Interleaving Distance Selection With a Soft Error Failure Model. IEEE Trans. Nucl. Sci. 2009, 56, 2111–2118. [Google Scholar] [CrossRef]

- Qi, C.; Xiao, L.; Wang, T.; Li, J.; Li, L. A Highly Reliable Memory Cell Design Combined with Layout-Level Approach to Tolerant Single-Event Upsets. IEEE Trans. Device Mater. Reliab. 2016, 16, 388–395. [Google Scholar] [CrossRef]

- Dodd, P.E.; Shaneyfelt, M.R.; Schwank, J.R.; Felix, J.A. Current and future challenges in radiation effects on CMOS electronics. IEEE Trans. Nucl. Sci. 2010, 57, 1747–1763. [Google Scholar] [CrossRef]

- Liu, J.; Yan, S.; Xue, J.; Wang, Y. Comparison of ionization track structure models for electronic devices of different sizes. Nucl. Instrum. Methods Phys. Res. Sect. B 2019, 444, 43–49. [Google Scholar] [CrossRef]

- Radaelli, D.; Puchner, H.; Wong, S.; Daniel, S. Investigation of multi-bit upsets in a 150 nm technology SRAM device. IEEE Trans. Nucl. Sci. 2005, 52, 2433–2437. [Google Scholar] [CrossRef]

- Wirthlin, M.; Lee, D.; Swift, G.; Quinn, H. A Method and Case Study on Identifying Physically Adjacent Multiple-Cell Upsets Using 28-nm, Interleaved and SECDED-Protected Arrays. IEEE Trans. Nucl. Sci. 2014, 61, 3080–3087. [Google Scholar] [CrossRef]

- Horn, K.; Doyle, B.; Sexton, F. Nuclear microprobe imaging of single-event upsets. IEEE Trans. Nucl. Sci. 1992, 39, 7–12. [Google Scholar] [CrossRef]

- Horn, K.; Doyle, B.; Sexton, F.; Laird, J.; Saint, A.; Cholewa, M.; Legge, G. Ion beam induced charge collection (IBICC) microscopy of ICs: Relation to single event upsets (SEU). Nucl. Instrum. Methods Phys. Res. Sect. B 1993, 77, 355–361. [Google Scholar] [CrossRef]

- Schone, H.; Walsh, D.; Sexton, F.; Doyle, B.; Dodd, P.; Aurand, J.; Flores, R.; Wing, N. Time-resolved ion beam induced charge collection (TRIBICC) in micro-electronics. IEEE Trans. Nucl. Sci. 1998, 45, 2544–2549. [Google Scholar] [CrossRef] [Green Version]

- Yang, W.; Du, X.; He, C.; Shi, S.; Cai, L.; Hui, N.; Guo, G.; Huang, C. Microbeam heavy-ion single-event effect on Xilinx 28-nm system on chip. IEEE Trans. Nucl. Sci. 2018, 65, 545–549. [Google Scholar] [CrossRef]

- Fischer, B.; Heiß, M.; Cholewa, M. About the art to shoot with single ions. Nucl. Instrum. Methods Phys. Res. Sect. B 2003, 210, 285–291. [Google Scholar] [CrossRef]

- Zhangd, K.; Furuta, J.; Kobayashi, K.; Onodera, H.; Zhang, K. Dependence of Cell Distance and Well-Contact Density on MCU Rates by Device Simulations and Neutron Experiments in a 65-nm Bulk Process. IEEE Trans. Nucl. Sci. 2014, 61, 1583–1589. [Google Scholar] [CrossRef]

| (a) | (b) | (c) | |

|---|---|---|---|

| Patterns |  |  |  , ,  |

| Percentage | 56% | 17% | 27% |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2022 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Sun, H.; Guo, G.; Sun, R.; Zhao, W.; Zhang, F.; Liu, J.; Zhang, Z.; Chen, Y.; Zhao, Y. Study on Single Event Upsets in a 28 nm Technology Static Random Access Memory Device Based on Micro-Beam Irradiation. Electronics 2022, 11, 3413. https://doi.org/10.3390/electronics11203413

Sun H, Guo G, Sun R, Zhao W, Zhang F, Liu J, Zhang Z, Chen Y, Zhao Y. Study on Single Event Upsets in a 28 nm Technology Static Random Access Memory Device Based on Micro-Beam Irradiation. Electronics. 2022; 11(20):3413. https://doi.org/10.3390/electronics11203413

Chicago/Turabian StyleSun, Haohan, Gang Guo, Ruinan Sun, Wen Zhao, Fengqi Zhang, Jiancheng Liu, Zheng Zhang, Ya Chen, and Yongle Zhao. 2022. "Study on Single Event Upsets in a 28 nm Technology Static Random Access Memory Device Based on Micro-Beam Irradiation" Electronics 11, no. 20: 3413. https://doi.org/10.3390/electronics11203413