2-Mbps Power-Line Communication Transmitter Based on Switched Capacitors for Automotive Networks

Abstract

:1. Introduction

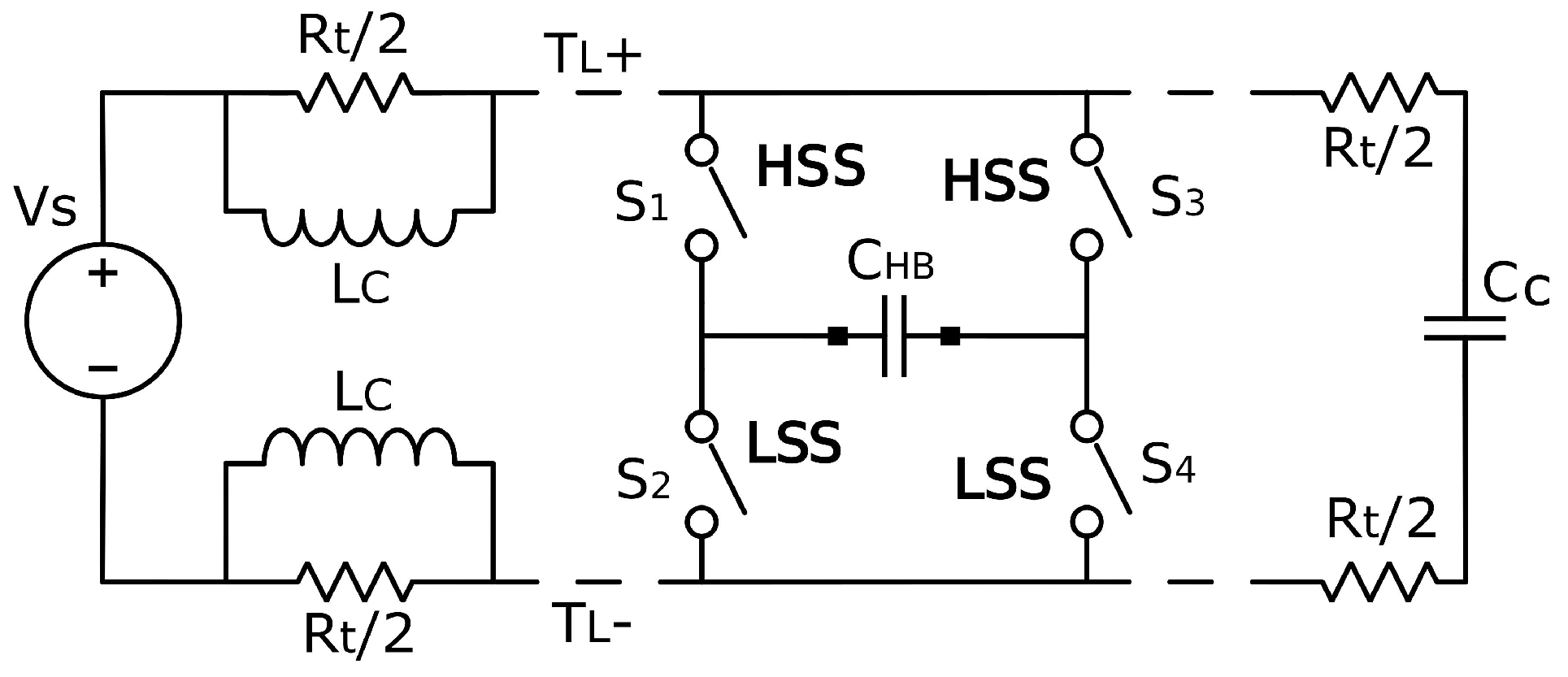

2. Switched-Capacitor Transmitter Topologies

2.1. H-Bridge Topology

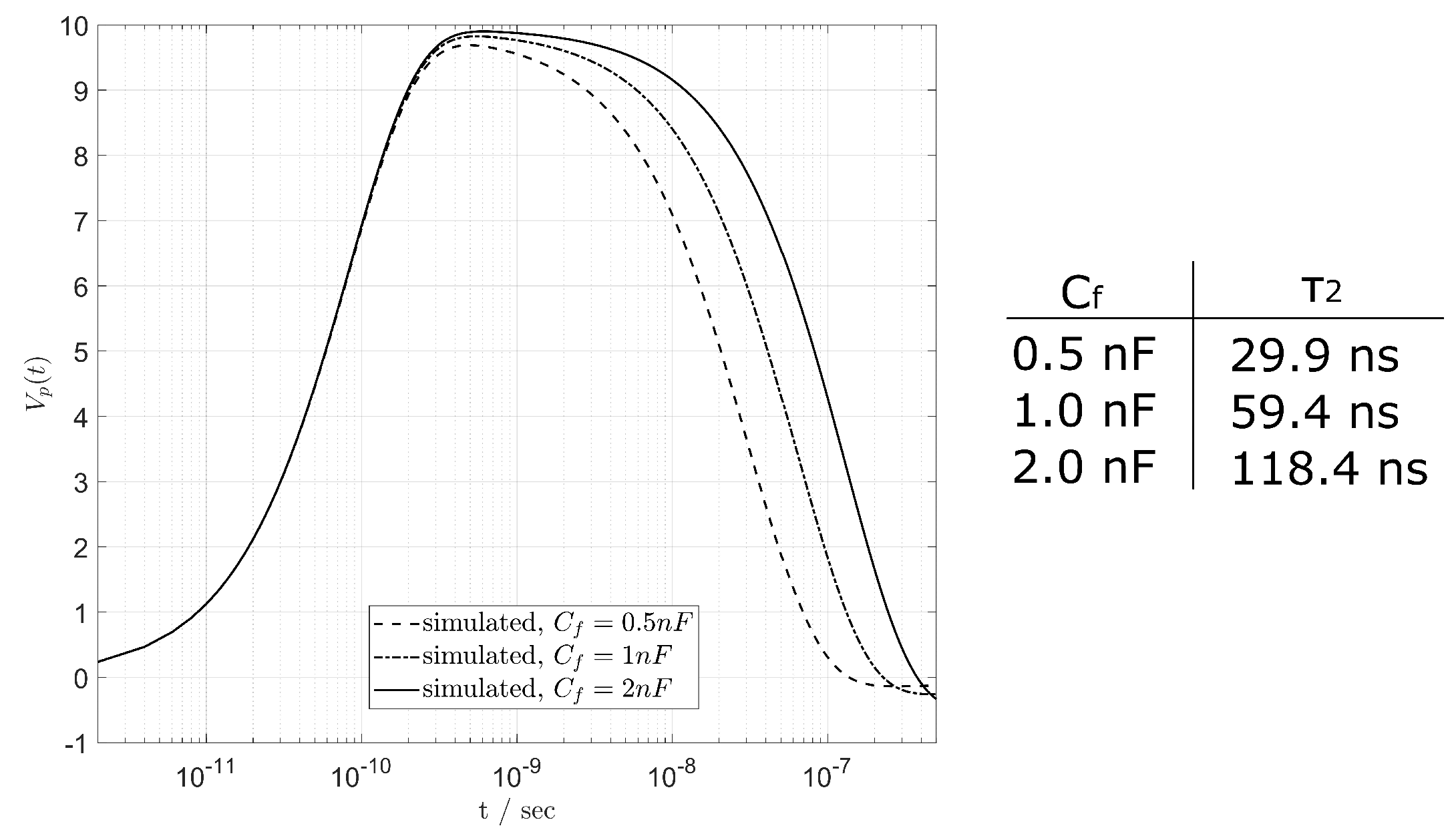

2.2. 3-Switches Topology

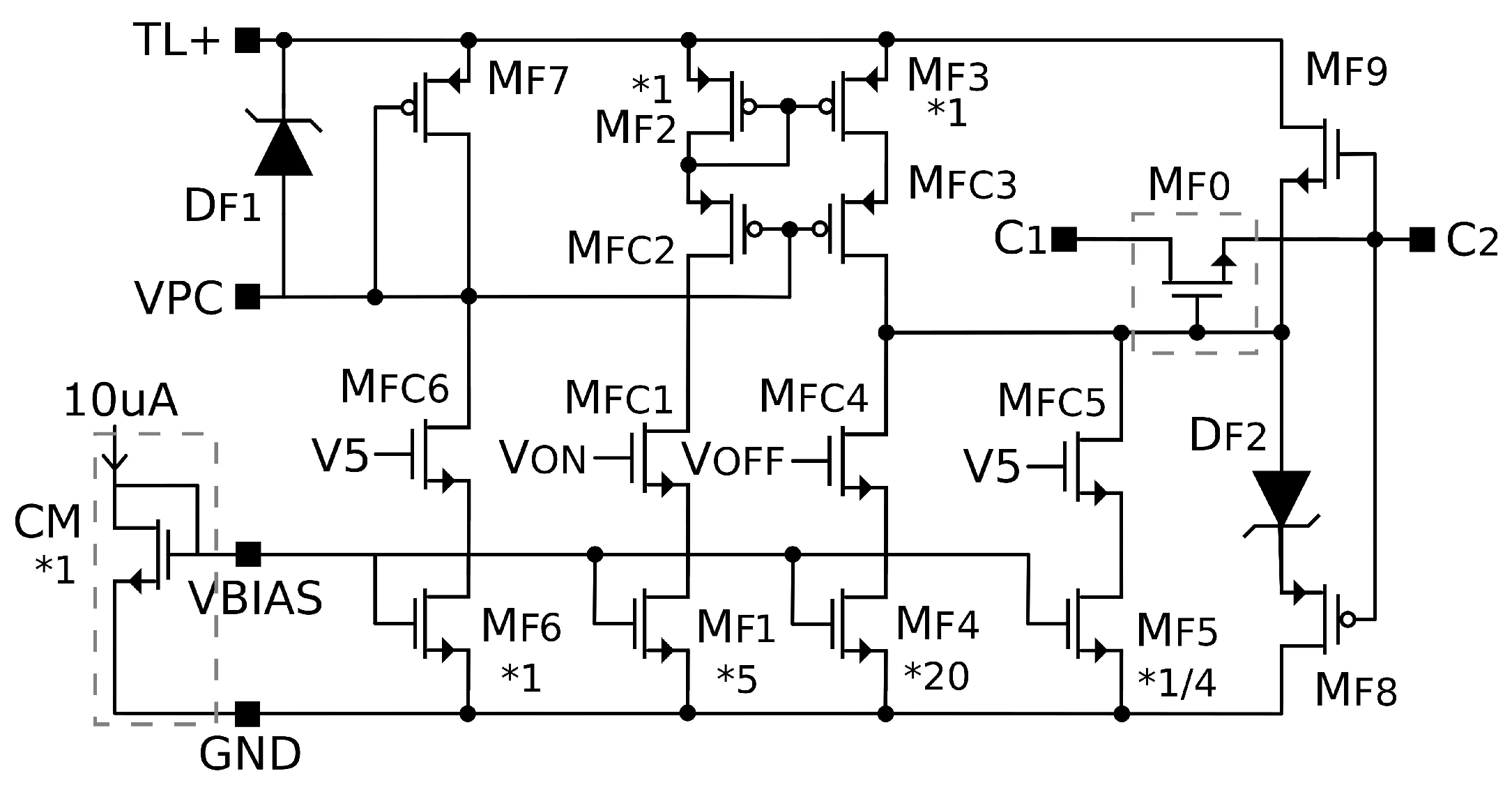

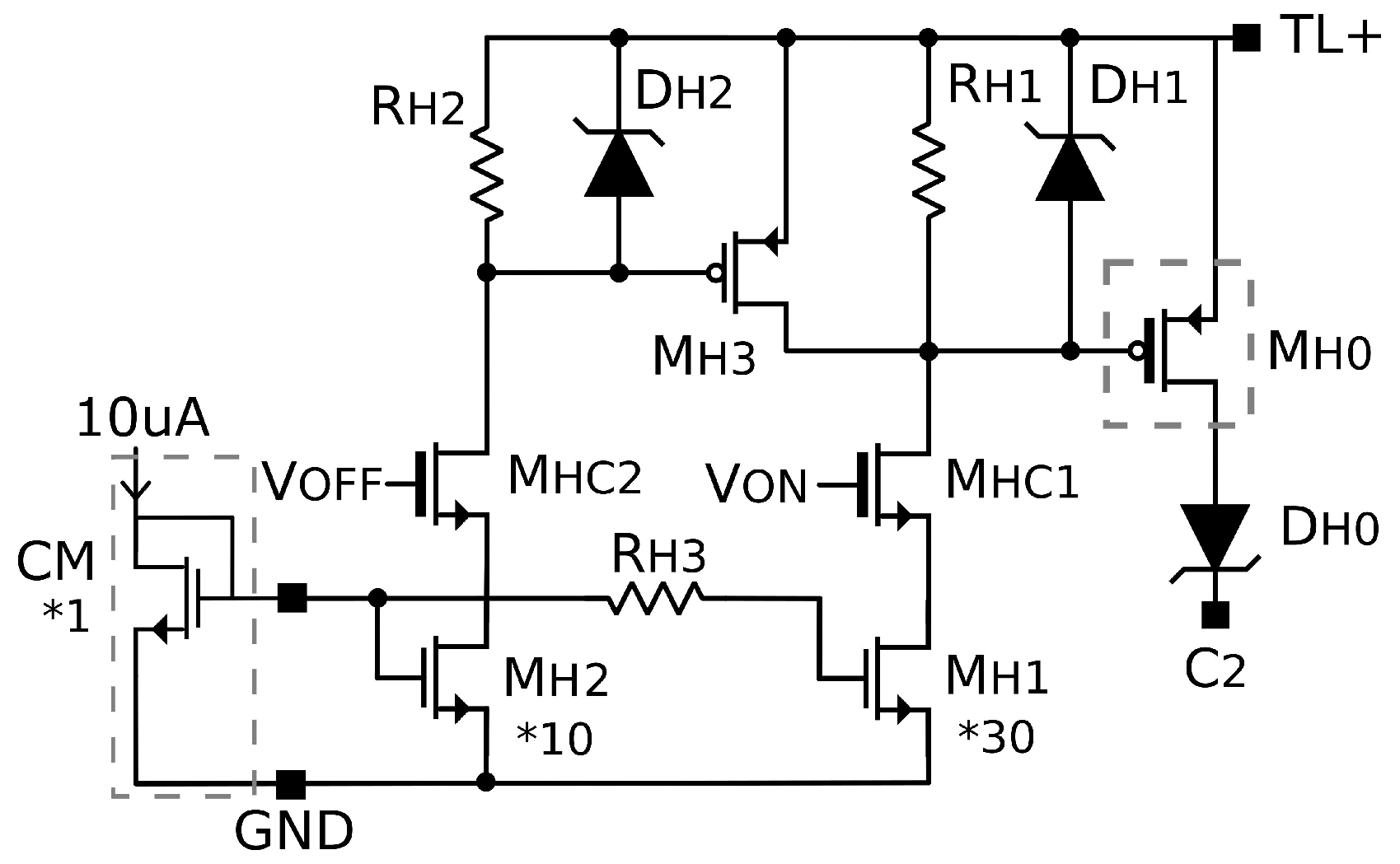

3. Switch Implementations

3.1. Floating Switch

3.2. Low Side Switch

3.3. High Side Switch

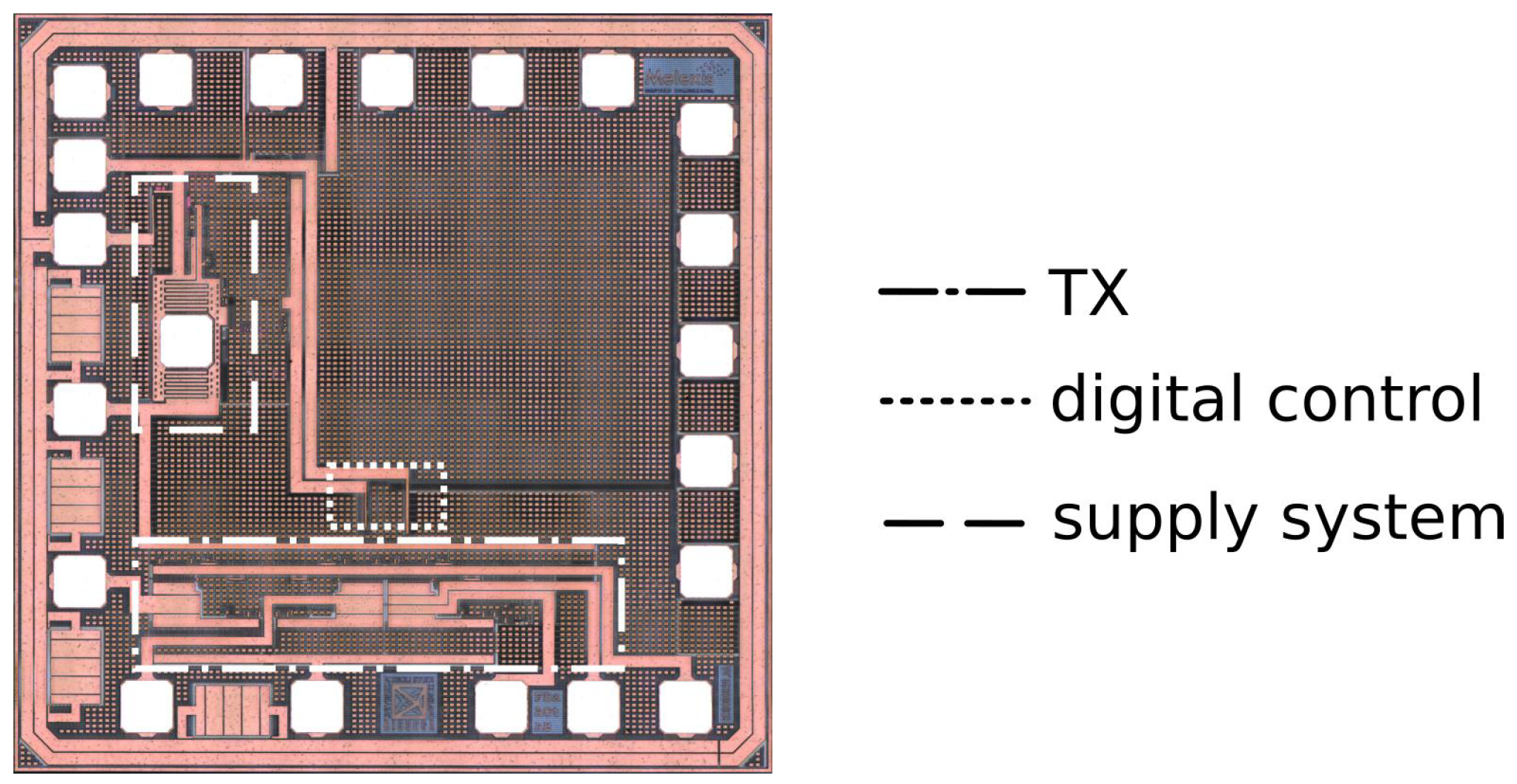

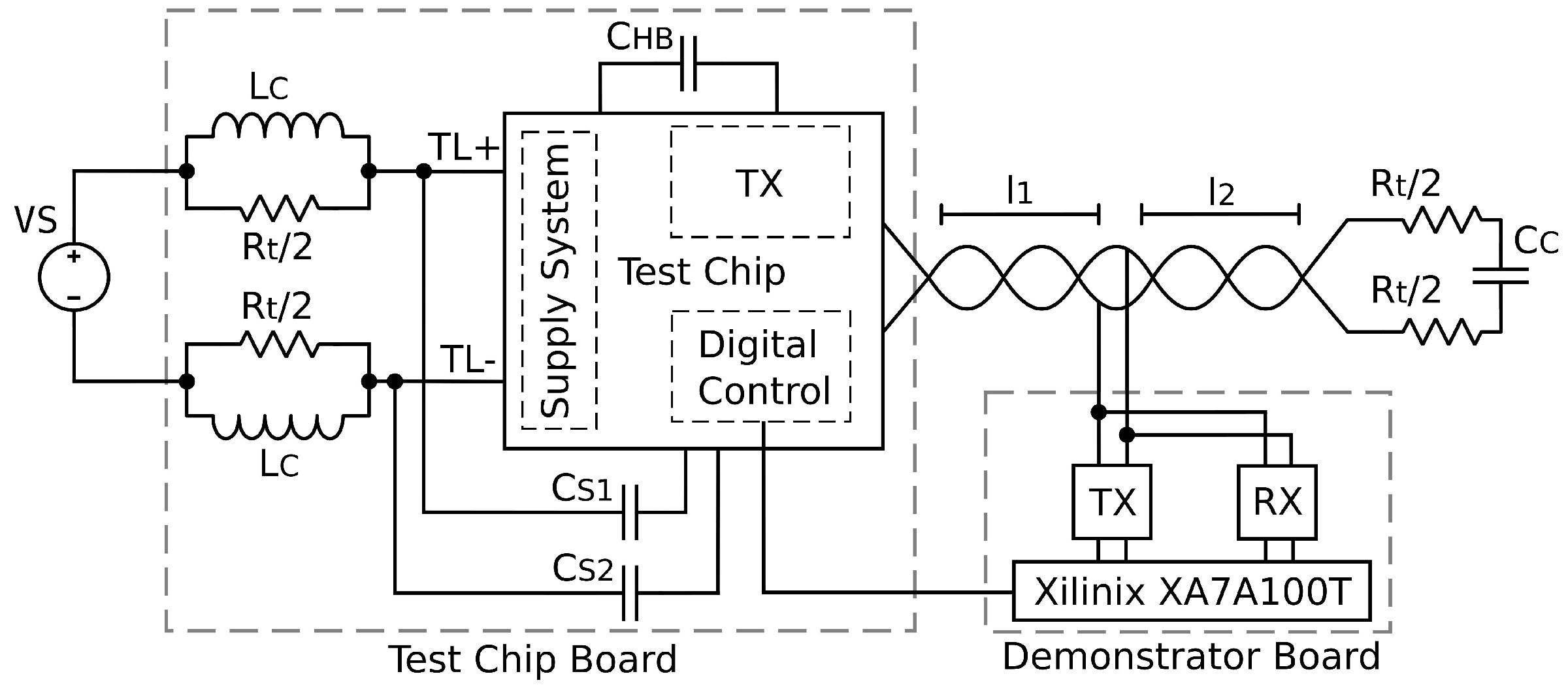

4. Fabricated Prototype

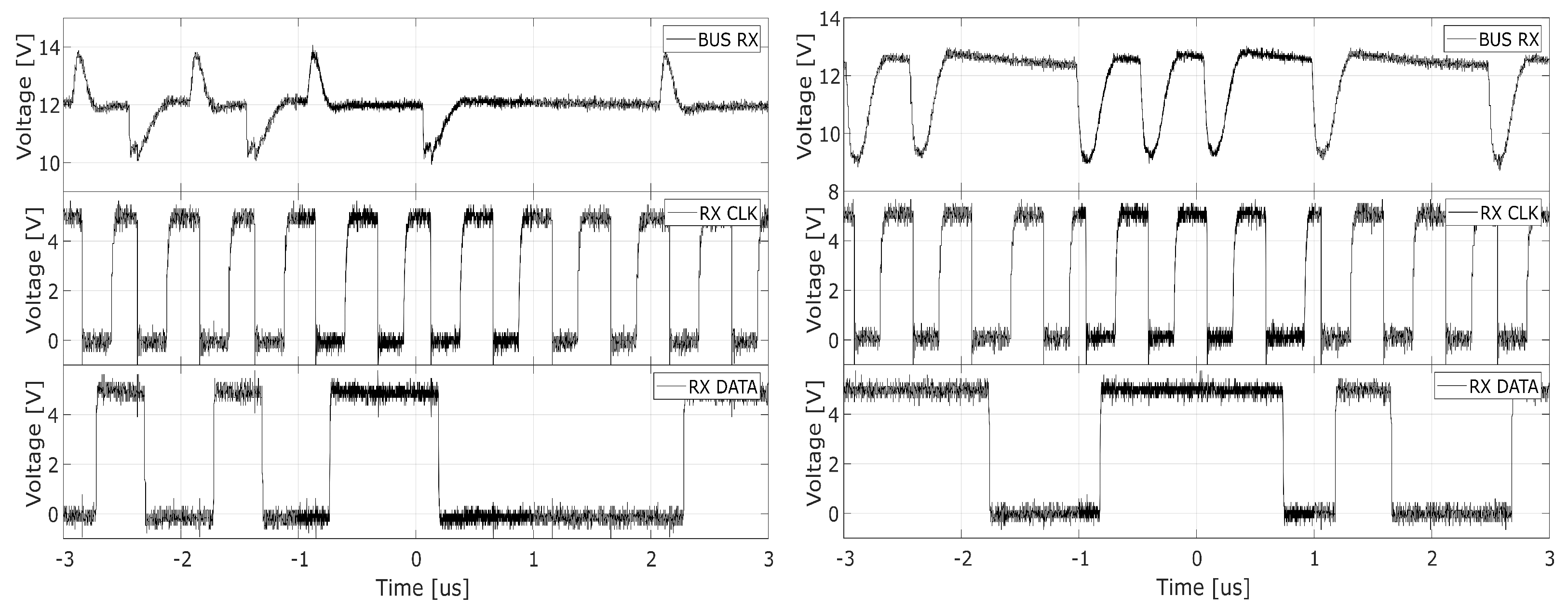

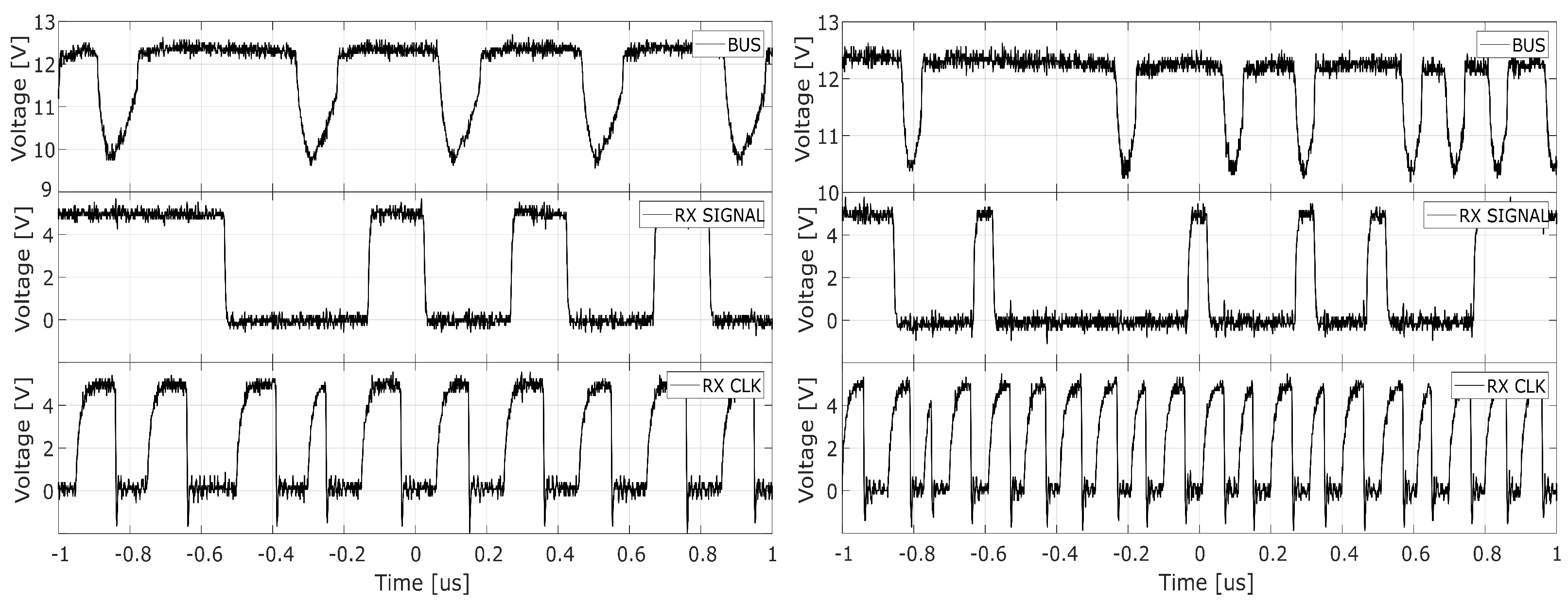

5. Measurements Results

6. Conclusions

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

References

- Ahmad, A. Automotive Semiconductor Industry—Trends, Safety and Security Challenges. In Proceedings of the 2020 8th International Conference on Reliability, Infocom Technologies and Optimization (Trends and Future Directions) (ICRITO), Noida, India, 4–5 June 2020; pp. 1373–1377. [Google Scholar]

- Challenges and Technologies—NXP Semiconductor. Available online: https://www.nxp.com/files-static/training_pdf/VFTF09_AA106.pdf (accessed on 19 July 2022).

- Heisler, P.; Kuhn, M.; Süß-Wolf, R.; Franke, J. Innovative Solutions for the Covering Process in the Manufacturing of Wire Harnesses to Increase the Automation Degree. In Proceedings of the 2020 IEEE 11th International Conference on Mechanical and Intelligent Manufacturing Technologies (ICMIMT), Cape town, South Africa, 20–22 January 2020; pp. 193–201. [Google Scholar]

- Lodi, G.A.; Ott, A.; Cheema, S.A.; Haardt, M.; Freitag, T. Power Line Communication in automotive harness on the example of Local Interconnect Network. In Proceedings of the International Symposium on Power Line Communications and its Applications, (ISPLC), Bottrop, Germany, 20–23 May 2016. [Google Scholar]

- DCAN500 CAN Power Line Transceiver. Available online: https://yamar.com/product/dcan500/ (accessed on 19 July 2022).

- Llaria, A.; Terrasson, G.; Pierlot, N. Feasibility of power supply over CAN bus: Study on different elementary design aspects. In Proceedings of the 2018 IEEE/AIAA 37th Digital Avionics Systems Conference (DASC), London, UK, 23–27 September 2018; pp. 1–7. [Google Scholar]

- ISO/TX 22/SC 31; ISO 11898-2:2016: Road Vehicles—Controller Area Network (CAN)—Part 2: High-Speed Medium Access Unit. ISO: Geneva, Switzerland, 2016.

- Grassi, F.; Pignari, S.A. Coupling/decoupling circuits for powerline communications in differential DC power buses. In Proceedings of the 2012 IEEE International Symposium on Power Line Communications and Its Applications, ISPLC 2012, Beijing, China, 27–30 March 2012; pp. 392–397. [Google Scholar]

- D’Aniello, F.; Ott, A.; Baschirotto, A. Supply Line Embedded Communication inAutomotive Sensor/Actuator Networks. In Proceedings of the 2021 IEEE International Symposium on Circuits and Systems, ISCAS 2021, Daegu, Korea, 23–26 May 2021. [Google Scholar]

- Ott, A.; D’Aniello, F.; Baschirotto, A. A Switched Capacitor Approach for Power Line Communication in Differential Networks. In Proceedings of the 2022 IEEE 17th International Conference on PhD Research in Microelectronics and Electronics, PRIME 2022, Villasimius, Italy, 12–15 June 2022. [Google Scholar]

- ISO/TC 22/SC 31; ISO 17987-3:2016: Road Vehicles—Local Inter-Connect Network (LIN)—Part 3: Protocol Specification. ISO: Geneva, Switzerland, 2016.

- Deffebach, H.L.; Frost, W. A Survey of Digital Baseband Signaling Techniques. NASA George C. Marshall Space Flight Center, Alabama, Tech. Rep. 1971. Available online: https://ntrs.nasa.gov/api/citations/19710028227/downloads/19710028227.pdf (accessed on 19 July 2022).

- D’Aniello, F.; Ott, A.; Baschirotto, A. StrongArm-Latch-Based Receiver for Supply Line Embedded Communication. In Proceedings of the 2022 IEEE 17th International Conference on PhD Research in Microelectronics and Electronics, PRIME 2022, Villasimius, Italy, 12–15 June 2022. [Google Scholar]

| State | S1, S4 | S2, S3 | Description |

|---|---|---|---|

| Open | Open | Open | not connected. Charge is preserved |

| Charge 1–4 | Close | Open | charge accumulated during Charge 2–3 phase is recharged to level |

| Charge 2–3 | Open | Close | charge accumulated during Charge 1–4 phase is recharged to the level |

| State | S1, S2 | S3 | Description |

|---|---|---|---|

| Open | Open | Open | , not connected. Charges are preserved |

| Charge | Close | Open | , are connected in parallel to the bus and charged to |

| Discharge | Open | Close | , are connected in series and discharged to |

| l1 = 0.25 m l2 = 0.25 m | l1 = 6 m l2 = 0.25 m | l1 = 0.25 m l2 = 6 m | ||||

|---|---|---|---|---|---|---|

| Charge 1–4/2–3 | Charge 1–4/2–3 | Charge 1–4/2–3 | ||||

| 820 pF | 3.29 | 240 | 2.85 | 251 | 4.35 | 246 |

| 330 pF | 3.16 | 120 | 2.6 | 124 | 4.04 | 125 |

| 180 pF | 2.75 | 81 | 2.19 | 91 | 3.14 | 83 |

| l1 = 0.25 m l2 = 0.25 m | l1 = 6 m l2 = 0.25 m | l1 = 0.25 m l2 = 6 m | ||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|

| Charge | Discharge | Charge | Discharge | Charge | Discharge | |||||||

| 820 pF | 2.88 | 211 | 2.5 | 96 | 2.13 | 254 | 1.81 | 95 | 3.38 | 203 | 2.81 | 94 |

| 330 pF | 2.63 | 97 | 1.31 | 72 | 1.59 | 140 | 1.03 | 72 | 2.88 | 114 | 1.56 | 70 |

| 180 pF | 2.16 | 55 | 0.78 | 65 | 1.44 | 96 | 0.59 | 59 | 2.44 | 78 | 0.97 | 60 |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2022 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

D’Aniello, F.; Ott, A.; Baschirotto, A. 2-Mbps Power-Line Communication Transmitter Based on Switched Capacitors for Automotive Networks. Electronics 2022, 11, 3651. https://doi.org/10.3390/electronics11223651

D’Aniello F, Ott A, Baschirotto A. 2-Mbps Power-Line Communication Transmitter Based on Switched Capacitors for Automotive Networks. Electronics. 2022; 11(22):3651. https://doi.org/10.3390/electronics11223651

Chicago/Turabian StyleD’Aniello, Federico, Andreas Ott, and Andrea Baschirotto. 2022. "2-Mbps Power-Line Communication Transmitter Based on Switched Capacitors for Automotive Networks" Electronics 11, no. 22: 3651. https://doi.org/10.3390/electronics11223651