A 12-Bit, 100 MS/s SAR ADC Based on a Bridge Capacitor Array with Redundancy and Non-Linearity Calibration in 28 nm CMOS

Abstract

:1. Introduction

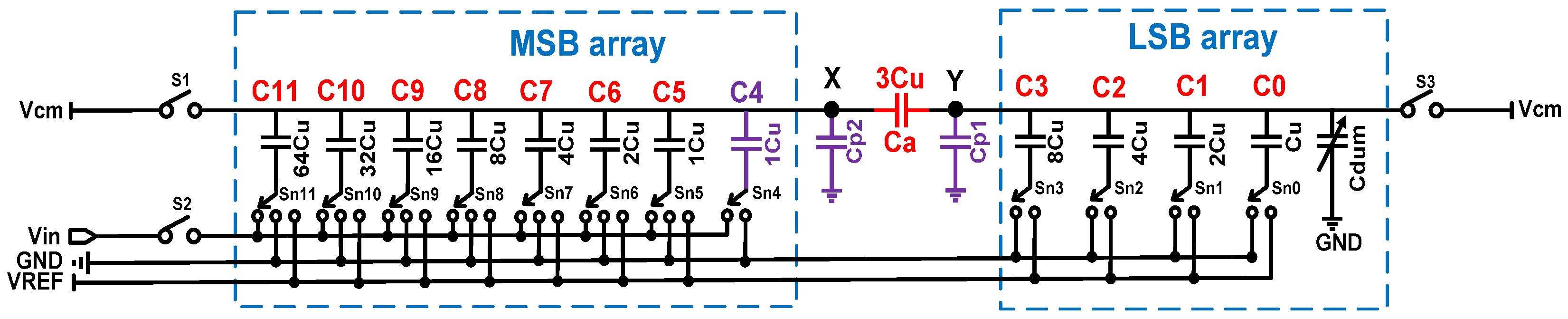

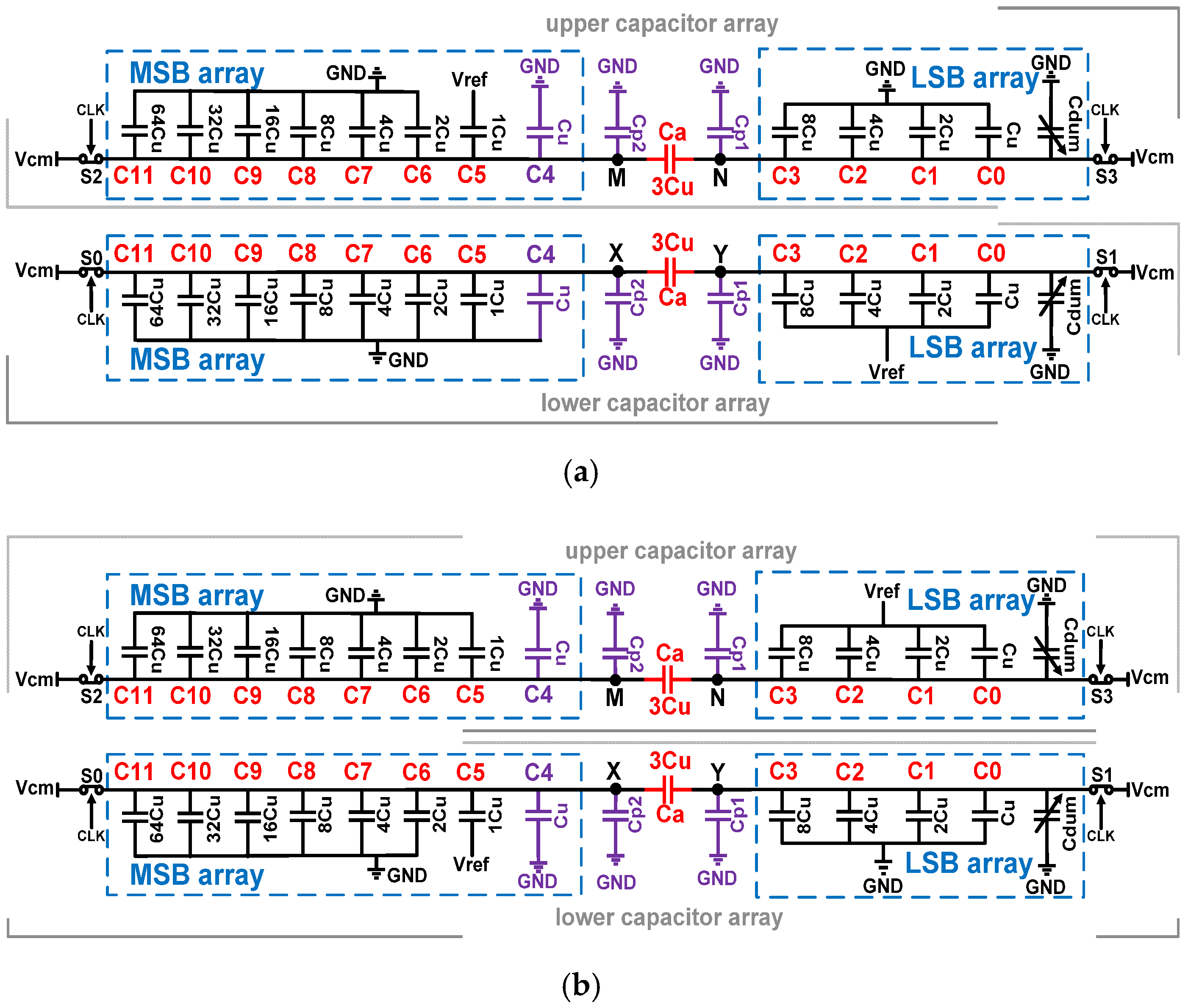

2. SAR ADC Overall Architecture

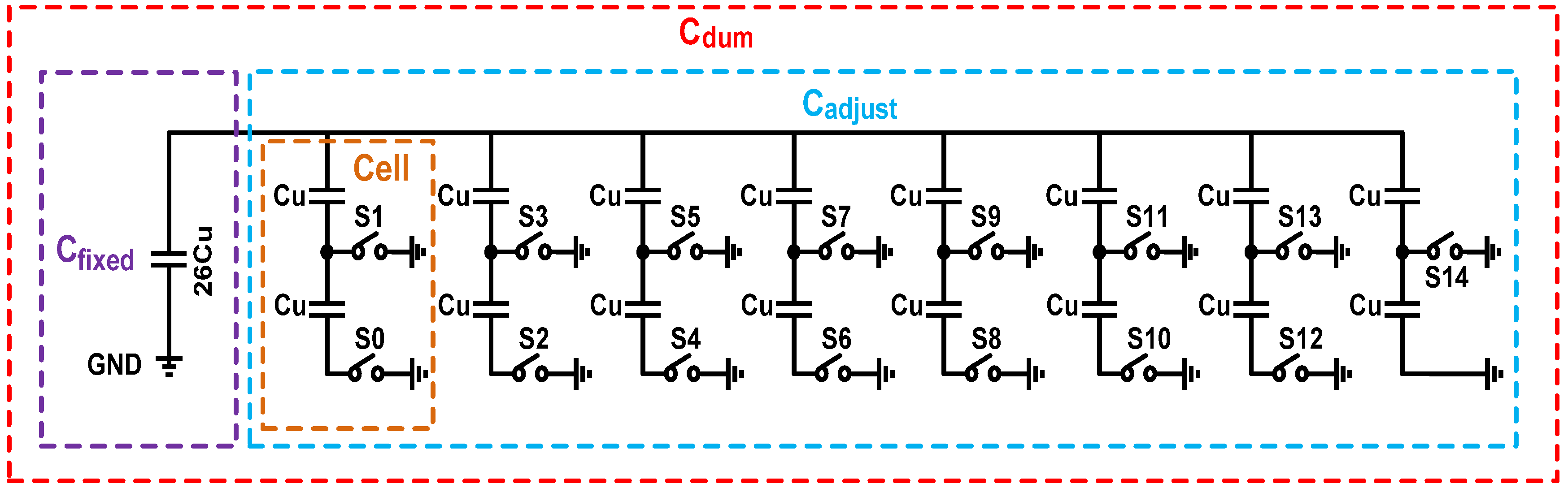

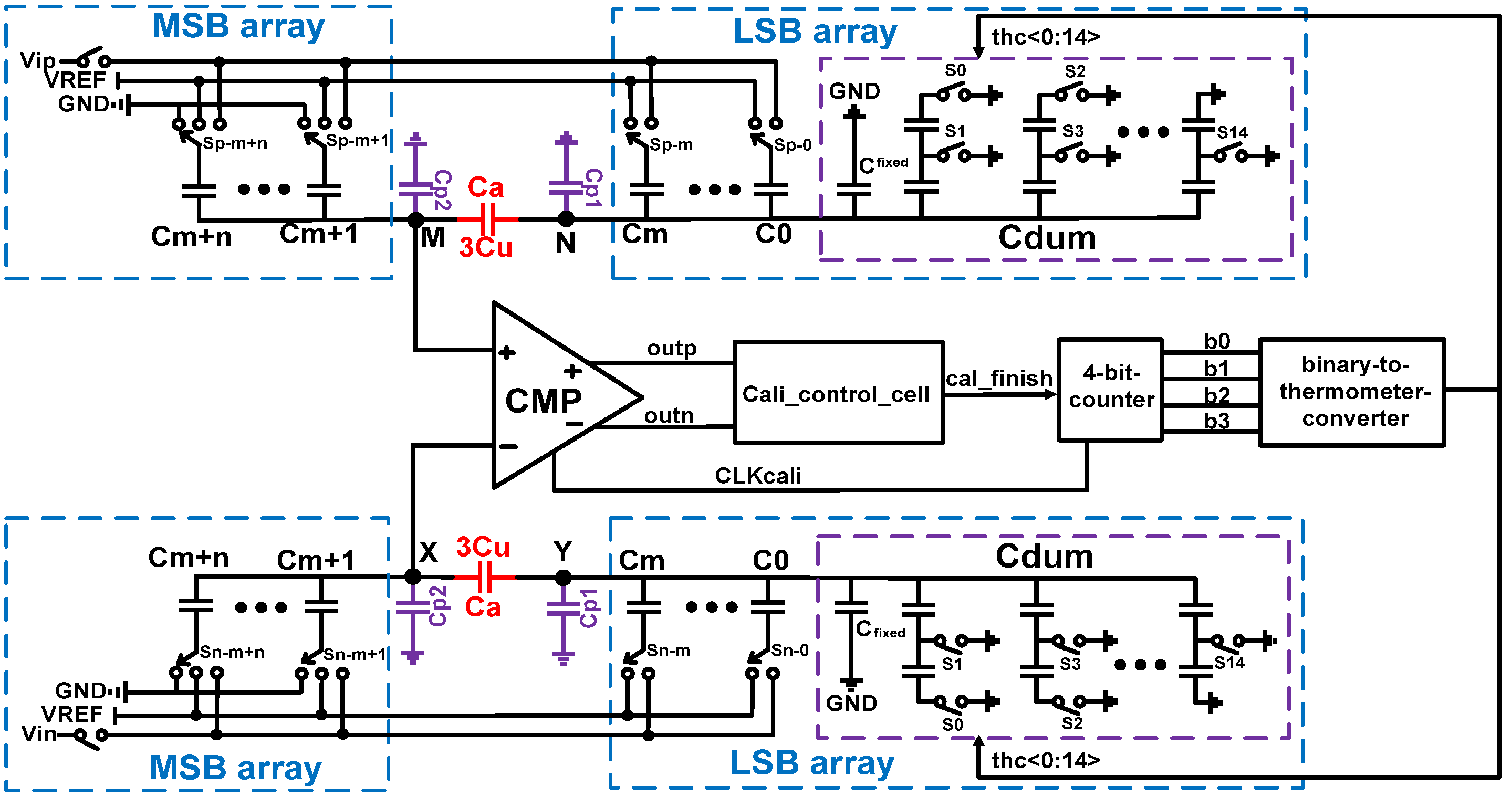

3. The Proposed Differential Non-Linearity Calibration Method and Hybrid Redundancy Scheme

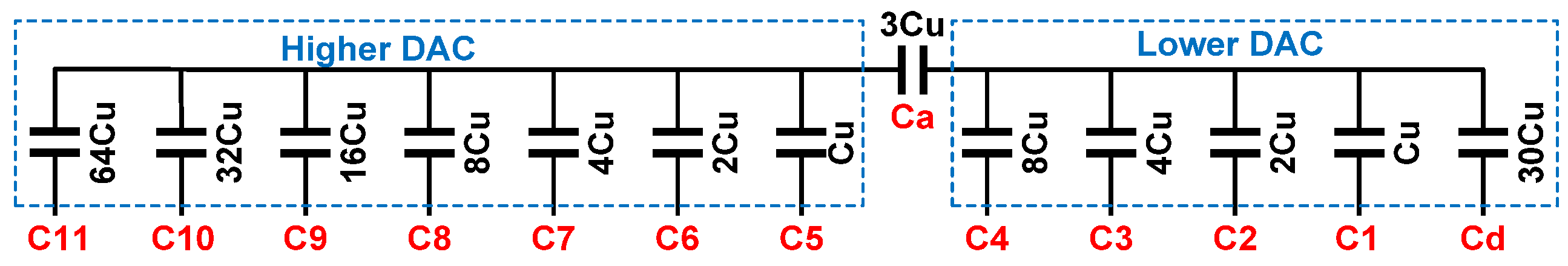

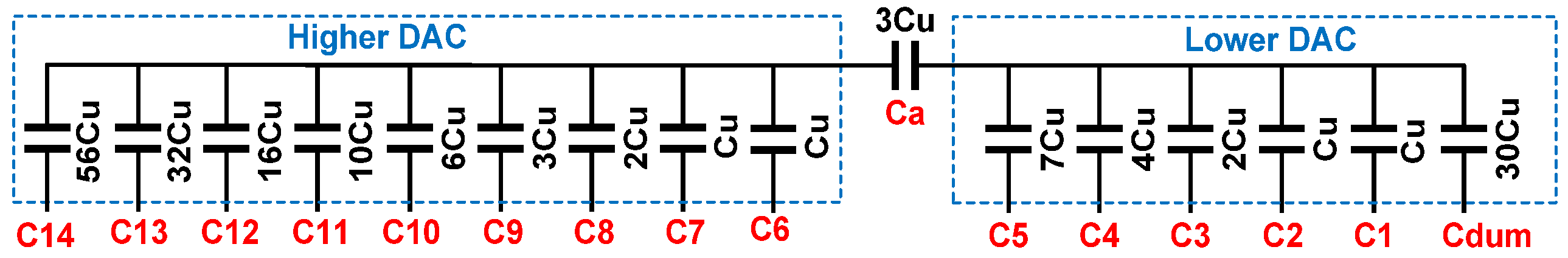

3.1. Analysis of Parasitic Capacitance in the Bridge DAC Capacitor Array

3.2. The Proposed Differential Non-Linearity Calibration Method

3.3. The Proposed Hybrid Redundancy Method

4. The Implementation of Key Building Blocks

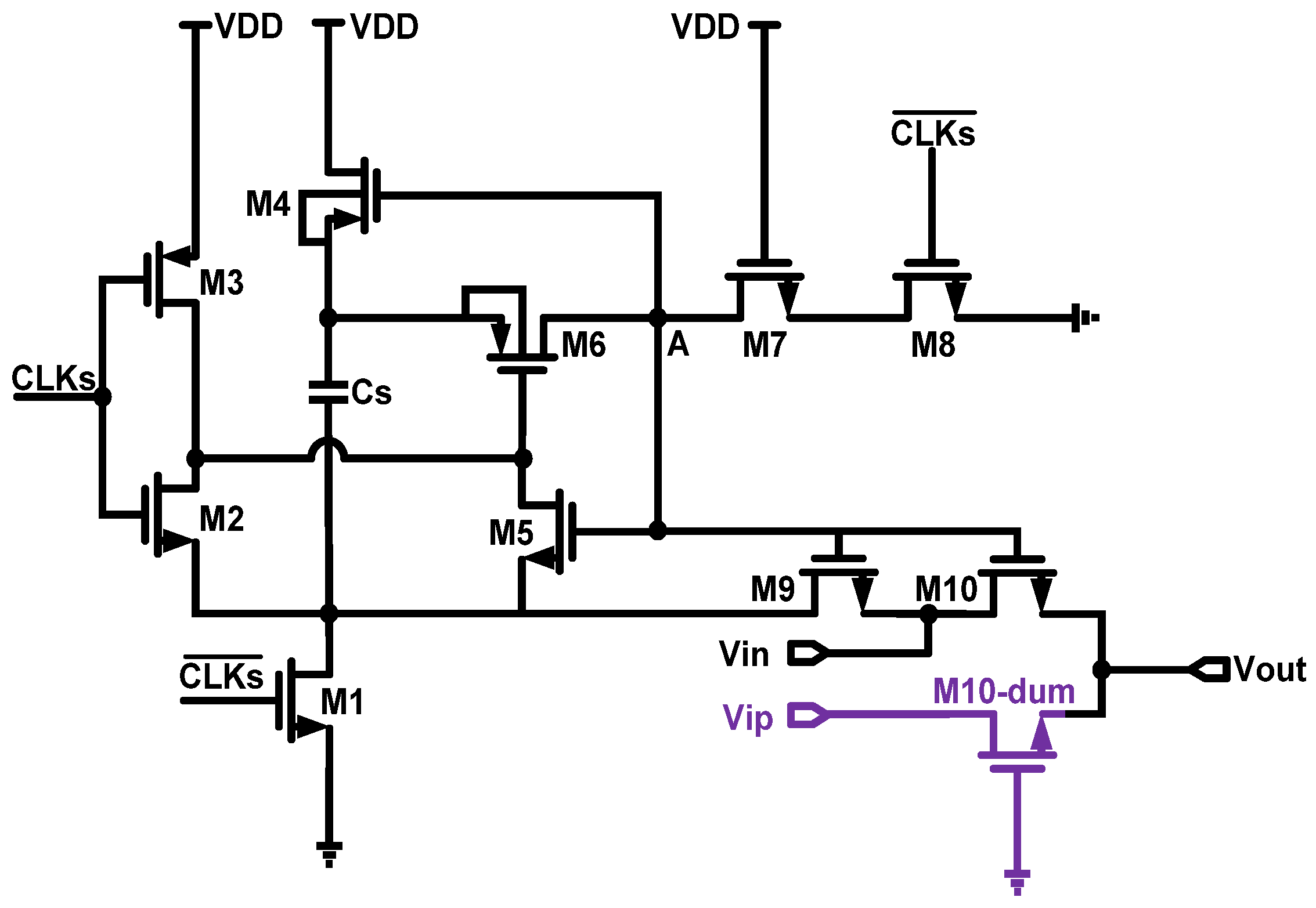

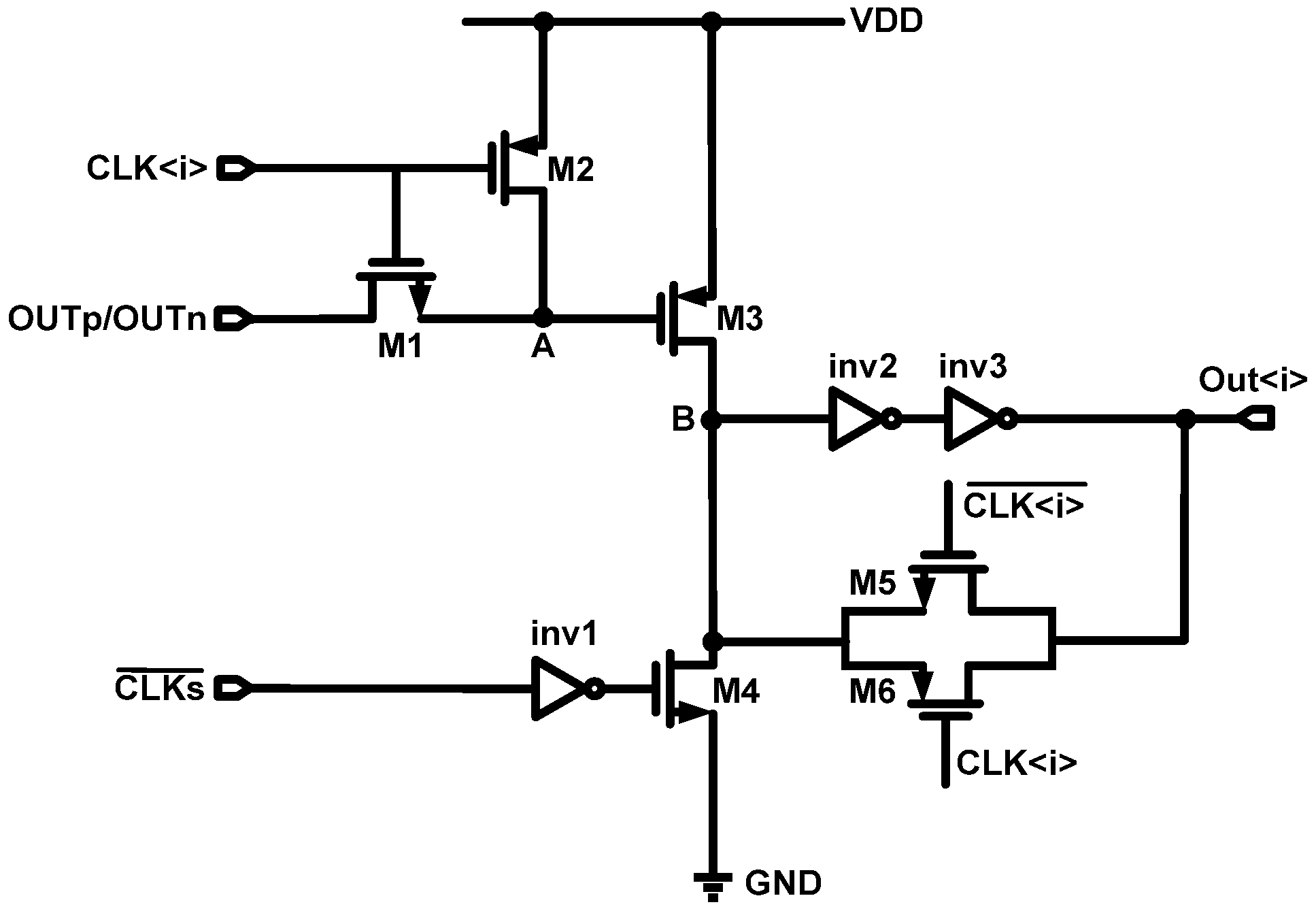

4.1. Bootstrapped Switch

4.2. Dynamic Comparator

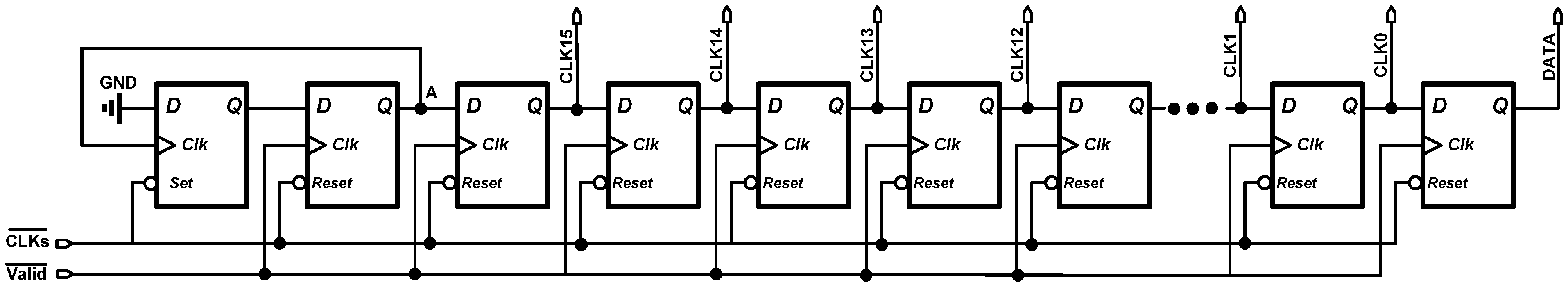

4.3. Asynchronous Dynamic Control Logic

4.4. Capacitor Array

4.5. Clock Driver

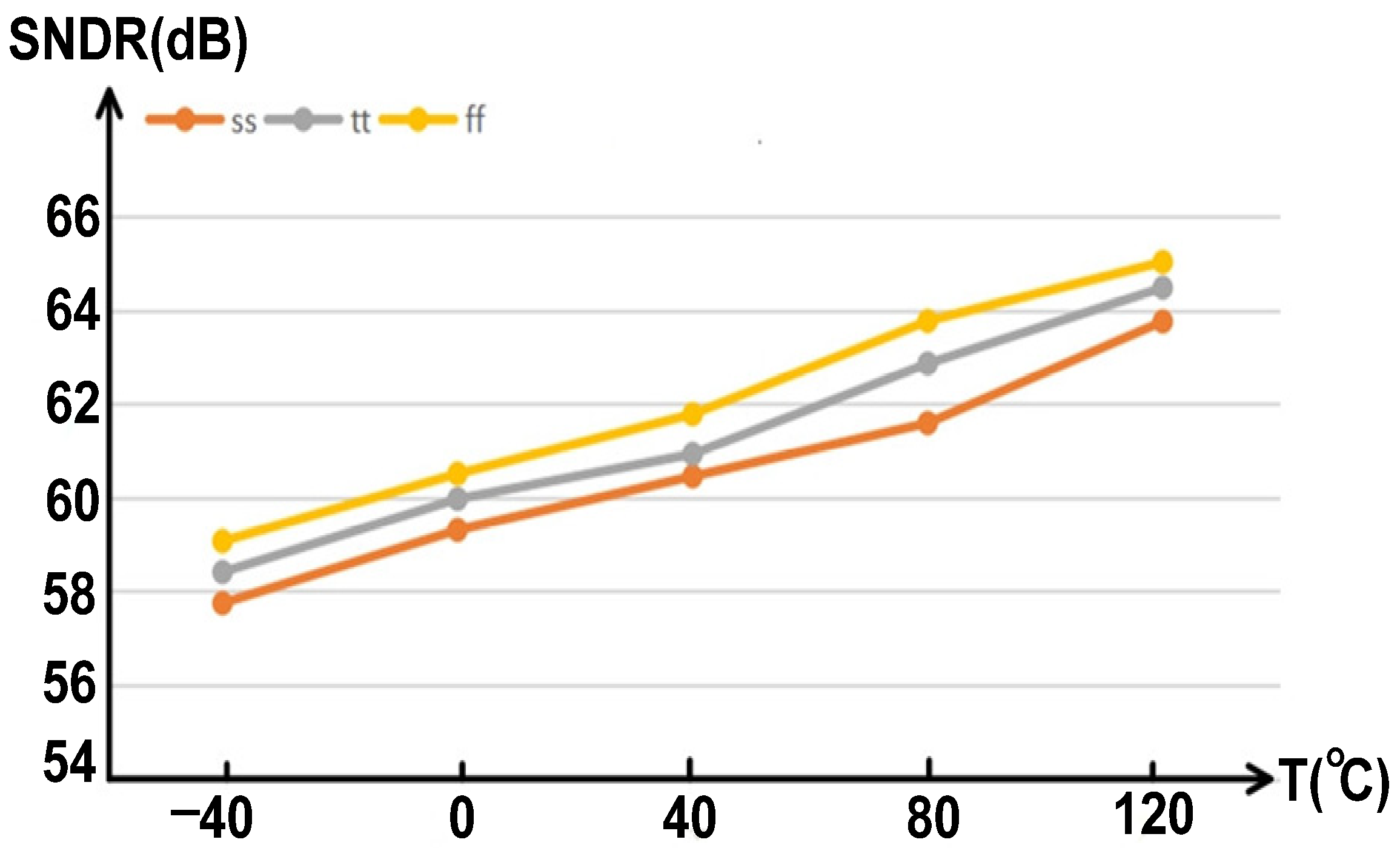

4.6. Post Simulation

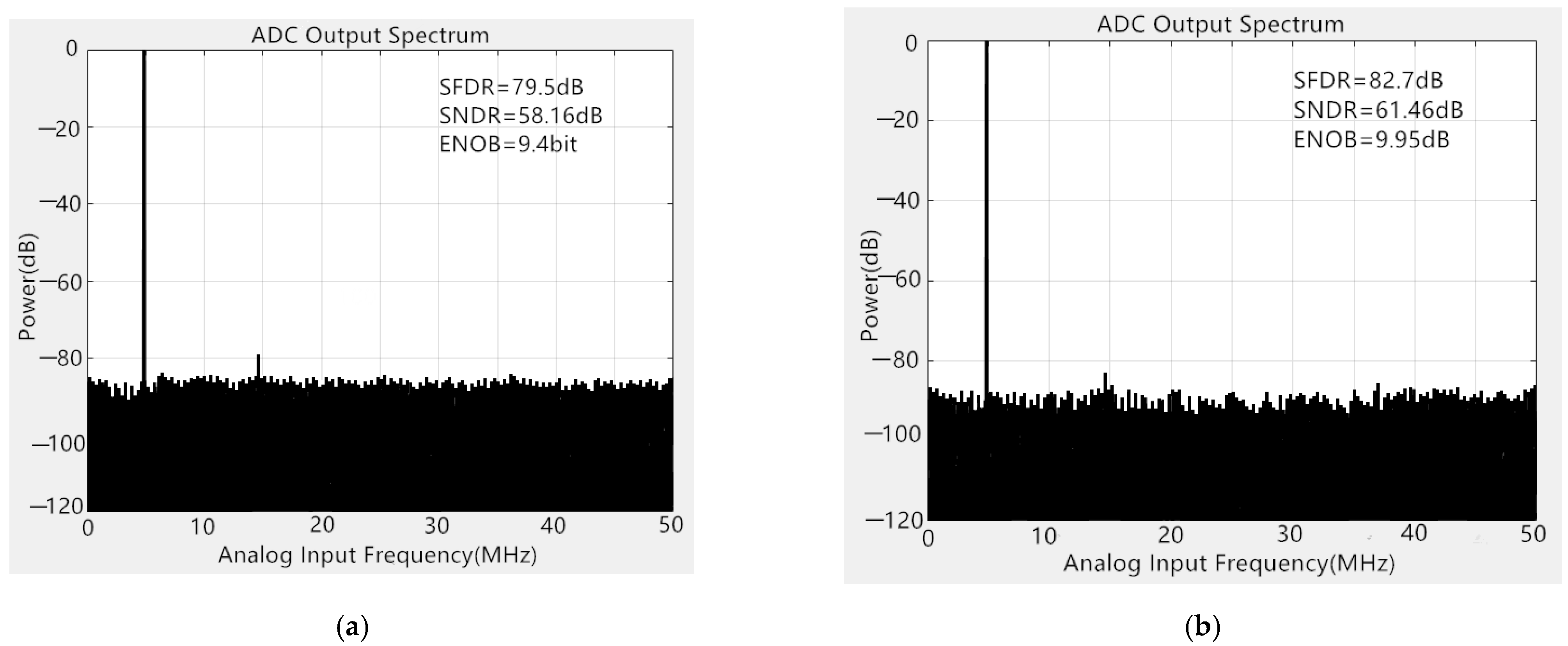

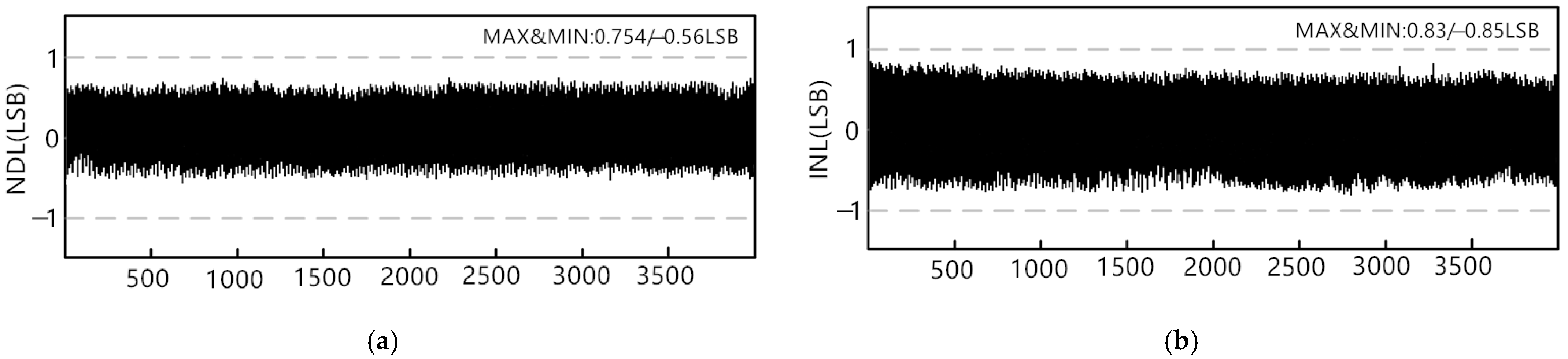

5. Measurement Results

6. Conclusions

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

References

- Liu, C.-C.; Huang, M.-C.; Tu, Y.-H. A 12 bit 100 MS/s SAR-Assisted Digital-Slope ADC. IEEE J. Solid-State Circuits 2016, 51, 2941–2950. [Google Scholar] [CrossRef]

- Tseng, W.; Lee, W.; Huang, C.; Chiu, P. A 12-bit 104 MS/s SAR ADC in 28 nm CMOS for Digitally-Assisted Wireless Transmitters. IEEE J. Solid-State Circuits 2016, 51, 2222–2231. [Google Scholar] [CrossRef]

- Luu, D.; Kull, L.; Toifl, T.; Menolfi, C.; Brandli, M.; Francese, P.A.; Morf, T.; Kossel, M.; Yueksel, H.; Cevrero, A.; et al. A 12-bit 300-MS/s SAR ADC With Inverter-Based Preamplifier and Common-Mode-Regulation DAC in 14-nm CMOS FinFET. IEEE J. Solid-State Circuits 2018, 53, 3268–3279. [Google Scholar] [CrossRef]

- Li, M.; Chen, Y.; Ye, F.; Ren, J. A 100MS/S 12-bit Coarse-Fine SAR ADC with Shared Split-CDAC. In Proceedings of the 2018 IEEE International Symposium on Circuits and Systems (ISCAS), Florence, Italy, 27–30 May 2018; pp. 1–4. [Google Scholar]

- Lan, Z.; Dong, L.; Jing, X.; Geng, L. A 12-Bit 100MS/s SAR ADC with Digital Error Correction and High-Speed LMS-Based Background Calibration. In Proceedings of the 2021 IEEE International Symposium on Circuits and Systems (ISCAS), Daegu, Korea, 22–28 May 2021; pp. 1–5. [Google Scholar]

- Wang, Q.; Zhou, L.; Peng, Z.; Li, N.; Wang, Z. A 12-b 100MS/s low-power successive approximation register ADC in 65nm COMS. In Proceedings of the 2014 IEEE International Conference on Electron Devices and Solid-State Circuits, Barcelona, Spain, 5 May 2014; pp. 1–2. [Google Scholar]

- Du, L.; Wu, S.; Jiang, M.; Ning, N.; Yu, Q.; Liu, Y. A 10-bit 100MS/s subrange SAR ADC with time-domain quantization. In Proceedings of the 2014 IEEE International Symposium on Circuits and Systems (ISCAS), Melbourne, Australia, 1–5 June 2014; pp. 301–304. [Google Scholar]

- Zheng, Y.; Lan, J.; Ye, F.; Ren, J. A 68.36 dB 12 bit 100MS/s SAR ADC with a low-noise comparator in 14-nm CMOS FinFet. In Proceedings of the 14th International Conference on ASIC (ASICON), Kunming, China, 26–29 October 2021; pp. 1–4. [Google Scholar]

- Zhang, B.; Yao, B.; Liu, L.; Wu, N. A 10-bit 100-MS/s power-efficient asynchronous SAR ADC. In Proceedings of the 13th IEEE International Conference on Solid-State and Integrated Circuit Technology (ICSICT), Hangzhou, China, 25–28 October 2016; pp. 722–724. [Google Scholar]

- Wu, S.Y.; Du, L.; Jiang, M.; Ning, N.; Yu, Q.; Liu, Y. A 10-bit 100MS/s time domain Flash-SAR ADC. In Proceedings of the 2014 IEEE International Conference on Electron Devices and Solid-State Circuits, Chengdu, China, 18–20 June 2014; pp. 1–2. [Google Scholar]

- Agnes, A.; Bonizzoni, E.; Malcovati, P.; Maloberti, F. A 9.4-ENOB 1V 3.8μW 100kS/s SAR ADC with Time-Domain Comparator. In Proceedings of the IEEE International Solid-State Circuits Conference—Digest of Technical Papers, San Francisco, CA, USA, 3–7 February 2008; pp. 246–610. [Google Scholar]

- Zhu, Y.; Chan, C.-H.; Wong, S.-S.; Seng-Pan, U.; Martins, R.P. Histogram-Based Ratio Mismatch Calibration for Bridge-DAC in 12-bit 120 MS/s SAR ADC. IEEE Trans. Very Large Scale Integr. Syst. 2016, 24, 1203–1207. [Google Scholar] [CrossRef]

- Liu, J.; Zhu, Y.; Chan, C.-H.; Sin, S.-W.; U, S.-P.; Martins, R.P.D.S. Uniform Quantization Theory-Based Linearity Calibration for Split Capacitive DAC in an SAR ADC. IEEE Trans. Very Large Scale Integr. Syst. 2016, 24, 2603–2607. [Google Scholar] [CrossRef]

- Ye, F.; Li, S.; Zhu, M.; Ni, Z.; Ren, J. A 13-bit 180-MS/s SAR ADC with Efficient Capacitor-Mismatch Estimation and Dither Enhancement. In Proceedings of the 2019 IEEE International Symposium on Circuits and Systems (ISCAS), Sapporo, Japan, 26–29 May 2019; pp. 1–4. [Google Scholar]

- Chan, K.L.; Rakuljic, N.; Galton, I. Segmented Dynamic Element Matching for High-Resolution Digital-to-Analog Con-version. IEEE Trans. Circuits Syst. I Regul. Pap. 2008, 55, 3383–3392. [Google Scholar] [CrossRef]

- Chang, S.; Zhou, X.; Ding, Z.; Li, Q. A 12-bit 30MS/s SAR ADC with VCO-Based Comparator and Split-and-Recombination Redundancy for Bypass Logic. In Proceedings of the 2019 IEEE International Symposium on Circuits and Systems (ISCAS), Sapporo, Japan, 26–29 May 2019; pp. 1–5. [Google Scholar]

- Mei, Y.; Li, S. A 10-bit 100MS/s SAR ADC for the Hadronic Calorimeter Upgrade. In Proceedings of the 2019 IEEE National Aerospace and Electronics Conference (NAECON), Dayton, OH, USA, 15–19 July 2019; pp. 59–62. [Google Scholar]

- Okazaki, T.; Kanemoto, D.; Pokharel, R.; Yoshida, K.; Kanaya, H. A design technique for a high-speed SAR ADC using non-binary search algorithm and redundancy. In Proceedings of the Asia-Pacific Microwave Conference Proceedings (APMC), Seoul, Korea, 5–8 November 2013; pp. 506–508. [Google Scholar]

- Ogawa, T.; Kobayashi, H.; Hotta, M.; Takahashi, Y.; San, H.; Takai, N. SAR ADC algorithm with redundancy. In Proceedings of the APCCAS—IEEE Asia Pacific Conference on Circuits and Systems, Macau, China, 30 November–3 December 2008; pp. 268–271. [Google Scholar]

- Verma, D.; Rikan, B.S.; Shehzad, K.; Kim, S.J.; Khan, D.; Kommangun, V.; Ali Shah, S.A.; Pu, Y.; Yoo, S.-S.; Hwang, K.C.; et al. A Design of 44.1 fJ/Conv-Step 12-Bit 80 ms/s Time Interleaved Hybrid Type SAR ADC With Redundancy Capacitor and On-Chip Time-Skew Calibration. IEEE Access 2021, 9, 133143–133155. [Google Scholar] [CrossRef]

- Lopez-Angulo, A.; Gines, A.; Peralias, E. Digital calibration of capacitor mismatch and comparison offset in Split-CDAC SAR ADCs with redundancy. In Proceedings of the 18th IEEE International New Circuits and Systems Conference (NEWCAS), Online, 16–19 June 2020; pp. 130–133. [Google Scholar]

- Bunsen, K.; Martens, E.; Dermit, D.; Craninckx, J. A Redundancy-Based Background Calibration for Comparator Off-set/Threshold and DAC Gain in a Ping-Pong SAR ADC. IEEE Trans. Circuits Syst. II Express Briefs 2021, 68, 592–596. [Google Scholar] [CrossRef]

- Guerber, J.; Gande, M.; Venkatram, H.; Waters, A.; Moon, U.-K. A 10b Ternary SAR ADC with decision time quantization based redundancy. In Proceedings of the IEEE Asian Solid-State Circuits Conference, Jeju, Korea, 14–16 November 2011; pp. 65–68. [Google Scholar] [CrossRef]

- Chang, A.H.; Lee, H.-S.; Boning, D. A 12b 50MS/s 2.1mW SAR ADC with redundancy and digital background calibration. In Proceedings of the ESSCIRC (ESSCIRC), Bucharest, Romania, 16–20 September 2013; pp. 109–112. [Google Scholar]

- Gines, A.; Lopez-Angulo, A.; Peralias, E.; Rueda, A. Description of SAR ADCs with Digital Redundancy using a Unified Hardware-Based Approach. In Proceedings of the IEEE International Symposium on Circuits and Systems (ISCAS), Florence, Italy, 27–30 May 2018; pp. 1–5. [Google Scholar]

- Li, D.; Liu, M.; Zhao, L.; Mao, H.; Ding, R.; Zhu, Z. An 8-Bit 2.1-mW 350-MS/s SAR ADC With 1.5 b/cycle Redundancy in 65-nm CMOS. IEEE Trans. Circuits Syst. II Express Briefs 2020, 67, 2307–2311. [Google Scholar] [CrossRef]

- Haenzsche, S.; Hoppner, S.; Ellguth, G.; Schuffny, R. A 12-b 4-MS/s SAR ADC With Configurable Redundancy in 28-nm CMOS Technology. IEEE Trans. Circuits Syst. II Express Briefs 2014, 61, 835–839. [Google Scholar] [CrossRef]

- Zeloufi, M.; Dzahini, D. Design of low power and low area 12-bit 40MSPS SAR ADCs with a redundancy algorithm and digital calibration for high dynamic range calorimeter readout. In Proceedings of the 2016 IEEE Nuclear Science Symposium, Medical Imaging Conference and Room-Temperature Semiconductor Detector Workshop (NSS/MIC/RTSD), Strasbourg, France, 29 October–6 November 2016; pp. 1–7. [Google Scholar]

- Kuttner, F. A 1.2V 10b 20MSample/s non-binary successive approximation ADC in 0.13 μm CMOS. In Proceedings of the International Solid-State Circuits Conference—(ISSCC), San Francisco, CA, USA, 13 February 2003; Volume 1, pp. 176–177. [Google Scholar]

- Liu, C.-C.; Chang, S.-J.; Huang, G.-Y.; Lin, Y.-Z.; Huang, C.-M.; Huang, C.-H.; Bu, L.; Tsai, C.-C. A 10b 100MS/s 1.13mW SAR ADC with binary-scaled error compensation. In Proceedings of the 2010 IEEE International Solid-State Circuits Conference—(ISSCC), San Francisco, CA, USA, 7–11 February 2010; pp. 386–387. [Google Scholar]

- Zheng, Y.; Ye, F.; Ren, J. A 13 Bit 100 MS/s SAR ADC with 74.57 dB SNDR in 14-nm CMOS FinFET. In Proceedings of the 2020 IEEE International Symposium on Circuits and Systems (ISCAS), Online, 10–21 October 2020; pp. 1–4. [Google Scholar]

- Li, M.; Yao, Y.; Hu, B.; Wei, J.; Chen, Y.; Ma, S.; Ye, F.; Ren, J. A 6.94-fJ/Conversion-Step 12-bit 100-MS/s Asynchronous SAR ADC Exploiting Split-CDAC in 65-nm CMOS. IEEE Access 2021, 9, 77545–77554. [Google Scholar] [CrossRef]

- Fiorelli, R.; Guerra, O.; Del Rio, R.; Rodriguez-Vazquez, A. Effects of capacitors non-idealities in un-even split-capacitor array SAR ADCs. In Proceedings of the 2015 Conference on Design of Circuits and Integrated Systems (DCIS), Estoril, Portugal, 25–27 November 2015; pp. 1–4. [Google Scholar]

- Liu, C.-C.; Kuo, C.-H.; Lin, Y.-Z. A 10 bit 320 MS/s Low-Cost SAR ADC for IEEE 802.11ac Applications in 20 nm CMOS. IEEE J. Solid-State Circuits 2015, 50, 2645–2654. [Google Scholar] [CrossRef]

- Yang, J.; Naing, T.L.; Brodersen, R.W. A 1 GS/s 6 Bit 6.7 mW Successive Approximation ADC Using Asynchronous Processing. IEEE J. Solid-State Circuits 2010, 45, 1469–1478. [Google Scholar] [CrossRef]

- Chan, C.-H.; Zhu, Y.; Li, C.; Zhang, W.-H.; Ho, I.-M.; Wei, L.; U, S.-P.; Martins, R.P. 60-dB SNDR 100-MS/s SAR ADCs With Threshold Reconfigurable Reference Error Calibration. IEEE J. Solid-State Circuits 2017, 52, 2576–2588. [Google Scholar] [CrossRef]

- Roh, Y.-J.; Chang, D.-J.; Ryu, S.-T. A 40-nm CMOS 12b 120-MS/s Nonbinary SAR-Assisted SAR ADC With Double Clock-Rate Coarse Decision. IEEE Trans. Circuits Syst. II Express Briefs 2020, 67, 2833–2837. [Google Scholar] [CrossRef]

- Chang, K.-H.; Hsieh, C.-C. A 12 bit 150 MS/s 1.5 mW SAR ADC with adaptive radix DAC in 40 nm CMOS. In Proceedings of the IEEE Asian Solid-State Circuits Conference (A-SSCC), Toyama, Japan, 7–9 November 2016; pp. 157–160. [Google Scholar]

- Zheng, Y.; Lan, J.; Ye, F.; Ren, J. A 12-bit 100MS/s SAR ADC With Equivalent Split-Capacitor and LSB-Averaging in 14-nm CMOS FinFET. IEEE Access 2021, 9, 169107–169121. [Google Scholar] [CrossRef]

- Verma, D.; Shehzad, K.; Khan, D.; Kim, S.J.; Pu, Y.G.; Yoo, S.-S.; Hwang, K.C.; Yang, Y.; Lee, K.-Y. A Design of Low-Power 10-bit 1-MS/s Asynchronous SAR ADC for DSRC Application. Electronics 2020, 9, 1100. [Google Scholar] [CrossRef]

| Recombination [6] | Proposed Hybrid Method | |||

|---|---|---|---|---|

| 14 bit Cycles to Convert 13 bit | 16 bit Cycles to Convert 13 bit | |||

| Number of bit Cycling | bit Weighting | Redundancy Range (LSB) | bit Weighting | Redundancy Range (LSB) |

| 1 | 1792 | 512 | 1792 | 532 |

| 2 | 1024 | 256 | 1024 | 276 |

| 3 | 512 | 256 | 512 | 276 |

| 4 | 320 | 128 | 320 | 148 |

| 5 | 192 | 64 | 192 | 84 |

| 6 | 128 | 0 | 96 | 84 |

| 7 | 64 | 0 | 64 | 52 |

| 8 | 32 | 0 | 32 | 52 |

| 9 | 14 | 4 | 32 | 20 |

| 10 | 8 | 2 | 16 | 20 |

| 11 | 4 | 2 | 16 | 4 |

| 12 | 2 | 2 | 8 | 4 |

| 13 | 2 | 0 | 4 | 4 |

| 14 | 1 | 0 | 4 | 0 |

| 15 | 2 | 0 | ||

| 16 | 1 | 0 | ||

| This Work | [34] | [36] | [37] | [38] | [39] | ||

|---|---|---|---|---|---|---|---|

| Architecture | SAR | SAR | SAR | SAR | SAR | SAR | |

| CMOS technology | 28 nm | 20 nm | 65 nm | 40 nm | 40 nm | 14 | |

| Resolution (bits) | 12 | 10 | 11 | 12 | 12 | 12 | |

| Supply Voltage (V) | 0.9 | 1 | 1.2 | 1 | 0.9 | 0.8 | |

| Sampling Rates (MS/s) | 100 | 320 | 100 | 120 | 150 | 100 | |

| SNDR (dB) | @LF | 61.46 | 57.1 | 60 | 60.33 | 61.7 | 61.29 |

| @Nyquist | 58.82 | 50.9 | 58.8 | 58.1 | 56.2 | 58.34 | |

| SFDR (dB) | @LF | 82.7 | 78.1 | 74 | 72.9 | 74.4 | 82.08 |

| @Nyquist | 79.1 | 58.6 | 74.61 | 72 | 63.5 | 78.02 | |

| ENOB (bit) | @LF | 9.95 | 9.2 | 9.67 | 9.72 | 9.95 | 9.89 |

| @Nyquist | 9.51 | 8.16 | 9.51 | 9.35 | 9.0 | 9.40 | |

| Power (mW) | 0.86 | 1.52 | 1.6 | 1.9 | 1.5 | 0.78 | |

| FOM (fJ/conv-step) | @LF | 8.69 | 8.1 | 19.2 | 18.7 | 10.3 | 8.2 |

| @Nyquist | 11.8 | 16.5 | 21.9 | 24.26 | 18.5 | 11.15 | |

| Area (mm2) | 0.00227 | 0.0012 | 0.011 | 0.0128 | 0.04 | 0.112 | |

| DNL (LSB) | 0.754/−0.56 | 0.41/−0.34 | 1.05/−0.842 | 0.96/−0.93 | 1.77/−0.91 | — | |

| INL (LSB) | 0.83/−0.85 | 0.28/−0.43 | 1.28/−0.972 | 1.6/−1.08 | 2.95/−2.63 | — | |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2022 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Zheng, Y.; Ye, F.; Ren, J. A 12-Bit, 100 MS/s SAR ADC Based on a Bridge Capacitor Array with Redundancy and Non-Linearity Calibration in 28 nm CMOS. Electronics 2022, 11, 705. https://doi.org/10.3390/electronics11050705

Zheng Y, Ye F, Ren J. A 12-Bit, 100 MS/s SAR ADC Based on a Bridge Capacitor Array with Redundancy and Non-Linearity Calibration in 28 nm CMOS. Electronics. 2022; 11(5):705. https://doi.org/10.3390/electronics11050705

Chicago/Turabian StyleZheng, Yan, Fan Ye, and Junyan Ren. 2022. "A 12-Bit, 100 MS/s SAR ADC Based on a Bridge Capacitor Array with Redundancy and Non-Linearity Calibration in 28 nm CMOS" Electronics 11, no. 5: 705. https://doi.org/10.3390/electronics11050705