A Simple Commutation Method and a Cost-Effective Clamping Circuit for Three-to-Five-Phase Indirect-Matrix Converters

Abstract

:1. Introduction

2. Five-Phase Indirect-Matrix Converter

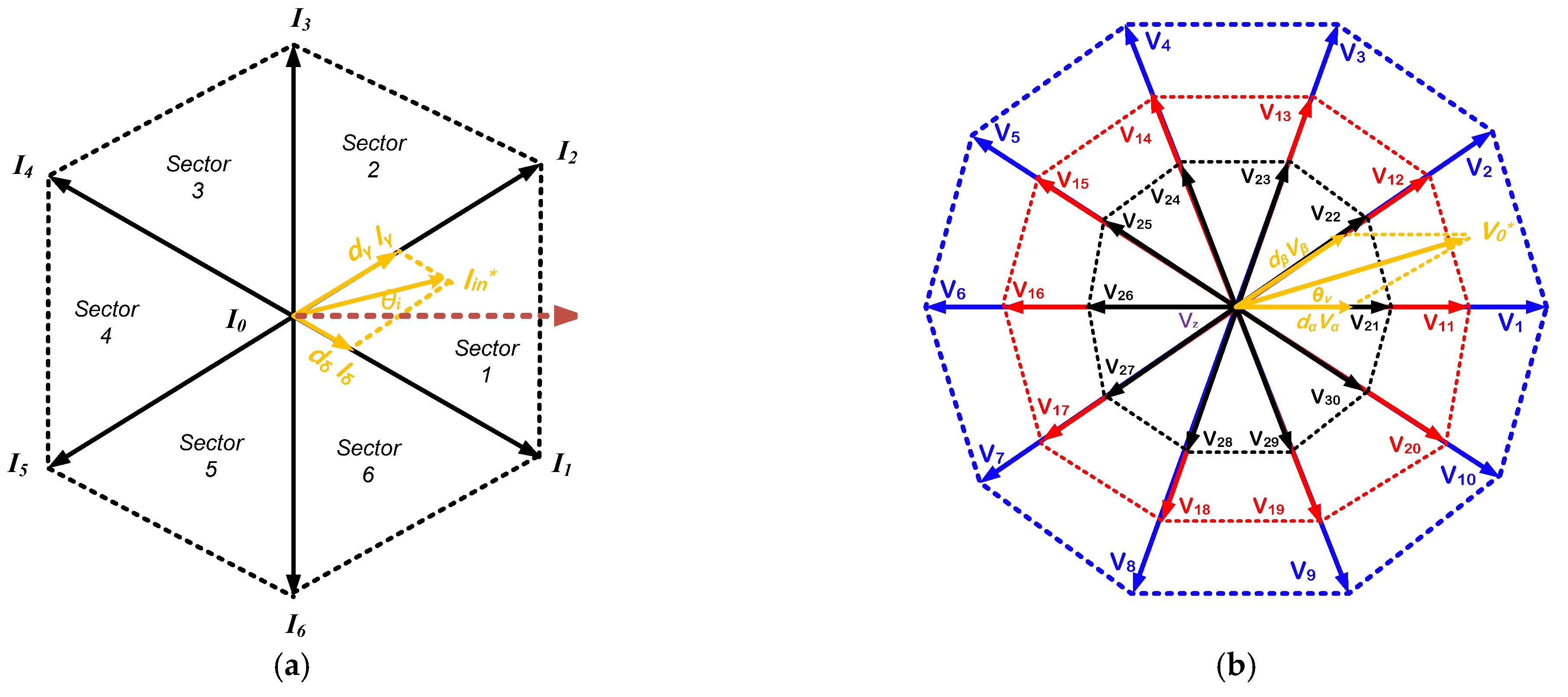

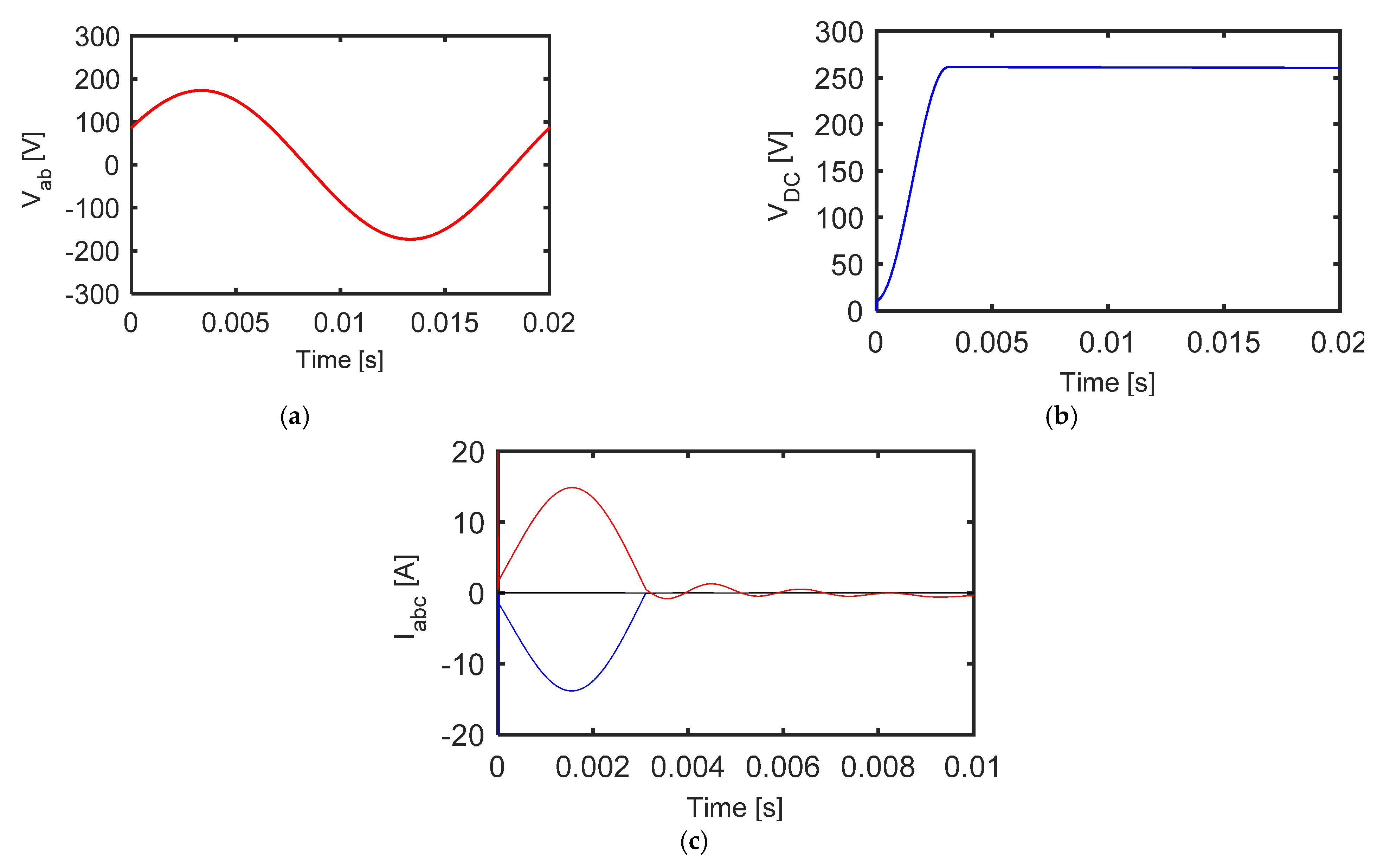

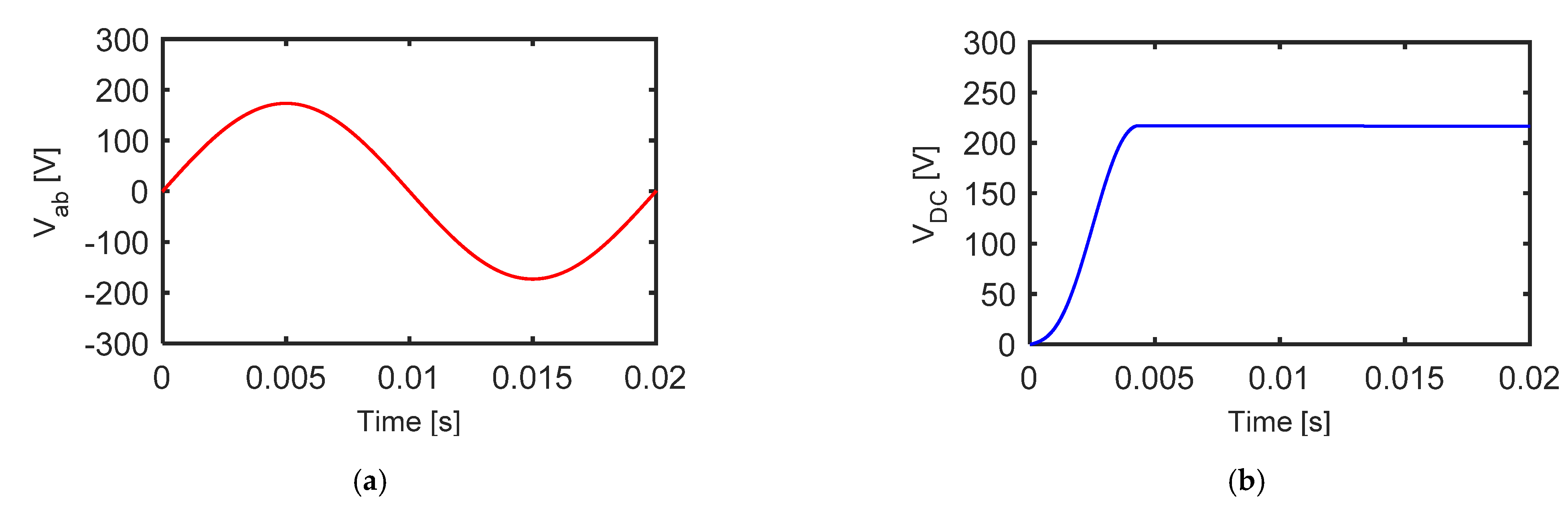

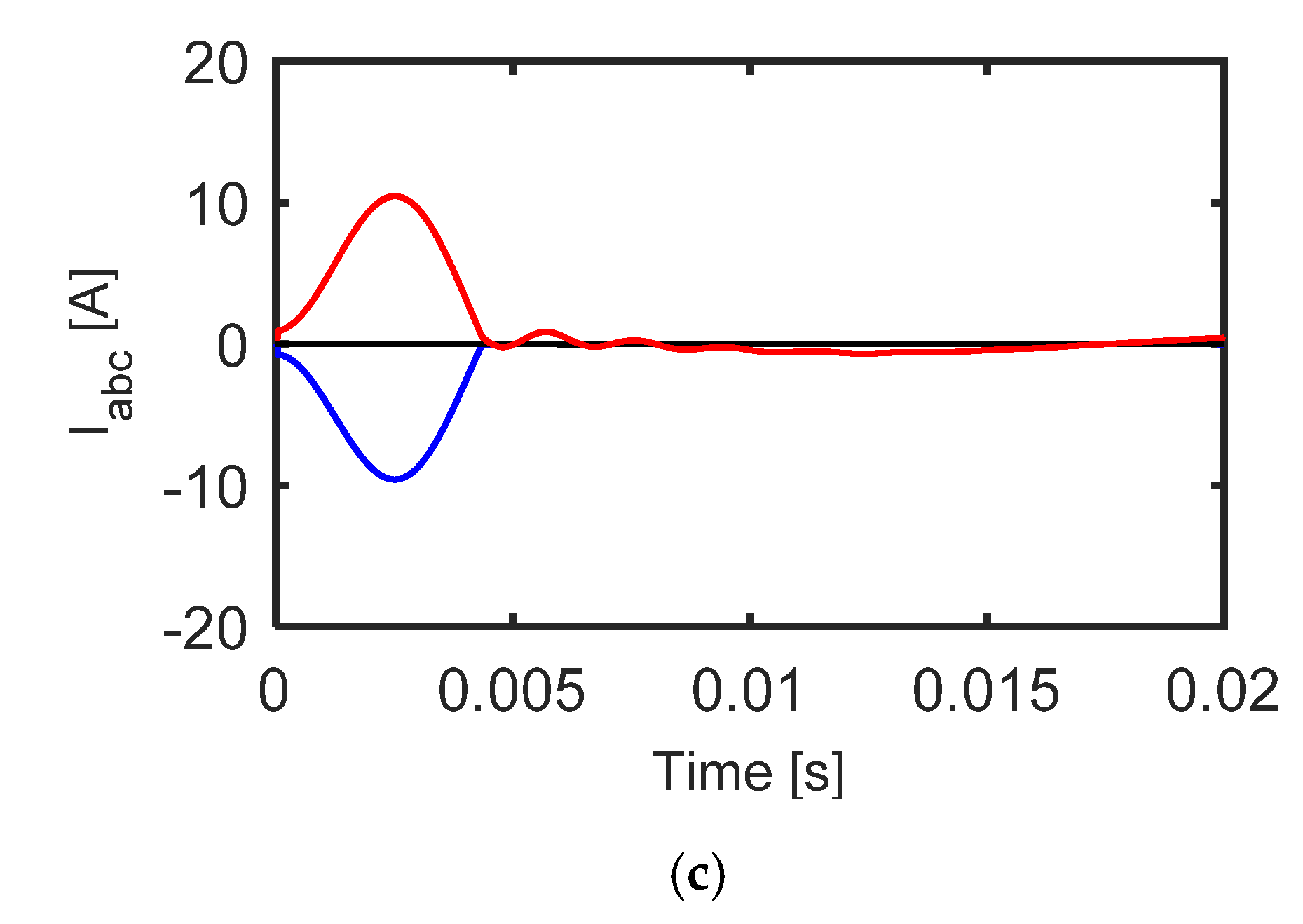

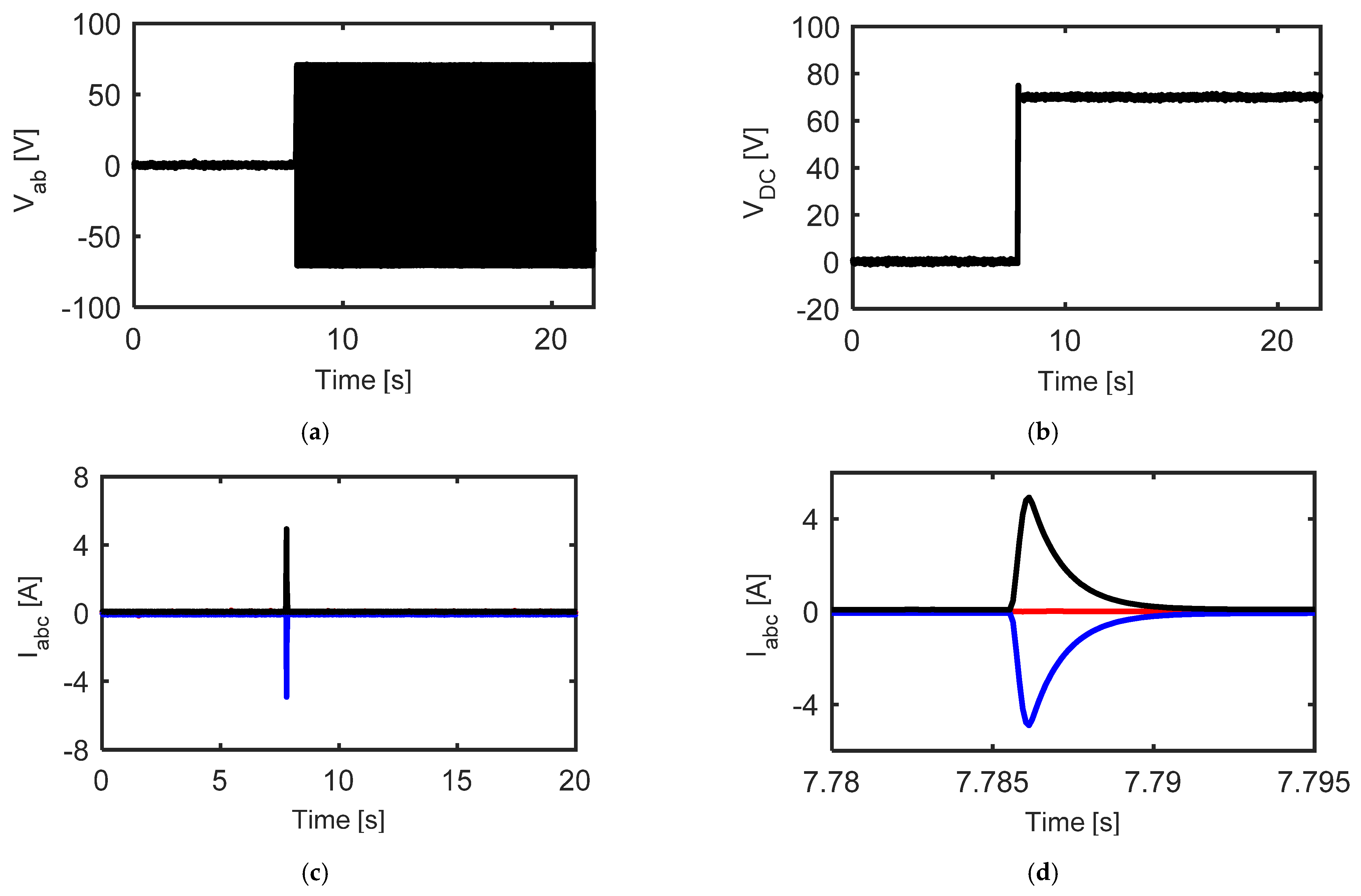

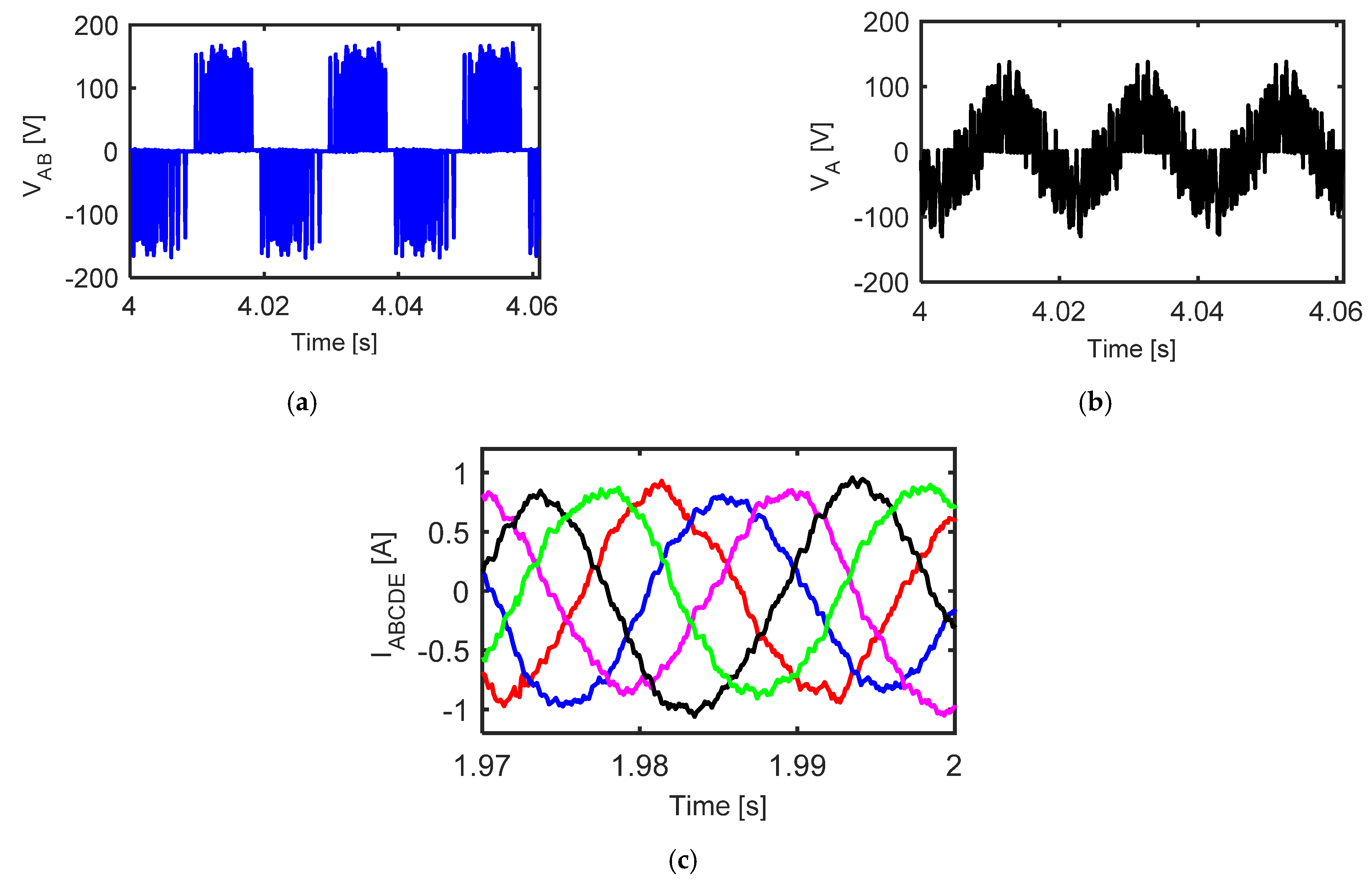

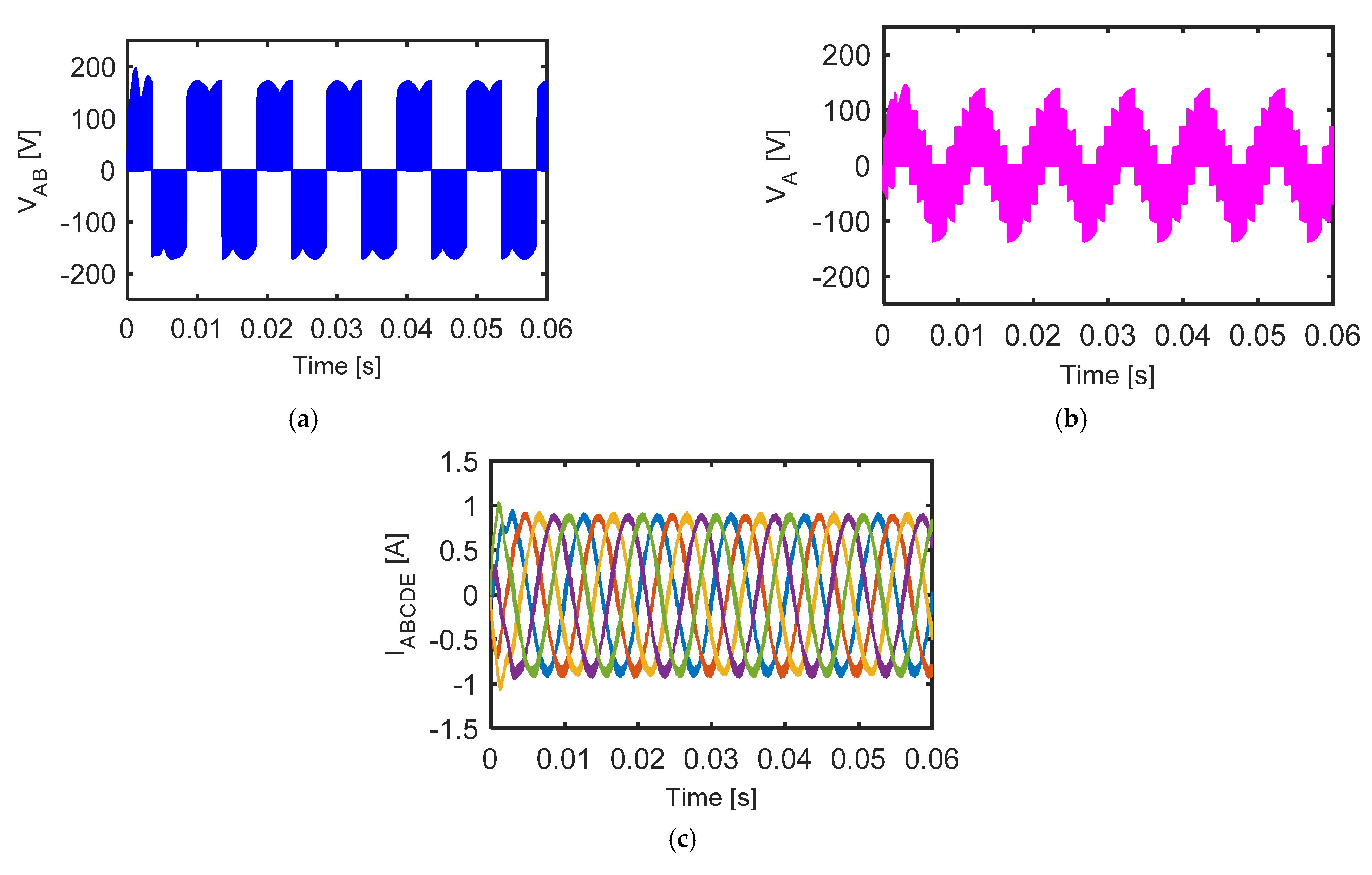

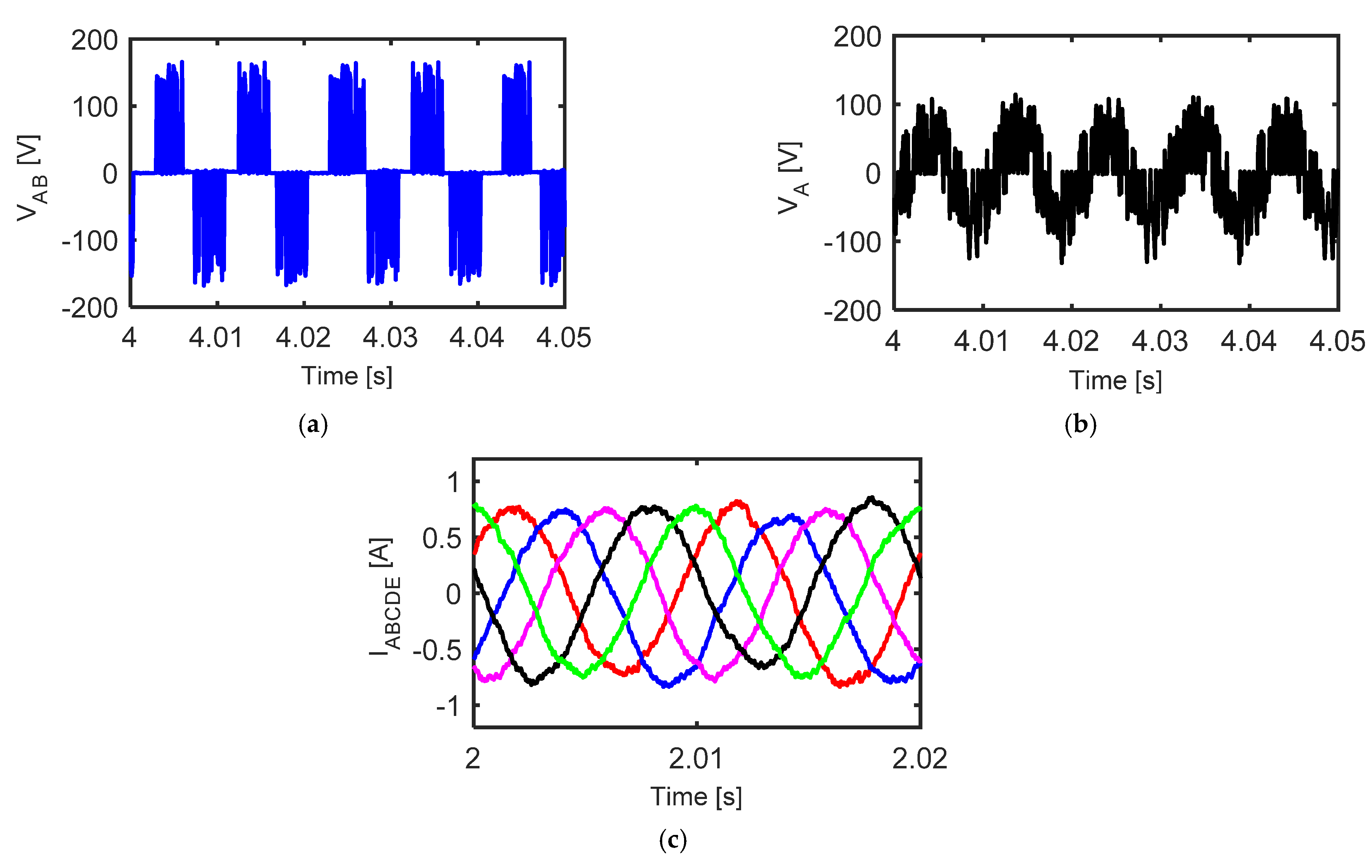

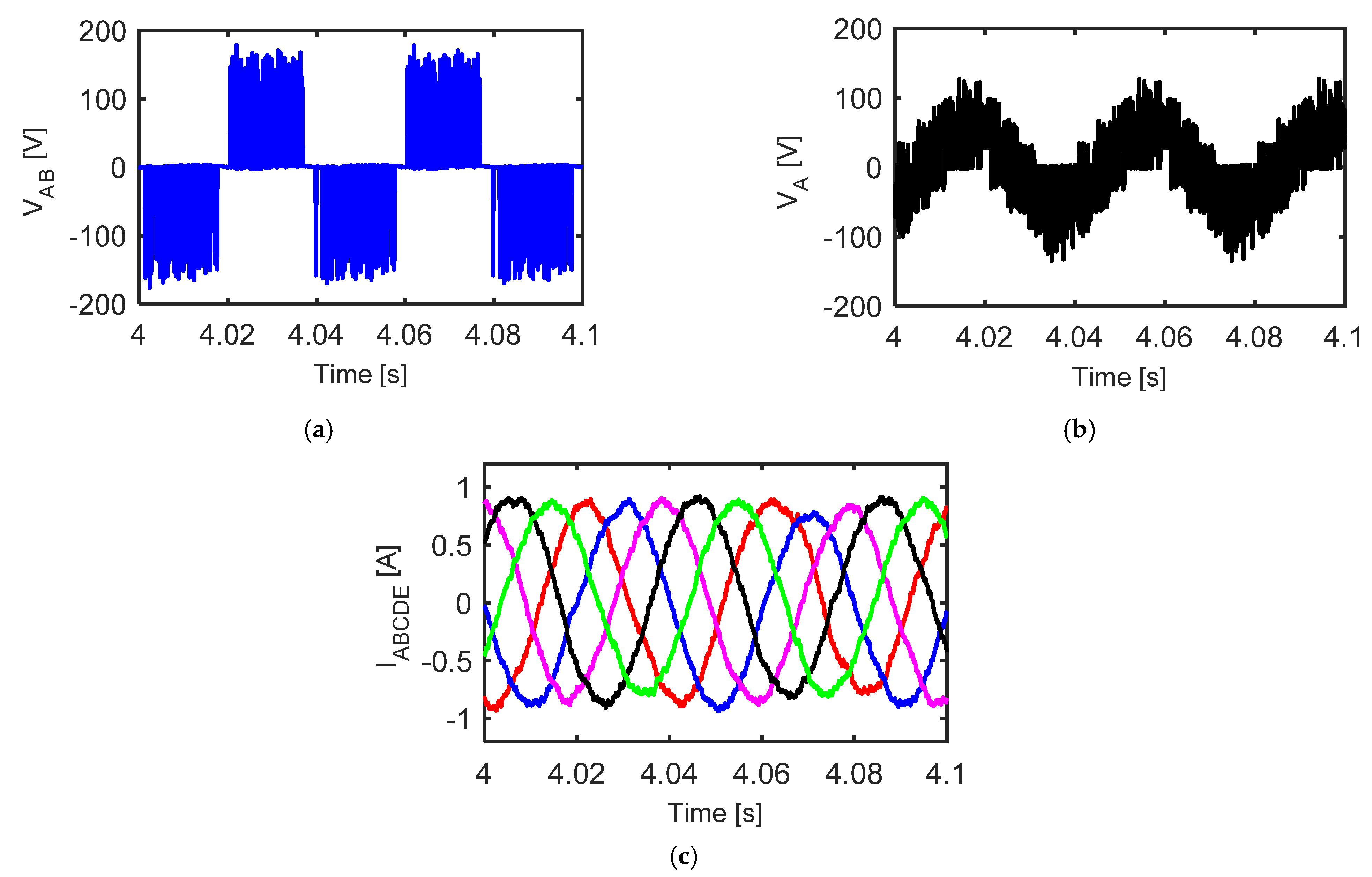

2.1. Indirect Space Vector Modulation

2.1.1. Current-Source Rectifier

2.1.2. Five-Phase Voltage-Source Inverter

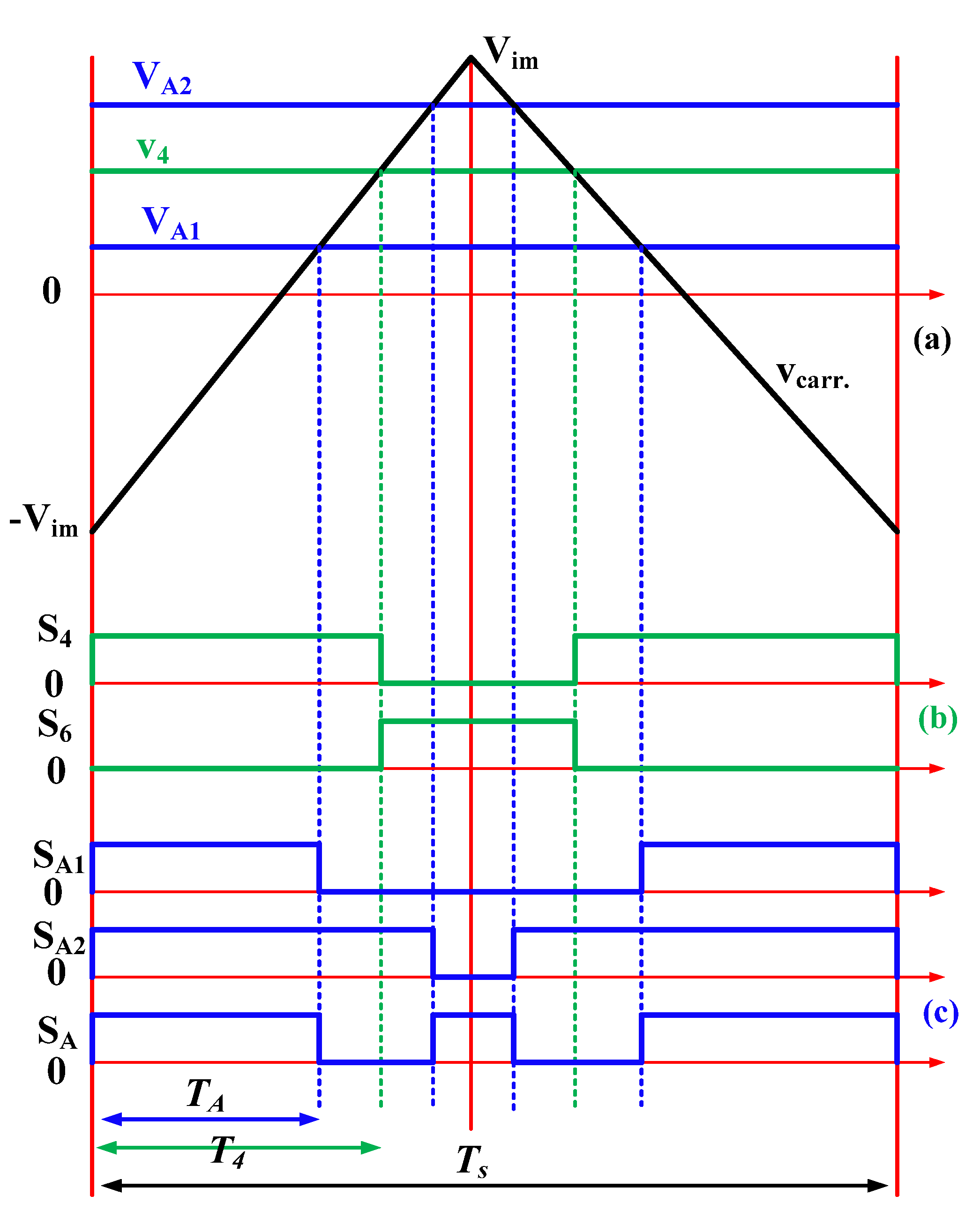

2.2. Carrier-Based Pulse Width Modulation

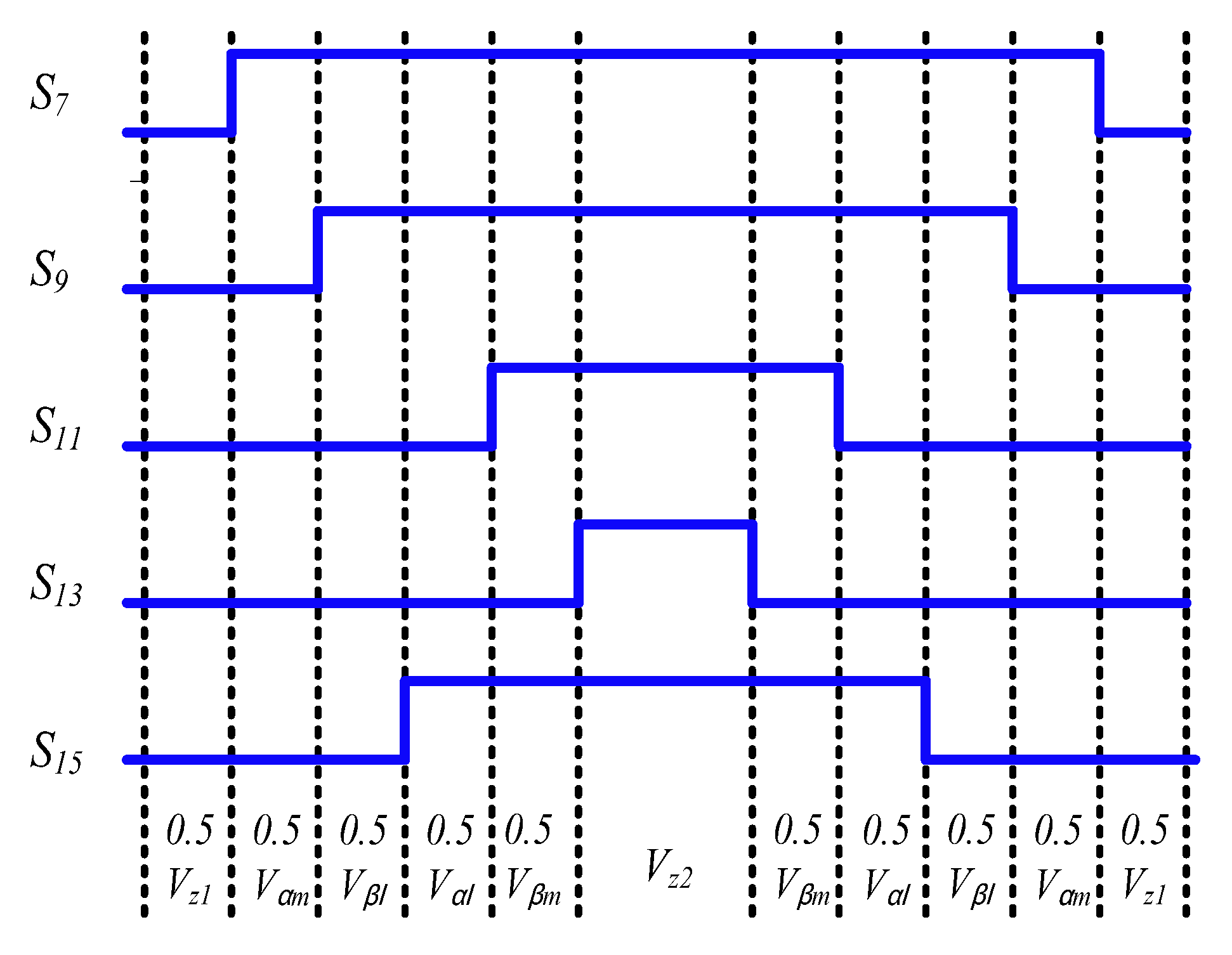

2.2.1. Current-Source Rectifier

2.2.2. Five-Phase Inverter

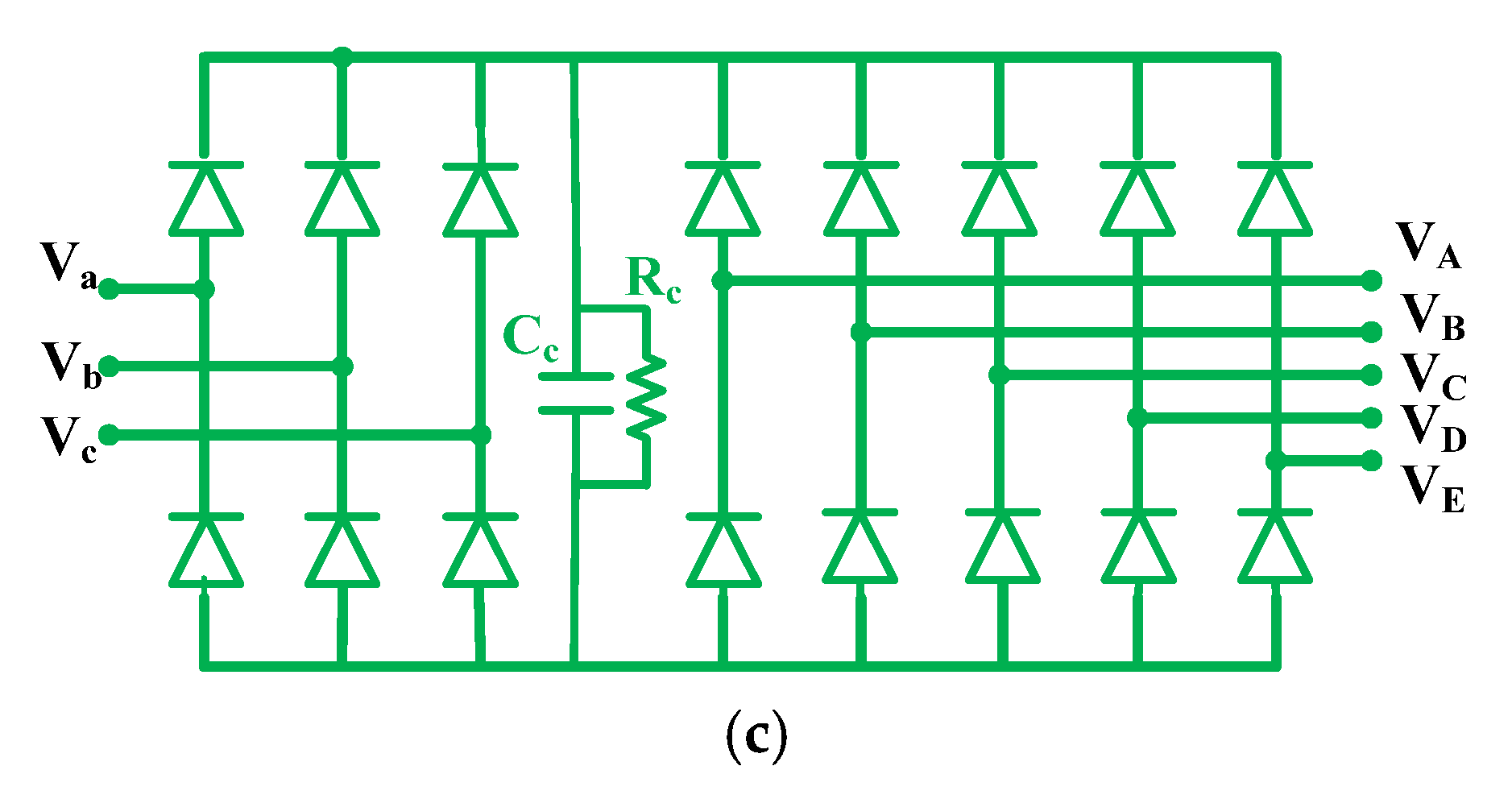

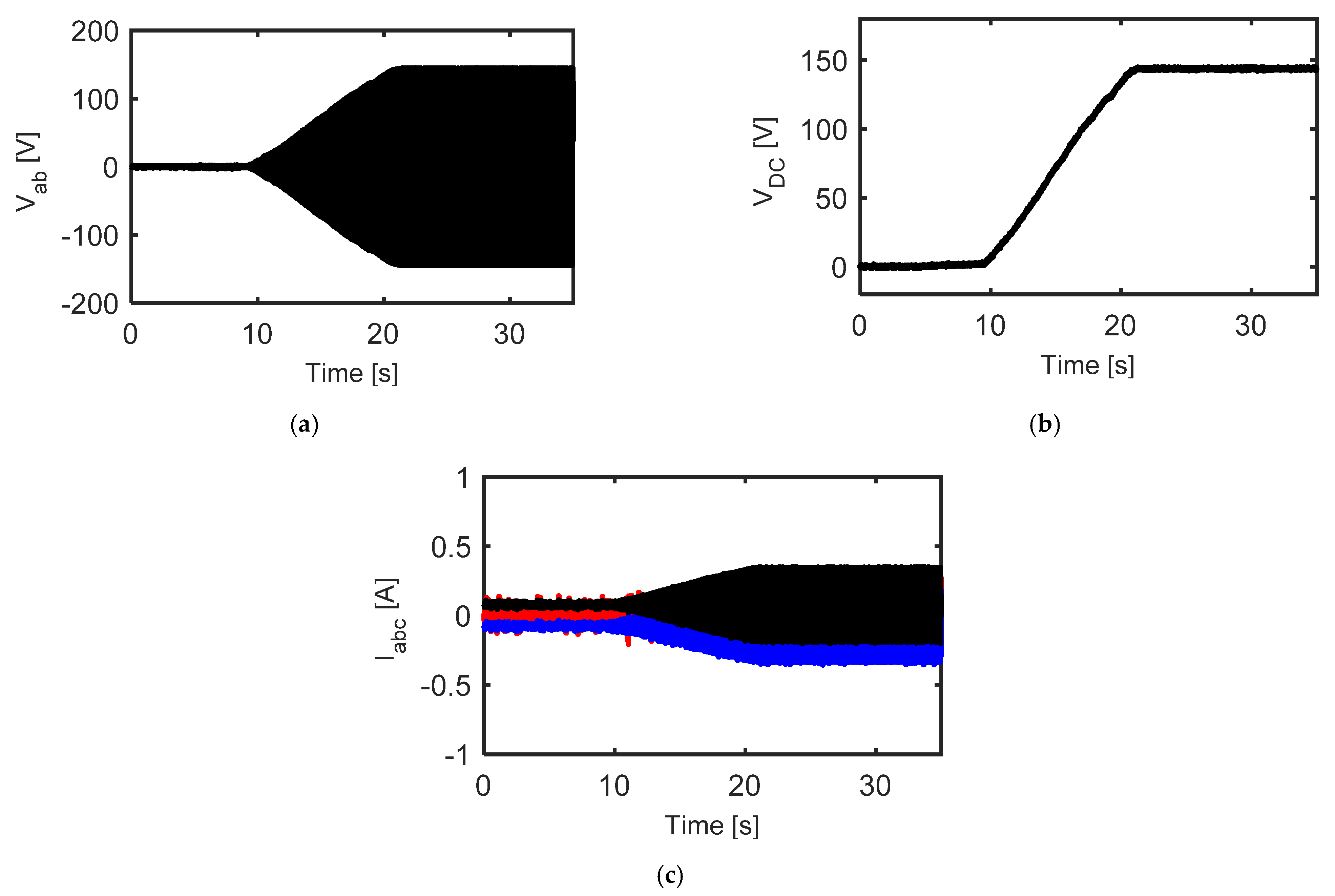

3. Clamping Circuit and Input Filter

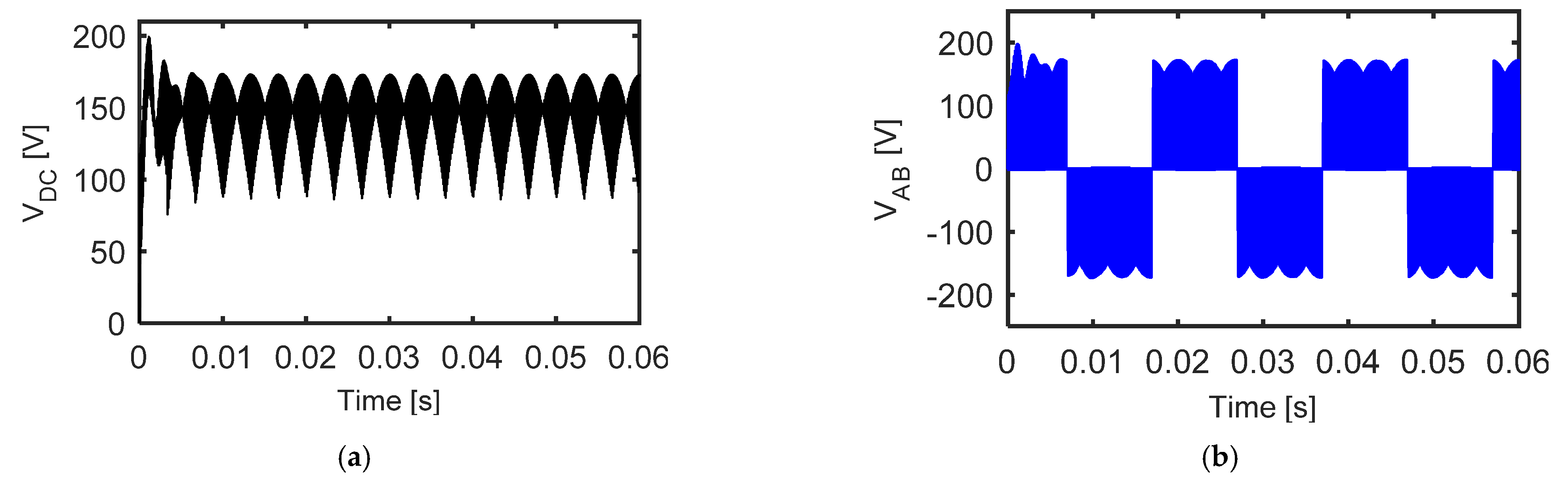

3.1. Analysis of Clamping Circuit

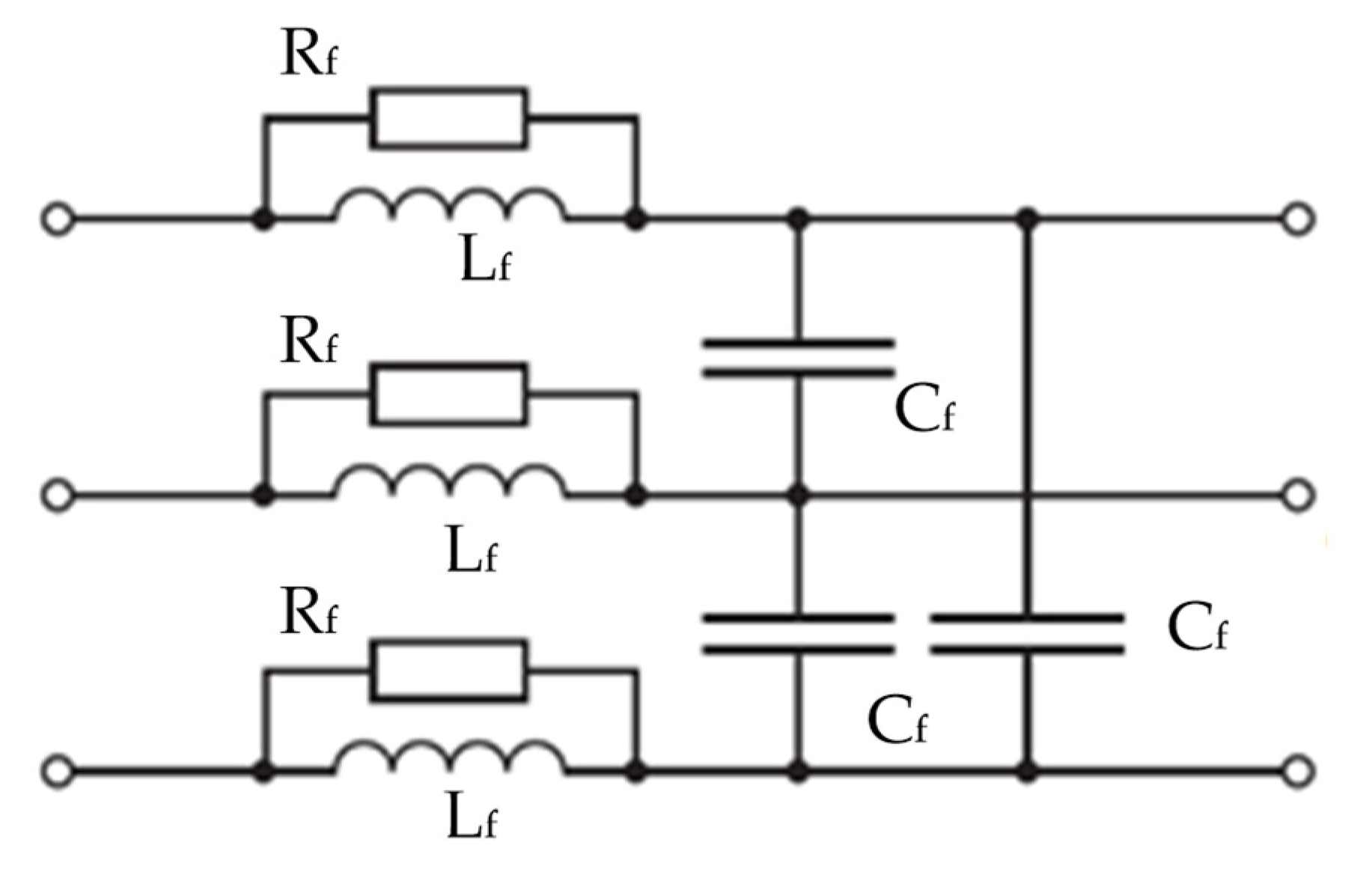

3.2. Low-Pass Input Filter

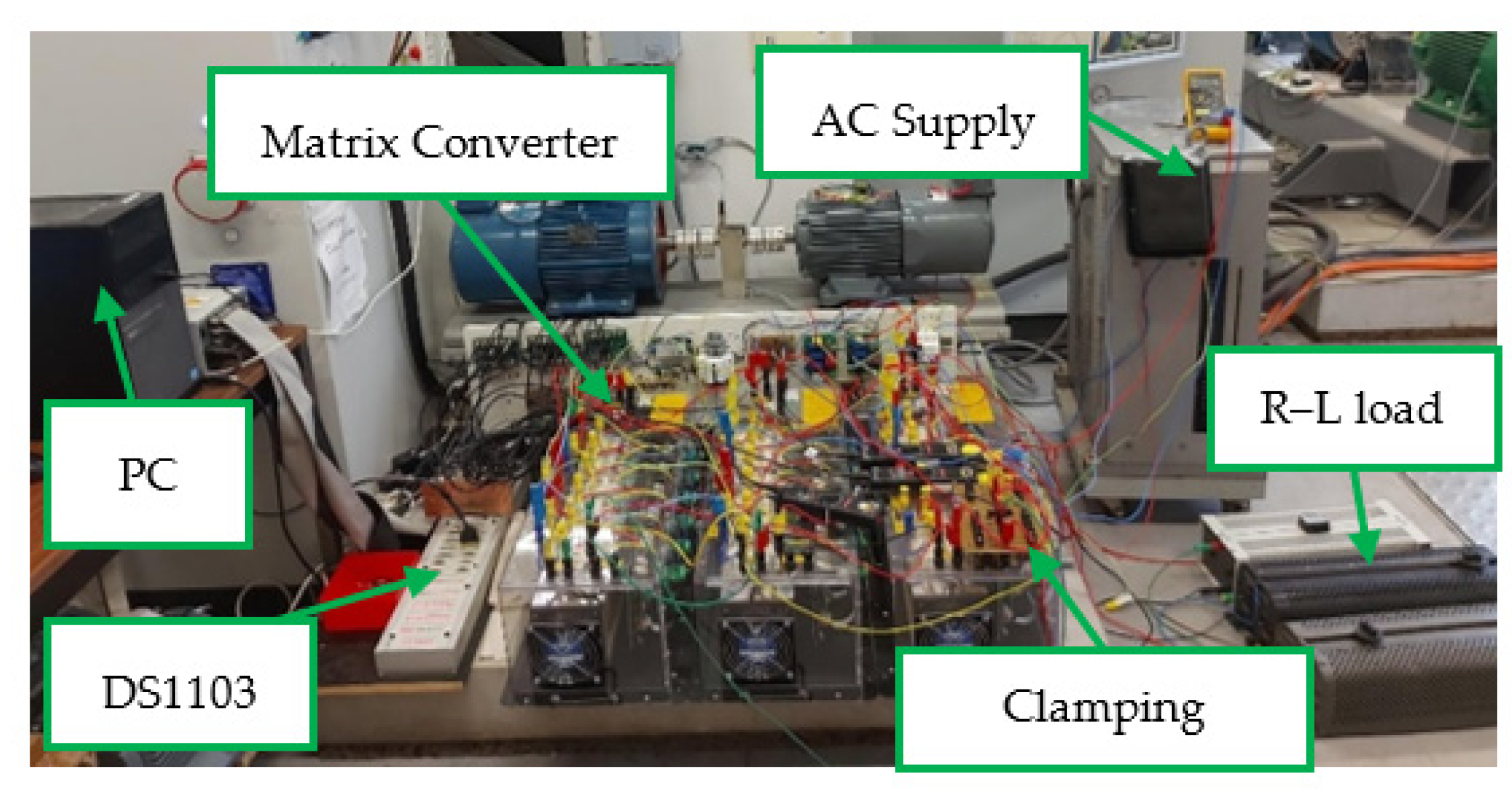

4. Results and Discussion

5. Conclusions

Author Contributions

Funding

Conflicts of Interest

References

- Vancini, L.; Mengoni, M.; Rizzoli, G.; Sala, G.; Zarri, L.; Tani, A. Carrier-Based PWM Overmodulation Strategies for Five-Phase Inverters. IEEE Trans. Power Electron. 2021, 36, 6988–6999. [Google Scholar] [CrossRef]

- Tawfiq, K.B.; Ibrahim, M.N.; El-Kholy, E.E.; Sergeant, P. Construction of Synchronous Reluctance Machines with Combined Star-Pentagon Configuration Using Standard Three-Phase Stator Frames. IEEE Trans. Ind. Electron. 2021. [Google Scholar] [CrossRef]

- Wang, K.; Gu, Z.Y.; Liu, C.; Zhu, Z.Q. Design and Analysis of a Five-Phase SPM Machine Considering Third Harmonic Current Injection. IEEE Trans. Energy Convers. 2018, 33, 1108–1117. [Google Scholar] [CrossRef]

- Tawfiq, K.B.; Ibrahim, M.N.; El-Kholy, E.E.; Sergeant, P. Comparative Analysis of Refurbishing Methods of Three-phase Synchronous Reluctance Machines to Five-phase with Minimum Cost. IEEE Trans. Ind. Appl. 2021, 57, 6007–6022. [Google Scholar] [CrossRef]

- Kong, W.; Kang, M.; Li, D.; Qu, R.; Jiang, D.; Gan, C. Investigation of spatial harmonic magnetic field coupling effect on torque ripple for multiphase induction motor under open fault condition. IEEE Trans. Power Electron. 2017, 33, 6060–6071. [Google Scholar] [CrossRef]

- Levi, E.; Jones, M.; Vukosavic, S.N.; Toliyat, H.A. A novel concept of a multiphase, multimotor vector-controlled drive system supplied from a single voltage source inverter. IEEE Trans. Power Electron. 2004, 19, 320–335. [Google Scholar] [CrossRef]

- Li, L.; Lee, K.; Bai, K.; Ouyang, X.; Yang, H. Inverse models and harmonics compensation for suppressing torque ripples of multiphase permanent magnet motor. IEEE Trans. Ind. Electron. 2018, 65, 8730–8739. [Google Scholar] [CrossRef]

- Mengoni, M.; Zarri, L.; Tani, A.; Parsa, L.; Serra, G.; Casadei, D. High torque-density control of multiphase induction motor drives operating over a wide speed range. IEEE Trans. Ind. Electron. 2015, 62, 814–825. [Google Scholar] [CrossRef]

- Kolar, J.W.; Friedli, T.; Rodriguez, J.; Wheeler, P.W. Review of three phase PWM AC–AC converter topologies. IEEE Trans. Ind. Electron. 2011, 58, 4988–5006. [Google Scholar] [CrossRef]

- Tran, Q.; Lee, H. A Three-Vector Modulation Strategy for Indirect Matrix Converter Fed Open-End Load to Reduce Common-Mode Voltage with Improved Output Performance. IEEE Trans. Power Electron. 2017, 32, 7904–7915. [Google Scholar] [CrossRef]

- Nguyen, T.D.; Lee, H. Development of a Three-to-Five-Phase Indirect Matrix Converter with Carrier-Based PWM Based on Space-Vector Modulation Analysis. IEEE Trans. Ind. Electron. 2016, 63, 13–24. [Google Scholar] [CrossRef]

- Tran, Q.; Lee, H. An Advanced Modulation Strategy for Three-to-Five-Phase Indirect Matrix Converters to Reduce Common-Mode Voltage with Enhanced Output Performance. IEEE Trans. Ind. Electron. 2018, 65, 5282–5291. [Google Scholar] [CrossRef]

- Nguyen, T.D.; Lee, H. A New SVM Method for an Indirect Matrix Converter with Common-Mode Voltage Reduction. IEEE Trans. Ind. Inform. 2014, 10, 61–72. [Google Scholar] [CrossRef]

- Nguyen, T.D.; Lee, H. Dual Three-Phase Indirect Matrix Converter with Carrier-Based PWM Method. IEEE Trans. Power Electron. 2014, 29, 569–581. [Google Scholar] [CrossRef]

- Tran, Q.H.; Nguyen, T.D.; Phuong, L.M. Simplified Space-Vector Modulation Strategy for Indirect Matrix Converter with Common-Mode Voltage and Harmonic Distortion Reduction. IEEE Access 2020, 8, 218489–218498. [Google Scholar] [CrossRef]

- Kolar, J.W.; Schafmeister, F.; Round, S.D.; Ertl, H. Novel three-phase AC–AC sparse matrix converters. IEEE Trans. Power Electron. 2007, 22, 1649–1661. [Google Scholar] [CrossRef]

- Wang, B.; Sherif, E. Spectral analysis of matrix converters based on 3-D fourier integral. IEEE Trans. Power Electron. 2013, 28, 19–25. [Google Scholar] [CrossRef]

- Rivera, M.; Rojas, C.; Rodríguez, J.; Wheeler, P.; Wu, B.; Espinoza, J.R. Predictive current control with input filter resonance mitigation for a direct matrix converter. IEEE Trans. Power Electron. 2011, 26, 2794–2803. [Google Scholar] [CrossRef]

- Jayaprakasan, S.; Ashok, S.; Ramchand, R. Analysis of Current Error Space Phasor for a Space Vector Modulated Indirect Matrix Converter. IEEE Trans. Ind. Electron. 2022, 69, 4451–4459. [Google Scholar] [CrossRef]

- Liu, X.; Loh, P.C.; Wang, P.; Han, X. Improved modulation schemes for indirect Z-source matrix converter with sinusoidal input and output waveforms. IEEE Trans. Power Electron. 2012, 27, 4039–4050. [Google Scholar] [CrossRef]

- Park, K.; Lee, K.-B.; Blaabjerg, F. Improving output performance of a Z-source sparse matrix converter under unbalanced input-voltage conditions. IEEE Trans. Power Electron. 2012, 27, 2043–2054. [Google Scholar] [CrossRef]

- Friedli, T.; Round, S.D.; Kolar, J.W. A 100 kHz SiC sparse matrix converter. In Proceedings of the IEEE Power Electronics Specialists Conference, Orlando, FL, USA, 17–21 June 2007; IEEE: New York, NY, USA, 2007; pp. 2148–2154. [Google Scholar]

- Schonberger, J.; Friedli, T.; Round, S.D.; Kolar, J.W. An ultra-sparse matrix converter with a novel active clamp circuit. In Proceedings of the Power Conversion Conference-Nagoya, Nagoya, Japan, 2–5 April 2007; IEEE: New York, NY, USA, 2007; pp. 784–791. [Google Scholar]

- Sun, Y. Indirect matrix converter-based topology and modulation schemes for enhancing input reactive power capability. IEEE Trans. Power Electron. 2015, 30, 4669–4681. [Google Scholar] [CrossRef]

- Espina, J. Reduction of output common mode voltage using a novel SVM implementation in matrix converters for improved motor lifetime. IEEE Trans. Ind. Electron. 2014, 61, 5903–5911. [Google Scholar] [CrossRef] [Green Version]

- Wei, L.; Lipo, T.L. A novel matrix converter topology with simple commutation. In Proceedings of the 36th IAS Annual Meeting, Chicago, IL, USA, 30 September–4 October 2001; IEEE: New York, NY, USA, 2001; pp. 1749–1754. [Google Scholar]

- Garcia, C. A simple current control strategy for a four-leg indirect matrix converter. IEEE Trans. Power Electron. 2015, 30, 2275–2287. [Google Scholar] [CrossRef]

- Cárdenas, R.; Juri, C.; Peña, R.; Wheeler, P.; Clare, J. The application of resonant controllers to four-leg matrix converters feeding unbalanced or nonlinear loads. IEEE Trans. Power Electron. 2012, 27, 1120–1129. [Google Scholar] [CrossRef]

- Loh, P.C.; Rong, R.; Blaabjerg, F.; Wang, P. Digital carrier modulation and sampling issues of matrix converters. IEEE Trans. Power Electron. 2009, 24, 1690–1700. [Google Scholar] [CrossRef]

- Chiang, G.T.; Itoh, J. Comparison of two overmodulation strategies in an indirect matrix converter. IEEE Trans. Ind. Electron. 2013, 60, 43–53. [Google Scholar] [CrossRef]

- Wang, B.; Venkataramanan, G. A carrier-based PWM algorithm for indirect matrix converters. In Proceedings of the 37th IEEE Power Electronics Specialists Conference, Jeju, Korea, 18–22 June 2006; IEEE: New York, NY, USA, 2006; pp. 1–8. [Google Scholar]

- Baranwal, R.; Basu, K.; Mohan, N. Carrier-based implementation of SVPWM for dual two-level VSI and dual matrix converter with zero common-mode voltage. IEEE Trans. Power Electron. 2015, 30, 1471–1487. [Google Scholar] [CrossRef]

- Nguyen, T.D.; Lee, H.-H. Carrier-based PWM technique for three-to five phase indirect matrix converters. In Proceedings of the IECON 2011—37th Annual Conference of the IEEE Industrial Electronics Society, Melbourne, VIC, Australia, 7–10 November 2011; IEEE: New York, NY, USA, 2011; pp. 3662–3667. [Google Scholar]

- Tawfiq, K.B.; Ibrahim, M.N.; El-Kholy, E.E.; Sergeant, P. An Enhanced Fault-Tolerant Control of a Five-Phase Synchronous Reluctance Motor Fed from a Three-to-Five-phase Matrix Converter. IEEE J. Emerg. Sel. Top. Power Electron. 2022. [Google Scholar] [CrossRef]

- Lee, K.B.; Blaabjerg, F. An improved DTC SVM method for sensorless matrix converter drives using an overmodulation strategy and a simple nonlinearity compensation. IEEE Trans. Ind. Electron. 2007, 54, 3155–3166. [Google Scholar] [CrossRef]

- Rebsdorf, A.; Helle, L. Variable Speed Wind Turbine Having a Matrix Converter. U.S. Patent 6,856,038, 20 May 2003. [Google Scholar]

- Nikkhajoei, H.; Iravani, M.R. A matrix converter based micro-turbine distributed generation system. IEEE Trans. Power Del. 2005, 20, 2182–2192. [Google Scholar] [CrossRef]

- Kwak, S. Indirect matrix converter drives for unity displacement factor and minimum switching losses. Electr. Power Syst. Res. 2007, 77, 447–454. [Google Scholar] [CrossRef]

- Cha, H.J.; Enjeti, P. An approach to reduce common-mode voltage in matrix converter. IEEE Trans. Ind. Appl. 2003, 39, 1151–1159. [Google Scholar]

- Lee, K.B.; Blaabjerg, F. Sensorless DTC-SVM for induction motor driven by a matrix converter using a parameter estimation strategy. IEEE Trans. Ind. Electron. 2008, 55, 512–521. [Google Scholar] [CrossRef]

- Arias, A.; Empringham, L.; Asher, G.; Wheeler, P.W.; Bland, P.M.; Apap, M.; Sumner, M.; Clare, J. Elimination of waveform distortions in matrix converters using a new dual compensation method. IEEE Trans. Ind. Electron. 2007, 54, 2079–2087. [Google Scholar] [CrossRef]

- Casadei, D.; Clare, J.; Empringham, L.; Serra, G.; Tani, A.; Trentin, A.; Wheeler, P.; Zarri, L. Large-signal model for the stability analysis of matrix converters. IEEE Trans. Ind. Electron. 2007, 54, 939–950. [Google Scholar] [CrossRef]

- Wheeler, P.; Rodriguez, J.; Clare, J.; Empringham, L.; Weinstein, A. Matrix converters: A technology review. IEEE Trans. Ind. Electron. 2002, 49, 276–288. [Google Scholar] [CrossRef]

- Klumpner, C.; Blaabjerg, F. Using reverse-blocking IGBTs in power converters for adjustable-speed drives. IEEE Trans. Ind. Appl. 2006, 42, 807–816. [Google Scholar] [CrossRef]

- Empringham, L.; de Lillo, L.; Wheeler, P.; Clare, J. Matrix converter protection for more electric aircraft applications. In Proceedings of the IECON 2006—32nd Annual Conference on IEEE Industrial Electronics, Paris, France, 6–10 November 2006; IEEE: New York, NY, USA, 2006; pp. 2564–2568. [Google Scholar]

- Klumpner, C. An indirect matrix converter with a cost-effective protection and control. In Proceedings of the 2005 European Conference on Power Electronics and Applications, Dresden, Germany, 11–14 September 2005; IEEE: New York, NY, USA, 2005. [Google Scholar]

- Shi, B.; Zhou, B. Open-circuit behavior analysis for indirect matrix converter. In Proceedings of the IECON 2017—43rd Annual Conference of the IEEE Industrial Electronics Society, Beijing, China, 29 October–1 November 2017; IEEE: New York, NY, USA, 2017; pp. 7338–7342. [Google Scholar]

- Tawfiq, K.B.; Ibrahim, M.N.; El-Kholy, E.E.; Sergeant, P. Performance Analysis of a Five-phase Synchronous Reluctance Motor Connected to Matrix Converter. In Proceedings of the 2021 IEEE International Electric Machines & Drives Conference (IEMDC), Hartford, CT, USA, 17–20 May 2021; IEEE: New York, NY, USA, 2021; pp. 1–6. [Google Scholar] [CrossRef]

- Nasir, U.; Costabeber, A.; Wheeler, P.; Rivera, M.; Clare, J. A Three-Phase Modular Isolated Matrix Converter. IEEE Trans. Power Electron. 2019, 34, 11760–11773. [Google Scholar] [CrossRef]

- Tawfiq, K.B.; Ibrahim, M.N.; Rezk, H.; El-Kholy, E.E.; Sergeant, P. Mathematical Modelling, Analysis and Control of a Three to Five-Phase Matrix Converter for Minimal Switching Losses. Mathematics 2021, 9, 96. [Google Scholar] [CrossRef]

- Nielsen, P.; Blaabjerg, F.; Pederson, J.K. Novel Solutions for Protection of Matrix Converter to Three Phase Induction Machine. In Proceedings of the IEEE IAS Conference Record, New Orleans, LA, USA, 5–9 October 1997; IEEE: New York, NY, USA, 1997; pp. 1447–1454. [Google Scholar]

| Sector Number | ON Switch | The Duty Cycles and Modulated Switches | DC-Link Voltage | |||

|---|---|---|---|---|---|---|

| 1 | ||||||

| 2 | ||||||

| 3 | ||||||

| 4 | ||||||

| 5 | ||||||

| 6 | ||||||

| Sector No. | ||||||

|---|---|---|---|---|---|---|

| 1 | V11 (10000) | V1 (11001) | V12 (11101) | V2 (11000) | ||

| 2 | V13 (01000) | V2 (11000) | V3 (11100) | V12 (11101) | ||

| 3 | V13 (01000) | V4 (01100) | V3 (11100) | V14 (11110) | ||

| 4 | V15 (00100) | V4 (01100) | V5 (01110) | V14 (11110) | ||

| 5 | V15 (00100) | V6 (00110) | V5 (01110) | V16 (01111) | V31 (00000) | V32 (11111) |

| 6 | V17 (00010) | V6 (00110) | V7 (00111) | V16 (01111) | ||

| 7 | V17 (00010) | V8 (00011) | V7 (00111) | V18 (10111) | ||

| 8 | V19 (00001) | V8 (00011) | V9 (10011) | V18 (10111) | ||

| 9 | V19 (00001) | V10 (10001) | V9 (10011) | V20 (11011) | ||

| 10 | V11 (10000) | V10 (10001) | V1 (11001) | V20 (11011) |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2022 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Tawfiq, K.B.; Ibrahim, M.N.; Sergeant, P. A Simple Commutation Method and a Cost-Effective Clamping Circuit for Three-to-Five-Phase Indirect-Matrix Converters. Electronics 2022, 11, 808. https://doi.org/10.3390/electronics11050808

Tawfiq KB, Ibrahim MN, Sergeant P. A Simple Commutation Method and a Cost-Effective Clamping Circuit for Three-to-Five-Phase Indirect-Matrix Converters. Electronics. 2022; 11(5):808. https://doi.org/10.3390/electronics11050808

Chicago/Turabian StyleTawfiq, Kotb B., Mohamed N. Ibrahim, and Peter Sergeant. 2022. "A Simple Commutation Method and a Cost-Effective Clamping Circuit for Three-to-Five-Phase Indirect-Matrix Converters" Electronics 11, no. 5: 808. https://doi.org/10.3390/electronics11050808