A High-Loop-Gain Low-Dropout Regulator with Adaptive Positive Feedback Compensation Handling 1-A Load Current

Abstract

:1. Introduction

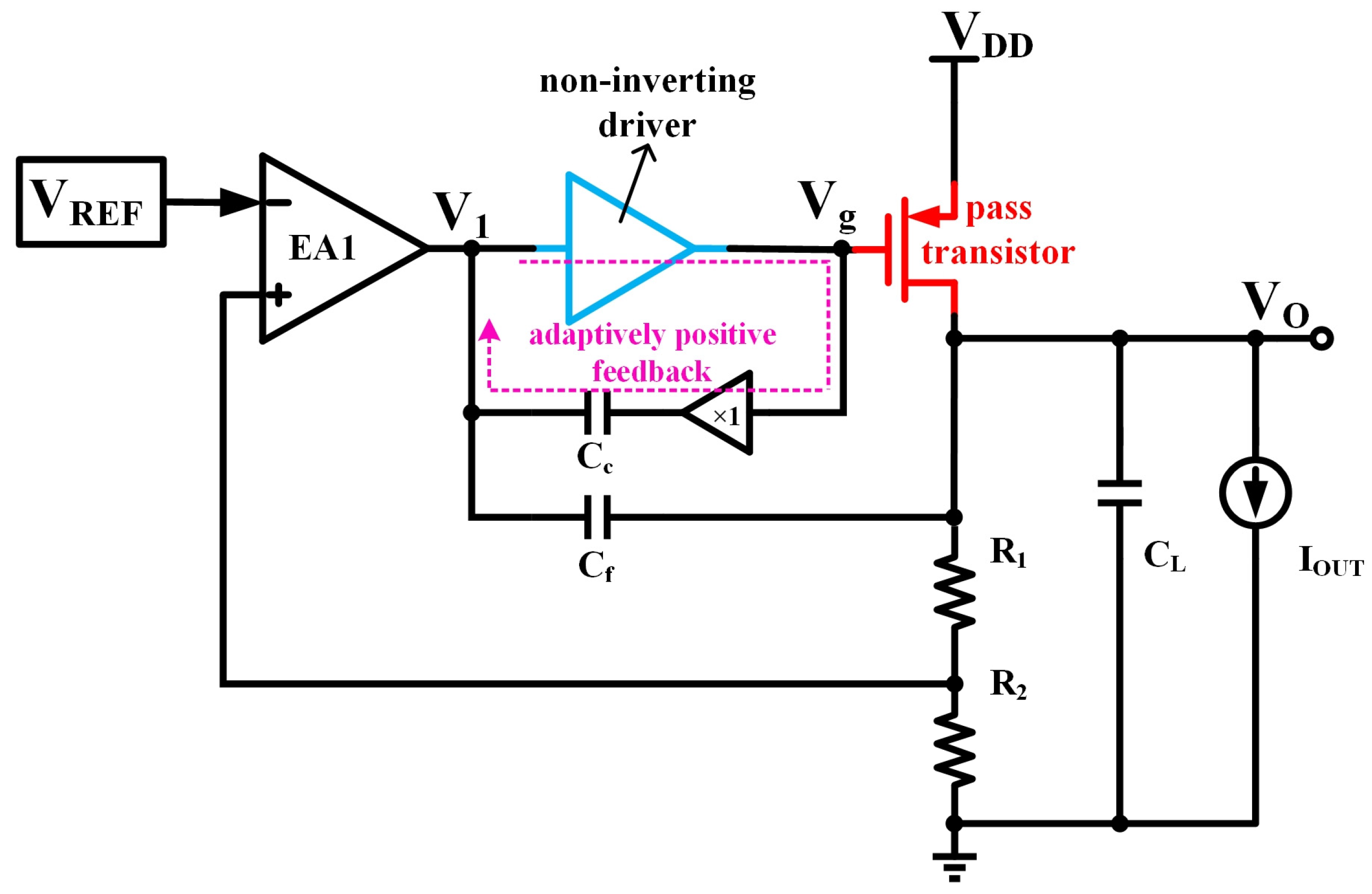

2. Proposed Structure

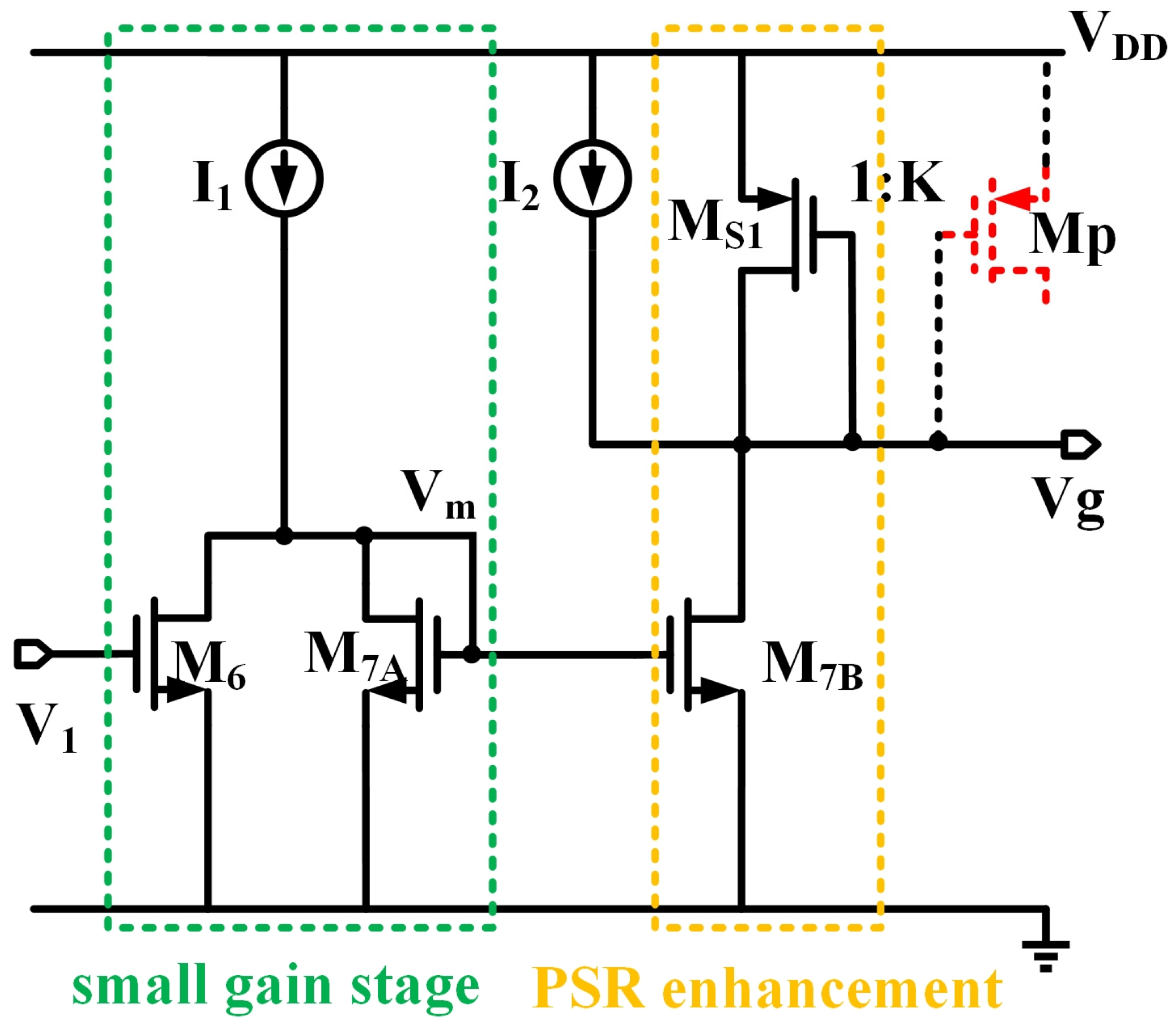

2.1. Non-Inverting Driver Stage

2.2. Adaptive Positive Feedback Compensation

- is much larger than other capacitors;

- , , are much larger than .

2.3. Circuit Design Considerations

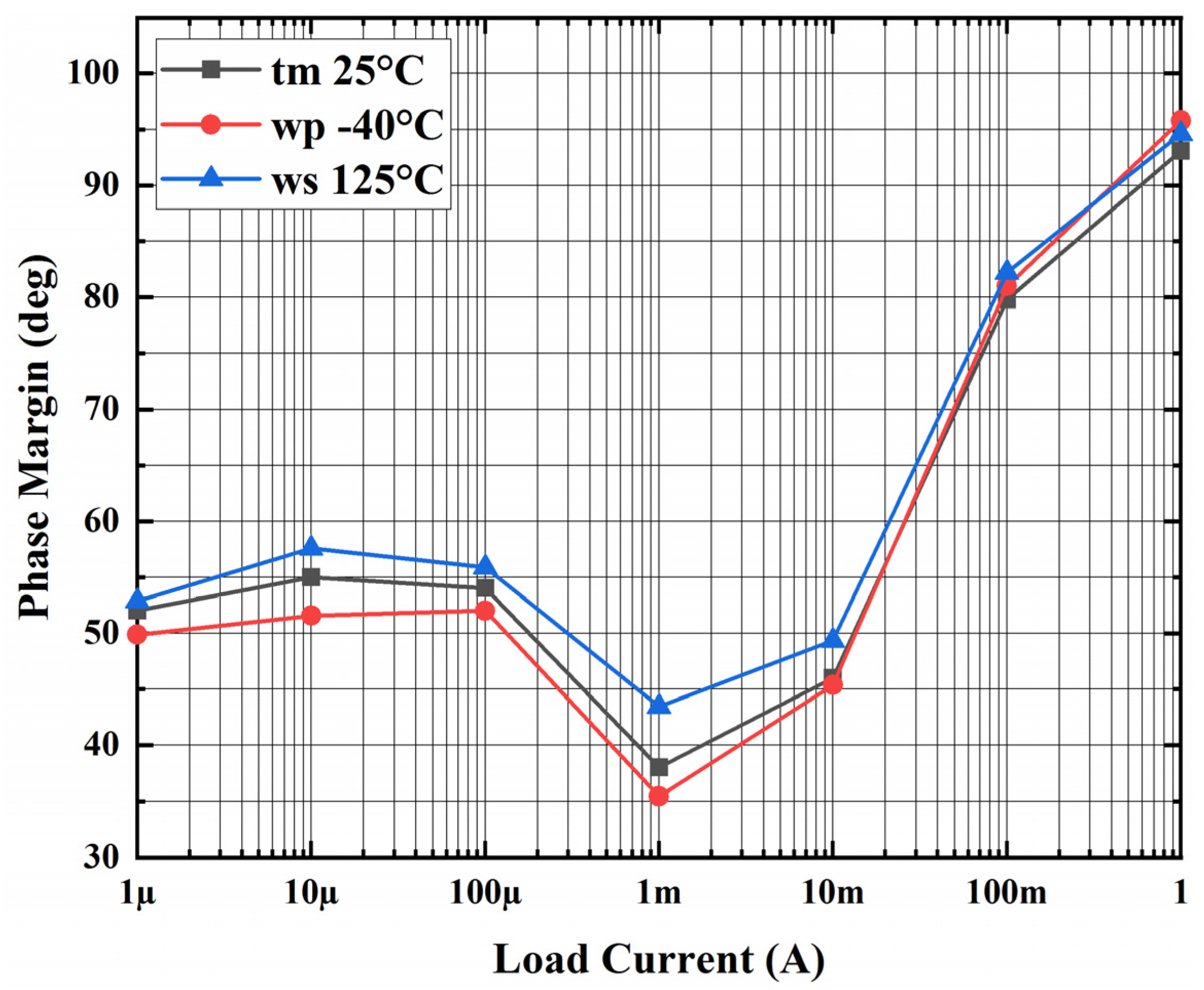

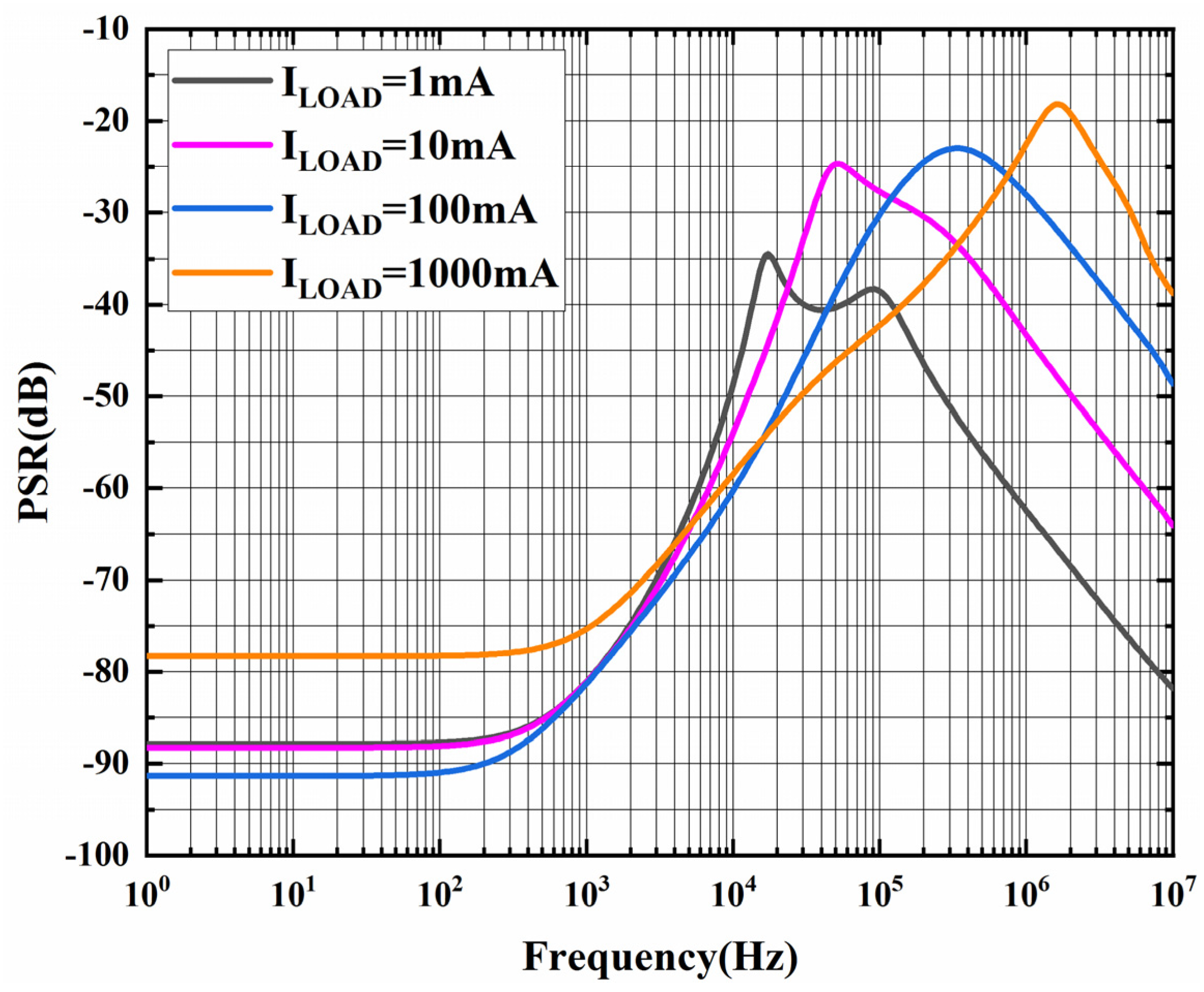

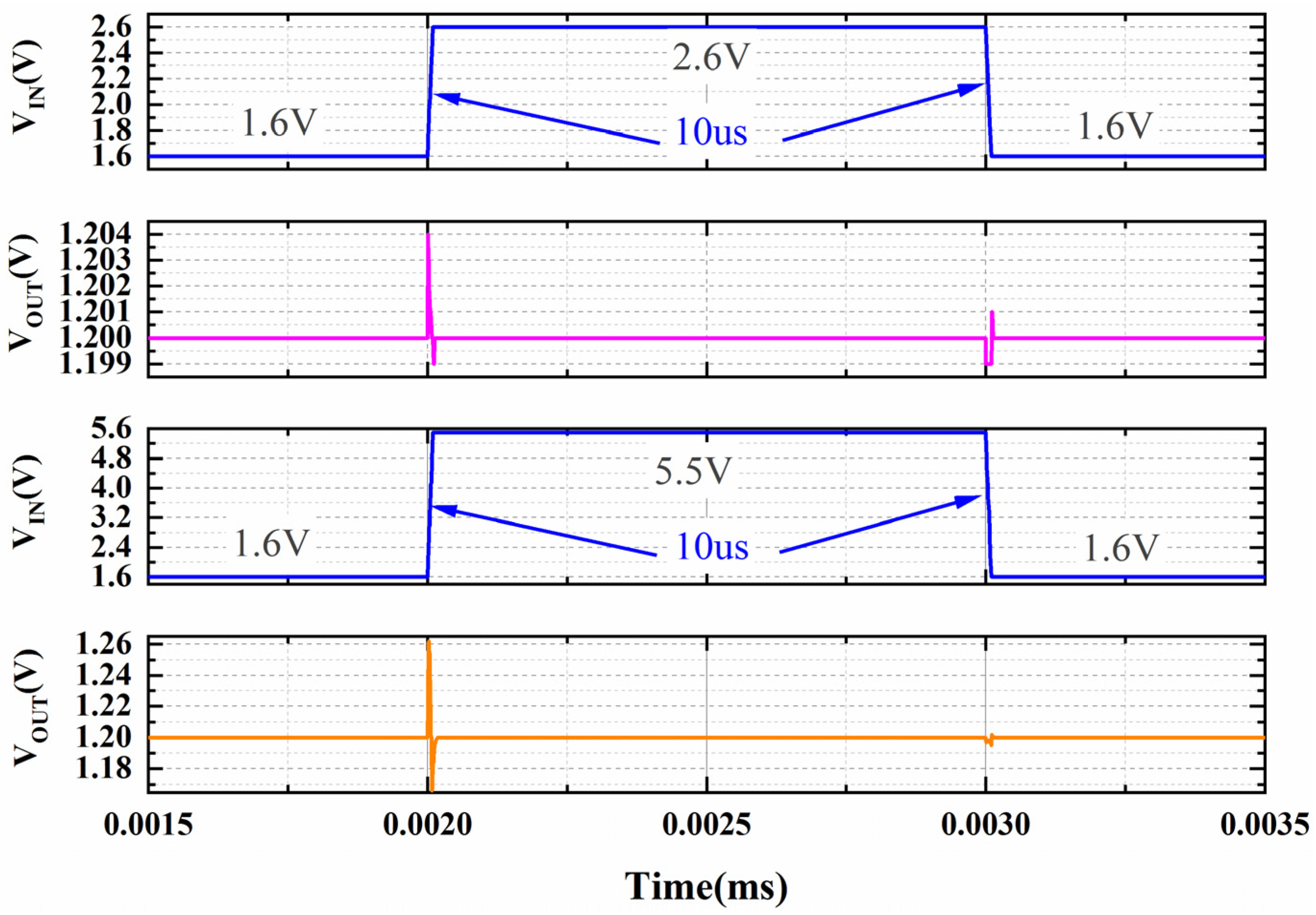

3. Simulation Results

4. Conclusions

Author Contributions

Funding

Data Availability Statement

Acknowledgments

Conflicts of Interest

References

- Ming, X.; Kuang, J.J.; Liang, H.; Zhang, J.; Qin, Y.; Zhang, Z.W.; Wang, Z.; Zhang, B. A Fast-Transient Low-Dropout Regulator with Current-Efficient Super Transconductance Cell and Dynamic Reference Control. IEEE Trans. Circuits Syst. I Regul. Pap. 2021, 68, 2354–2367. [Google Scholar] [CrossRef]

- Huang, C.H.; Ma, Y.T.; Liao, W.C. Design of a Low-Voltage Low-Dropout Regulator. IEEE Trans. Very Large Scale Integr. VLSI Syst. 2014, 22, 1308–1313. [Google Scholar] [CrossRef]

- Lu, Y.; Wang, Y.P.; Pan, Q.; Ki, W.H.; Yue, C.P. A Fully-Integrated Low-Dropout Regulator With Full-Spectrum Power Supply Rejection. IEEE Trans. Circuits Syst. I Regul. Pap. 2015, 62, 707–716. [Google Scholar] [CrossRef]

- Xu, W.; Upadhyaya, P.; Wang, X.; Tsang, R.; Lin, L. A 1A LDO Regulator Driven by a 0.0013mm(2) Class-D Controller. In Proceedings of the 2017 IEEE International Solid-State Circuits Conference (ISSCC), San Francisco, CA, USA, 5–9 February 2017; p. 104. [Google Scholar]

- Duan, Q.; Li, W.; Huang, S.; Ding, Y.; Meng, Z.; Shi, K. A Two-Module Linear Regulator with 3.9-10 V Input, 2.5 V Output, and 500 mA Load. Electronics 2019, 8, 1143. [Google Scholar] [CrossRef] [Green Version]

- Li, K.; Yang, C.; Guo, T.; Zheng, Y. A Multi-Loop Slew-Rate-Enhanced NMOS LDO Handling 1-A-Load-Current Step with Fast Transient for 5G Applications. IEEE J. Solid-State Circuits 2020, 55, 3076–3086. [Google Scholar] [CrossRef]

- Mandal, D.; Desai, C.; Bakkaloglu, B.; Kiaei, S. Adaptively Biased Output Cap-Less NMOS LDO With 19 ns Settling Time. IEEE Trans. Circuits Syst. II Express Briefs 2019, 66, 167–171. [Google Scholar] [CrossRef]

- Duong, Q.-H.; Huy-Hieu, N.; Kong, J.-W.; Shin, H.-S.; Ko, Y.-S.; Yu, H.-Y.; Lee, Y.-H.; Bea, C.-H.; Park, H.-J. Multiple-Loop Design Technique for High-Performance Low-Dropout Regulator. IEEE J. Solid-State Circuits 2017, 52, 2533–2549. [Google Scholar] [CrossRef]

- Magod, R.; Bakkaloglu, B.; Manandhar, S. A 1.24 mu A Quiescent Current NMOS Low Dropout Regulator With Integrated Low-Power Oscillator-Driven Charge-Pump and Switched-Capacitor Pole Tracking Compensation. IEEE J. Solid-State Circuits 2018, 53, 2356–2367. [Google Scholar] [CrossRef]

- Jiang, J.; Shu, W.; Chang, J.S. A 65-nm CMOS Low Dropout Regulator Featuring >60-dB PSRR Over 10-MHz Frequency Range and 100-mA Load Current Range. IEEE J. Solid-State Circuits 2018, 53, 2331–2342. [Google Scholar] [CrossRef]

- Milliken, R.J.; Silva-Martinez, J.; Sanchez-Sinencio, E. Full On-Chip CMOS Low-Dropout Voltage Regulator. IEEE Trans. Circuits Syst. I Regul. Pap. 2007, 54, 1879–1890. [Google Scholar] [CrossRef]

- Man, T.Y.; Mok, P.K.T.; Chan, M. A High Slew-Rate Push–Pull Output Amplifier for Low-Quiescent Current Low-Dropout Regulators with Transient-Response Improvement. IEEE Trans. Circuits Syst. II Express Briefs 2007, 54, 755–759. [Google Scholar] [CrossRef]

- Jeon, I.; Guo, T.; Roh, J. 300 mA LDO Using 0.94 mu A I-Q With an Additional Feedback Path for Buffer Turn-off Under Light-Load Conditions. IEEE Access 2021, 9, 51784–51792. [Google Scholar] [CrossRef]

- Lu, Y.; Ki, W.-H.; Yue, C.P. A 0.65ns-Response-Time 3.01ps FOM Fully-Integrated Low-Dropout Regulator with Full-Spectrum Power-Supply-Rejection for Wideband Communication Systems. In Proceedings of the 2014 IEEE International Solid-State Circuits Conference Digest of Technical Papers (ISSCC), San Francisco, CA, USA, 9–13 February 2014; pp. 306–307. [Google Scholar]

- Oh, W.; Bakkaloglu, B. A CMOS low-dropout regulator with current-mode feedback buffer amplifier. IEEE Trans. Circuits Syst. II Express Briefs 2007, 54, 922–926. [Google Scholar] [CrossRef]

- Zhan, C.; Ki, W.-H. An Output-Capacitor-Free Adaptively Biased Low-Dropout Regulator with Subthreshold Undershoot-Reduction for SoC. IEEE Trans. Circuits Syst. I Regul. Pap. 2012, 59, 1119–1131. [Google Scholar] [CrossRef]

- Al-Shyoukh, M.; Lee, H.; Perez, R. A transient-enhanced low-quiescent current low-dropout regulator with buffer impedance attenuation. IEEE J. Solid-State Circuits 2007, 42, 1732–1742. [Google Scholar] [CrossRef] [Green Version]

- Li, K.; Xiao, X.; Jin, X.; Zheng, Y. A 600-mA, Fast-Transient Low-Dropout Regulator with Pseudo-ESR Technique in 0.18-mu m CMOS Process. IEEE Trans. Very Large Scale Integr. VLSI Syst. 2020, 28, 403–413. [Google Scholar] [CrossRef]

- Park, J.; Lee, B.; Hong, S.-W. An Output Capacitorless Low-Dropout Regulator with a Low-V-DD Inverting Buffer for the Mobile Application. IEEE Trans. Ind. Electron. 2020, 67, 8931–8935. [Google Scholar] [CrossRef]

- Leung, K.N.; Mok, P.K.T. A capacitor-free CMOS low-dropout regulator with damping-factor-control frequency compensation. IEEE J. Solid-State Circuits 2003, 38, 1691–1702. [Google Scholar] [CrossRef]

- Hong, S.-W.; Cho, G.-H. High-Gain Wide-Bandwidth Capacitor-Less Low-Dropout Regulator (LDO) for Mobile Applications Utilizing Frequency Response of Multiple Feedback Loops. IEEE Trans. Circuits Syst. I Regul. Pap. 2016, 63, 46–57. [Google Scholar] [CrossRef]

- Lau, S.K.; Mok, P.K.T.; Leung, K.N. A Low-Dropout Regulator for SoC with Q-Reduction. IEEE J. Solid-State Circuits 2007, 42, 658–664. [Google Scholar] [CrossRef]

- Cao, H.; Yang, X.; Li, W.; Ding, Y.; Qu, W. An Impedance Adapting Compensation Scheme for High Current NMOS LDO Design. IEEE Trans. Circuits Syst. II Express Briefs 2021, 68, 2287–2291. [Google Scholar] [CrossRef]

- Lai, X.; Guo, J.; Sun, Z.; Xie, J. A 3-A CMOS low-dropout regulator with adaptive Miller compensation. Analog Integr. Circuits Signal Process. 2006, 49, 5–10. [Google Scholar] [CrossRef]

- Han, X.; Wu, L.; Gao, Y.; Ki, W.-H. An Adaptively Biased Output-Capacitor-Free Low-Dropout Regulator with Supply Ripple Subtraction and Pole-Tracking-Compensation. IEEE Trans. Power Electron. 2021, 36, 12795–12804. [Google Scholar] [CrossRef]

- Ming, X.; Liang, H.; Zhang, Z.-W.; Xin, Y.-L.; Qin, Y.; Wang, Z. A High-Efficiency and Fast-Transient Low-Dropout Regulator with Adaptive Pole Tracking Frequency Compensation Technique. IEEE Trans. Power Electron. 2020, 35, 12401–12415. [Google Scholar] [CrossRef]

- Bu, S.; Guo, J.; Leung, K.N. A 200-ps-Response-Time Output-Capacitorless Low-Dropout Regulator with Unity-Gain Bandwidth >100 MHz in 130-nm CMOS. IEEE Trans. Power Electron. 2018, 33, 3232–3246. [Google Scholar] [CrossRef]

- Ma, X.; Lu, Y.; Li, Q. A Fully Integrated LDO with 50-mV Dropout for Power Efficiency Optimization. IEEE Trans. Circuits Syst. II Express Briefs 2020, 67, 725–729. [Google Scholar] [CrossRef]

- Lv, S.P.; Wan, P.Y.; Zhang, H.D.; Geng, J.R.; Wen, J.B.; Yao, Y.M.; Chen, Z.J. A 0.18-ns Response Time Digital LDO Regulator with Adaptive PI Controller in 180-nm CMOS. Electronics 2021, 10, 1668. [Google Scholar] [CrossRef]

- Yu, Y.; Yuan, J.; Qiao, S.S.; Hei, Y. A Fast-Transient All-Digital LDO with Adaptive Clock Technique. Electronics 2019, 8, 1422. [Google Scholar] [CrossRef] [Green Version]

- Hazucha, P.; Karnik, T.; Bloechel, B.A.; Parsons, C.; Finan, D.; Borkar, S. Area-efficient linear regulator with ultra-fast load regulation. IEEE J. Solid-State Circuits 2005, 40, 933–940. [Google Scholar] [CrossRef]

- Ho, M.; Guo, J.; Mak, K.H.; Goh, W.L.; Bu, S.; Zheng, Y.; Tang, X.; Leung, K.N. A CMOS Low-Dropout Regulator With Dominant-Pole Substitution. IEEE Trans. Power Electron. 2016, 31, 6362–6371. [Google Scholar] [CrossRef]

- Choe, Y.-J.; Nam, H.; Park, J.-D. A Low-Dropout Regulator with PSRR Enhancement through Feed-Forward Ripple Cancellation Technique in 65 nm CMOS Process. Electronics 2020, 9, 146. [Google Scholar] [CrossRef] [Green Version]

- Zhang, H.D.; Wan, P.Y.; Geng, J.R.; Liu, Z.Z.; Chen, Z.J. A Fast Transient Response Digital LDO with a TDC-Based Signal Converter. Electronics 2020, 9, 132. [Google Scholar] [CrossRef] [Green Version]

| [5] | [8] | [32] | [33] | [34] | This Study | |

|---|---|---|---|---|---|---|

| Technology (μm) | 0.25 | 0.13 | 0.18 | 0.065 | 0.065 | 0.18 |

| Power MOS type | NPN | PMOS | PMOS | PMOS | PMOS | PMOS |

| Input voltage (V) | 3.9–10 | 1.05–2.0 | 1.2–1.8 | 1.2 | 0.7–1.1 | 1.6~5.5 |

| Dropout voltage (mV) | >200 | 29.7 | 200 | 0.98 | N/A | 200 |

| Max. Output current (mA) | 500 | 300 | 100 | 20 | 120 | 1000 |

| Quiescent current (μA) | 350 | 14–120 | 135.1 | 385 | 495 | 21–424 |

| Current Efficiency (%) | 99.93 | 99.96 | 99.87 | 98.11 | 99.58 | 99.96 |

| Load Regulation (μV/mA) | 32.8 | 6 | 75 | 2300 | 600 | 0.089 |

| Line Regulation (mV/V) | 0.2 | 0.44 | 22.7 | 80 | 15 | 0.562 * |

| FOM (ps) | 3388 | 12.44 | 439 | N/A | 20.46 | 6.031 |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2022 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Jiang, Y.; Wang, L.; Wang, Y.; Wang, S.; Guo, M. A High-Loop-Gain Low-Dropout Regulator with Adaptive Positive Feedback Compensation Handling 1-A Load Current. Electronics 2022, 11, 949. https://doi.org/10.3390/electronics11060949

Jiang Y, Wang L, Wang Y, Wang S, Guo M. A High-Loop-Gain Low-Dropout Regulator with Adaptive Positive Feedback Compensation Handling 1-A Load Current. Electronics. 2022; 11(6):949. https://doi.org/10.3390/electronics11060949

Chicago/Turabian StyleJiang, Yongchao, Lixin Wang, Yue Wang, Shixin Wang, and Min Guo. 2022. "A High-Loop-Gain Low-Dropout Regulator with Adaptive Positive Feedback Compensation Handling 1-A Load Current" Electronics 11, no. 6: 949. https://doi.org/10.3390/electronics11060949