A Novel Buck Converter with Dual Loops Control Mechanism

Abstract

:1. Introduction

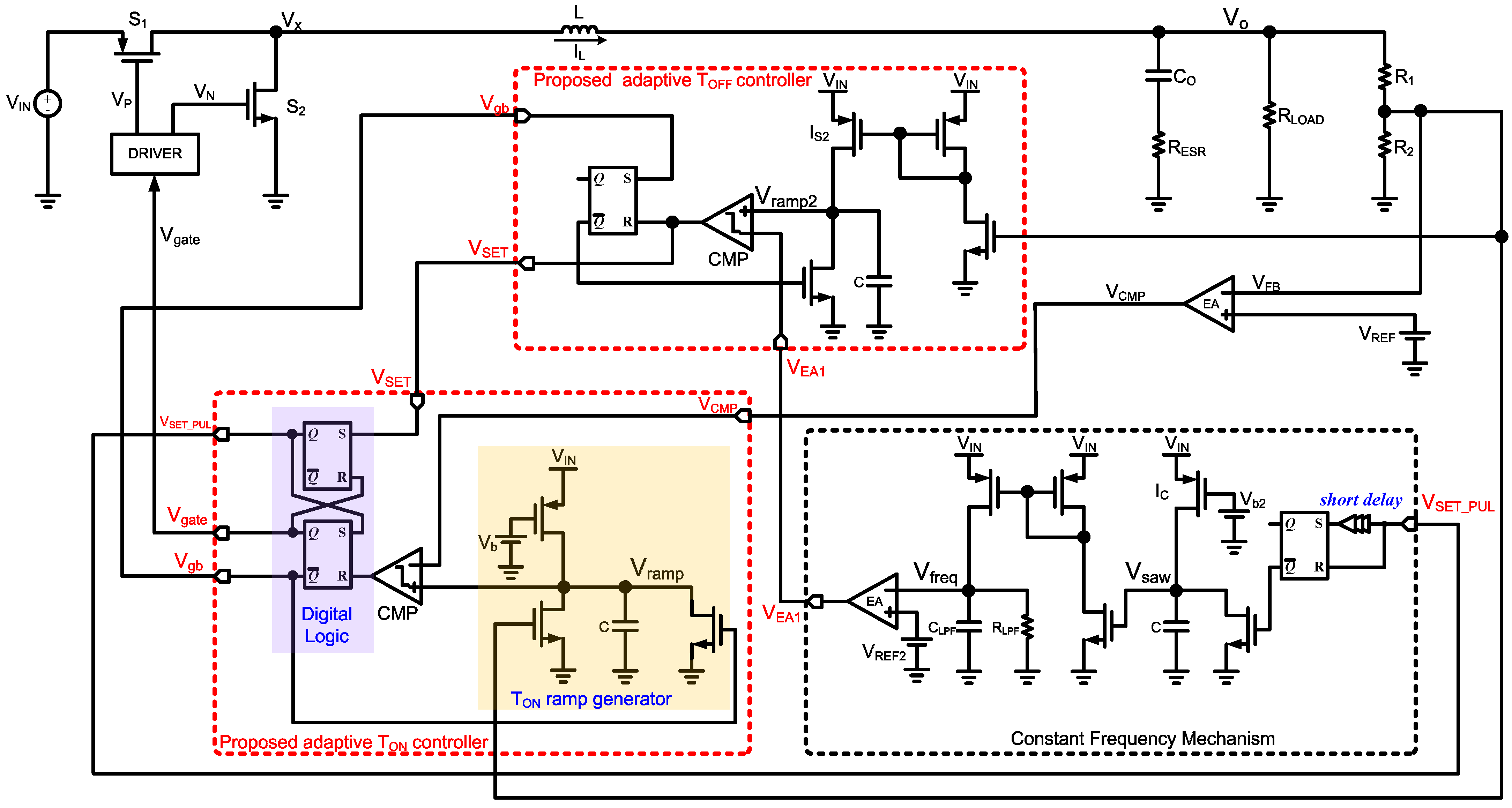

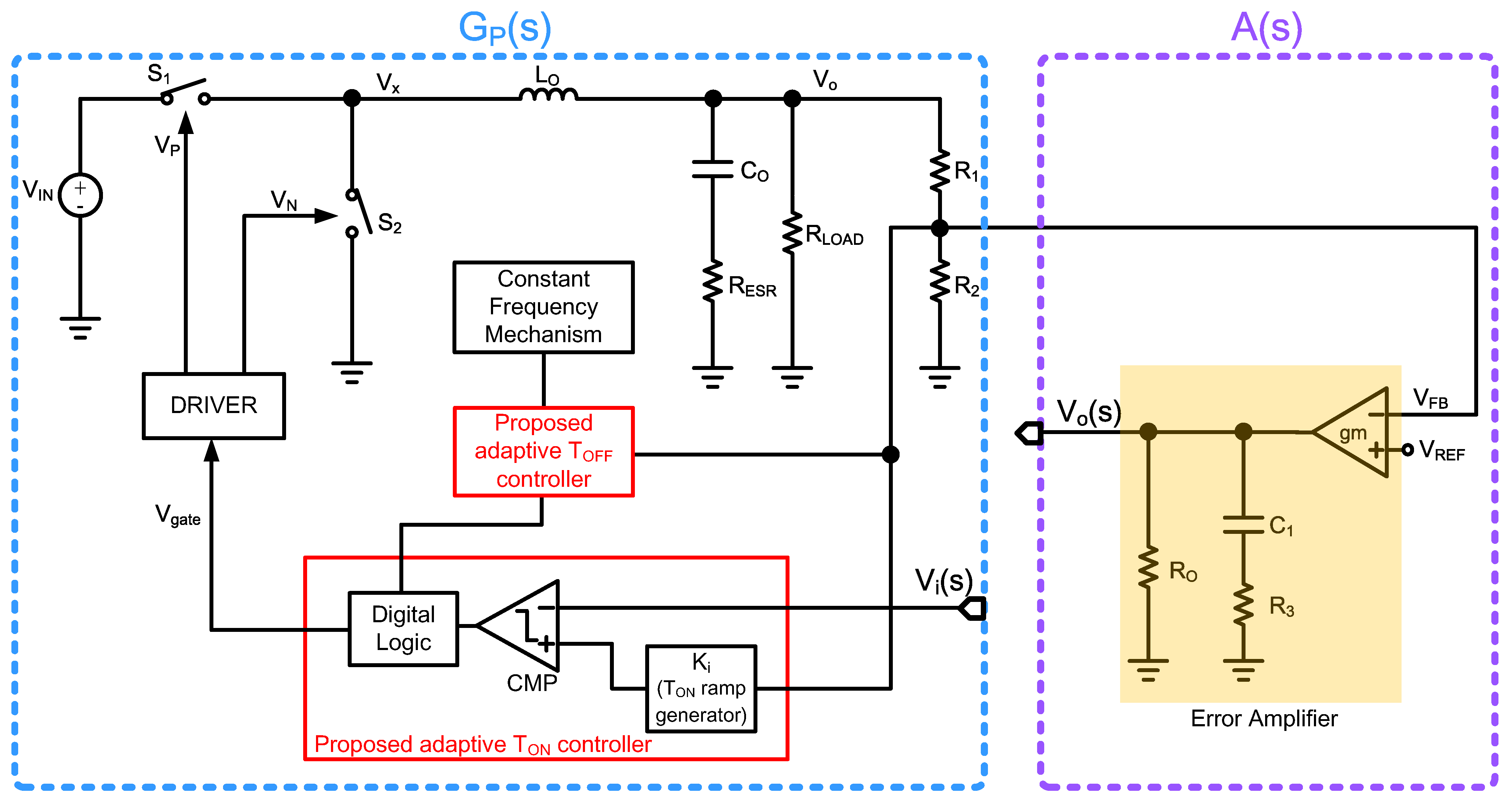

2. Proposed Control Topology and Circuit Realization

2.1. Proposed Control Topology

- (A)

- Constant Frequency Mechanism:

- (B)

- Proposed adaptive TOFF controller:

- (C)

- Proposed adaptive TON controller:

- (D)

- EA (Error Amplifier)

- (E)

- DRIVER:

- Advantages

- (A)

- The scheme does not need to design a complex sensing circuit to sense the inductor current at any time. Compared with the scheme of using the current sensor [2], the proposed scheme is easy to implement and suitable for mass production.

- (B)

- The whole control circuit does not require special semiconductor devices, and there is no special matching issue in layout.

- (C)

- By the “constant frequency mechanism” module, the proposed scheme can make the switching frequency constant, which greatly reduces the difficulty in solving EMI issue. Moreover, the “constant frequency mechanism” is easy to implement, instead of PLL [31].

- Disadvantages

- (A)

- In contrast to SC converter, the scheme cannot be fully integrated into silicon.

2.2. Circuit Realization and Operating Principle

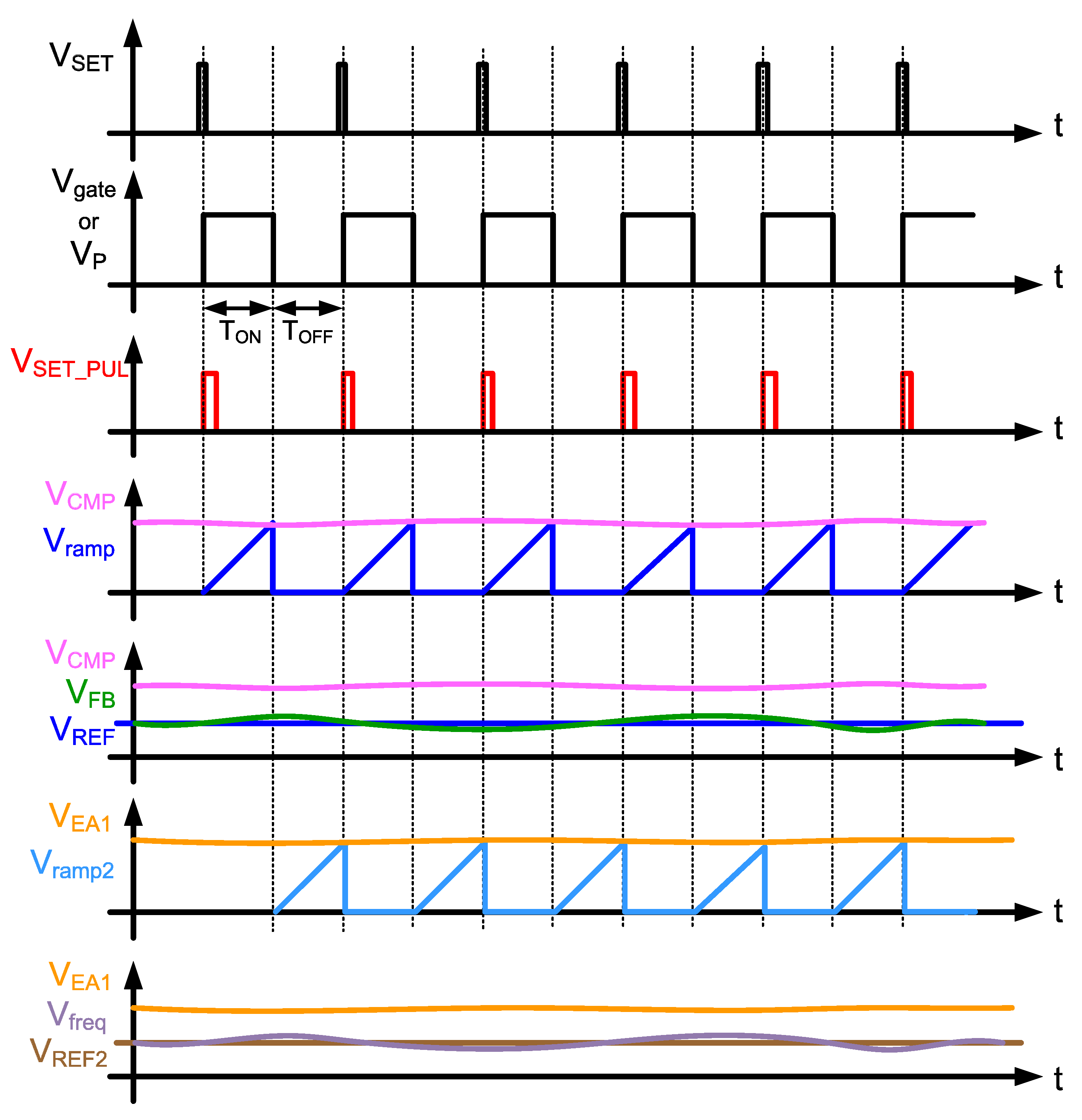

- The switch S1 turns ON, and the switch S2 turns OFF. In this state, the inductor is in the charging phase. The ON time of S1 is labeled as TON. The TON is determined by the “proposed adaptive TON controller” module. When S1 is ON, the Vramp begins to rise toward the VCMP. Once the Vramp reaches the VCMP, the S1 is turned OFF, and the S2 is turned ON.

- The switch S1 turns OFF, and the switch S2 turns ON. In this state, the inductor is in the discharging phase. The OFF time of S1 is labeled as TOFF. The TOFF is determined by the “proposed adaptive TOFF controller” module.

- The “constant frequency mechanism” works to detect the switching frequency. The VEA1 controls the “proposed adaptive TOFF controller” to decide TOFF [31].

- In the steady state, the VFB and the Vfreq are almost equal to the VREF and the VREF2, respectively. In other words, the VCMP and the VEA1 will eventually converge to their stable voltages. The key waveforms of the converter are drawn in Figure 4.

3. Theoretical Analysis

3.1. Mathematical Model

3.2. Component Selection

4. Simulation Results

4.1. SIMPLIS Schematic

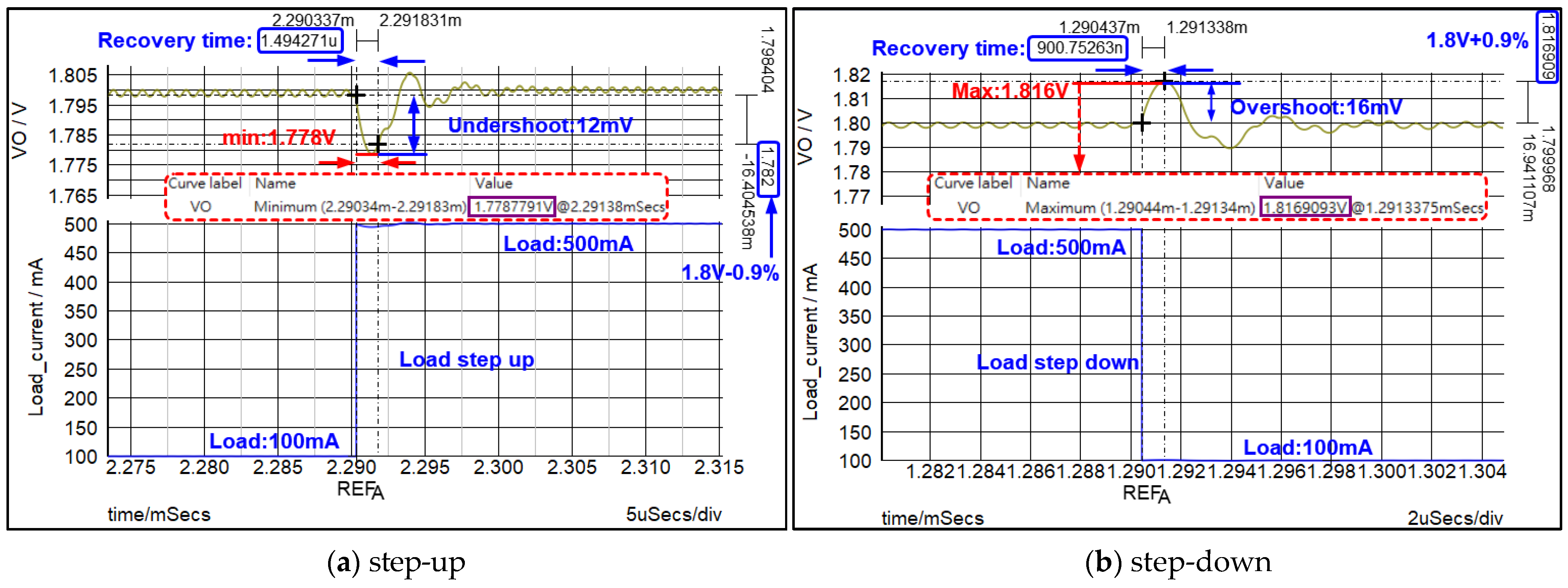

4.2. Transient Performance

4.3. Load Regulation

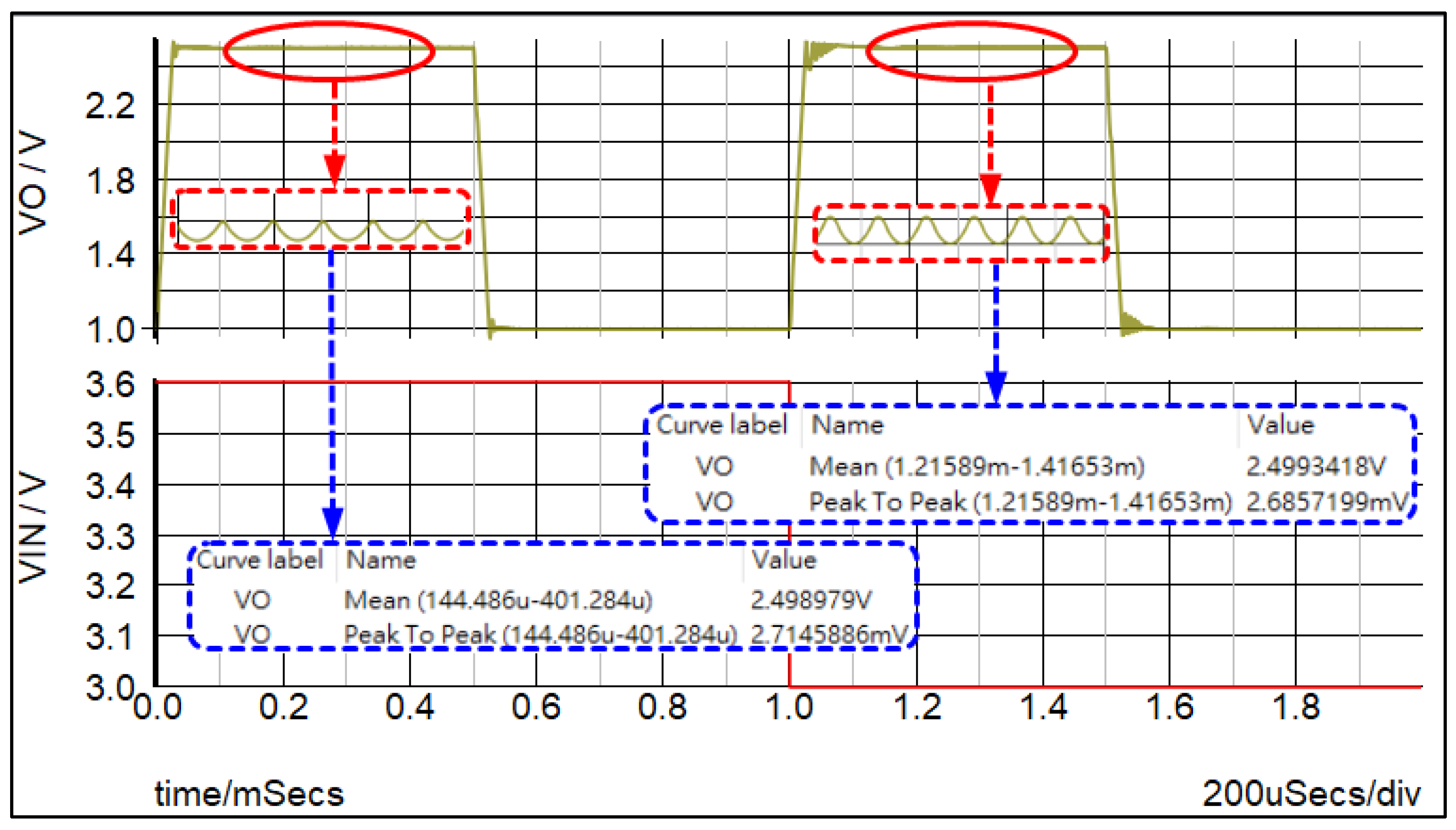

4.4. Line Regulation

4.5. Switching Frequency Regulation

- (A)

- Conversion step:

- (B)

- Regulation step:

4.6. Performance List

5. Conclusions

Author Contributions

Funding

Conflicts of Interest

References

- Chen, J.-J.; Lu, M.-X.; Wu, T.-H.; Hwang, Y.-S. Sub-1-V Fast-Response Hysteresis-Controlled CMOS Buck Converter Using Adaptive Ramp Techniques. IEEE Trans. Very Large Scale Integr. (VLSI) Syst. 2012, 21, 1608–1618. [Google Scholar] [CrossRef]

- Chen, J.-J.; Hwang, Y.-S.; Chen, J.-H.; Ku, Y.-T.; Yu, C.-C. A New Fast-Response Current-Mode Buck Converter with Improved I2 -Controlled Techniques. IEEE Trans. Very Large Scale Integr. (VLSI) Syst. 2018, 26, 903–911. [Google Scholar] [CrossRef]

- Hwang, Y.S.; Chen, J.J.; Ku, Y.T.; Yang, J.Y. An Improved Optimum-Damping Current-Mode Buck Converter with Fast-Transient Response and Small-Transient Voltage using New Current Sensing Circuits. IEEE Trans. Ind. Electron. 2020, 68, 9505–9514. [Google Scholar] [CrossRef]

- Ballo, A.; Grasso, A.D.; Palumbo, G. A Review of Charge Pump Topologies for the Power Management of IoT Nodes. Electronics 2019, 8, 480. [Google Scholar] [CrossRef] [Green Version]

- Ballo, A.; Grasso, A.D.; Palumbo, G.; Tanzawa, T. Charge Pumps for Ultra-Low-Power Applications: Analysis, Design, and New Solutions. IEEE Trans. Circuits Syst. II 2021, 68, 2895–2901. [Google Scholar] [CrossRef]

- Souza, A.F.; Tofoli, F.L.; Ribeiro, E.R. Switched Capacitor DC-DC Converters: A Survey on the Main Topologies, Design Characteristics, and Applications. Energies 2021, 14, 2231. [Google Scholar] [CrossRef]

- Seeman, M.D.; Sanders, S.R. Analysis and Optimization of Switched-Capacitor DC–DC Converters. IEEE Trans. Power Electron. 2008, 23, 841–851. [Google Scholar] [CrossRef]

- Deepa, K.; Saju, H.; Kumar, M. Soft switched flyback converter for smps applications. In Proceedings of the 2013 International Conference on Control Communication and Computing (ICCC), Thiruvananthapuram, India, 13–15 December 2013; pp. 475–478. [Google Scholar]

- Aharon, I.; Kuperman, A.; Aharon, I.; Shmilovitz, D. Analysis of Bi-Directional Buck-Boost Converter for Energy Storage Applications. In Proceedings of the IECON 2013—39th Annual Conference of the IEEE Industrial Electronics Society, Vienna, Austria, 10–13 November 2013; pp. 88–96. [Google Scholar]

- Gallo, C.A.; Tofoli, F.L.; Pinto, J.A.C. Two-Stage Isolated Switch-Mode Power Supply with High Efficiency and High Input Power Factor. IEEE Trans. Ind. Electron. 2010, 57, 3754–3766. [Google Scholar] [CrossRef]

- Huang, Q.; Zhan, C.; Burm, J. A 30-MHz Voltage-Mode Buck Converter Using Delay-Line-Based PWM Control. IEEE Trans. Circuits Syst. II Express Briefs 2018, 65, 1659–1663. [Google Scholar] [CrossRef]

- Chen, J.-J.; Hwang, Y.-S.; Ku, Y.-T.; Li, Y.-H.; Chen, J.-A. A Current-Mode-Hysteretic Buck Converter with Constant-Frequency-Controlled and New Active-Current-Sensing Techniques. IEEE Trans. Power Electron. 2020, 36, 3126–3134. [Google Scholar] [CrossRef]

- Chen, J.-J.; Hwang, Y.-S.; Lin, J.-Y.; Ku, Y. A Dead-Beat-Controlled Fast-Transient-Response Buck Converter with Active Pseudo-Current-Sensing Techniques. IEEE Trans. Very Large Scale Integr. (VLSI) Syst. 2019, 27, 1751–1759. [Google Scholar] [CrossRef]

- Chen, W.-W.; Chen, J.-F.; Liang, T.-J.; Wei, L.-C.; Ting, W.-Y. Designing a Dynamic Ramp with an Invariant Inductor in Current-Mode Control for an On-Chip Buck Converter. IEEE Trans. Power Electron. 2013, 29, 750–758. [Google Scholar] [CrossRef]

- Saini, D.K.; Reatti, A.; Kazimierczuk, M.K. Average Current-Mode Control of Buck DC-DC Converter with Reduced Control Voltage Ripple. In Proceedings of the 42nd Annual Conference of the IEEE Industrial Electronics Society, Florence, Italy, 23–26 October 2016; IECON: Florence, Italy, 2016. [Google Scholar]

- Ballo, A.; Bottaro, M.; Grasso, A.D.; Palumbo, G.; Grasso, A.D. Regulated Charge Pumps: A Comparative Study by Means of Verilog-AMS. Electronics 2020, 9, 998. [Google Scholar] [CrossRef]

- ABallo, A.; Grasso, A.D.; Palumbo, G. Current-mode body-biased switch to increase performance of linear charge pumps. Int. J. Circuit Theory Appl. 2020, 48, 1864–1872. [Google Scholar]

- Yan, Y.; Lee, F.C.; Mattavelli, P.; Liu, P.-H. I2 Average Current Mode Control for Switching Converters. IEEE Trans. Power Electron. 2013, 29, 2027–2036. [Google Scholar] [CrossRef]

- Redl, R.; Sokal, N.O. Current-mode control, five different types, used with the three basic classes of power converters: Small-signal AC and large-signal DC characterization, stability requirements, and implementation of practical circuits. In Proceedings of the 1985 IEEE Power Electronics Specialists Conference, Toulouse, France, 24–28 June 1985; pp. 771–785. [Google Scholar]

- Li, J. Current-Mode Control: Modeling and its Digital Application. Ph.D. Dissertation, Faculty of the Virginia Polytechnic Institute and State University, Blacksburg, VA, USA, 2009. [Google Scholar]

- Zhong, S.; Shen, Z. A Hybrid Constant On-Time Mode for Buck Circuits. Electronics 2021, 10, 930. [Google Scholar] [CrossRef]

- Lin, Y.-C.; Chen, C.-J.; Chen, D.; Wang, B. A Ripple-Based Constant On-Time Control with Virtual Inductor Current and Offset Cancellation for DC Power Converters. IEEE Trans. Power Electron. 2012, 27, 4301–4310. [Google Scholar] [CrossRef]

- Nien, C.-F.; Chen, D.; Hsiao, S.-F.; Kong, L.; Chen, C.-J.; Chan, W.-H.; Lin, Y.-L. A Novel Adaptive Quasi-Constant On-Time Current-Mode Buck Converter. IEEE Trans. Power Electron. 2016, 32, 8124–8133. [Google Scholar] [CrossRef]

- Lin, H.-C.; Fung, B.-C.; Chang, T.-Y. A current mode adaptive on-time control scheme for fast transient DC-DC converters. In Proceedings of the 2008 IEEE International Symposium on Circuits and Systems, Seattle, WA, USA, 18–21 May 2008; pp. 2602–2605. [Google Scholar]

- Zhen, S. Variable on time controlled buck converter for DVS applications. In Proceedings of the Conference of the IEEE Industrial Electronics Society, Beijing, China, 29 October–1 November 2017; pp. 1642–1648. [Google Scholar]

- Bari, S.; Li, Q.; Lee, F.C. Fast Adaptive on Time Control for Transient Performance Improvement. In Proceedings of the 2015 IEEE Applied Power Electronics Conference and Exposition (APEC), Charlotte, NC, USA, 15–19 March 2015; pp. 397–403. [Google Scholar]

- Liu, P.-J.; Kuo, M.-H. Adaptive On-Time Buck Converter with Wave Tracking Reference Control for Output Regulation Accuracy. Energies 2021, 14, 3809. [Google Scholar] [CrossRef]

- Bari, S.; Li, Q.; Lee, F.C. A New Fast Adaptive On-Time Control for Transient Response Improvement in Constant On-Time Control. IEEE Trans. Power Electron. 2018, 33, 2680–2689. [Google Scholar] [CrossRef]

- Wong, L.K.; Man, T.K. Adaptive On-Time Converters. IEEE Ind. Electron. Mag. 2010, 4, 28–35. [Google Scholar] [CrossRef]

- Chou, H.-H.; Chen, H.-L.; Fan, Y.-H.; Wang, S.-F. Adaptive On-Time Control Buck Converter with a Novel Virtual Inductor Current Circuit. Electronics 2021, 10, 2143. [Google Scholar] [CrossRef]

- Chou, H.-H.; Chen, H.-L. A Novel Buck Converter with Constant Frequency Controlled Technique. Energies 2021, 14, 5911. [Google Scholar] [CrossRef]

- Li, J.; Lee, F.C. New modeling approach and equivalent circuit representation for current-mode control. IEEE Trans. Power Electron. 2010, 25, 1218–1230. [Google Scholar]

- Enrique, J.M.; Barragán, A.J.; Durán, E.; Andújar, J.M.; Gómez, J.M.E.; Piña, A.J.B.; Aranda, E.D.; Márquez, J.M.A. Theoretical Assessment of DC/DC Power Converters’ Basic Topologies. A Common Static Model. Appl. Sci. 2017, 8, 19. [Google Scholar] [CrossRef] [Green Version]

- Suntio, T. Dynamic Modeling and Analysis of PCM-Controlled DCM-Operating Buck Converters—A Reexamination. Energies 2018, 11, 1267. [Google Scholar] [CrossRef] [Green Version]

- Ridley, R.B. An Accurate and Practical Small-Signal Model for Current-Mode Control. Available online: www.ridleyengineering.com (accessed on 24 July 2021).

- Zhen, S.; Zeng, P.; Chen, J.; Zhou, W.; Wang, J.; Luo, P.; Zhang, B. Transient Response Improvement of DC-DC Converter by Current Mode Variable on Time Control. In Proceedings of the 2018 IEEE 61st International Midwest Symposium on Circuits and Systems (MWSCAS), Windsor, ON, Canada, 5–8 August 2018. [Google Scholar]

- Jiang, C.R.; Chai, C.C.; Han, C.X.; Yang, Y.T. A high performance adaptive on-time controlled valley-current-mode DCDC buck converter. J. Semicond. 2020, 41, 062406. [Google Scholar] [CrossRef]

| Component | Value | Unit |

|---|---|---|

| RLOAD | 3.6 | Ω |

| Co | 10 | μF |

| L | 4.7 | μH |

| RESR | 5 | mΩ |

| Ro | 1 | MΩ |

| R3 | 180 | kΩ |

| C1 | 200 | pF |

| Parameter | Conditions | Min. | Typ. | Max. | Unit |

|---|---|---|---|---|---|

| Input voltage | 3.0 | 3.6 | V | ||

| Output voltage | 1.0 | 2.5 | V | ||

| Output ripple | Vin = 3.6 V, Vo = 2.5 V | 2.7 | mV | ||

| Load current | 100 | 500 | mA | ||

| Inductor | DCR *: 30 mΩ | 4.7 | μH | ||

| Output capacitor | ESR: 5 mΩ | 10 | μF | ||

| Switching frequency | Vin = 3.0~3.6 V, Vo = 1.0~2.5 V | 1 | MHz | ||

| Recovery time (step-up) | Vo = 1.8 V Load current: 100 mA to 500 mA | 1.5 | μs | ||

| Recovery time (step-down) | Vo = 1.8 V Load current: 500 mA to 100 mA | 0.9 | μs | ||

| Overshoot voltage | Vin = 3.3 V, Vo = 1.8 V | 16 | mV | ||

| Undershoot voltage | Vin = 3.3 V, Vo = 1.8 V | 12 | mV |

| References | 2018 [36] | 2020 [37] | 2021 [30] | 2021 [31] | This Work |

|---|---|---|---|---|---|

| Results | simulation | simulation | simulation | simulation | simulation |

| Control scheme | AOT | AOT | AOT | AOT | dual loops |

| Process (μm) | 0.35 | 0.18 | 0.35 ** | 0.18 ** | 0.35 ** |

| Input voltage (V) | 12 | 3.3–5.0 | 3.0–3.6 | 3.0–3.6 | 3.0–3.6 |

| Output voltage (V) | 1.2 | 1.8 | 1.0–2.5 | 1.0–2.5 | 1.0–2.5 |

| Inductor (μH) | 1 | 1.5 | 4.7 | 4.7 | 4.7 |

| Output Capacitor (μF) | 47 | 20 | 10 | 10 | 10 |

| Switching Frequency (MHz) | 1 | 1 | 1 | 1 | 1 |

| Switching frequency variation (%) | N/A | N/A | N/A | <1% | <1% |

| Max. Load current (mA) | 5000 | 2000 | 500 | 500 | 500 |

| Load current step (mA) | 4000 | 800 | 400 | 400 | 400 |

| Undershoot/Overshoot (mV) | 20/26 | 13/14 | 23/26 | 20/24 | 16/12 |

| Recovery time (μs) (rise/fall) | <3 | 6/2 | 1.98/1.6 | 1.69/1.62 | 1.5/0.9 |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2022 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Chou, H.-H.; Luo, W.-H.; Chen, H.-L.; Wang, S.-F. A Novel Buck Converter with Dual Loops Control Mechanism. Electronics 2022, 11, 1256. https://doi.org/10.3390/electronics11081256

Chou H-H, Luo W-H, Chen H-L, Wang S-F. A Novel Buck Converter with Dual Loops Control Mechanism. Electronics. 2022; 11(8):1256. https://doi.org/10.3390/electronics11081256

Chicago/Turabian StyleChou, Hsiao-Hsing, Wen-Hao Luo, Hsin-Liang Chen, and San-Fu Wang. 2022. "A Novel Buck Converter with Dual Loops Control Mechanism" Electronics 11, no. 8: 1256. https://doi.org/10.3390/electronics11081256