Experimental Comparison of a New 1.2 kV 4H-SiC Split-Gate MOSFET with Conventional SiC MOSFETs in Terms of Reliability Robustness

Abstract

:1. Introduction

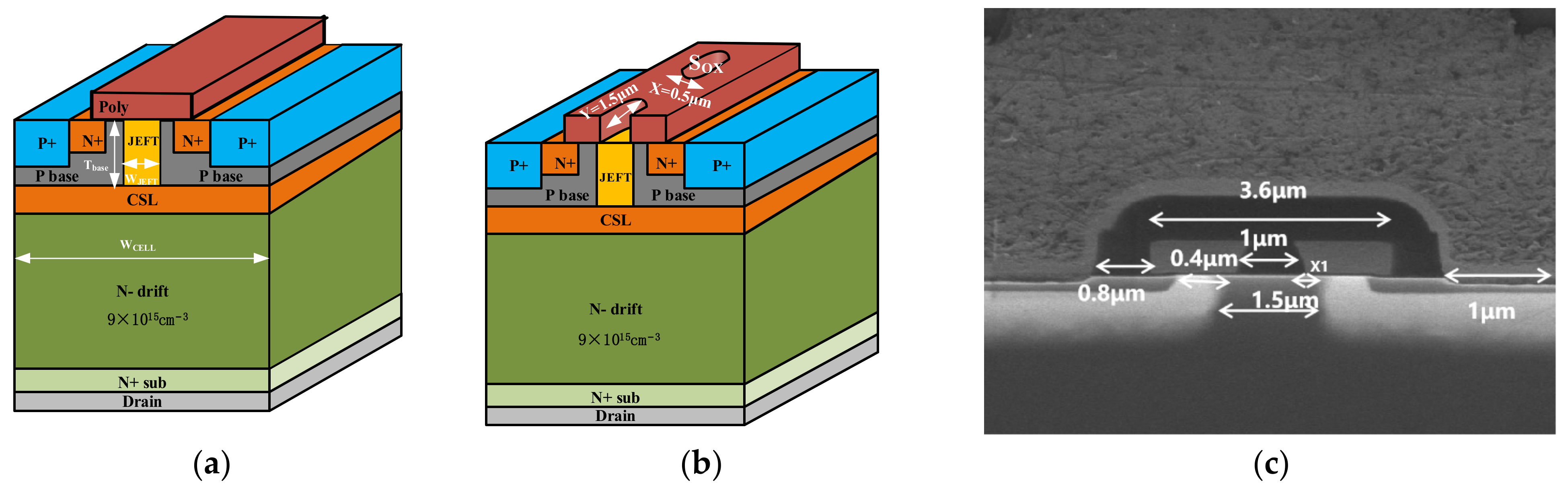

2. Device Design and Fabrication

3. Electrical Characteristics and Discussion

3.1. Static Electrical Characteristics

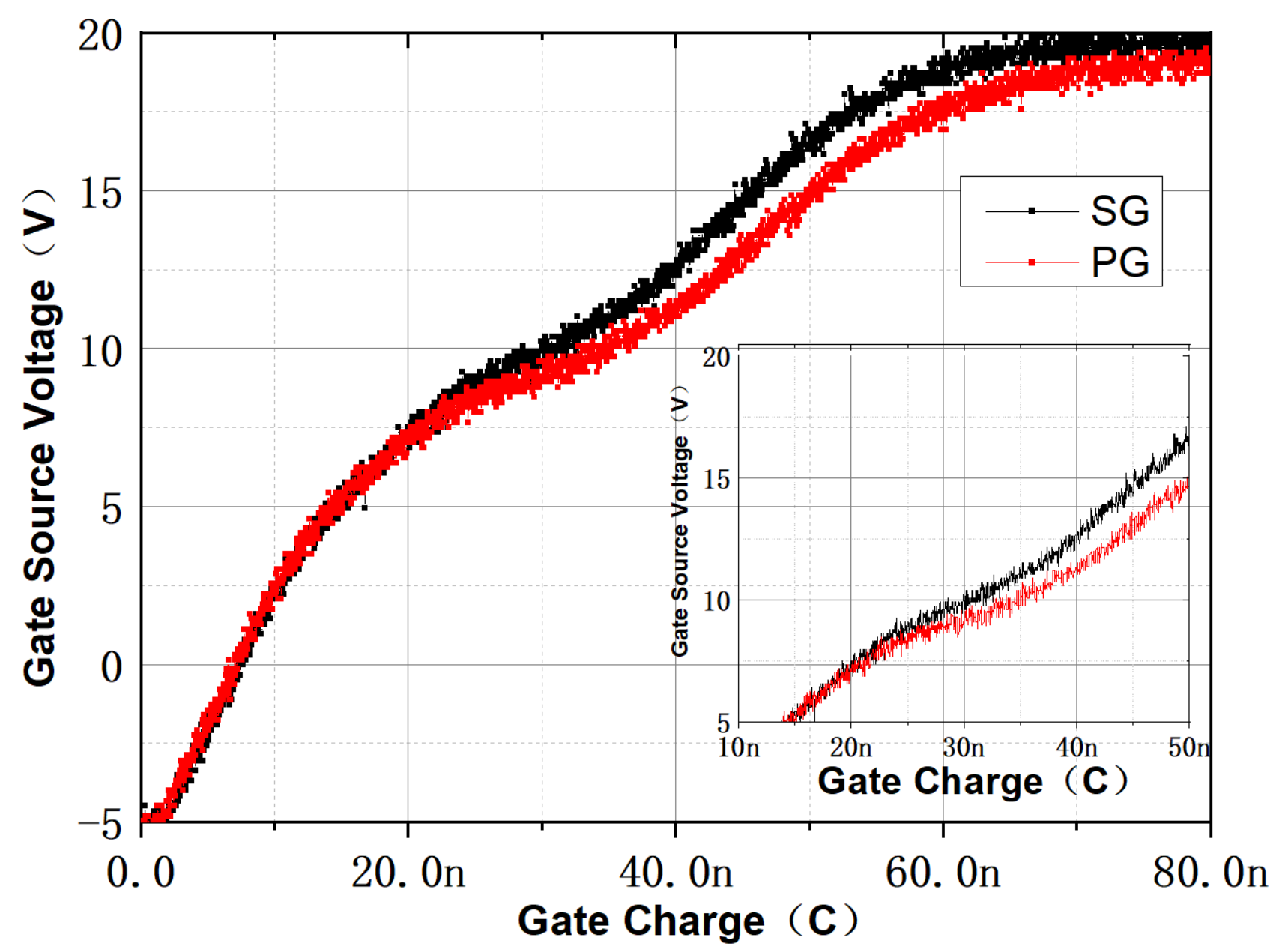

3.2. Dynamic Electrical Characteristics

4. Experimental Results and Discussion

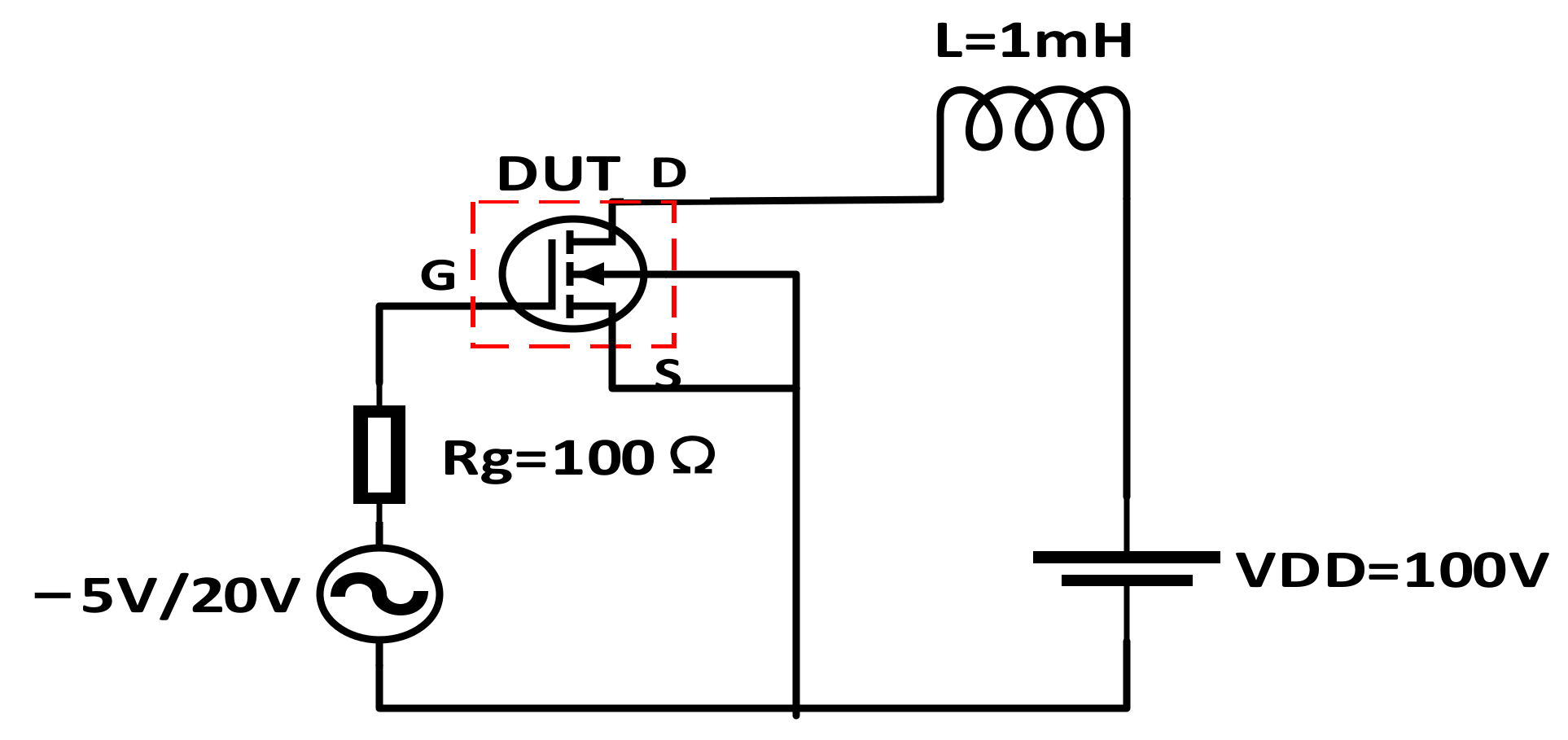

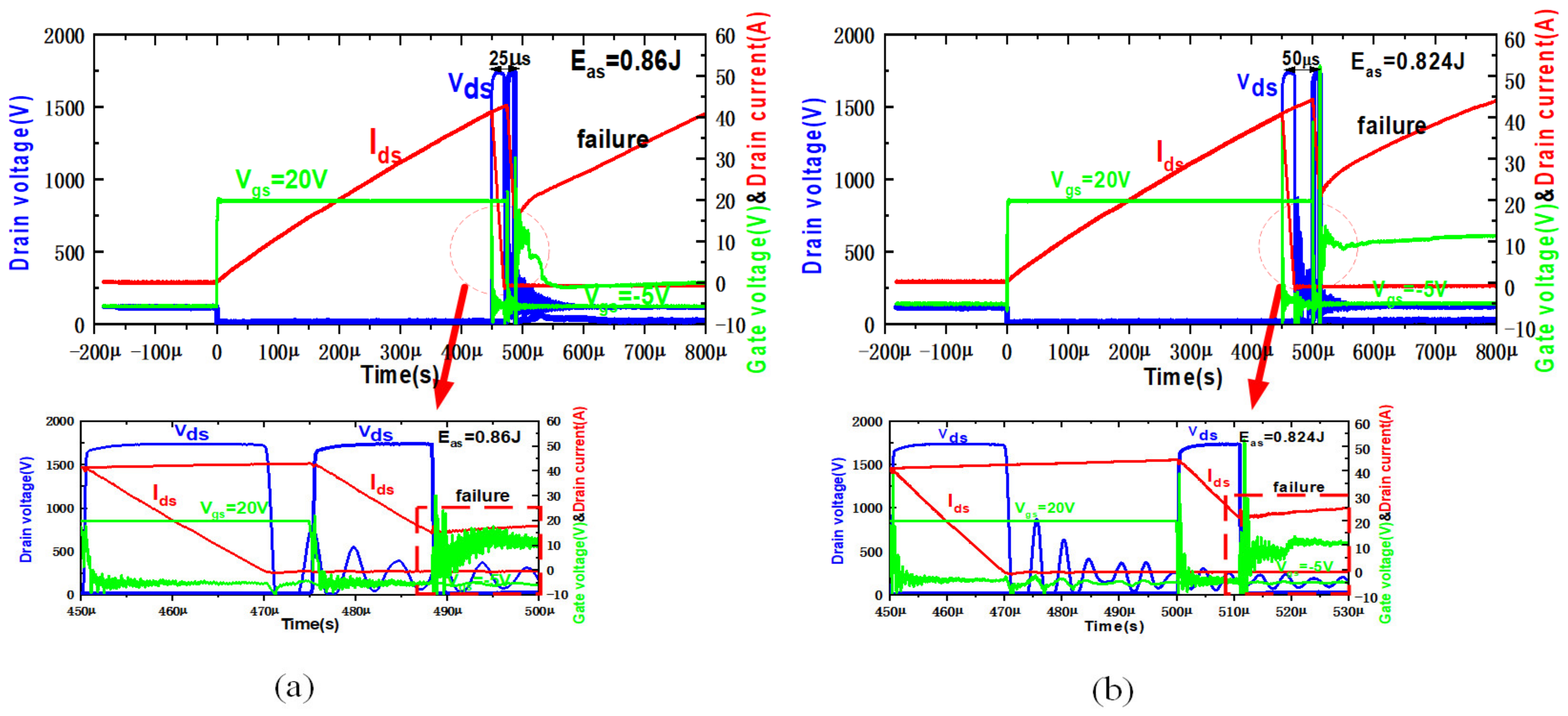

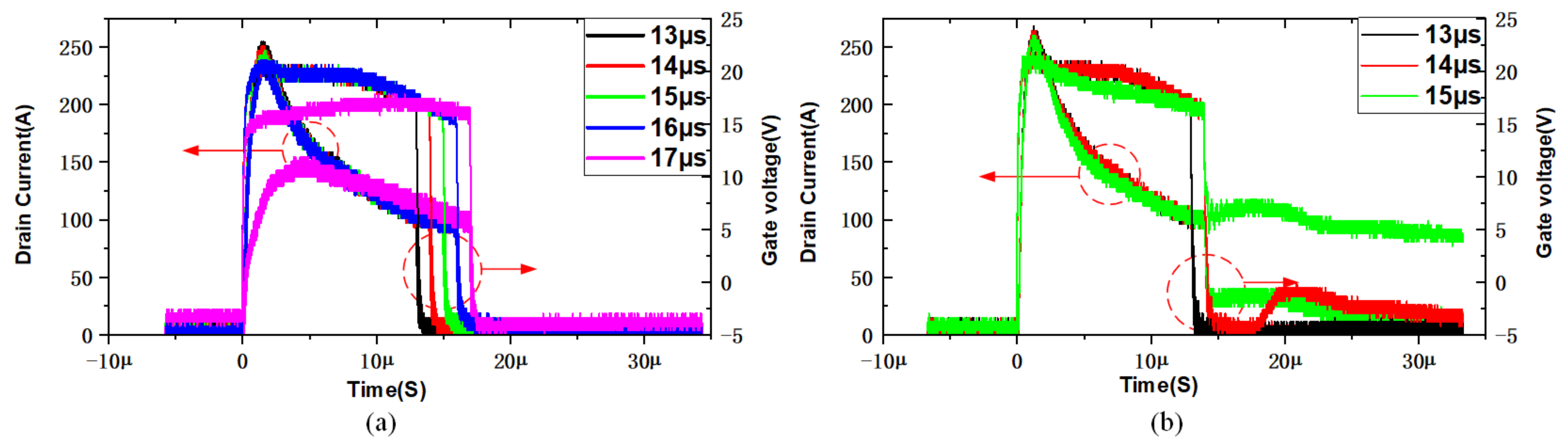

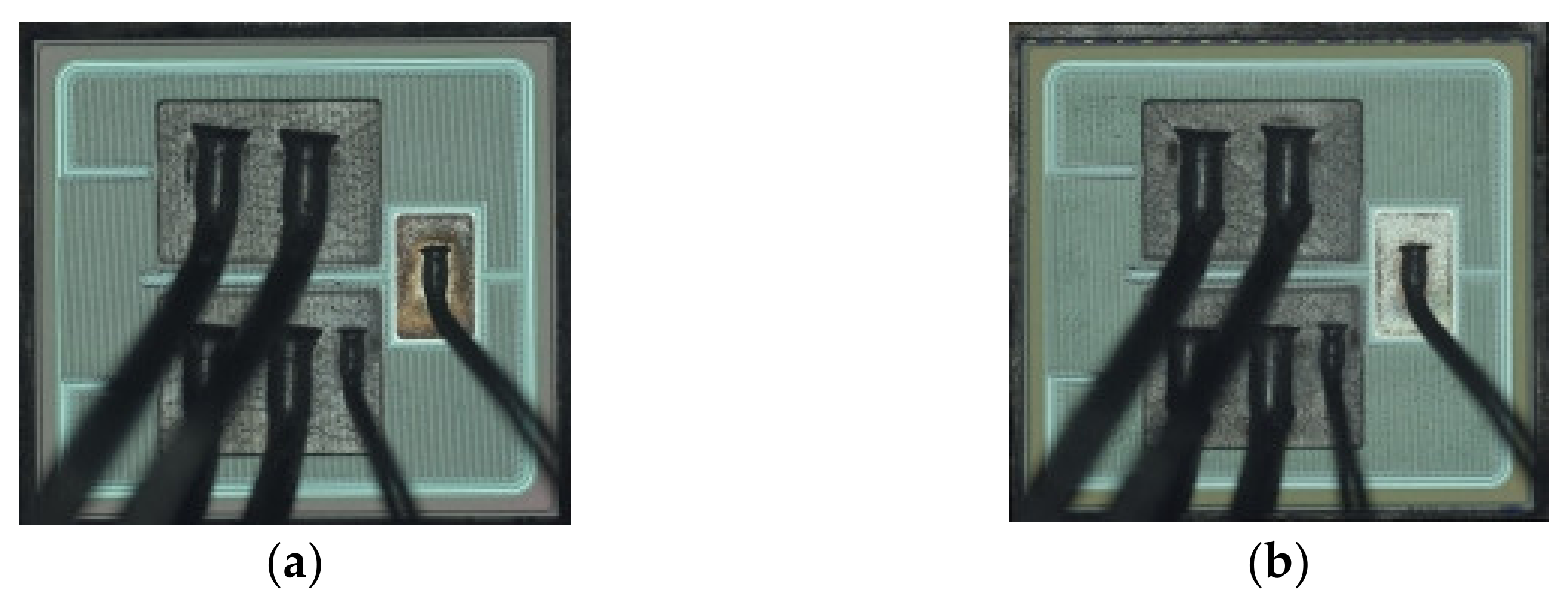

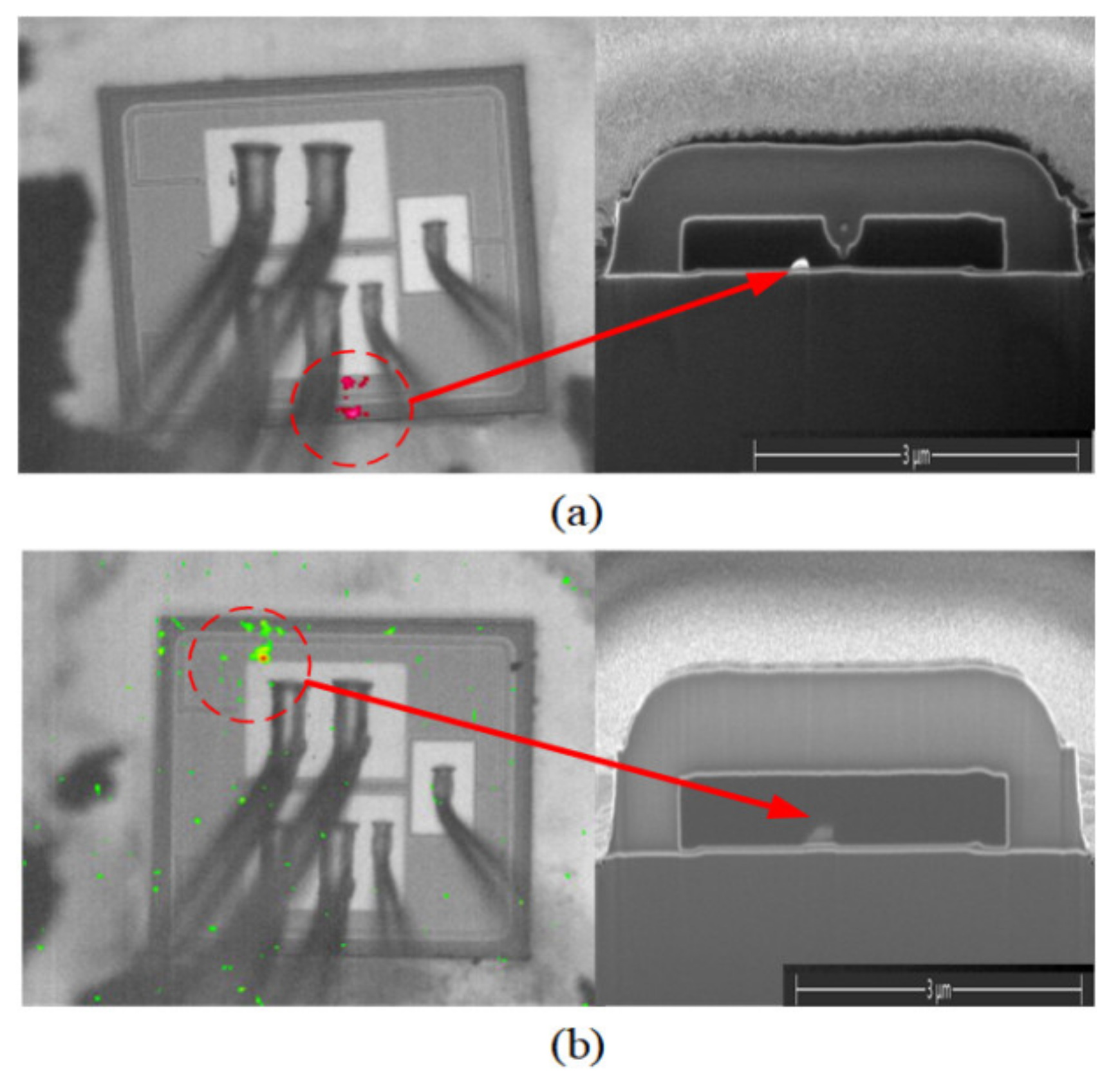

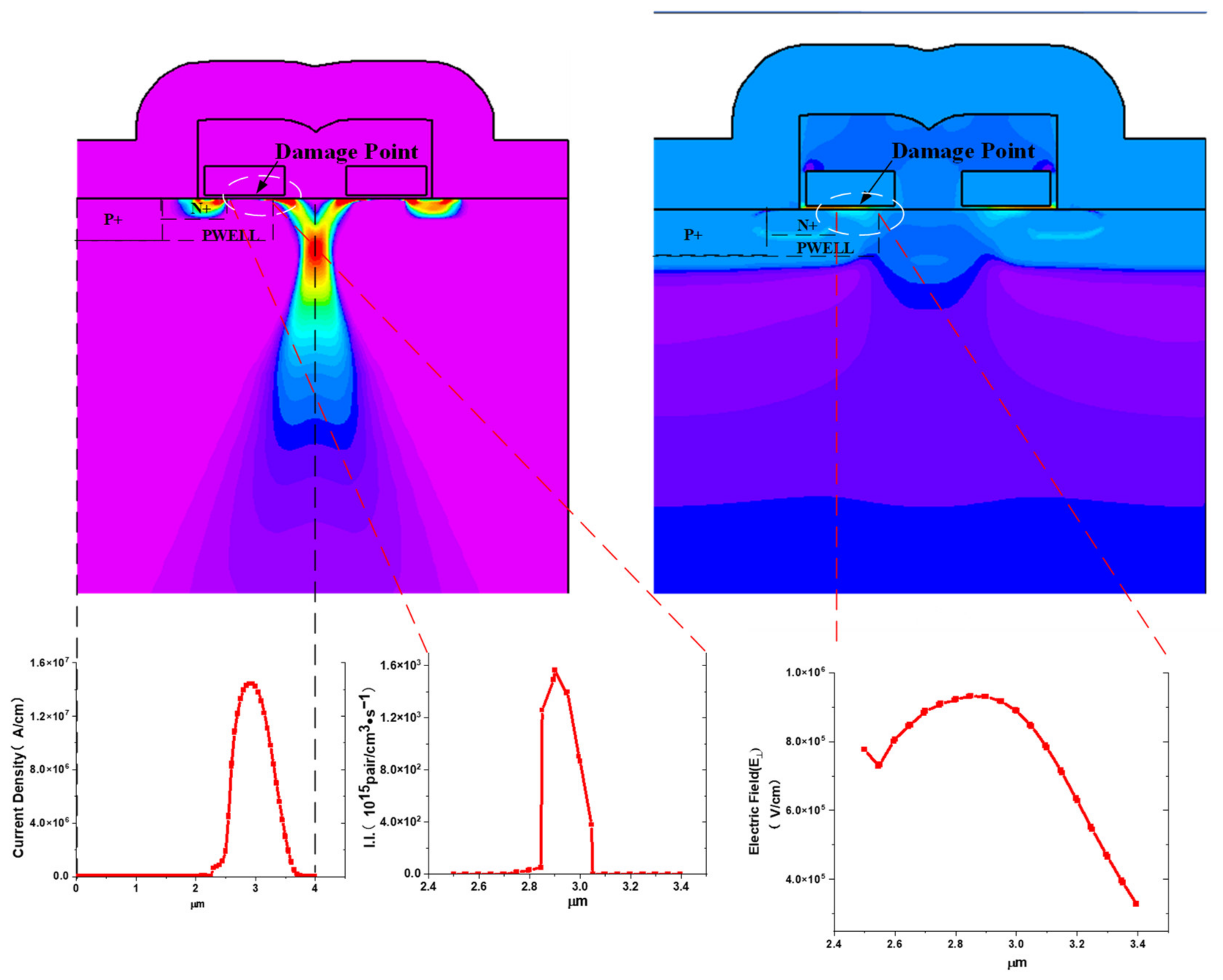

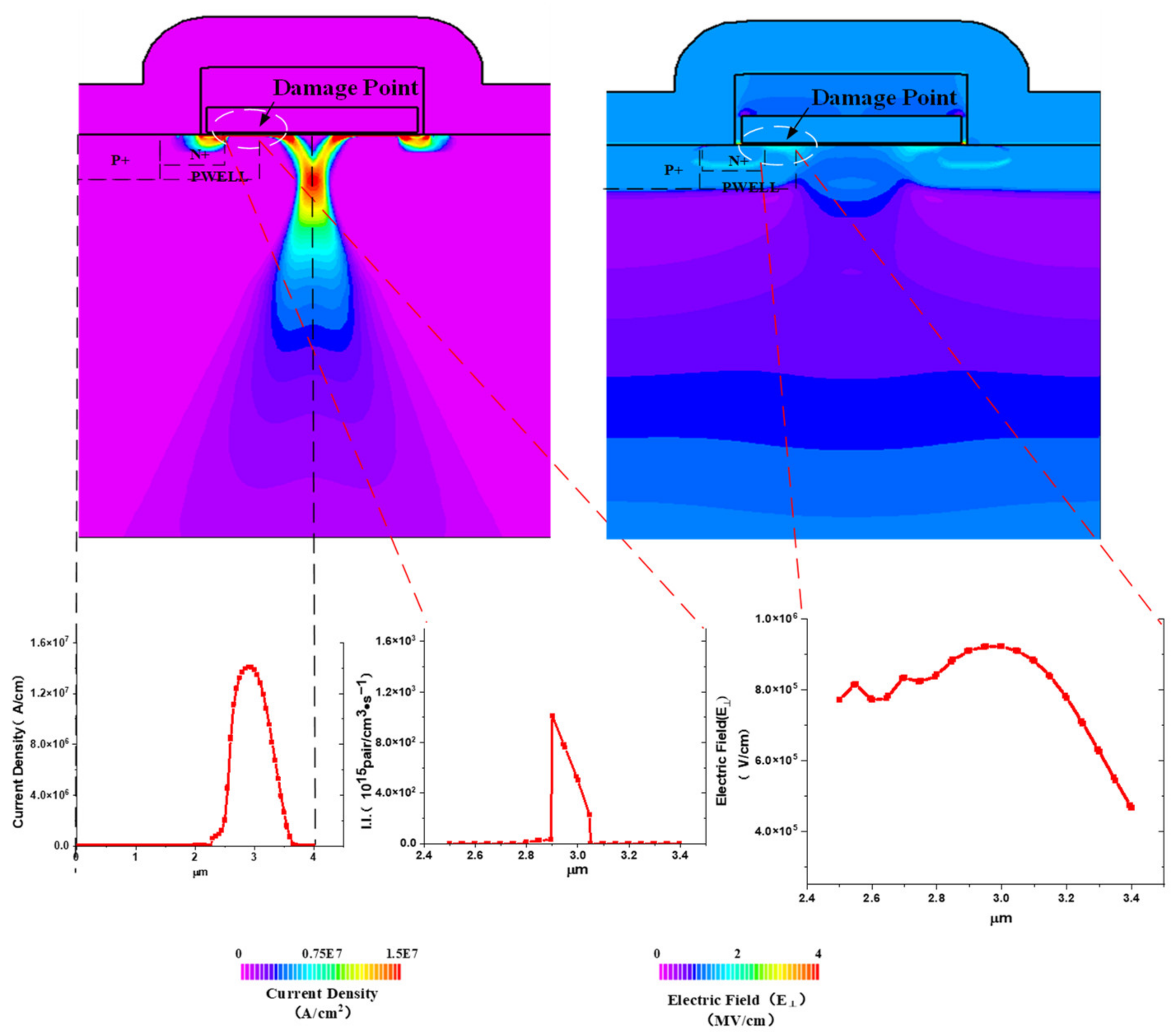

4.1. UIS Characteristics

4.2. Short-Circuit Characteristics

5. Conclusions

Author Contributions

Funding

Data Availability Statement

Acknowledgments

Conflicts of Interest

References

- Yoon, J.; Na, J.; Kim, K. A 1.2 kV SiC MOSFETs with Integrated Heterojunction Diode and P-shield Region. Energies 2021, 14, 8582. [Google Scholar] [CrossRef]

- Kimoto, T. Material science and device physics in SiC technology for high-voltage power devices. Jpn. J. Appl. Phys. 2015, 54, 040103. [Google Scholar] [CrossRef]

- Agarwal, A.; Han, K.; Baliga, B.J. 2.3 kV 4H-SiC Accumulation-Channel Split-Gate Planar Power MOSFETs with Reduced Gate Charge. IEEE J. Electron. Devices Soc. 2020, 8, 499–504. [Google Scholar] [CrossRef]

- Han, K.; Baliga, B.J.; Sung, W. Split-Gate 1.2-kV 4H-SIC MOSFETs: Analysis and Experimental Validation. IEEE Electron. Device Lett. 2017, 38, 1437–1440. [Google Scholar] [CrossRef]

- Yu, H.; Wang, J.; Liang, S.; Deng, G.; Liu, H.; Ji, B.; Shen, Z.J. 1.2-kV silicon carbide planar split-gate MOSFET with source field plate for superior figure-of-merits. IET Power Electron. 2022, 15, 1502–1510. [Google Scholar] [CrossRef]

- Han, Z.; Song, G.; Bai, Y.; Chen, H.; Liu, X.; Lu, J. A novel 4H-SiC MOSFET for low switching loss and high-reliability applications. Semicond. Sci. Technol. 2020, 35, 085017. [Google Scholar] [CrossRef]

- Han, K.; Baliga, B.J.; Sung, W. 1.2 kV 4H-SiC Split-Gate Power MOSFETs: Analysis and Experimental Results. Mater. Sci. Forum 2018, 924, 684–688. [Google Scholar]

- Yao, K.; Yano, H.; Tadano, H.; Iwamuro, N. Investigations of SiC MOSFETs Short-Circuit Failure Mechanisms Using Electrical, Thermal, and Mechanical Stress Analyses. IEEE Trans. Electron Devices 2020, 67, 4328–4334. [Google Scholar] [CrossRef]

- Agarwal, A.; Han, K.; Baliga, B.J. Comparison of 2.3 kV4H-SiC accumulation-channel planar MOSFETs fabricated with linear, square, hexagonal, and octagonal cell topologies. IEEE Trans. Electron Devices 2020, 67, 3673–3678. [Google Scholar] [CrossRef]

- Agarwal, A.; Han, K.; Baliga, B.J. 2.3 kV 4H-SiC accumulation channel JBSFETs: Experimental comparison of linear, hexagonal and octagonal cell topologies. In Proceedings of the 2020 Device Research Conference (DRC), Columbus, OH, USA, 21–24 June 2020; pp. 84–85. [Google Scholar]

- Baliga, B.J. Fundamentals of Power Semiconductor Devices, 2nd ed.; Springer: Cham, Switzerland, 2019; Chapter 6; pp. 283–440. [Google Scholar]

- Han, K.; Baliga, B.J. Comparison of four cell topologies for 1.2-kV accumulation-and inversion-channel 4H-SiC MOSFETs: Analysis and experimental results. IEEE Trans. Electron Devices 2019, 66, 2321–2326. [Google Scholar] [CrossRef]

- Jiang, H.; Wei, J.; Dai, X.; Ke, M.; Devany, I.; Mawby, P. SiC trench MOSFET with shielded fin-shaped gate to reduce oxide field and switching loss. IEEE Electron Device Lett. 2016, 37, 1324–1327. [Google Scholar] [CrossRef]

- Agarwal, A.; Han, K.J.; Baliga, B.J. Impact of cell topology on characteristics of 600 V 4H-SiC planar MOSFETs. IEEE Electron. Device Lett. 2019, 40, 773–776. [Google Scholar] [CrossRef]

- Xu, H.; Lin, C.; Ren, N.; Gan, X.; Liu, L.; Zhu, Z.; Liu, L.; Guo, Q.; Jiang, J.; Sheng, K. Comparison Study on Short Circuit Capability of 1.2 kV Split-Gate MOSFETs and Split-Source MOSFETs with Integrated JBS Diode. In Proceedings of the 2021 IEEE Workshop on Wide Bandgap Power Devices and Applications in Asia (WiPDA Asia), Wuhan, China, 25–27 August 2021. [Google Scholar]

- Han, K.; Baliga, B.J.; Sung, W. A novel 1.2 kV 4H-SiC buffered gate (BG) MOSFETs: Analysis and experimental results. IEEE Electron. Device Lett. 2018, 39, 248–251. [Google Scholar] [CrossRef]

- Zhu, Z.; Xu, H.; Liu, L.; Ren, N.; Sheng, K. Investigation on Surge Current Capability of 4H-SiC Trench-Gate MOSFETs in Third Quadrant Under Various VGS Biases. IEEE J. Emerg. Sel. Top. Power Electron. 2020, 9, 3028094. [Google Scholar]

- Tsibizov, A.; Kovačević-Badstübner, I.; Kakarla, B.; Grossner, U. Accurate Temperature Estimation of SiC Power MOSFETs under Extreme Operating Conditions. IEEE Trans. Power Electron. 2020, 35, 1855–1865. [Google Scholar] [CrossRef]

- Liu, J.; Zhang, G.; Wang, B.; Li, W.; Wang, J. Gate Failure Physics of SiC MOSFETs under Short-circuit Stress. IEEE Electron Device Lett. 2020, 41, 103–106. [Google Scholar] [CrossRef]

- Fayyaz, A.; Castellazzi, A.; Romano, G.; Riccio, M.; Irace, A.; Urresti, J.; Wright, N. Influence of gate bias on the avalanche ruggedness of SiC power MOSFETs. In Proceedings of the International Symposium on Power Semiconductor Devices and ICs, Sapporo, Japan, 28 May–1 June 2017; pp. 391–394. [Google Scholar]

| Parameters | SG-MOSFET | PG-MOSFET |

|---|---|---|

| Tdrift/Ndrift | 10 μm/9 × 15 cm−3 | 10 μm/9 × 15 cm−3 |

| NCSL | 1 × 17 cm−3 | 1 × 17 cm−3 |

| TPbase/NPbase | 0.7 μm/1 × 18 cm−3 | 0.7 μm/1 × 18 cm−3 |

| LCH | 0.4 μm | 0.4 μm |

| WJEFT | 1.8 μm | 1.8 μm |

| Sox | 1.5 μm × 0.5 μm | - |

| WCELL | 8.2 μm | 8.2 μm |

| Parameters | PG-MOSFET | SG-MOSFET | Change |

|---|---|---|---|

| Threshold voltage (V) | 2.6 | 2.65 | 2% |

| RON (mΩ) | 78.1 | 80 | 2% |

| RON(SP) (mΩ·cm2) | 5 | 5.12 | 2.4% |

| Breakdown voltage (V) | 1609 | 1609 | 0% |

| VSD@VGS = −4 V | 4.6 | 4.6 | 0% |

| Ciss@VDS = 0 V (pF) | 2073 | 1932 | 6.8% |

| Coss@VDS = 0 V (pF) | 2237 | 2068 | 7.6% |

| Crss@VDS = 0 V (pF) | 914 | 756 | 17.3% |

| Qg(nC)@VGS = 20 V | 80 | 72 | 10% |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2023 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Liu, H.; Wei, J.; Wei, Z.; Liu, S.; Shi, L. Experimental Comparison of a New 1.2 kV 4H-SiC Split-Gate MOSFET with Conventional SiC MOSFETs in Terms of Reliability Robustness. Electronics 2023, 12, 2551. https://doi.org/10.3390/electronics12112551

Liu H, Wei J, Wei Z, Liu S, Shi L. Experimental Comparison of a New 1.2 kV 4H-SiC Split-Gate MOSFET with Conventional SiC MOSFETs in Terms of Reliability Robustness. Electronics. 2023; 12(11):2551. https://doi.org/10.3390/electronics12112551

Chicago/Turabian StyleLiu, Hao, Jiaxing Wei, Zhaoxiang Wei, Siyang Liu, and Longxing Shi. 2023. "Experimental Comparison of a New 1.2 kV 4H-SiC Split-Gate MOSFET with Conventional SiC MOSFETs in Terms of Reliability Robustness" Electronics 12, no. 11: 2551. https://doi.org/10.3390/electronics12112551