High Step-Up Converter

Abstract

:1. Introduction

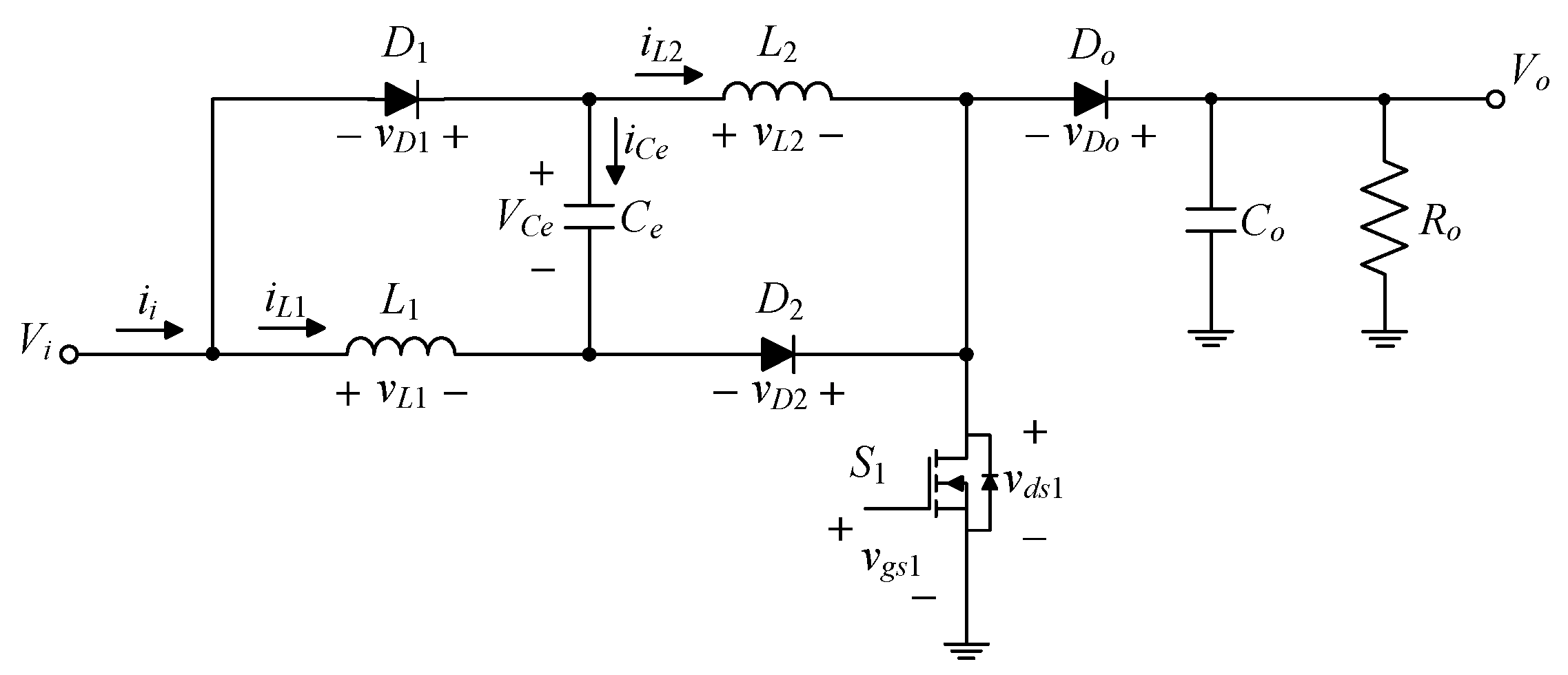

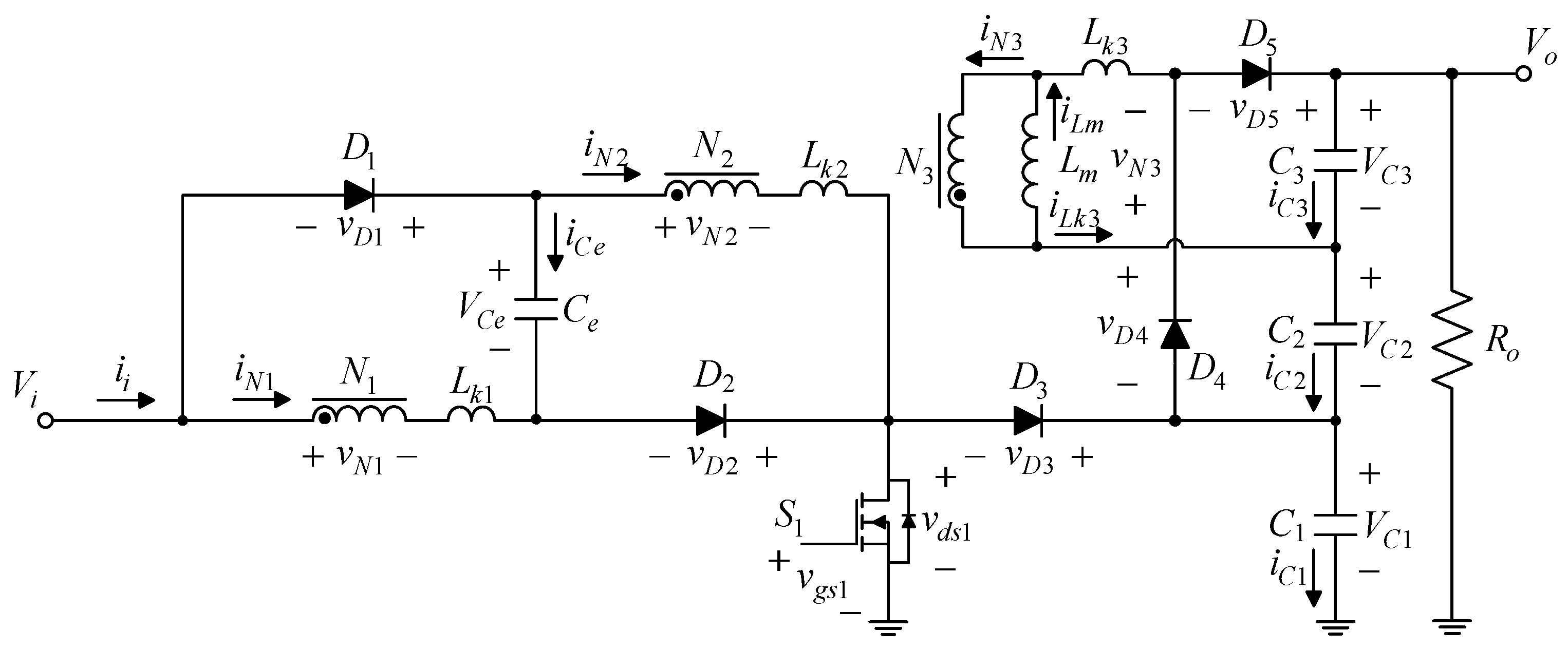

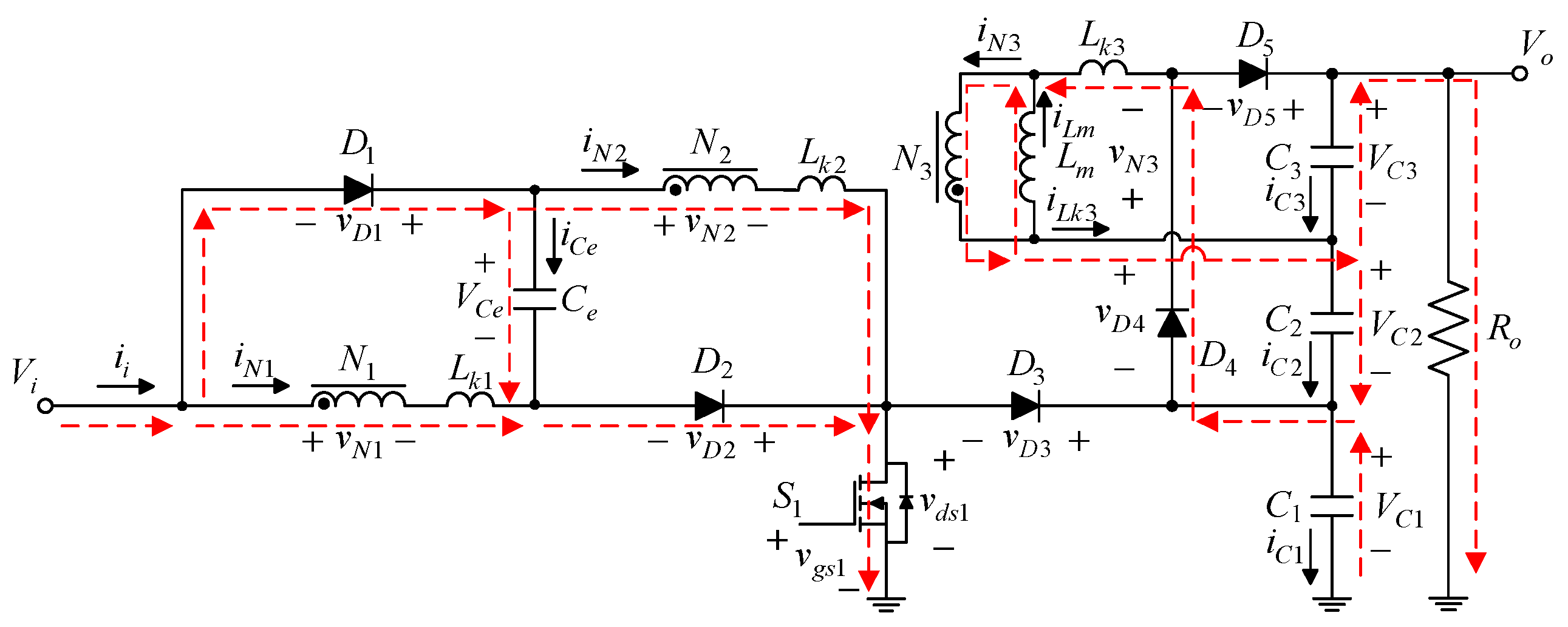

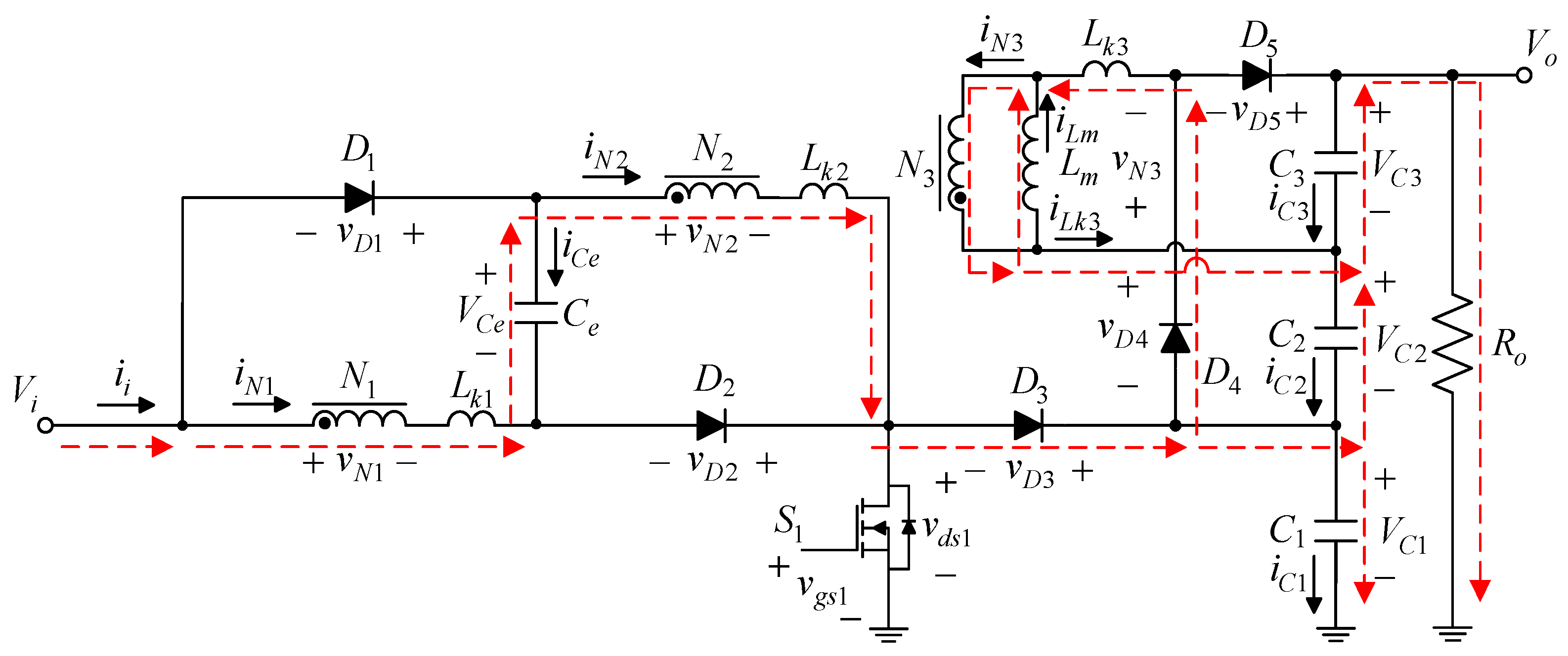

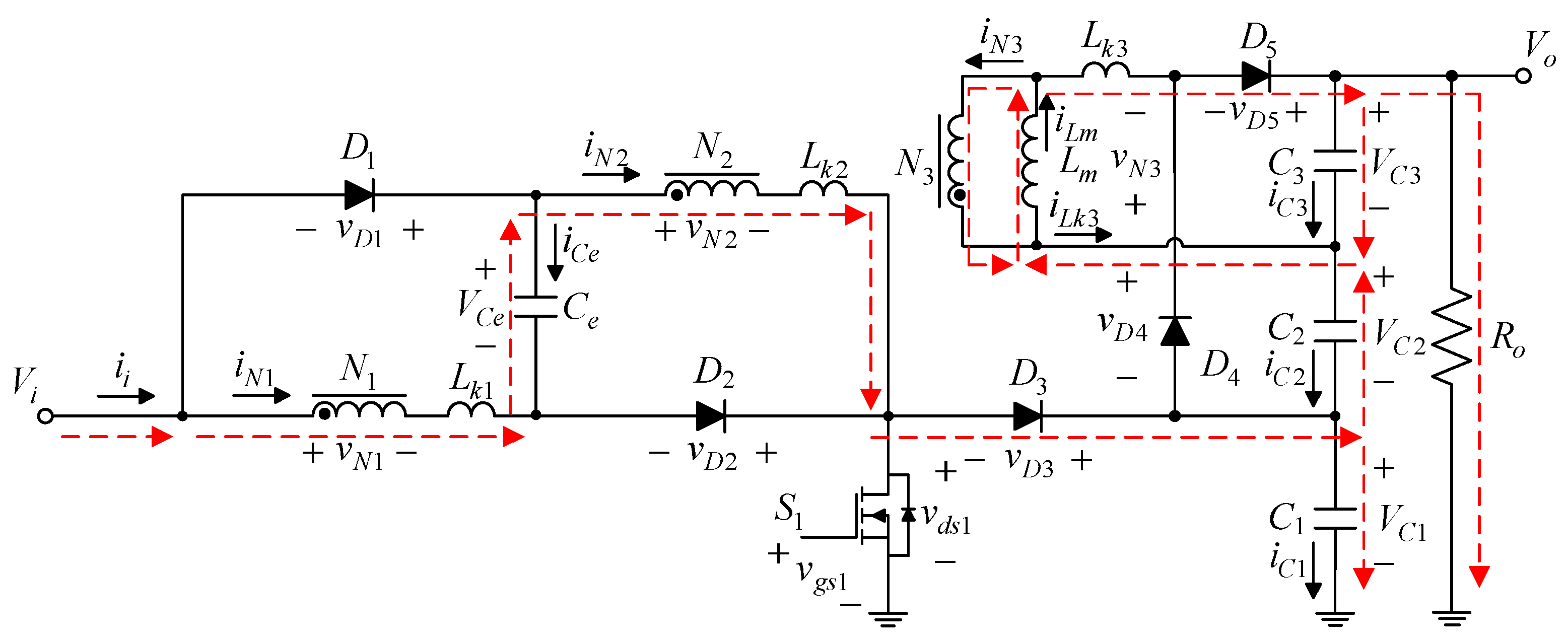

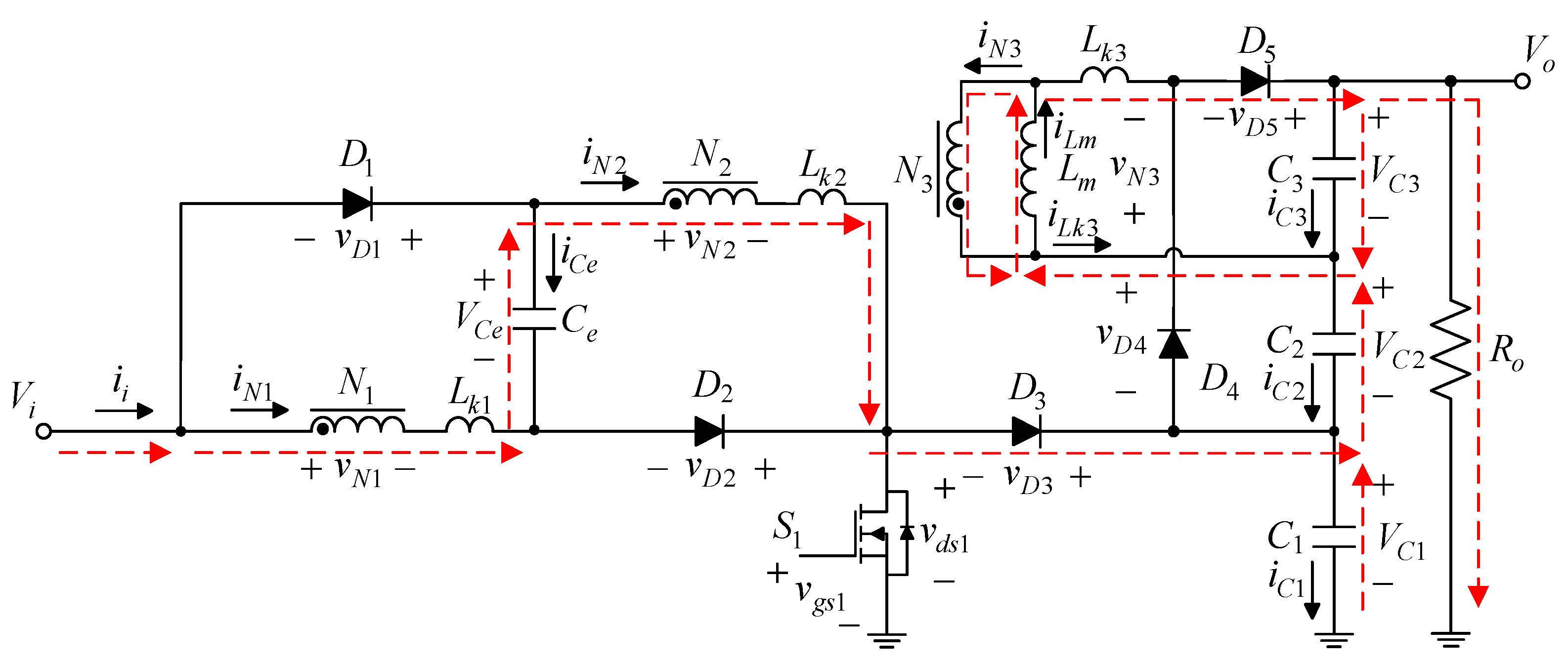

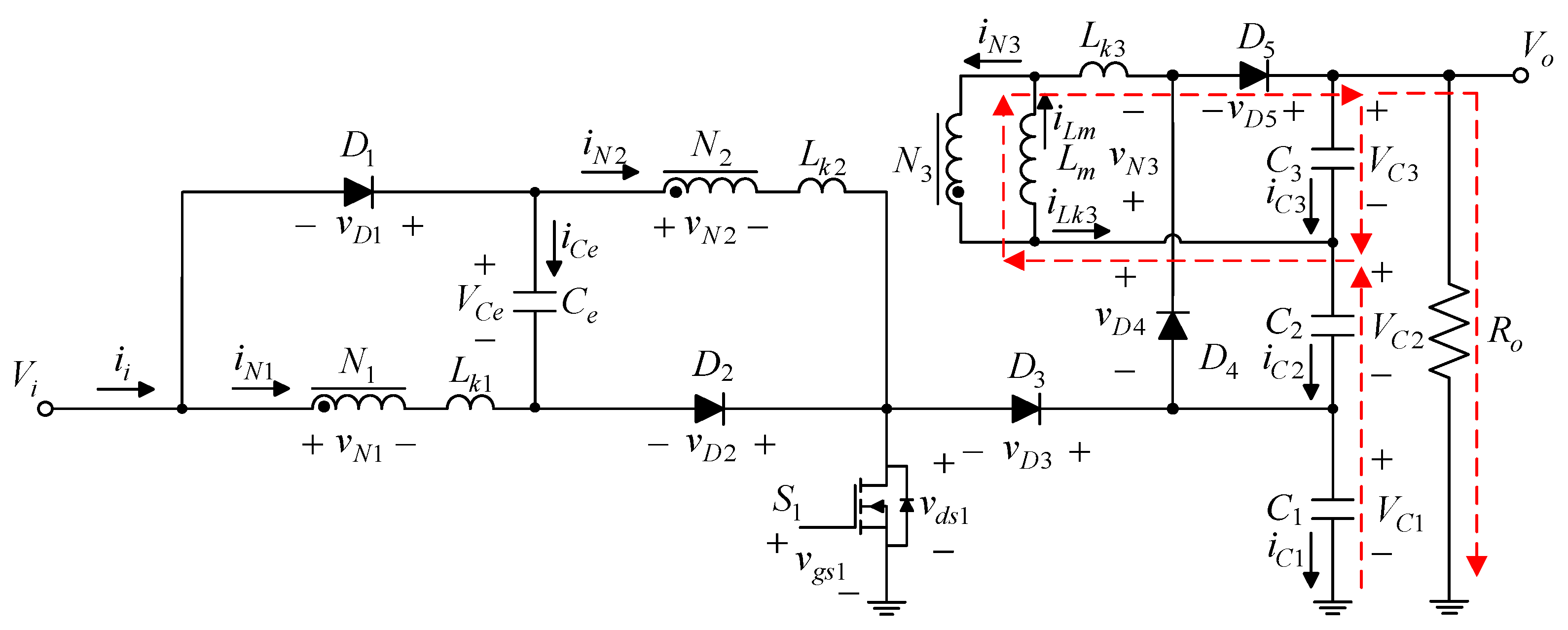

2. Proposed High-Boost Converter

2.1. Topology Description

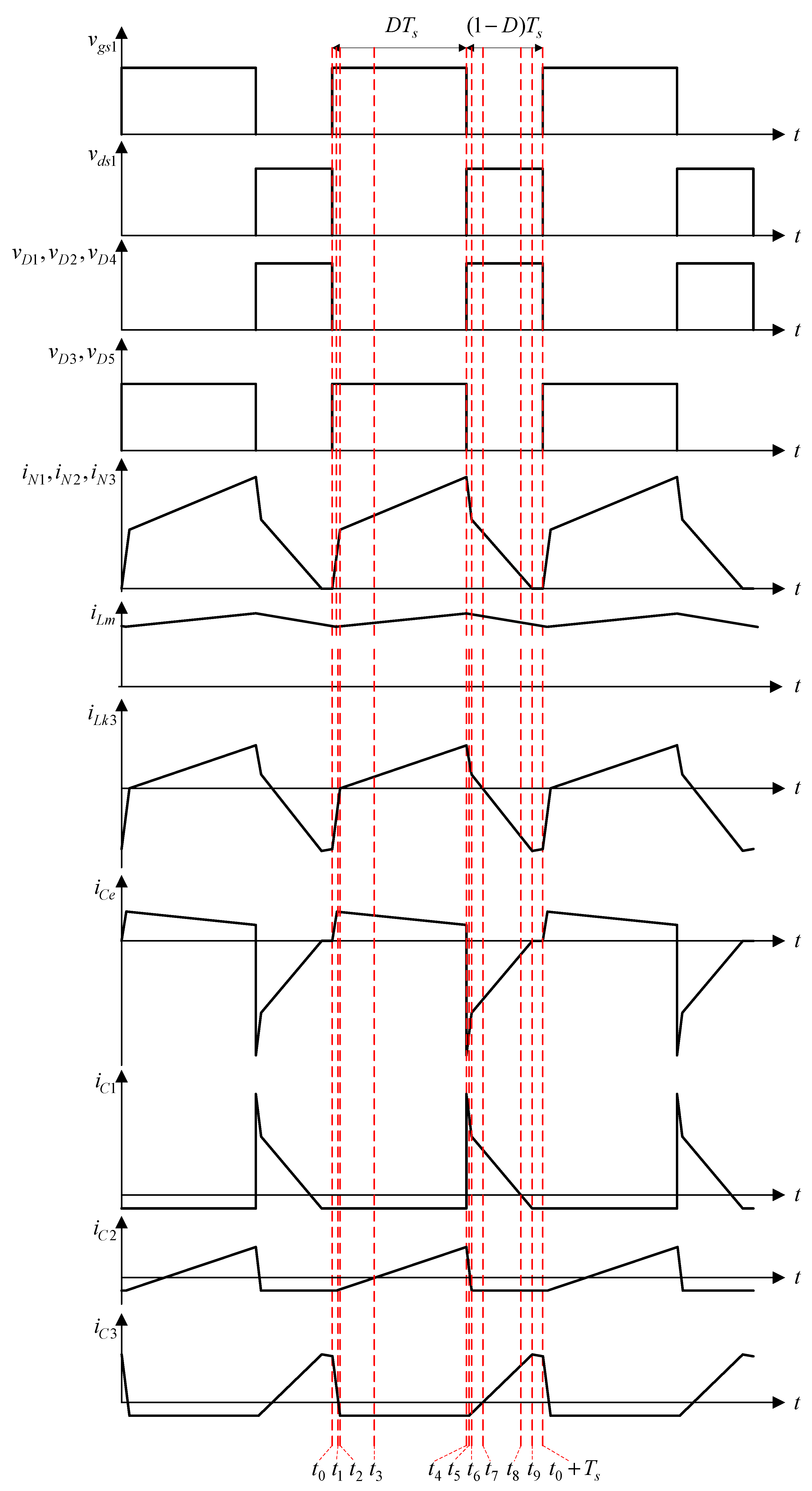

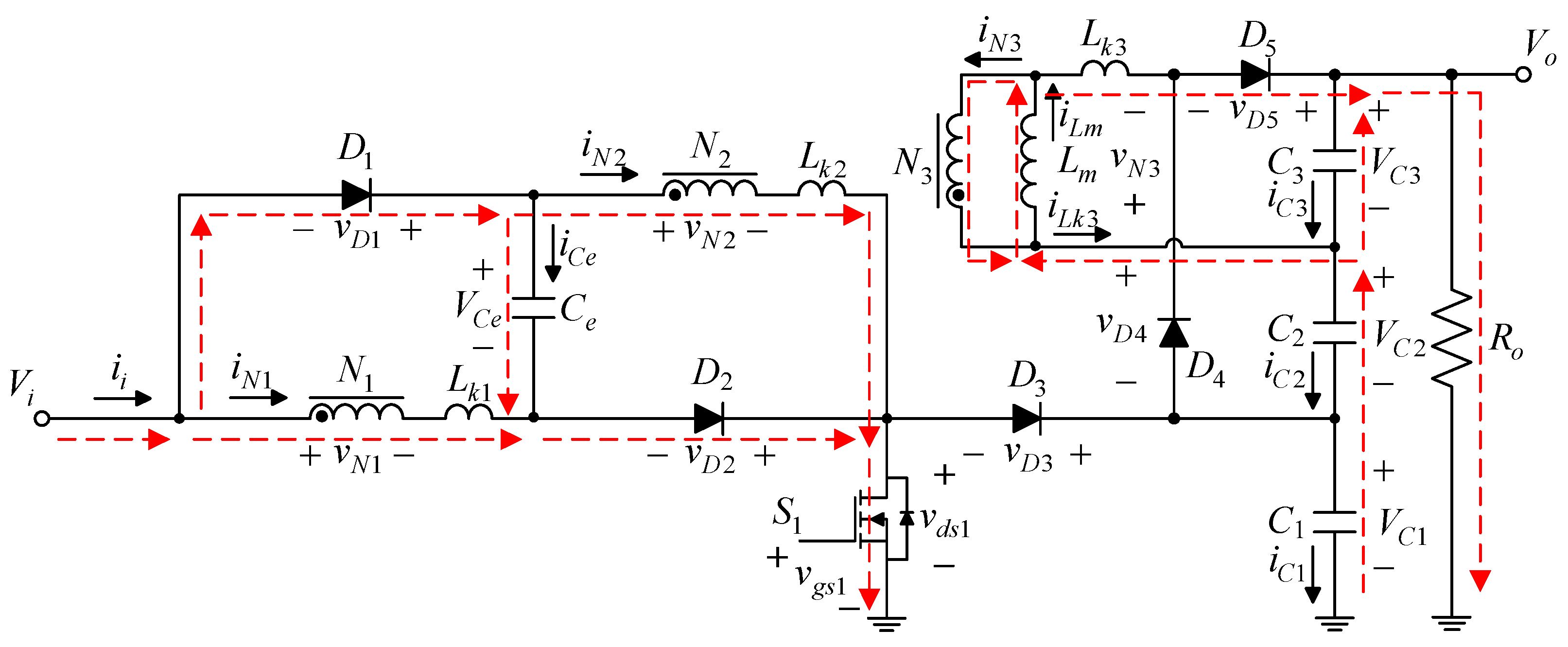

2.2. Operating Principles

2.2.1. State 1: []

2.2.2. State 2: []

2.2.3. State 3: []

2.2.4. State 4: []

2.2.5. State 5: []

2.2.6. State 6: []

2.2.7. State 7: []

2.2.8. State 8: []

2.2.9. State 9: []

2.2.10. State 10: []

2.3. Voltage Gain

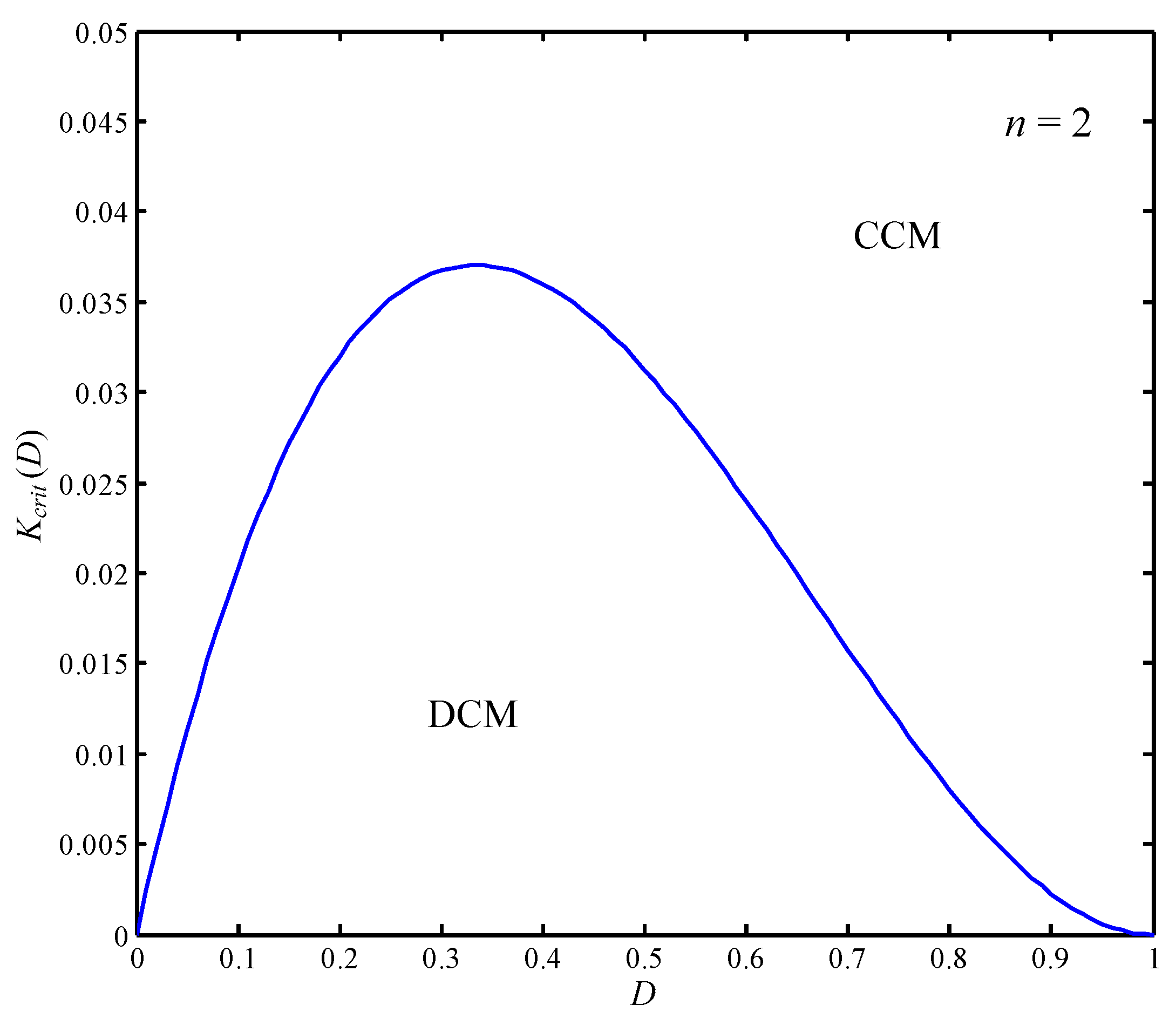

2.4. Boundary Curve between Operating Modes of Lm

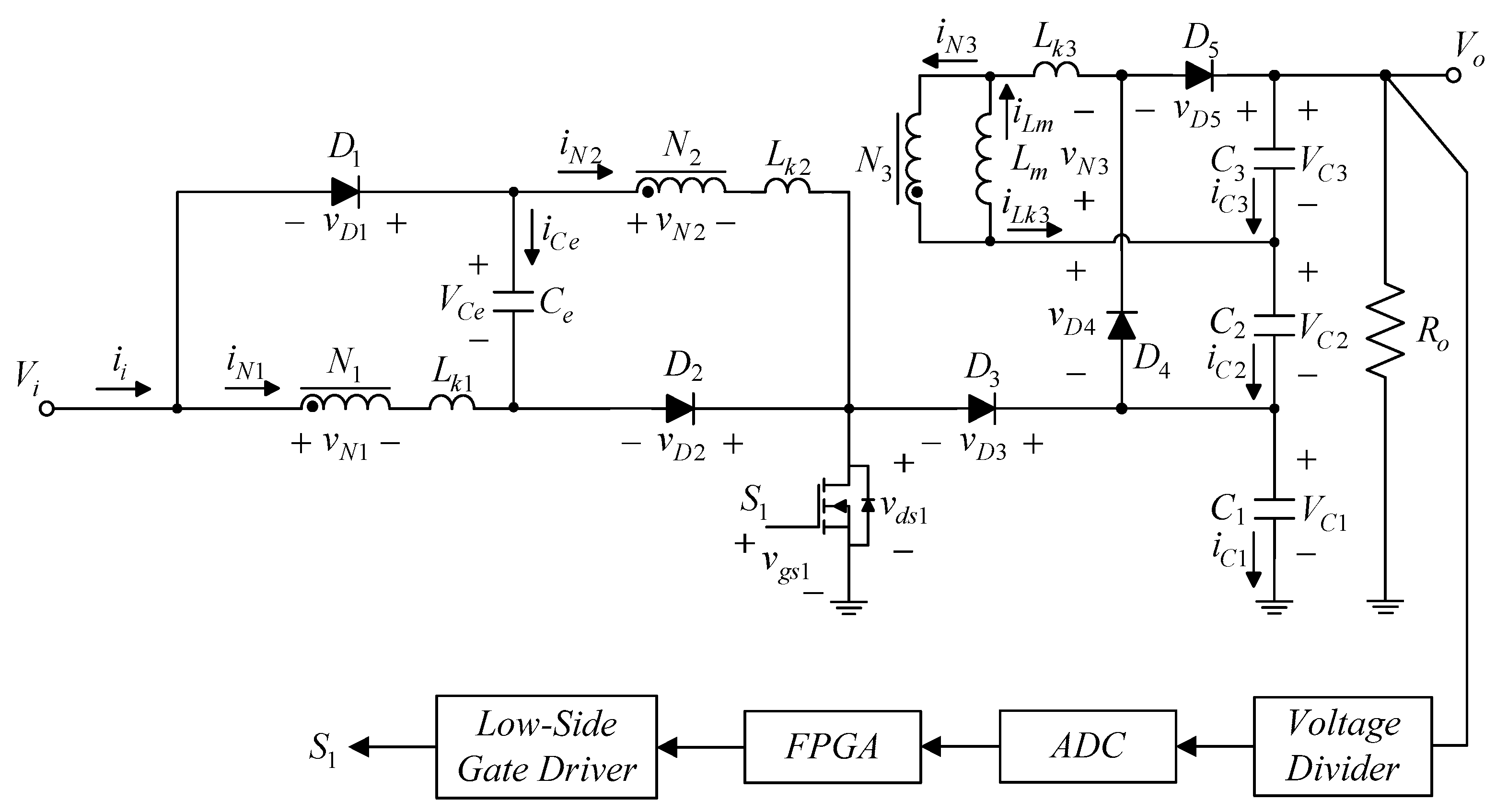

3. System and Component Specifications

4. Design Considerations

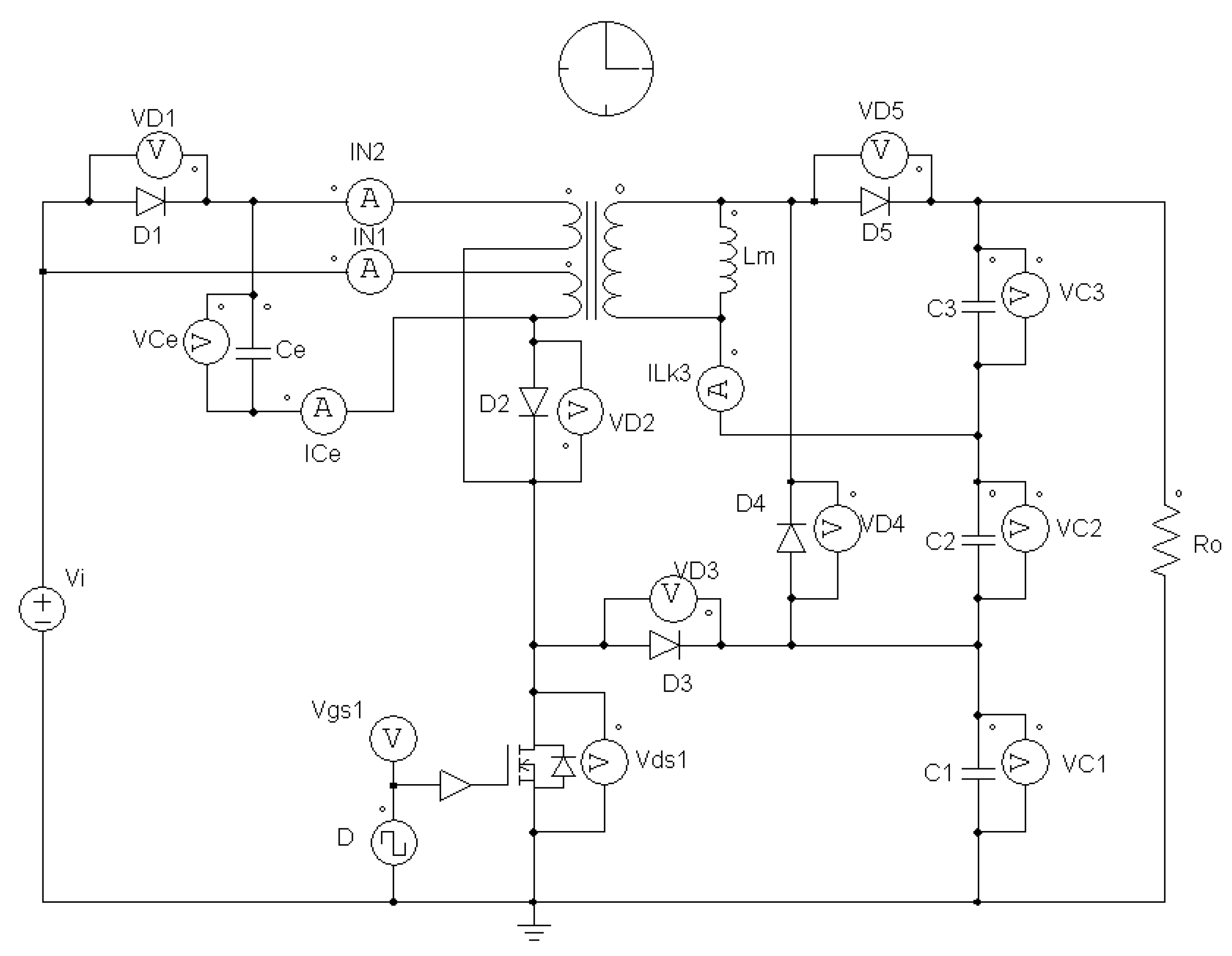

5. Simulated Waveforms

6. Measured Waveforms

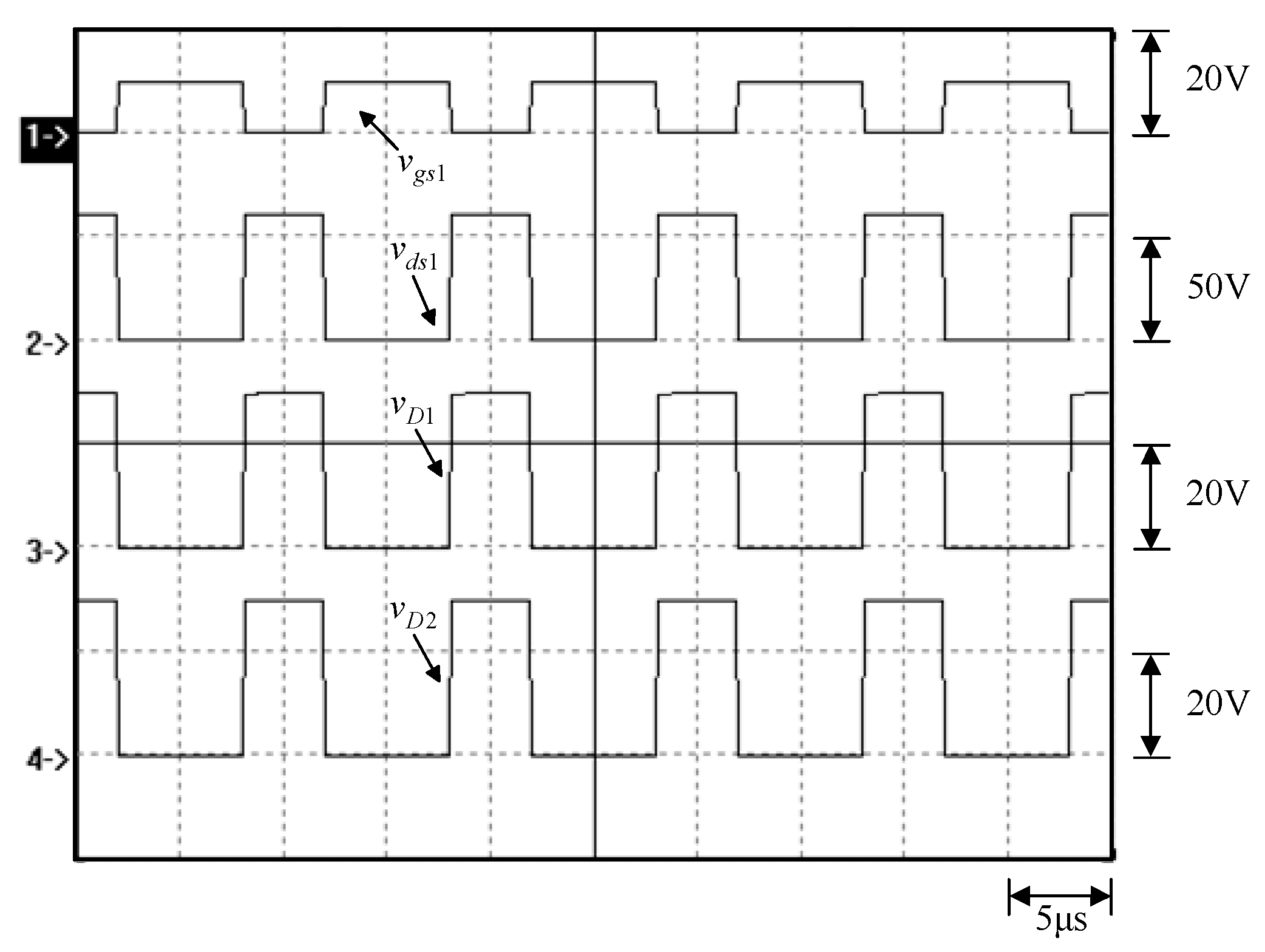

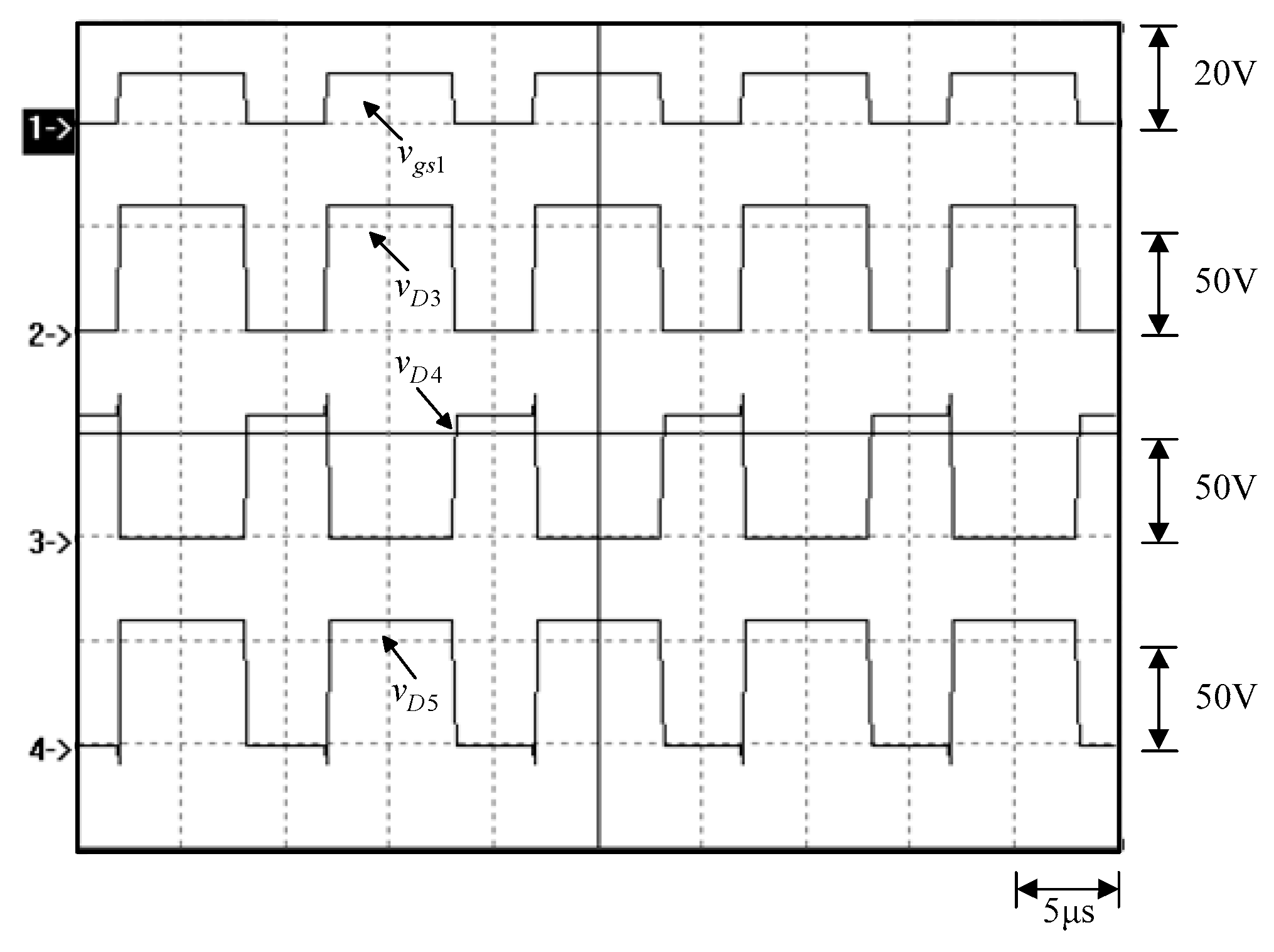

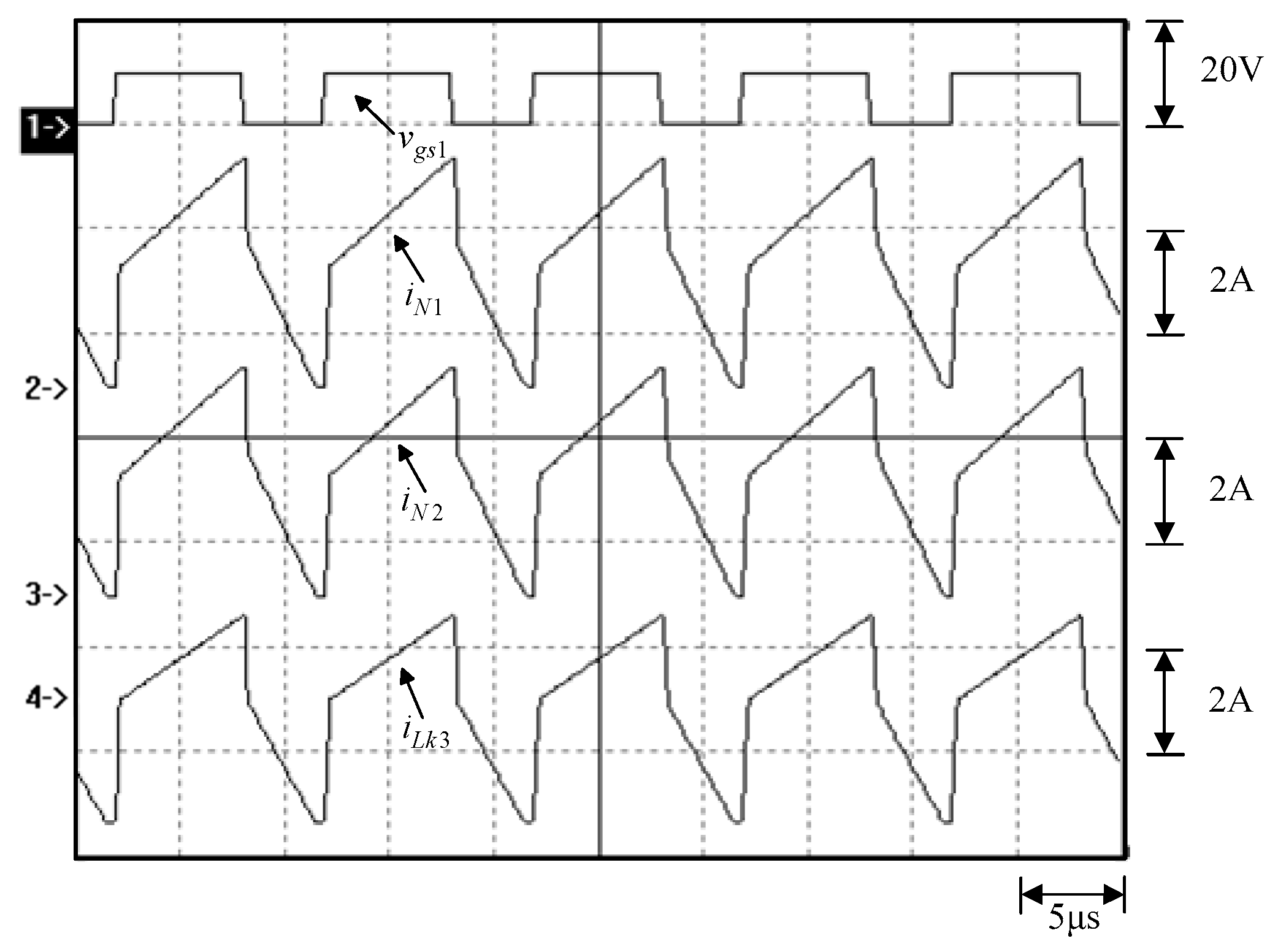

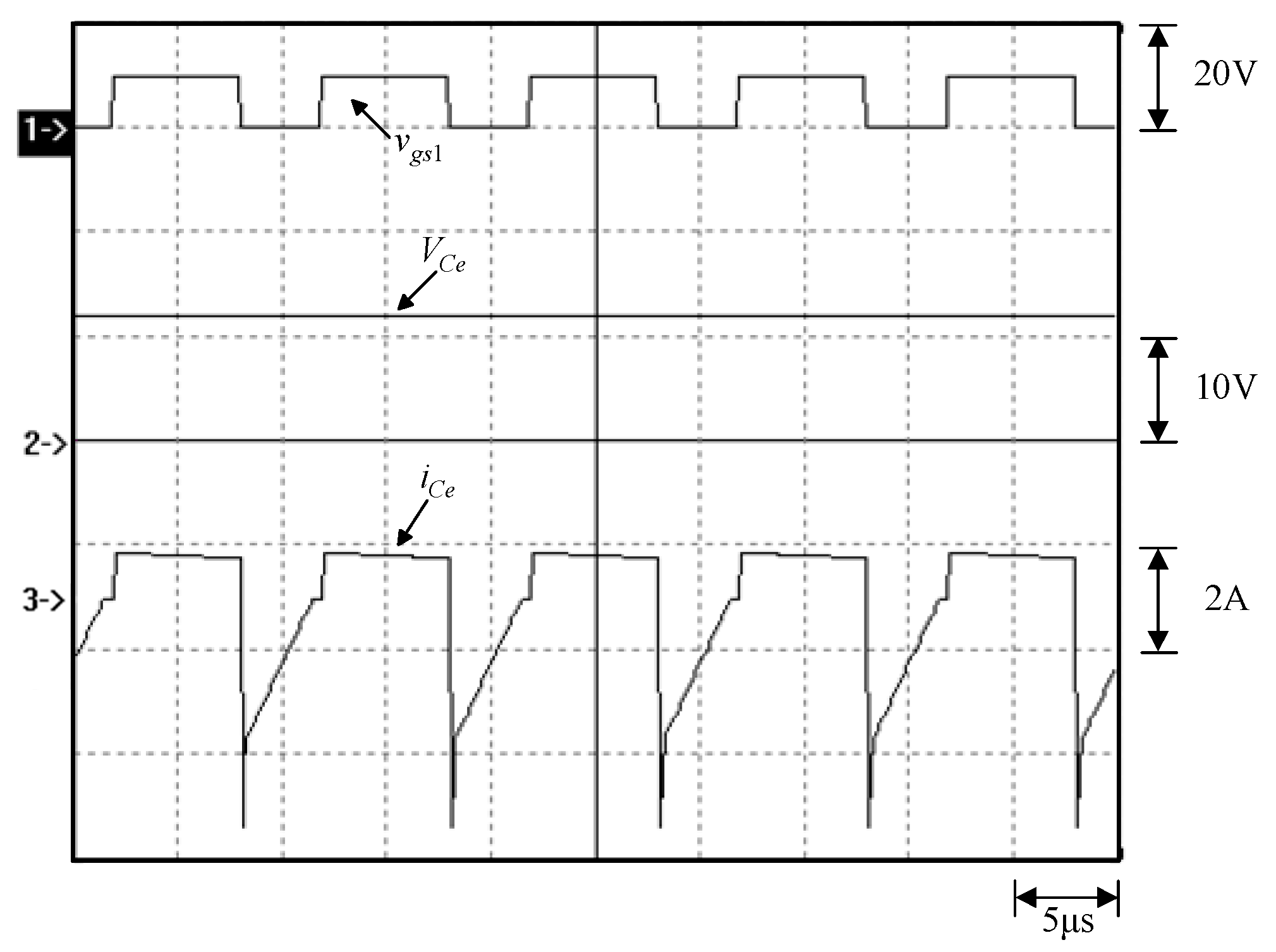

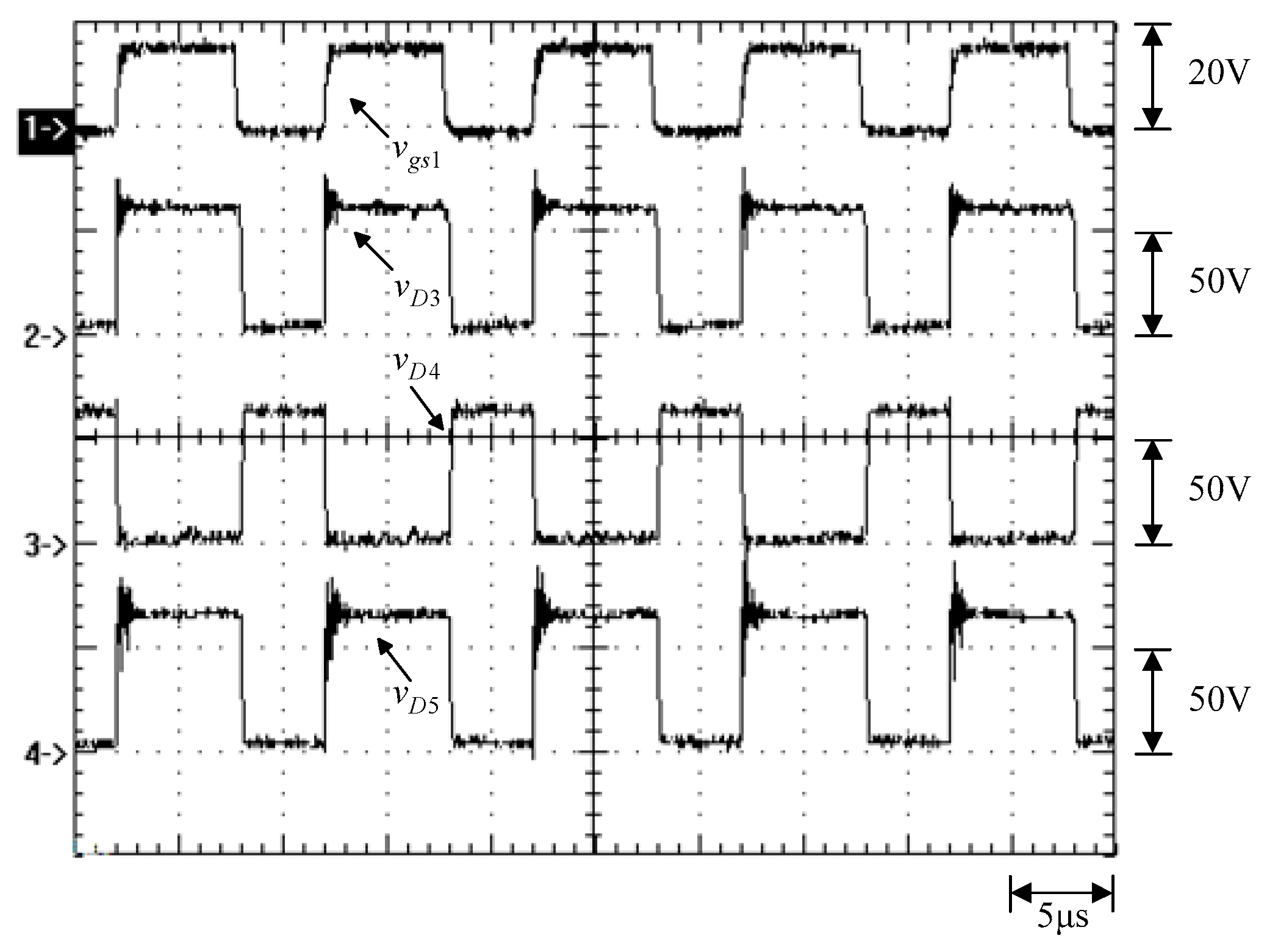

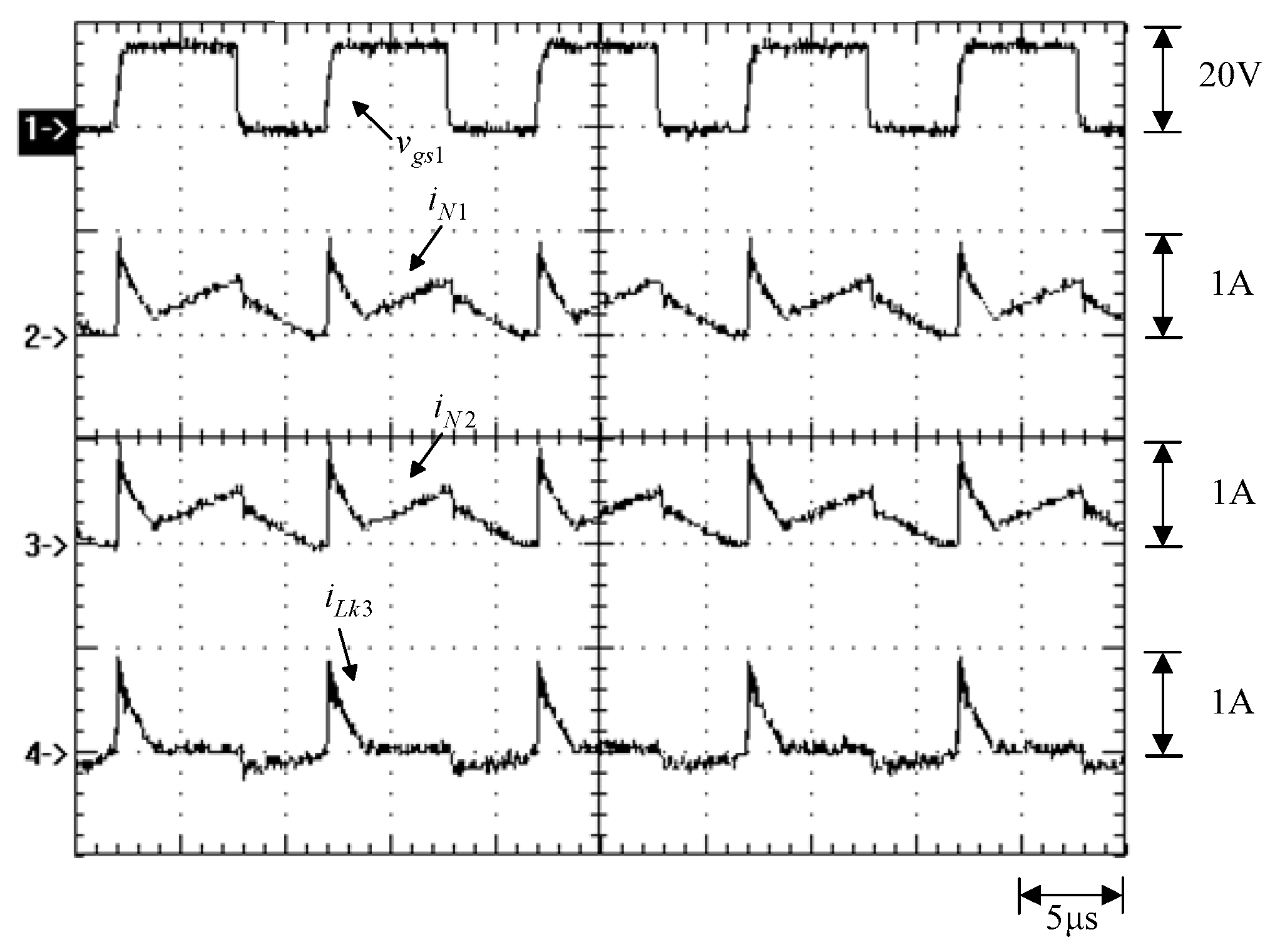

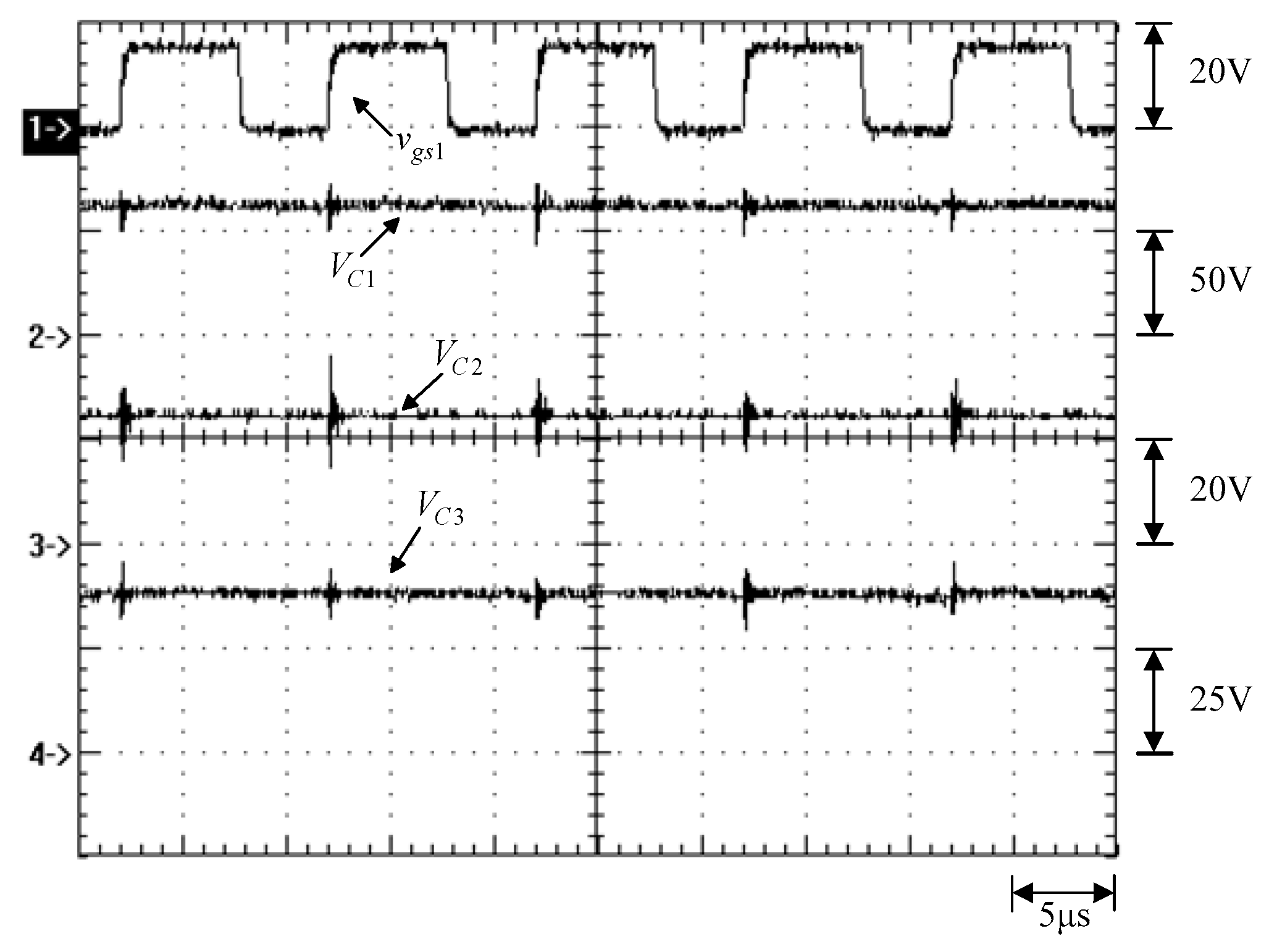

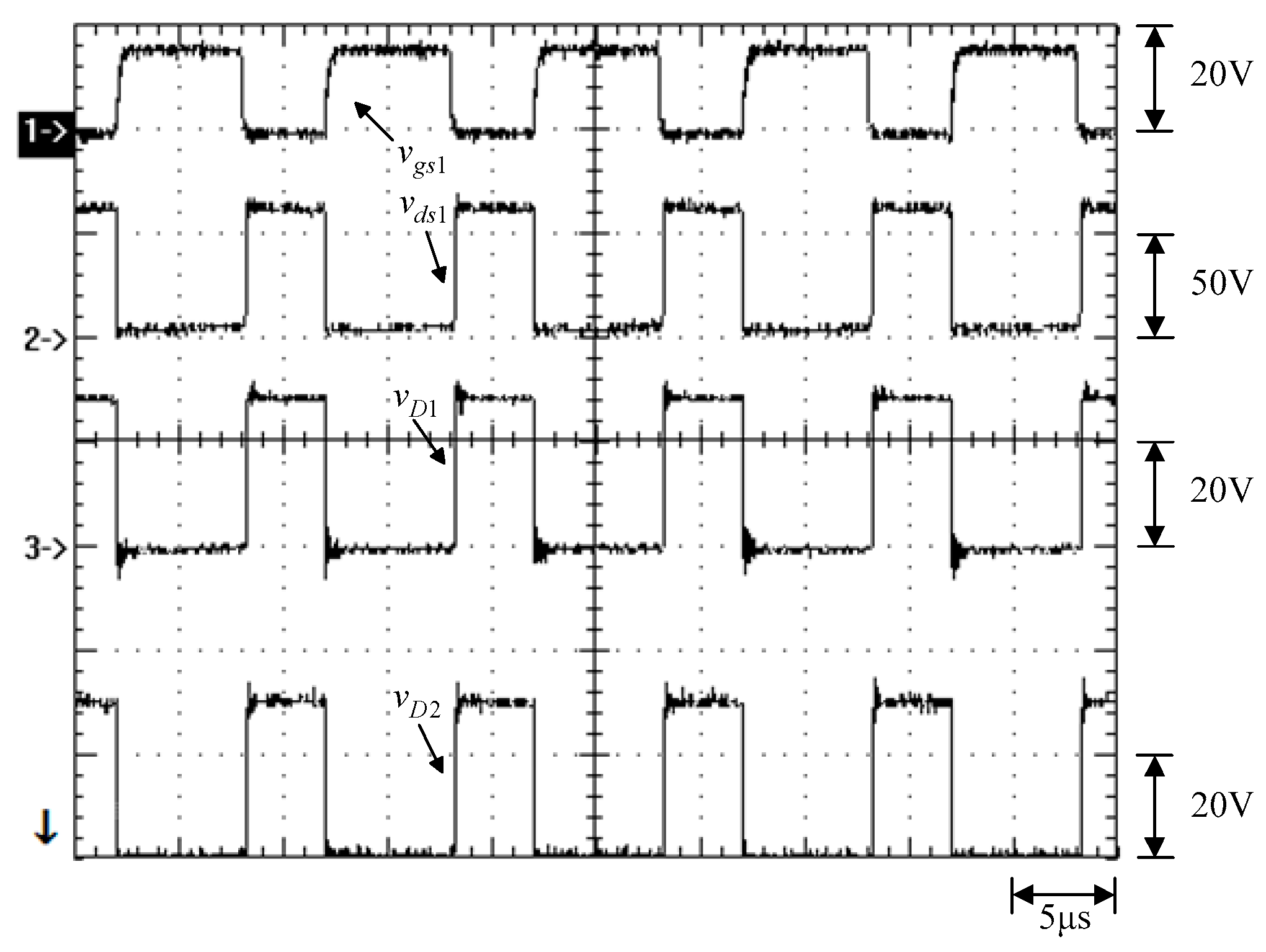

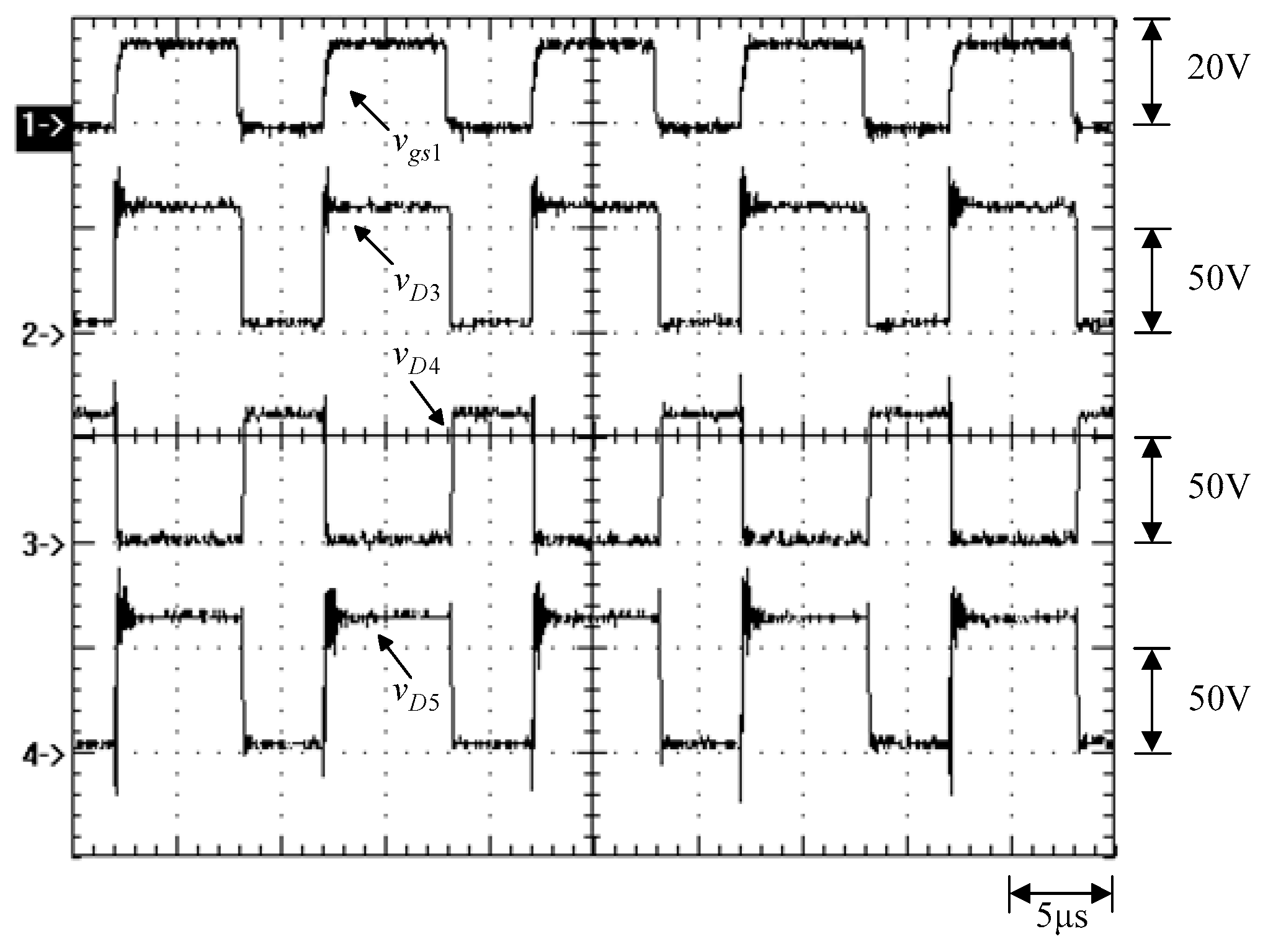

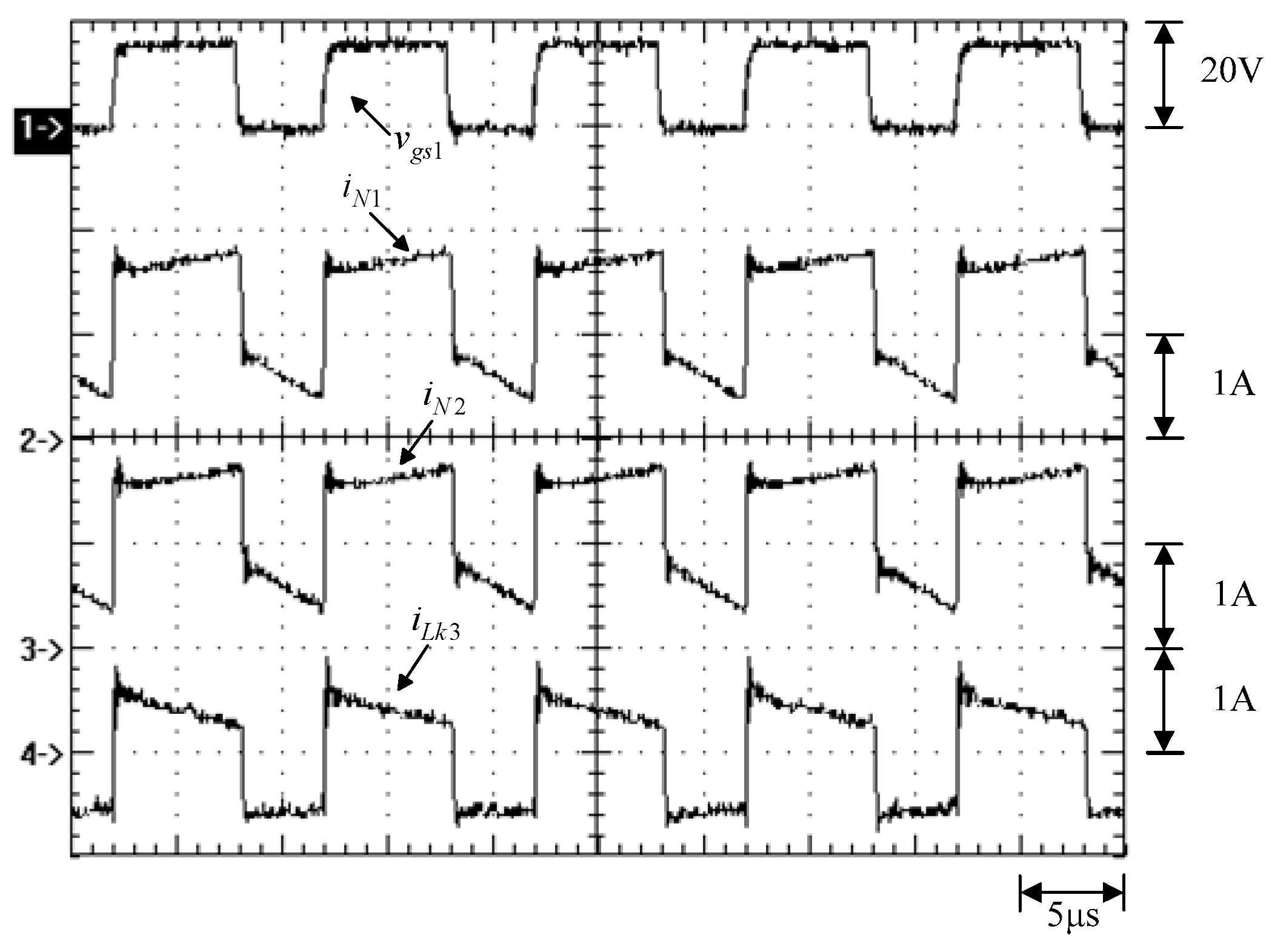

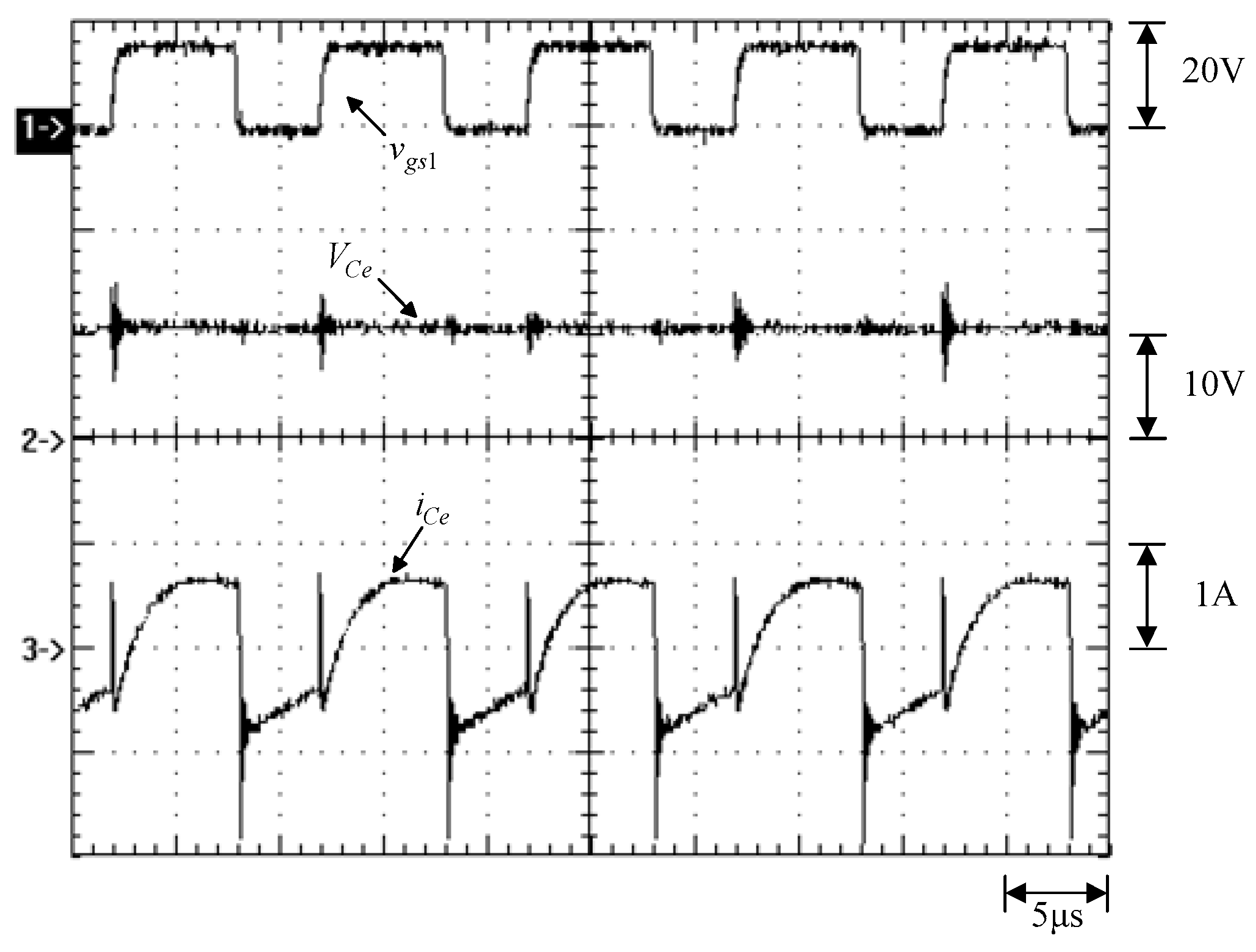

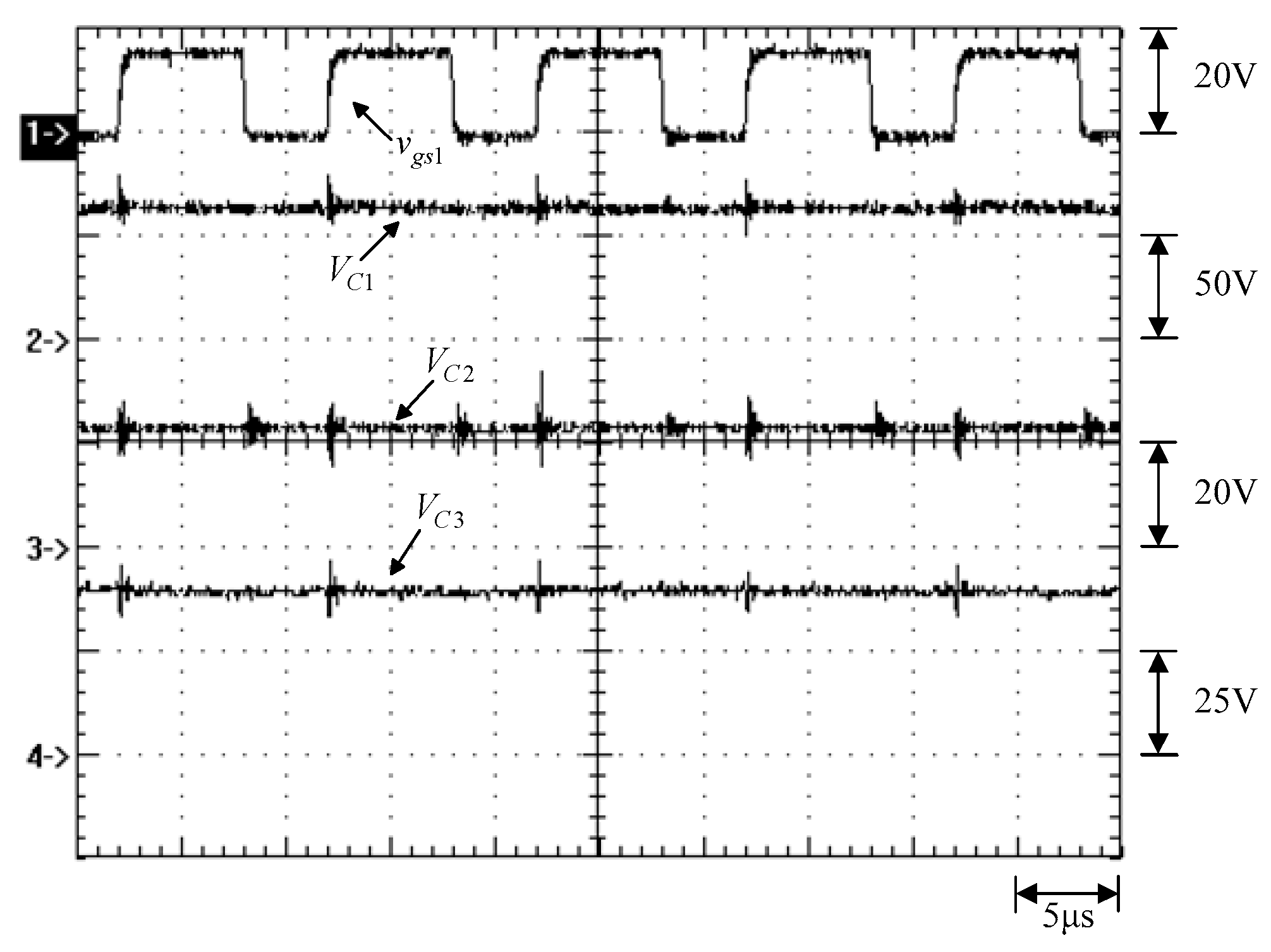

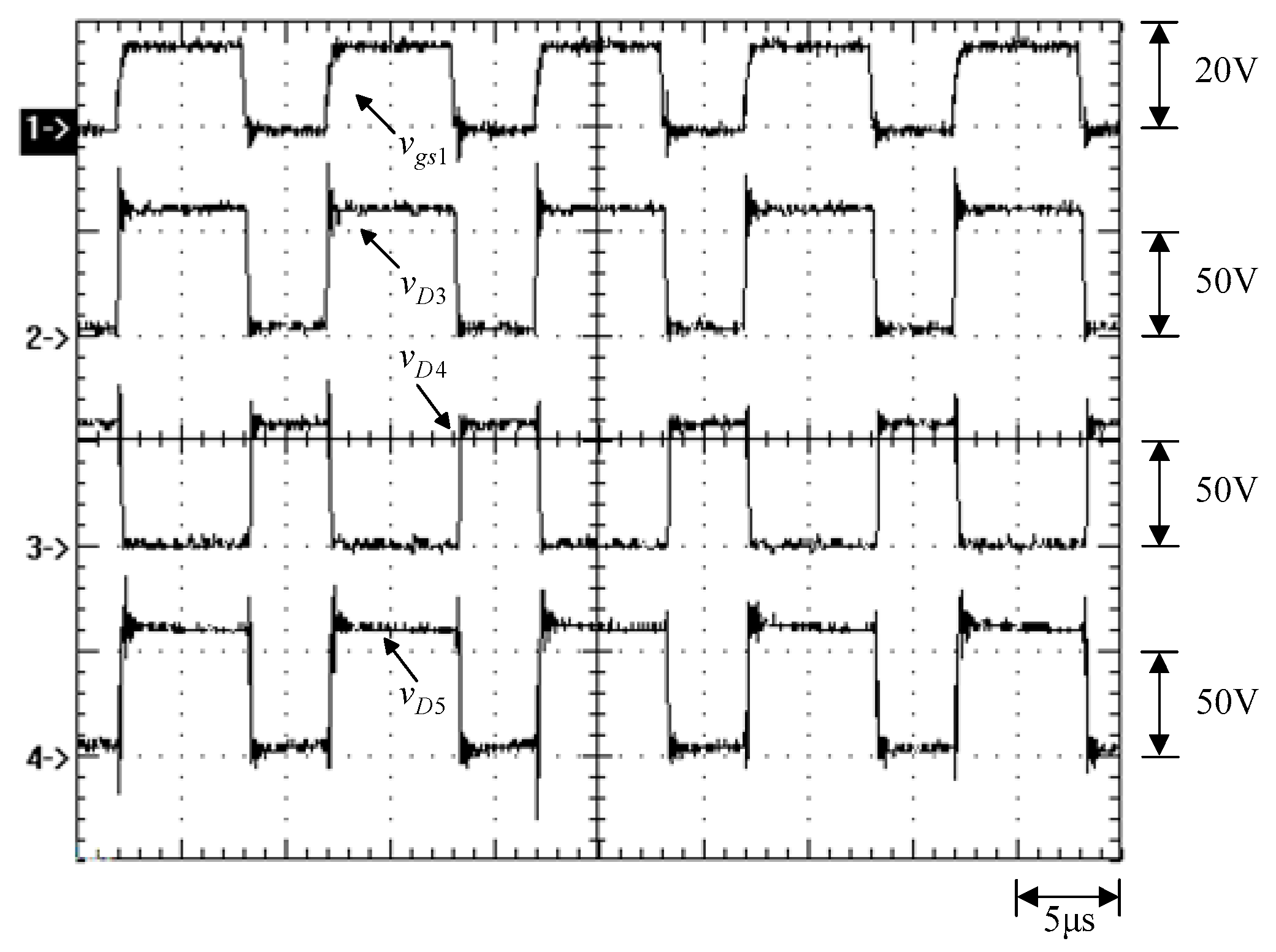

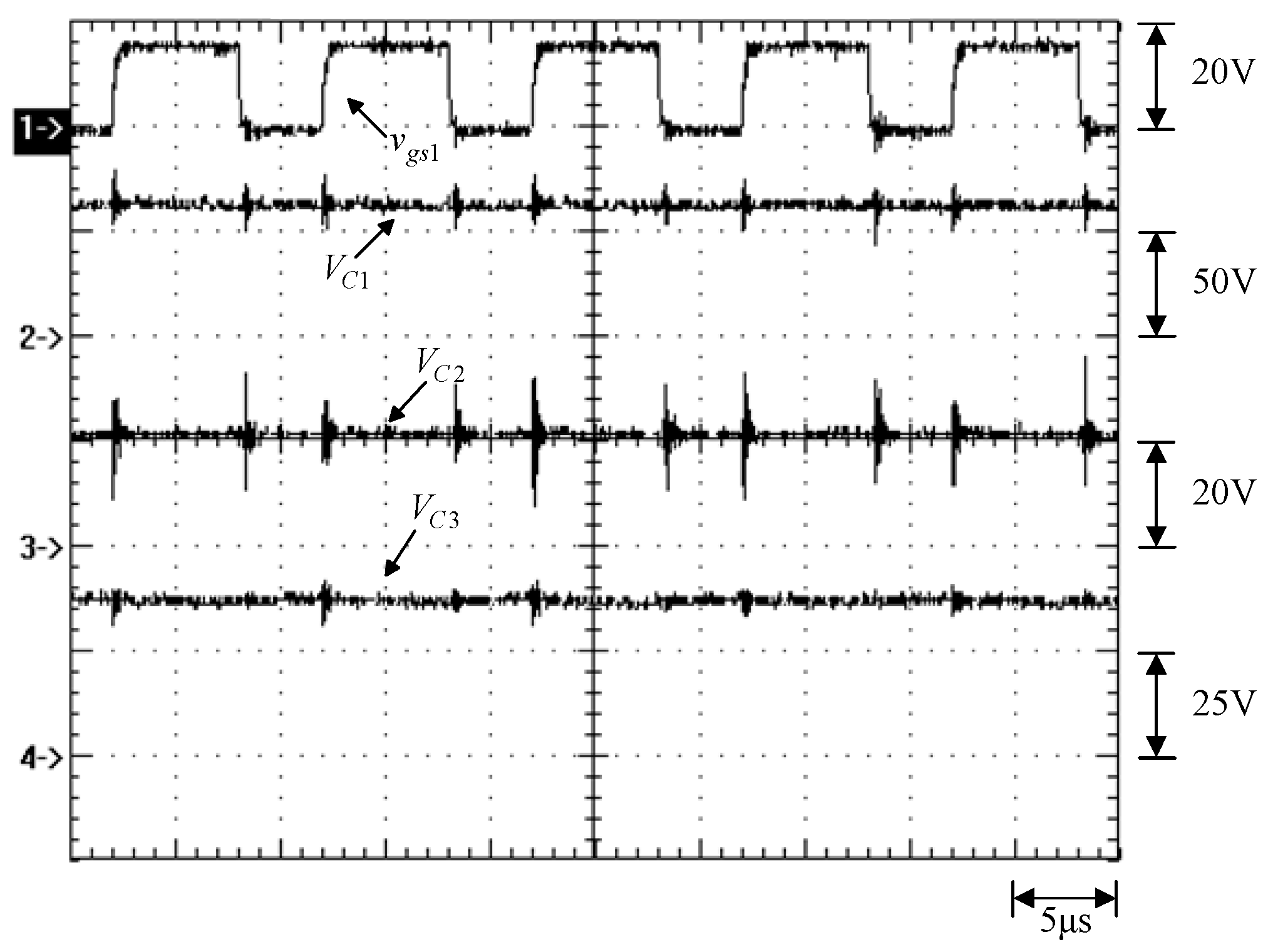

6.1. Steady-State Waveforms

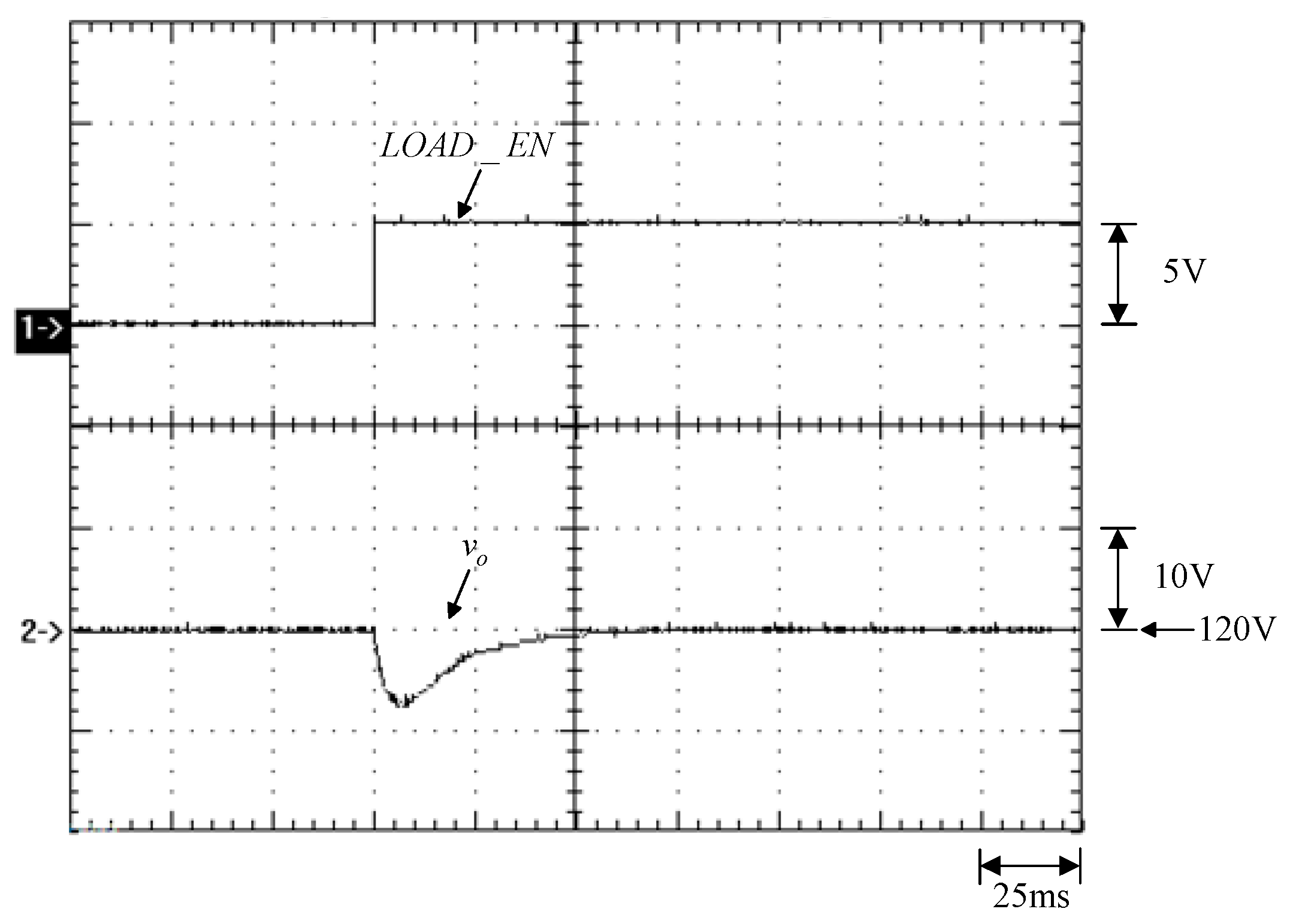

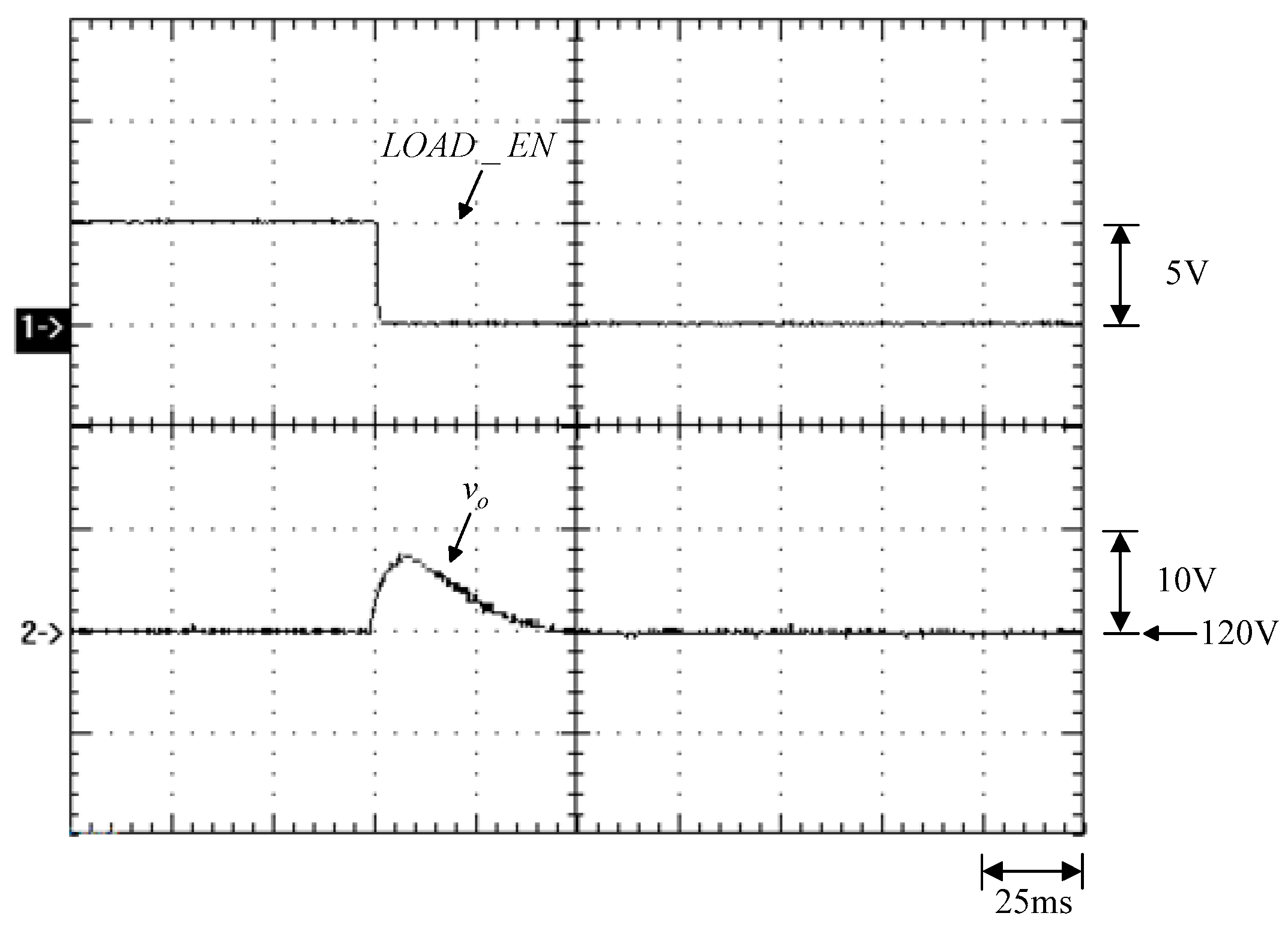

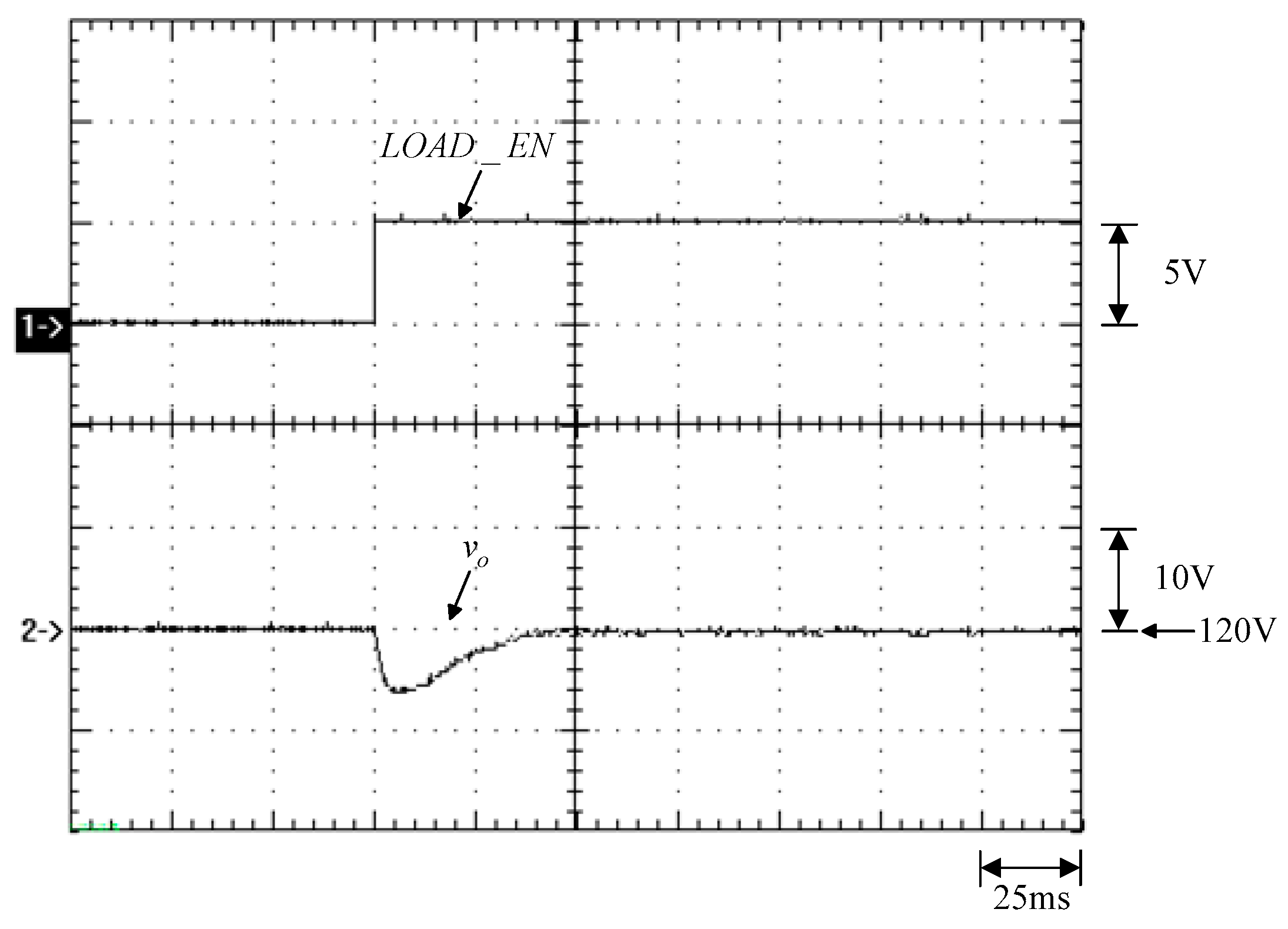

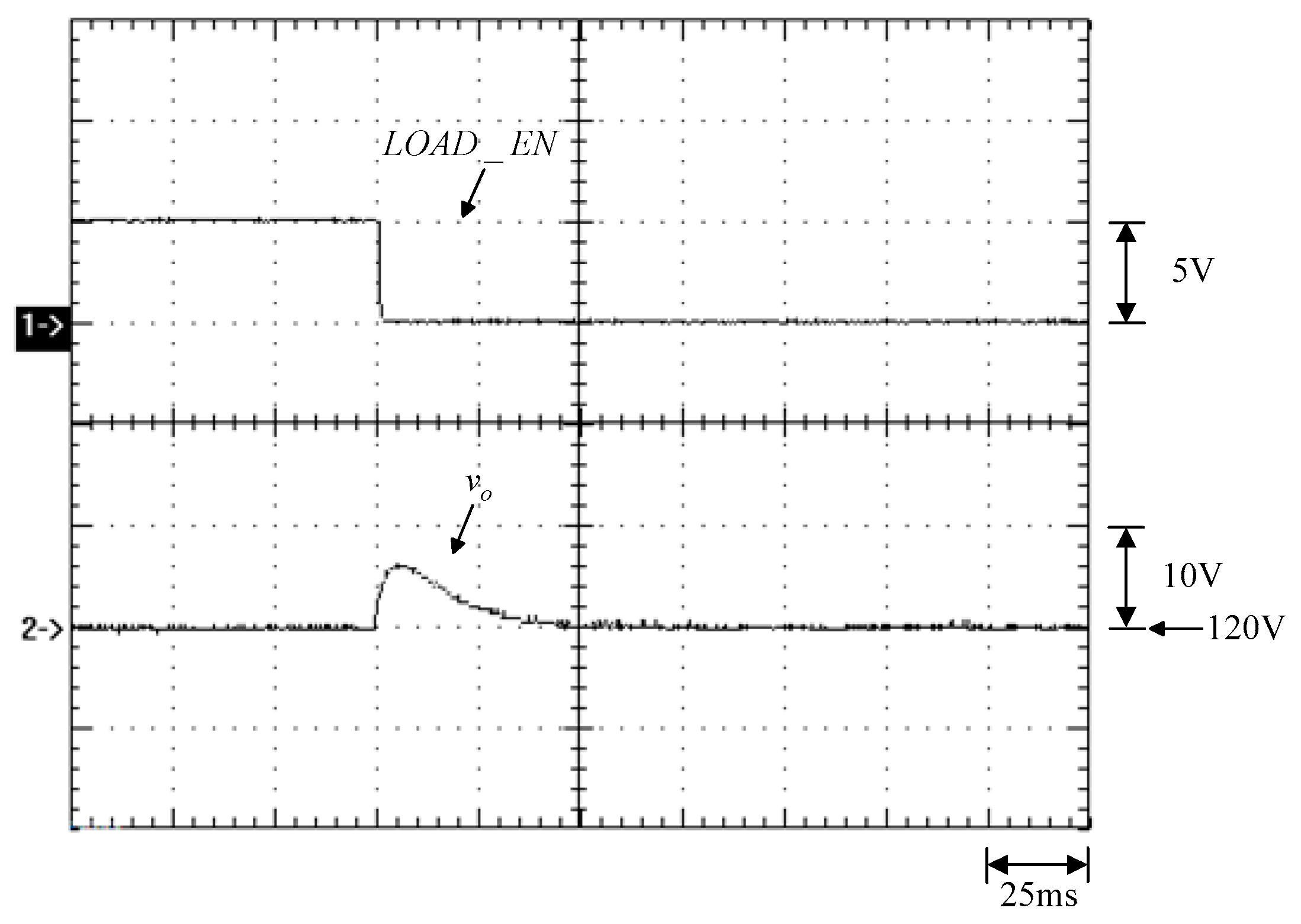

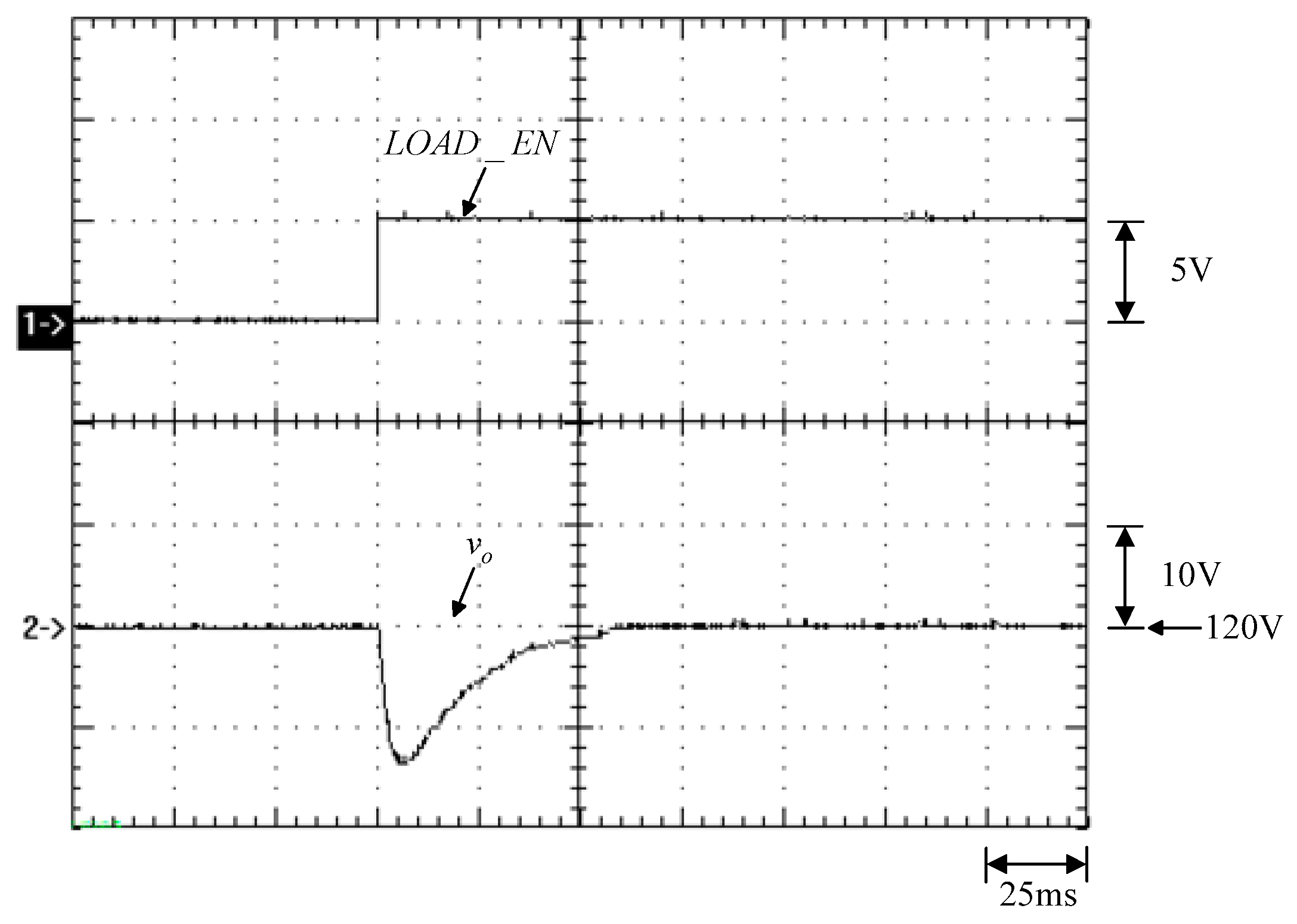

6.2. Dynamic Waveforms

6.3. Efficiency Measurement

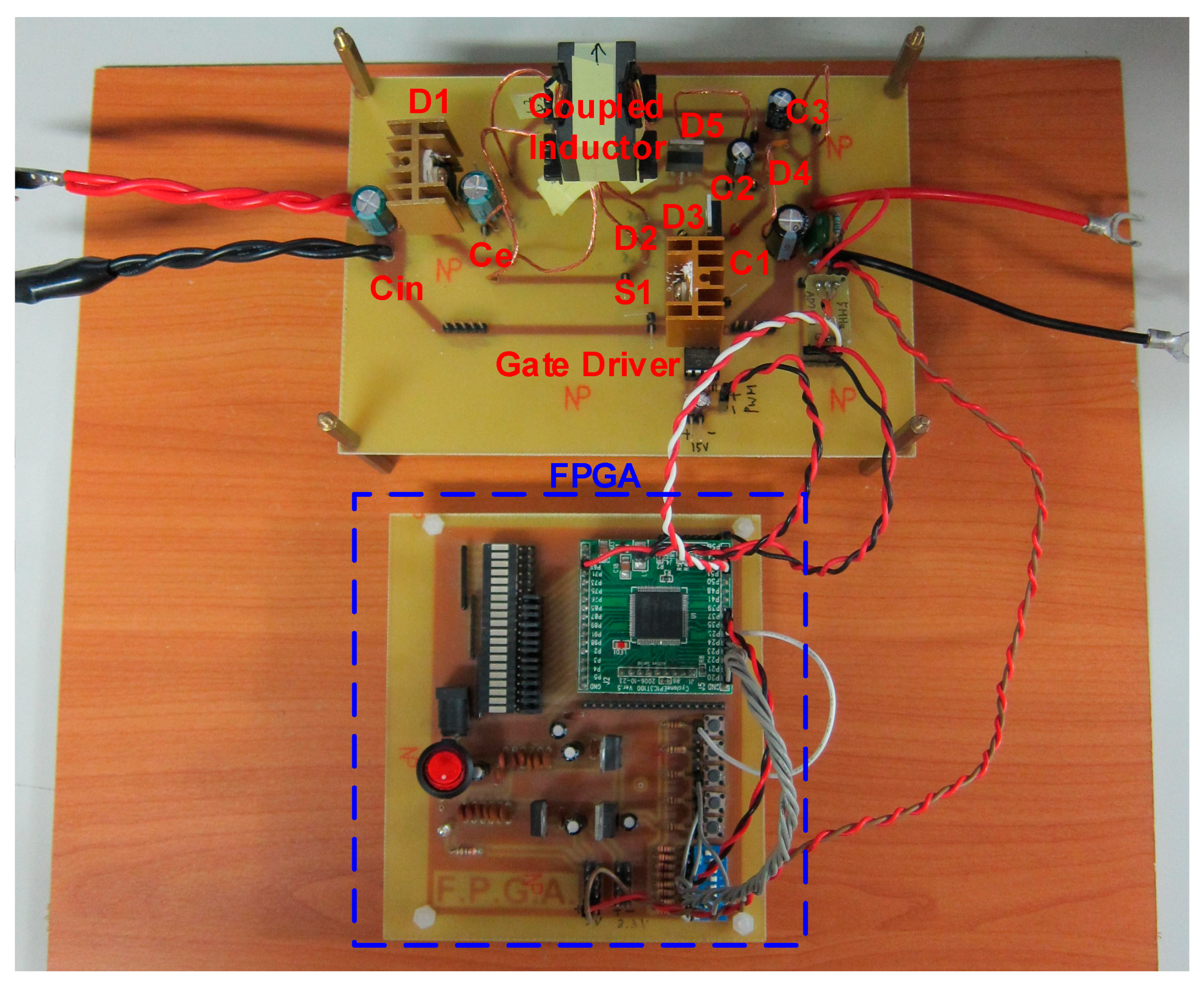

6.4. Experimental Setup

7. Circuit Comparison

8. Conclusions

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

References

- Gules, R.; Pacheco, J.D.P.; Hey, H.L.; Imhoff, J. A maximum power point tracking system with parallel connection for PV stand-alone applications. IEEE Trans. Power Electron. 2008, 55, 2674–2683. [Google Scholar] [CrossRef]

- Wu, Y.E.; Shen, C.L. Implementation of a DC power system with PV grid-connection and active power filtering. In Proceedings of the 2nd International Symposium on Power Electronics for Distributed Generation Systems, Hefei, China, 16–18 June 2010; pp. 116–121. [Google Scholar]

- Erickson, R.W.; Maksimovic, D. Fundamentals of Power Electronics, 2nd ed.; Kluwer Academic Publishers: Norwell, MA, USA, 2001. [Google Scholar]

- Sarvghadi, P.; Varjani, A.Y.; Shahparasti, M. A high step-up transformerless DC-DC converter with new voltage multiplier cell topology and coupled inductor. IEEE Trans. Ind. Electron. 2022, 69, 10162–10171. [Google Scholar] [CrossRef]

- Abkenar, P.P.; Samimi, M.H.; Marzoughi, A.; Samavatian, V.; Iman-Eini, H.; Naghibzadeh, Y. A highly reliable low-cost single-switch resonant DC-DC converter with high gain and low component count. IEEE Trans. Ind. Electron. 2023, 70, 2556–2565. [Google Scholar] [CrossRef]

- Wang, Z.; Zheng, Z.; Li, C. A high-step-up low-ripple and high-efficiency DC-DC converter for fuel-cell vehicles. IEEE Trans. Power Electron. 2022, 37, 3555–3569. [Google Scholar] [CrossRef]

- Bheemraj, T.S.; Kumar, Y.A.; Karthikeyan, V.; Pragaspathy, S. A Hybrid Structured High Step-Up DC–DC Converter for Integration of Energy Storage Systems in Military Applications. IEEE Trans. Circuits Syst. II Express Briefs 2023, 70, 1545–1549. [Google Scholar] [CrossRef]

- Hasanpour, S.; Siwakoti, Y.P.; Blaabjerg, F. A new soft-switched high step-up trans-inverse DC/DC converter based on built-in transformer. IEEE Open J. Power Electron. 2023, 4, 381–394. [Google Scholar] [CrossRef]

- Yu, L.; Wang, L.; Yang, C.; Zhu, L.; Gan, Y.; Zhang, H. A novel nonisolated GaN-based bidirectional DC-DC converter with high voltage gain. IEEE Trans. Ind. Electron. 2022, 69, 9052–9063. [Google Scholar] [CrossRef]

- Kong, I.-B.; Kim, W.-S.; Lee, S.-W. A novel high-voltage-gain quasi-resonant DC-DC converter with active-clamp and switched-capacitor techniques. IEEE Trans. Power Electron. 2023, 38, 7810–7820. [Google Scholar] [CrossRef]

- Ding, X.; Zhou, M.; Cao, Y.; Li, B.; Sun, Y.; Hu, X. A high step-up coupled-inductor-integrated DC-DC multilevel boost converter with continuous input current. IEEE J. Emerg. Sel. Top. Power Electron. 2022, 10, 7346–7360. [Google Scholar] [CrossRef]

- Zhang, M.; Wei, Z.; Zhou, M.; Wang, F.; Cao, Y.; Quan, L. A high step-up DC-DC converter with switched-capacitor and coupled-inductor techniques. IEEE J. Emerg. Sel. Top. Ind. Electron. 2022, 3, 1067–1076. [Google Scholar] [CrossRef]

- Mohammadi, M.R.; Amoorezaei, A.; Khajehoddin, S.A.; Moez, K. A high step-up/step-down LVS-parallel HVS-series ZVS bidirectional converter with coupled inductors. IEEE Trans. Power Electron. 2022, 37, 1945–1961. [Google Scholar]

- Mohseni, P.; Rahimpour, S.; Dezhbord, M.; Islam, M.R.; Muttaqi, K.M. An optimal structure for high step-up nonisolated DC-DC converters with soft-switching capability and zero input current ripple. IEEE Trans. Ind. Electron. 2022, 69, 4676–4686. [Google Scholar] [CrossRef]

- Selvam, S.; Sannasy, M.; Sridharan, M. Analysis and design of two-switch enhanced gain SEPIC converter. IEEE Trans. Ind. Appl. 2023, 59, 3552–3561. [Google Scholar] [CrossRef]

- Vaghela, M.A.; Mulla, M.A. High step-up gain converter based on two-phase interleaved coupled inductor without right-hand plane zero. IEEE Trans. Power Electron. 2023, 38, 5911–5927. [Google Scholar] [CrossRef]

- Pirpoor, S.; Rahimpour, S.; Andi, M.; Kanagaraj, N.; Pirouzi, S.; Mohammed, A.H. A novel and high-gain switched-capacitor and switched-inductor-based DC/DC boost converter with low input current ripple and mitigated voltage stresses. IEEE Access 2022, 10, 32782–32802. [Google Scholar] [CrossRef]

- Hasanpour, S.; Nouri, T.; Blaabjerg, F.; Siwakoti, Y.P. High step-up SEPIC-based trans-inverse DC-DC vonverter with quasi-resonance operation for renewable energy applications. IEEE Trans. Ind. Electron. 2023, 70, 485–497. [Google Scholar] [CrossRef]

- Hasanpour, S. New structure of single-switch ultra-high-gain DC/DC converter for renewable energy applications. IEEE Trans. Power Electron. 2022, 37, 12715–12728. [Google Scholar] [CrossRef]

- Harini, S.; Chellammal, N.; Chokkalingam, B.; Mihet-Popa, L. A novel high gain dual input single output z-quasi resonant (ZQR) DC/DC converter for off-board EV charging. IEEE Access 2022, 10, 83350–83367. [Google Scholar] [CrossRef]

- Jalilzadeh, T.; Rostami, N.; Babaei, E.; Maalandish, M. Nonisolated topology for high step-up DC-DC converters. IEEE J. Emerg. Sel. Top. Power Electron. 2023, 11, 1154–1168. [Google Scholar] [CrossRef]

- Hwu, K.I.; Yau, Y.T. High step-up converter based on charge pump and boost converter. IEEE Trans. Power Electron. 2012, 27, 2484–2494. [Google Scholar] [CrossRef]

| Component | Specification |

|---|---|

| Switch S1 | STP120NF10 |

| Diodes D1, D2 | MBRH2060CT |

| Diodes D3, D4, D5 | V20120C |

| Energy-Transferring Capacitor Ce | Ce = 470 µF/50 V Rubycon |

| Output Capacitors C1, C2, C3 | C1 = 100 µF/100 V Rubycon C2 = C3 = 50 µF/100 V Rubycon |

| Coupled Inductor | PC44PQ26/25Z-12 Lm = 300 µH N1 = N2 = 11 turns, N3 = 22 turns Lk1 = Lk2 = 180 nH, Lk3 = 90 nH |

| Gate Driver | TC4420 |

| FPGA | Cyclone I |

| Reference Number | CCM Voltage Gain | Total Component No. | Diode No. | Switch No. | Inductor No. | Capacitor No. | Switching Frequency | Efficiency |

|---|---|---|---|---|---|---|---|---|

| [18] | 14 | 4 | 1 | 4 | 1 | 55 kHz | 94.40% | |

| [19] | 16 | 5 | 1 | 4 | 6 | 60 kHz | 95.10% | |

| [20] | 16 | 6 | 1 | 4 | 5 | 50 kHz | 94.70% | |

| [21] | 16 | 5 | 2 | 3 | 6 | 33 kHz | 95.22% | |

| [22] | 8 | 3 | 1 | 2 | 2 | 100 kHz | 92.50% | |

| Proposed | 13 | 5 | 1 | 1 | 4 | 100 kHz | 92.61% |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2023 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Hwu, K.-I.; Tseng, P.-C. High Step-Up Converter. Electronics 2023, 12, 4000. https://doi.org/10.3390/electronics12194000

Hwu K-I, Tseng P-C. High Step-Up Converter. Electronics. 2023; 12(19):4000. https://doi.org/10.3390/electronics12194000

Chicago/Turabian StyleHwu, Kuo-Ing, and Pei-Ching Tseng. 2023. "High Step-Up Converter" Electronics 12, no. 19: 4000. https://doi.org/10.3390/electronics12194000