A Wideband and Low Reference Spur PLL with Clock Feedthrough Suppressed and Low Current Mismatch Charge Pump and Symmetrical CML Divider

Abstract

:1. Introduction

2. PLL Architecture

3. Circuit Design

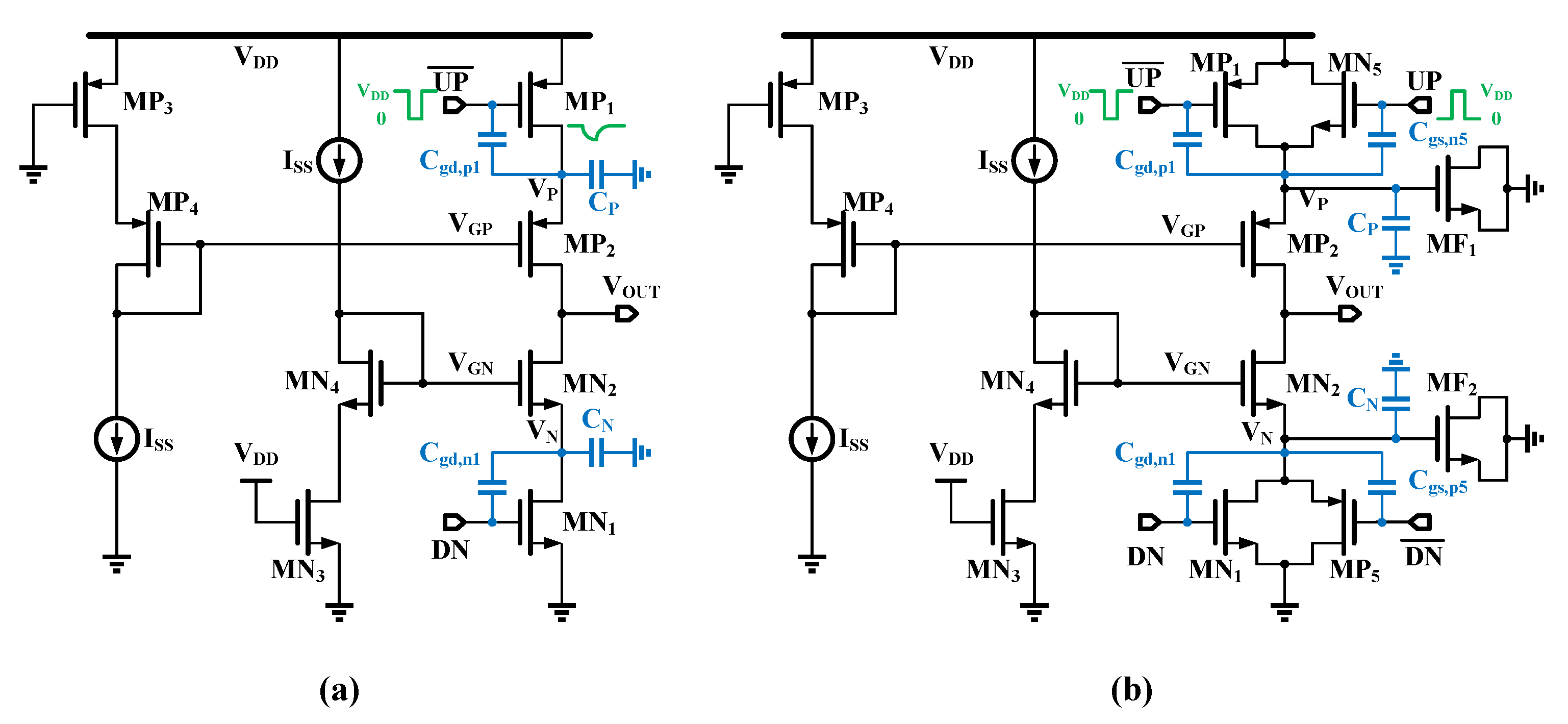

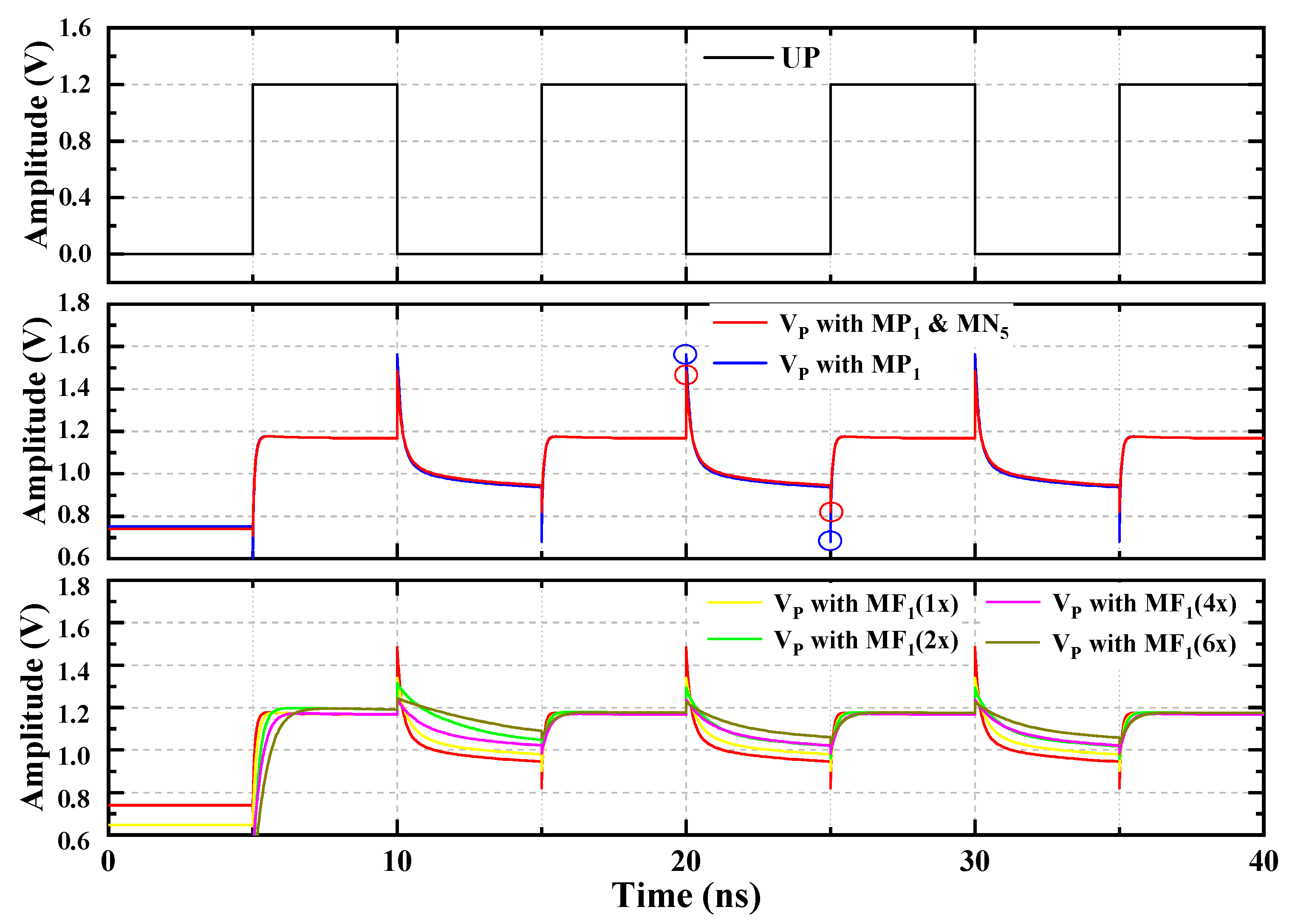

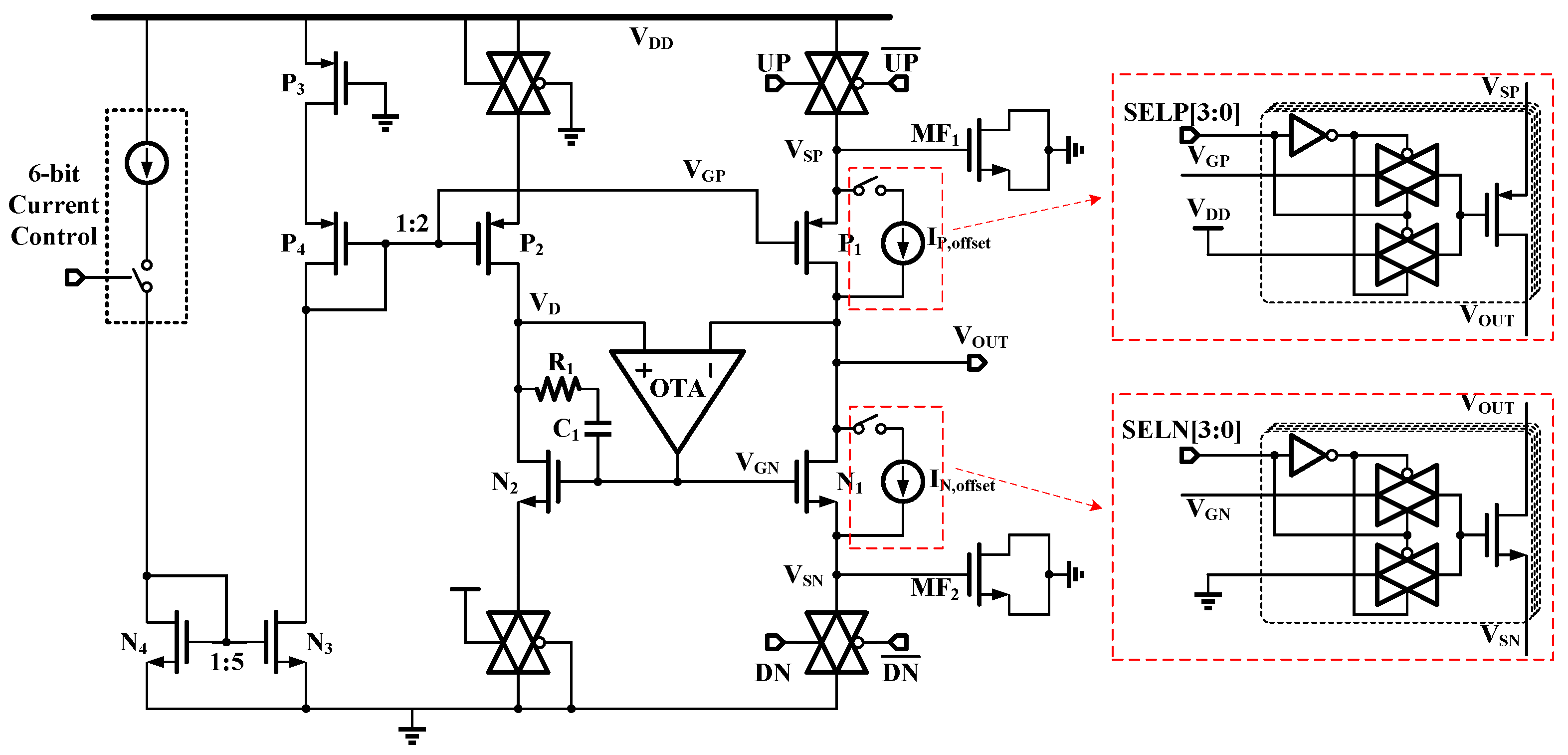

3.1. Clock Feedthrough Suppressed and Low Current Mismatch Charge Pump

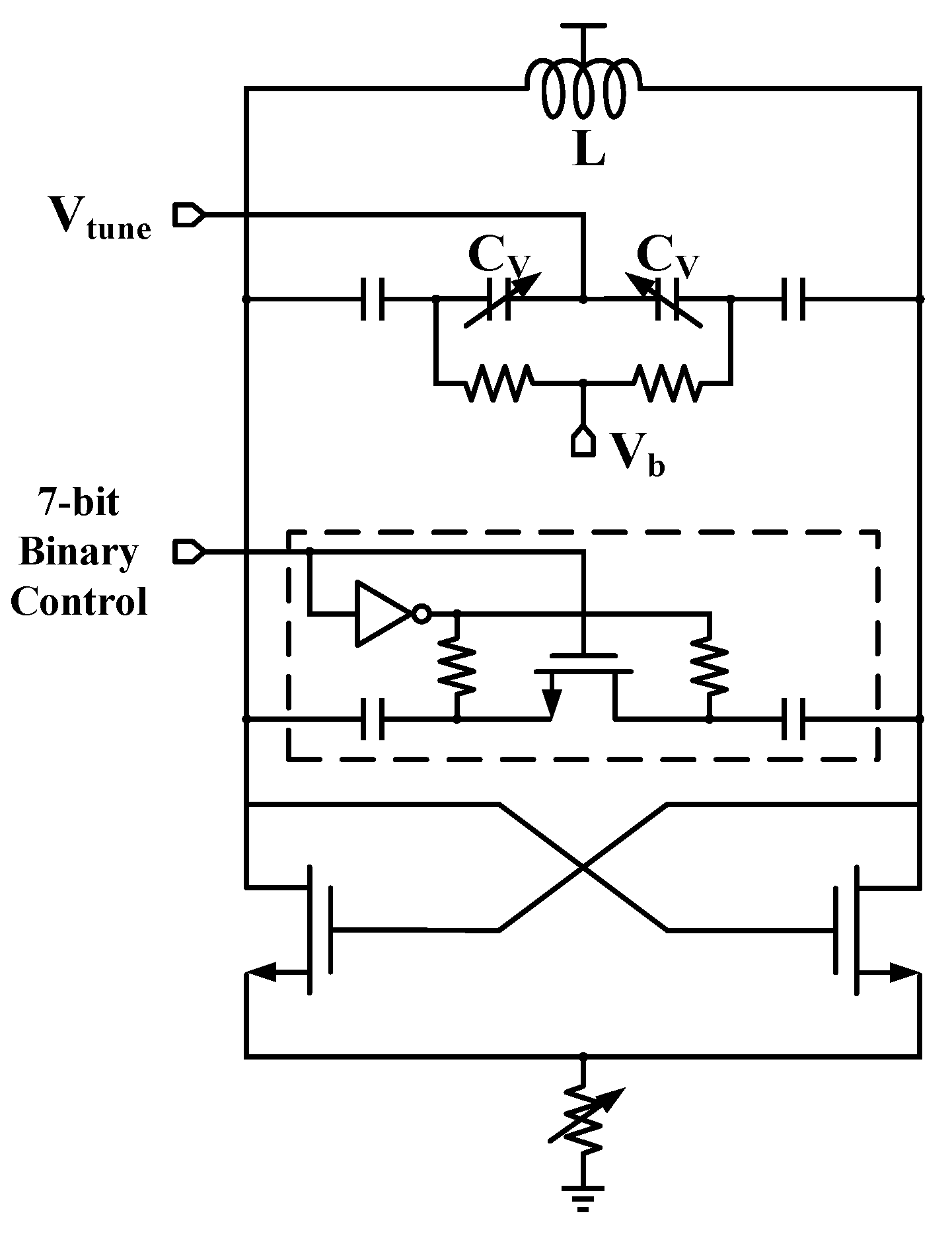

3.2. Wide-Tuning Range VCO

3.3. Symmetrical CML Divider

4. Measurement Results

5. Conclusions

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

References

- Debashis, M.; Bhattacharyya, T.K. 7.95 mW 2.4 GHz Fully-Integrated CMOS Integer N Frequency Synthesizer. In Proceedings of the 20th International Conference on VLSI Design Held Jointly with 6th International Conference on Embedded Systems (VLSID’07), Bangalore, India, 6–10 January 2007; pp. 156–164. [Google Scholar]

- Vamshi Krishna, M.; Xie, J.; Do, M.A.; Boon, C.C.; Yeo, K.S.; Do, A.V. A 1.8-V 3.6-mW 2.4-GHz fully integrated CMOS frequency synthesizer for IEEE 802.15.4. In Proceedings of the 2010 18th IEEE/IFIP International Conference on VLSI and System-on-Chip, Madrid, Spain, 27–29 September 2010; pp. 387–391. [Google Scholar]

- Wang, Z. An analysis of charge-pump phase-locked loops. IEEE Trans. Circuits Syst. I Regul. Pap. 2005, 52, 2128–2138. [Google Scholar] [CrossRef]

- Liao, T.-W.; Su, J.-R.; Hung, C.-C. Spur-Reduction Frequency Synthesizer Exploiting Randomly Selected PFD. IEEE Trans. Very Large Scale Integr. Syst. 2013, 21, 589–592. [Google Scholar] [CrossRef]

- Kong, L.; Razavi, B. A 2.4 GHz 4 mW Integer-N Inductorless RF Synthesizer. IEEE J. Solid-State Circuits 2016, 51, 626–635. [Google Scholar] [CrossRef]

- Zhang, X.; Liu, H.; Li, L. A low jitter phase-locked loop based on self-biased techniques. IEICE Electron. Express 2015, 12, 20150597. [Google Scholar]

- Mandal, D.; Mandal, P.; Bhattacharyya, T.K. Prediction of reference spur in frequency synthesisers. IET Circuits Devices Syst. 2015, 9, 131–139. [Google Scholar] [CrossRef]

- Kim, K.; Kim, K.; Yoo, C. A fREF/5 Bandwidth Type-II Charge-Pump Phase-Locked Loop with Dual-Edge Phase Comparison and Sampling Loop Filter. IEEE Microw. Wirel. Compon. Lett. 2018, 28, 825–827. [Google Scholar] [CrossRef]

- Mandal, D.; Mandal, P.; Bhattacharyya, T.K. Spur reducing architecture of frequency synthesiser using switched capacitors. IET Circuits Devices Syst. 2014, 8, 237–245. [Google Scholar] [CrossRef]

- Wang, H.Y.; Shou, G.L.; Wu, N.J. An adaptive frequency synthesizer architecture reducing reference sidebands. In Proceedings of the 2006 IEEE International Symposium on Circuits and Systems (ISCAS), Kos, Greece, 21–24 May 2006; p. 4. [Google Scholar]

- Li, A.; Chao, Y.; Chen, X.; Luong, H.C. A Spur-and-Phase-Noise-Filtering Technique for Inductor-Less Fractional-N Injection-Locked PLLs. IEEE J. Solid-State Circuits 2017, 52, 2128–2140. [Google Scholar] [CrossRef]

- Charles, C.T.; Allstot, D.J. A Calibrated Phase/Frequency Detector for Reference Spur Reduction in Charge-Pump PLLs. IEEE J. Solid-State Circuits 2006, 53, 822–826. [Google Scholar] [CrossRef]

- Hung, C.-M.; O, K.K. A fully integrated 1.5-V 5.5-GHz CMOS phase-locked loop. IEEE J. Solid-State Circuits 2002, 37, 521–525. [Google Scholar] [CrossRef]

- Gierkink, S.L.J. Low-Spur, Low-Phase-Noise Clock Multiplier Based on a Combination of PLL and Recirculating DLL with Dual-Pulse Ring Oscillator and Self-Correcting Charge Pump. IEEE J. Solid-State Circuits 2008, 43, 2967–2976. [Google Scholar] [CrossRef]

- Amer, A.G.; Ibrahim, S.A.; Ragai, H.F. A novel current steering charge pump with low current mismatch and variation. In Proceedings of the 2016 IEEE International Symposium on Circuits and Systems (ISCAS), Montreal, QC, Canada, 22–25 May 2016; pp. 1666–1669. [Google Scholar]

- Liang, C.-F.; Chen, S.-H.; Liu, S.-I. A Digital Calibration Technique for Charge Pumps in Phase-Locked Systems. IEEE J. Solid-State Circuits 2008, 43, 390–398. [Google Scholar] [CrossRef]

- Lin, W.-M.; Liu, S.-I.; Kuo, C.-H.; Li, C.-H.; Hsieh, Y.-J.; Liu, C.-T. A phase-locked loop with self-calibrated charge pumps in 3-µm LTPS-TFT technology. IEEE Trans. Circuits Syst. II Express Briefs 2009, 56, 142–146. [Google Scholar]

- Su, P.-E.; Pamarti, S. Mismatch shaping techniques to linearize charge pump errors in fractional-N PLLs. IEEE Trans. Circuits Syst. I Regul. Pap. 2010, 57, 1221–1230. [Google Scholar]

- Yang, P.; Guo, Y.; Jiang, H.; Wang, Z. A 360–456 MHz PLL frequency synthesizer with digitally controlled charge pump leakage calibration. In Proceedings of the 2019 IEEE Asian Solid-State Circuits Conference (A-SSCC), Macau, Macao, 4–6 November 2019; pp. 285–286. [Google Scholar]

- Luo, T.-N.; Chen, Y.-J.E. A 0.8-mW 55-GHz Dual-Injection-Locked CMOS Frequency Divider. IEEE Trans. Microw. Theory Tech. 2008, 56, 620–625. [Google Scholar]

- Tiebout, M. A CMOS direct injection-locked oscillator topology as high-frequency low-power frequency divider. IEEE J. Solid-State Circuits 2004, 39, 1170–1174. [Google Scholar] [CrossRef]

- Chen, Y.-T.; Li, M.-W.; Huang, T.-H.; Chuang, H.-R. A V-Band CMOS Direct Injection-Locked Frequency Divider Using Forward Body Bias Technology. IEEE Microw. Wirel. Compon. Lett. 2010, 20, 396–398. [Google Scholar] [CrossRef]

- Rong, S.; Ng, A.W.L.; Luong, H.C. 0.9 mW 7 GHz and 1.6 mW 60 GHz frequency dividers with locking-range enhancement in 0.13 µm CMOS. In Proceedings of the 2009 IEEE International Solid-State Circuits Conference—Digest of Technical Papers, San Francisco, CA, USA, 8–12 February 2009; pp. 96–97. [Google Scholar]

- Takatsu, K.; Tamura, H.; Yamamoto, T.; Doi, Y.; Kanda, K.; Shibasaki, T.; Kuroda, T. A 60-GHz 1.65 mW 25.9% locking range multi-order LC oscillator based injection locked frequency divider in 65 nm CMOS. In Proceedings of the IEEE Custom Integrated Circuits Conference 2010, San Jose, CA, USA, 19–22 September 2010; pp. 1–4. [Google Scholar]

- Wen, S.-H.; Huang, J.-W.; Wang, C.-S.; Wang, C.-K. A 60 GHz Wide Locking Range CMOS Frequency Divider using Power-Matching Technique. In Proceedings of the 2006 IEEE Asian Solid-State Circuits Conference, Hangzhou, China, 13–15 November 2006; pp. 187–190. [Google Scholar]

- Wang, H.; Hajimiri, A. A 19 GHz 0.5 mW 0.35 µm CMOS frequency divider with shunt-peaking locking-range enhancement. In Proceedings of the 2001 IEEE International Solid-State Circuits Conference, Digest of Technical Papers, ISSCC (Cat. No. 01CH37177), San Francisco, CA, USA, 5–7 February 2001; pp. 412–413. [Google Scholar]

- Maxim, A. Low-voltage CMOS charge-pump PLL architecture for low jitter operation. In Proceedings of the 28th European Solid-State Circuits Conference, Florence, Italy, 24–26 September 2002; pp. 423–426. [Google Scholar]

- Fan, Y.; Xiang, B.; Zhang, D.; Ayers, J.S.; Shen, K.-Y.J.; Mezhiba, A. 19.5 Digital Leakage Compensation for a Low-Power and Low-Jitter 0.5-to-5 GHz PLL in 10 nm FinFET CMOS Technology. In Proceedings of the 2019 IEEE International Solid-State Circuits Conference—(ISSCC), San Francisco, CA, USA, 17–21 February 2019; pp. 320–322. [Google Scholar]

- Kong, L.; Razavi, B. 25.7 A 2.4 GHz 4 mW inductorless RF synthesizer. In Proceedings of the 2015 IEEE International Solid-State Circuits Conference—(ISSCC), Digest of Technical Papers, San Francisco, CA, USA, 22–26 February 2015; pp. 1–3. [Google Scholar]

- Hsueh, Y.-L.; Cho, L.-C.; Shen, C.-H.; Tsai, Y.-C.; Chueh, T.-C.; Chang, T.-Y.; Hsu, J.-L.; Zhan, J.-H.C. 28.2 A 0.29 mm2 frequency synthesizer in 40 nm CMOS with 0.19 psrms jitter and <-100 dBc reference spur for 802.11 ac. In Proceedings of the 2014 IEEE International Solid-State Circuits Conference Digest of Technical Papers (ISSCC), San Francisco, CA, USA, 9–13 February 2014; pp. 472–473. [Google Scholar]

- Levantino, S.; Marzin, G.; Samori, C.; Lacaita, A.L. A Wideband Fractional-N PLL with Suppressed Charge-Pump Noise and Automatic Loop Filter Calibration. IEEE J. Solid-State Circuits 2013, 48, 2419–2429. [Google Scholar] [CrossRef]

- Park, P.; Park, D.; Cho, S. A 2.4 GHz Fractional-N Frequency Synthesizer with High-OSR ΔΣ Modulator and Nested PLL. IEEE J. Solid-State Circuits 2012, 47, 2433–2443. [Google Scholar] [CrossRef]

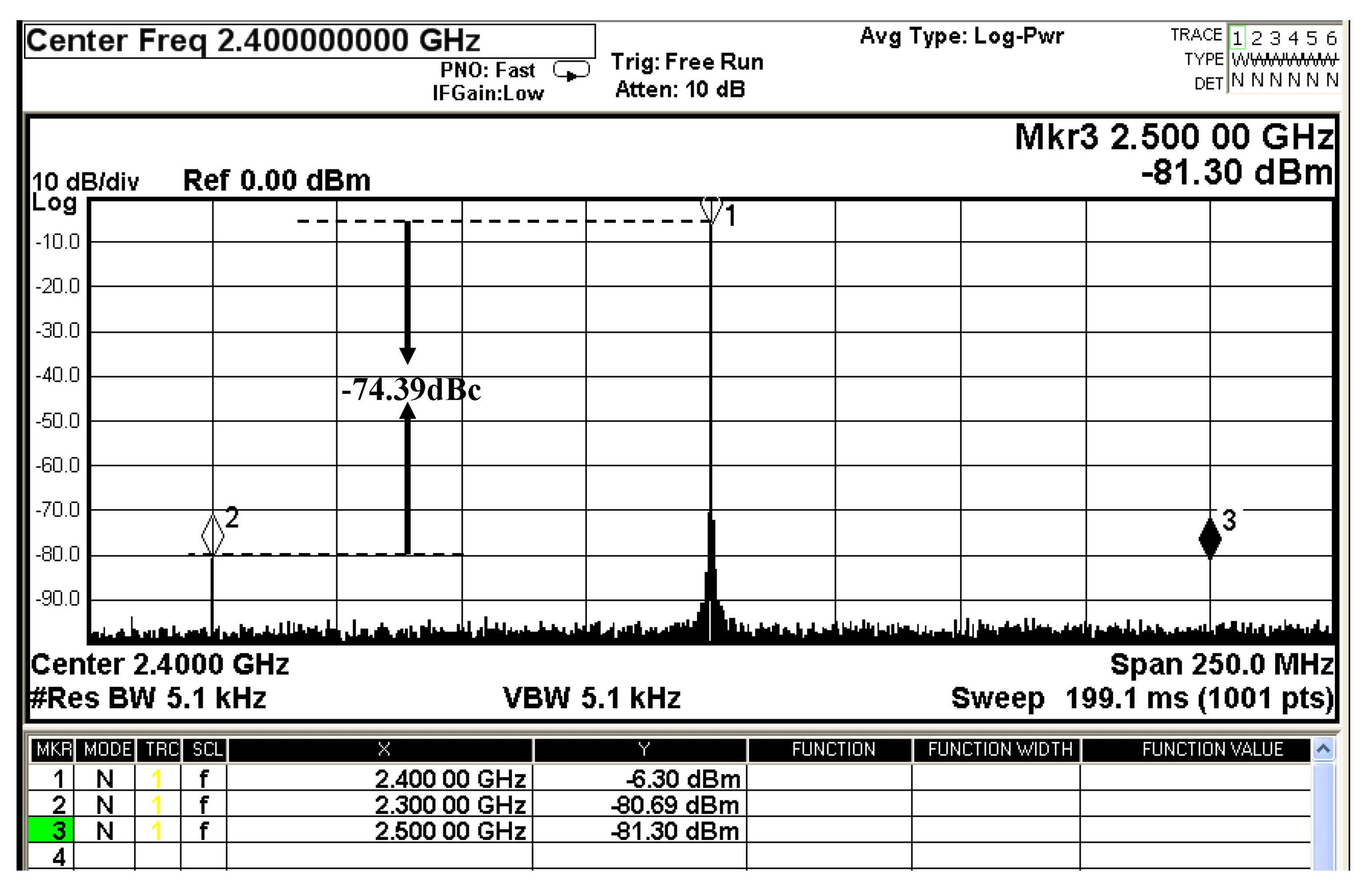

| Reference | This Work | ISSCC’19 [28] | ISSCC’15 [29] | ISSCC’14 [30] | JSSC’13 [31] | JSSC’12 [32] | |

|---|---|---|---|---|---|---|---|

| Technology (nm) | 130 | 10 | 45 | 40 | 65 | 130 | |

| Supply (V) | 1.2 | 0.9 | 1 | N/A | 1.2 | N/A | |

| Oscillator Topology | LC | Ring | Ring | LC | LC | LC | |

| Reference freq. (MHz) | 100 | 100 | 22.6 | 26 | 40 | 60 | |

| Output freq. (GHz) | 2.4 | 3.2 | 2.4 | 3.883 | 3.61 | 2.438 | |

| /freq. Range (GHz) | /(2.0–3.0) | /(0.5–5.0) | /(2.0–3.0) | /(3.276–3.883) | /(3.0–4.0) | / N/A | |

| Tuning Range (%) | 40 | 164 | 40 | 17 | 28.6 | N/A | |

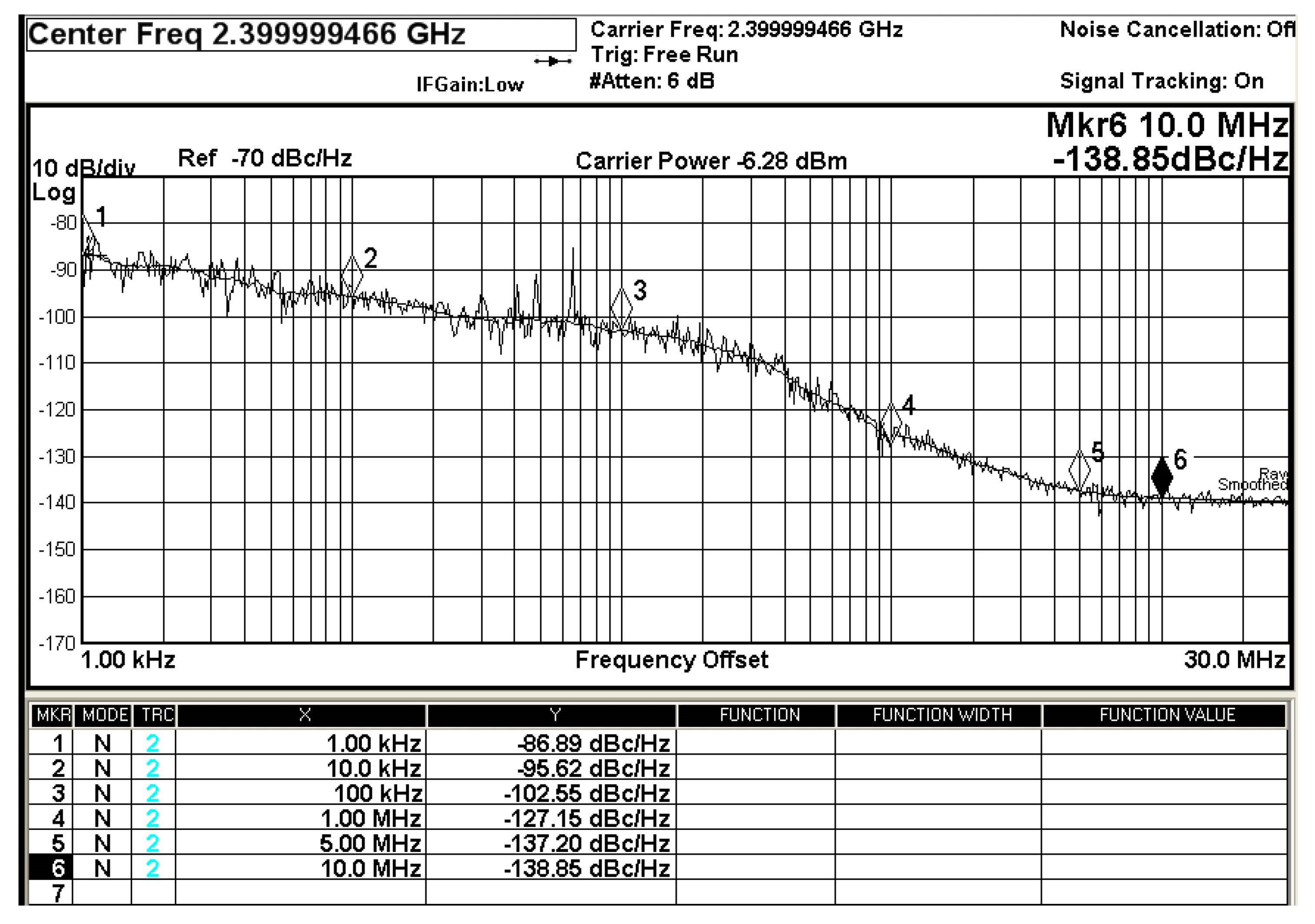

| Phase Noise (dBc/Hz) | @100 kHz | −102.55 | N/A | −109.18 | −105.49 | −103.62 | −102.27 |

| @1 MHz | −127.15 | N/A | −113.78 | −123.06 | −103.79 | −99.63 | |

| RMS jitter (fs) | 340.99 | 1870 | 970 | 300 | 972.9 | 1092.6 | |

| (10 k–10 M) | (100 k–100 M) | (1 k–200 M) | (1 k–10 M) | (3 k–30 M) | (10 k–10 M) | ||

| FoM (dB) * | −234.08 | −233 | −234.1 | −242 | −235.1 | −229.41 | |

| Reference Spur (dBc) | −74.39 | −57 | −65 | N/A | −71 | −54.7 | |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2023 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Wang, Y.; Liu, Y.; Xu, H.; Li, Z.; Li, Z. A Wideband and Low Reference Spur PLL with Clock Feedthrough Suppressed and Low Current Mismatch Charge Pump and Symmetrical CML Divider. Electronics 2023, 12, 4164. https://doi.org/10.3390/electronics12194164

Wang Y, Liu Y, Xu H, Li Z, Li Z. A Wideband and Low Reference Spur PLL with Clock Feedthrough Suppressed and Low Current Mismatch Charge Pump and Symmetrical CML Divider. Electronics. 2023; 12(19):4164. https://doi.org/10.3390/electronics12194164

Chicago/Turabian StyleWang, Yingxi, Yueyue Liu, Haotang Xu, Zhongmao Li, and Zhiqiang Li. 2023. "A Wideband and Low Reference Spur PLL with Clock Feedthrough Suppressed and Low Current Mismatch Charge Pump and Symmetrical CML Divider" Electronics 12, no. 19: 4164. https://doi.org/10.3390/electronics12194164