An Optimal Strategy for Submodule Capacitance Sizing of Cascaded H-Bridge-Based Active Power Filter

Abstract

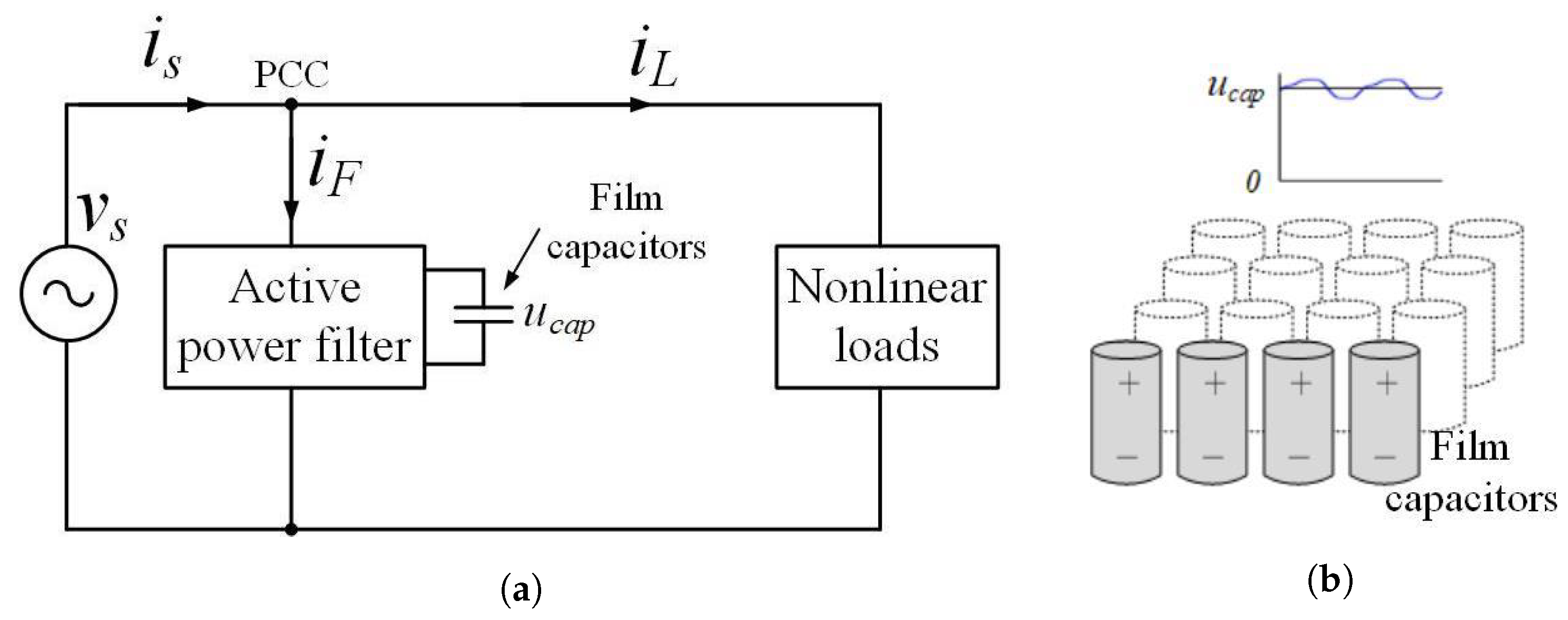

:1. Introduction

- By comparison of aluminum electrolytic capacitors and film capacitors, the design rules specially for film capacitors are proposed.

- With the help of trigonometric transformation, the capacitance design rules are represented as a series of positive univariate polynomials, coefficients of which are with regard to the capacitance value. This transformation is not an approximation but an equivalent representation so that the accuracy of the method is ensured.

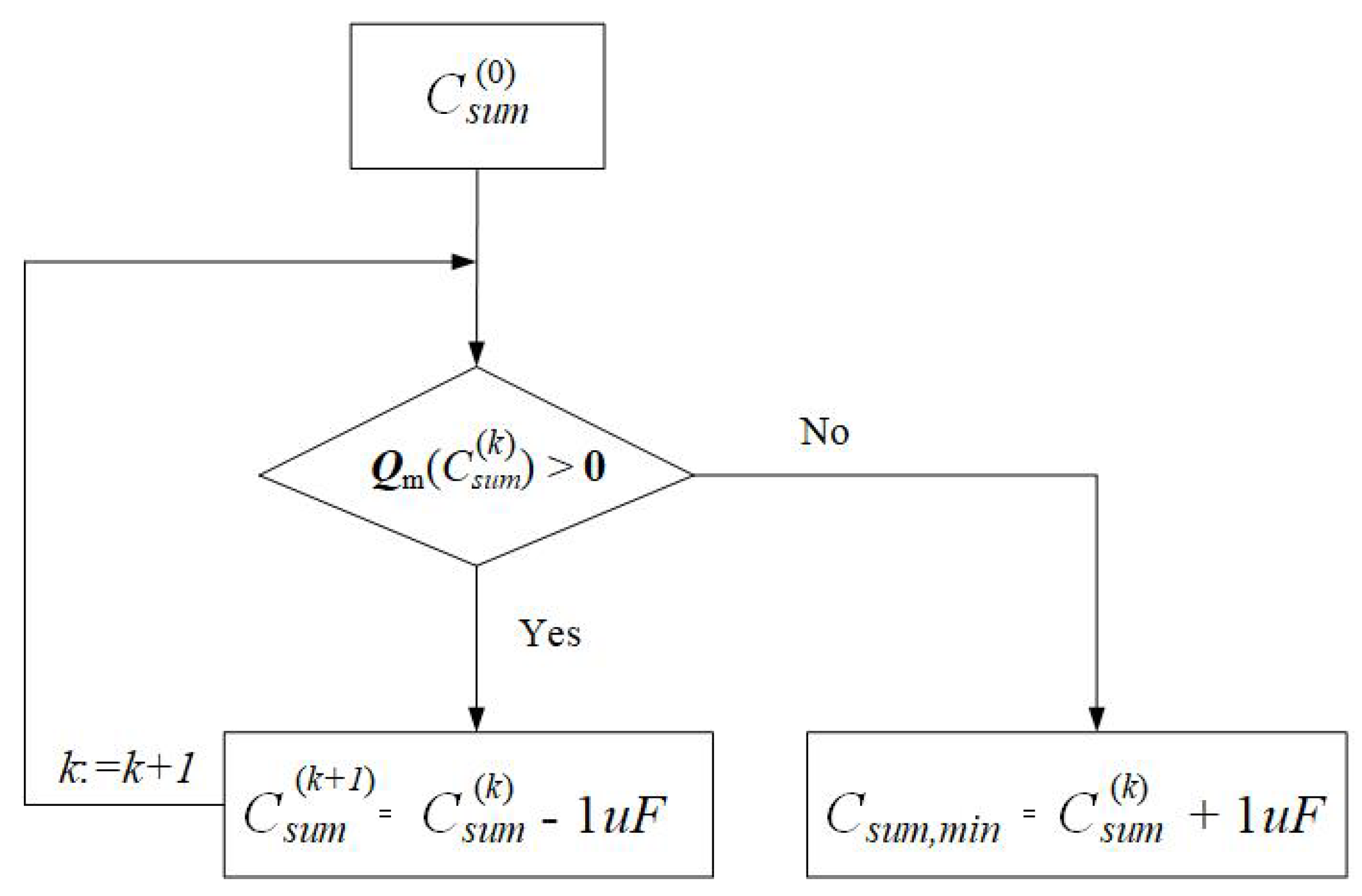

- The capacitance sizing strategy is formulated as an optimal problem, and the optimization solver SeDuMi is then applied to determine the minimal capacitance value that abides by the design constraints.

2. Generic Expression of Capacitor Voltages and Branch Voltages

2.1. Generic Expression of Three-Phase Time-Varying Signals

2.1.1. Expression of Branch Voltages

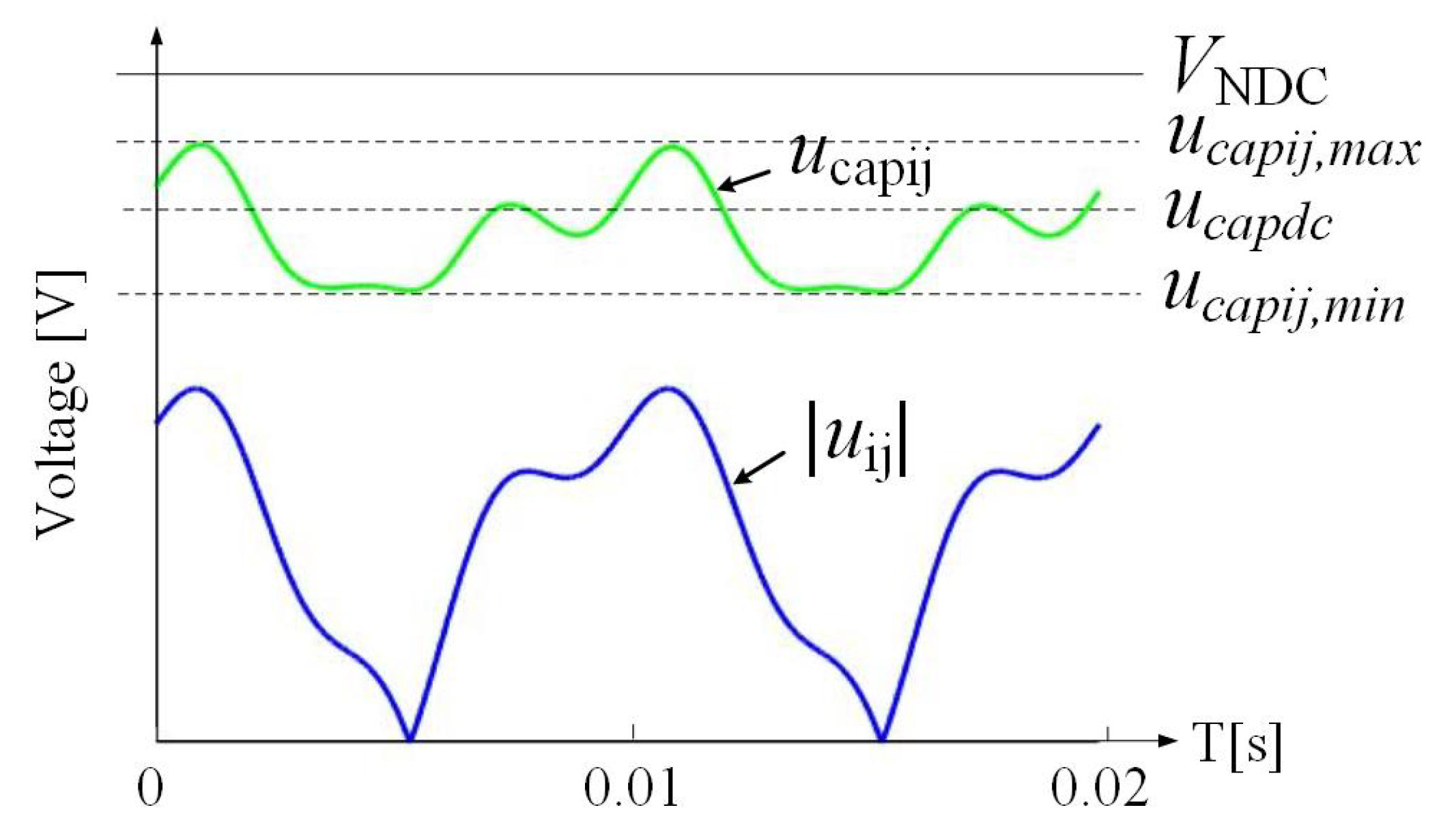

2.1.2. Expression of Capacitor Voltages

3. Optimal Capacitance Design for Film Capacitors

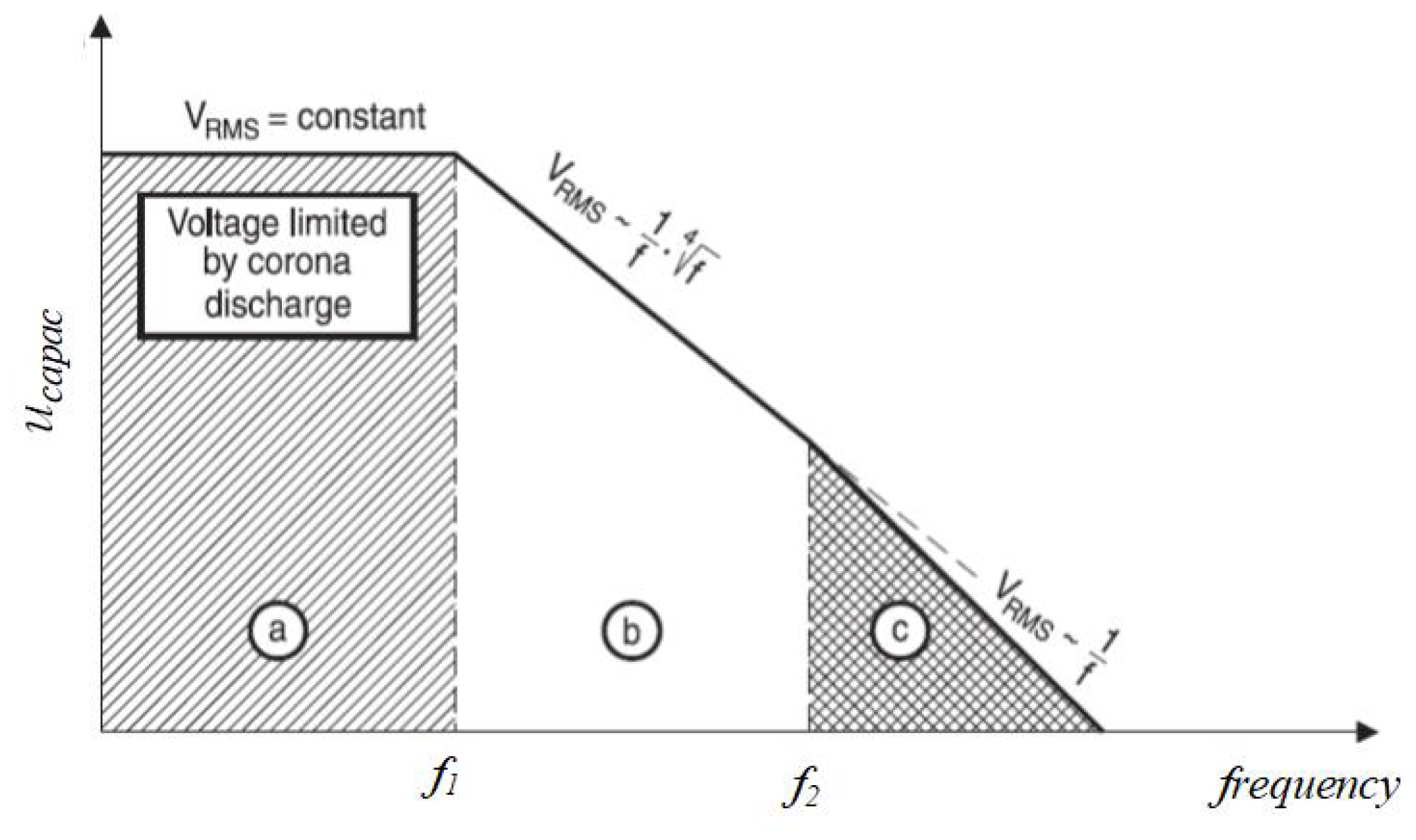

3.1. Aluminum Electrolytic Capacitors and Film Capacitors

3.2. Constraints for Capacitance Design with Film Capacitors

- In the whole period, so that the power quality can be guaranteed.

- The positive peak value of capacitor voltage shall not exceed the permissible peak voltage, .

- The peak–peak ripple voltage shall not be greater than the permissible peak–peak voltage, .

3.2.1. Overmodulation Avoidance

3.2.2. Peak Permissible Voltage

3.2.3. Peak–Peak Permissible Voltage

3.3. Optimal Problem Formulation and Its Solution

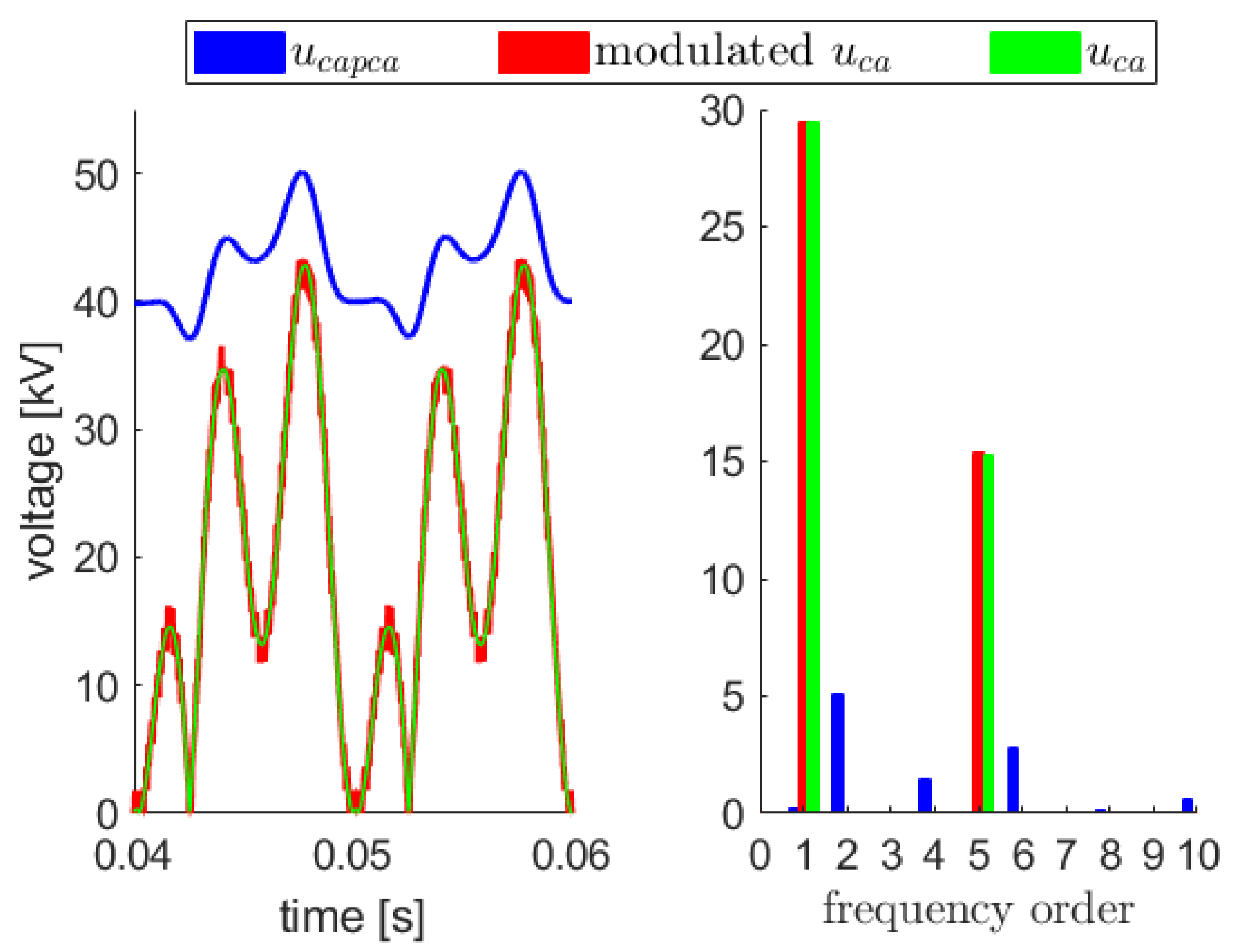

4. Simulations

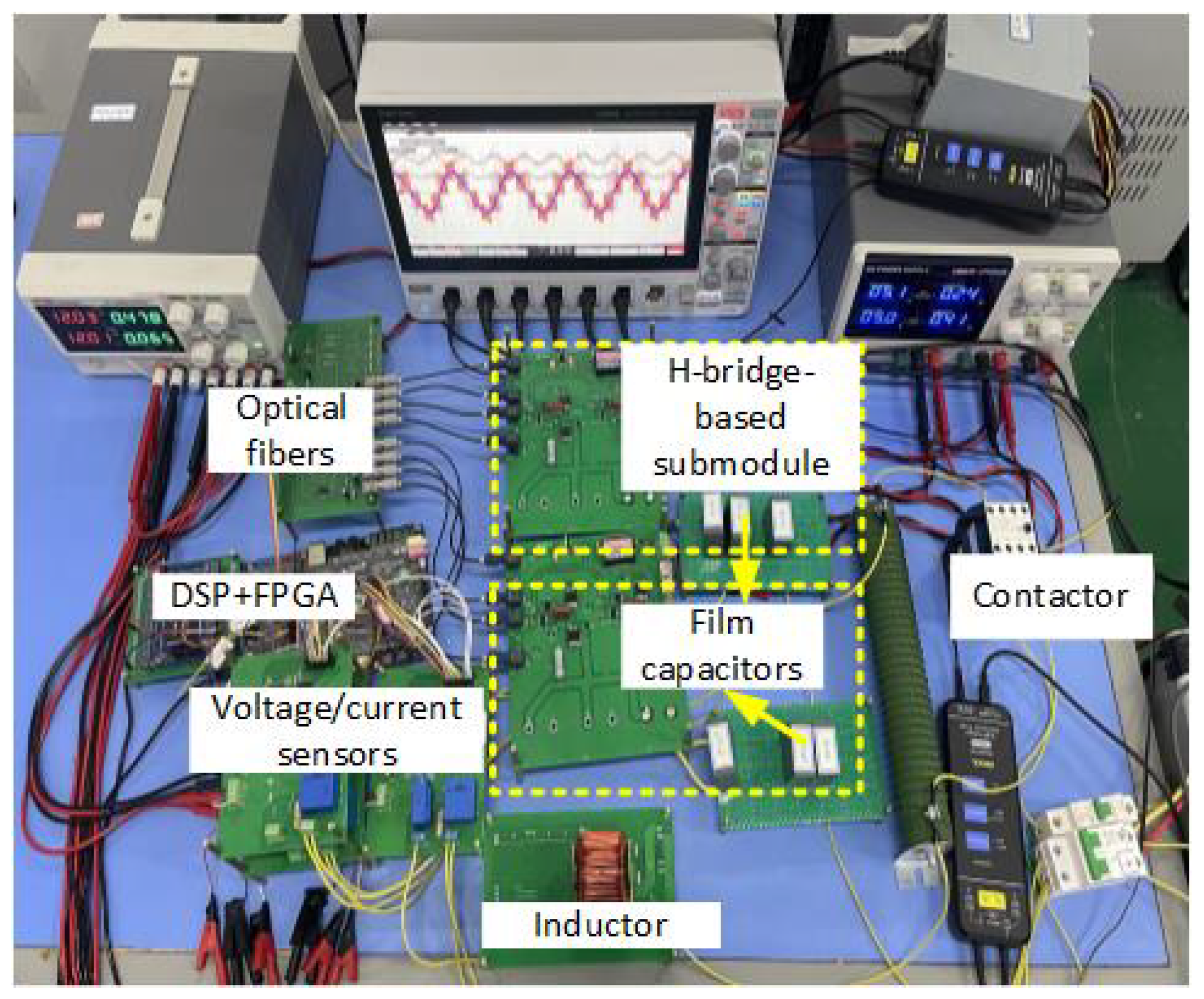

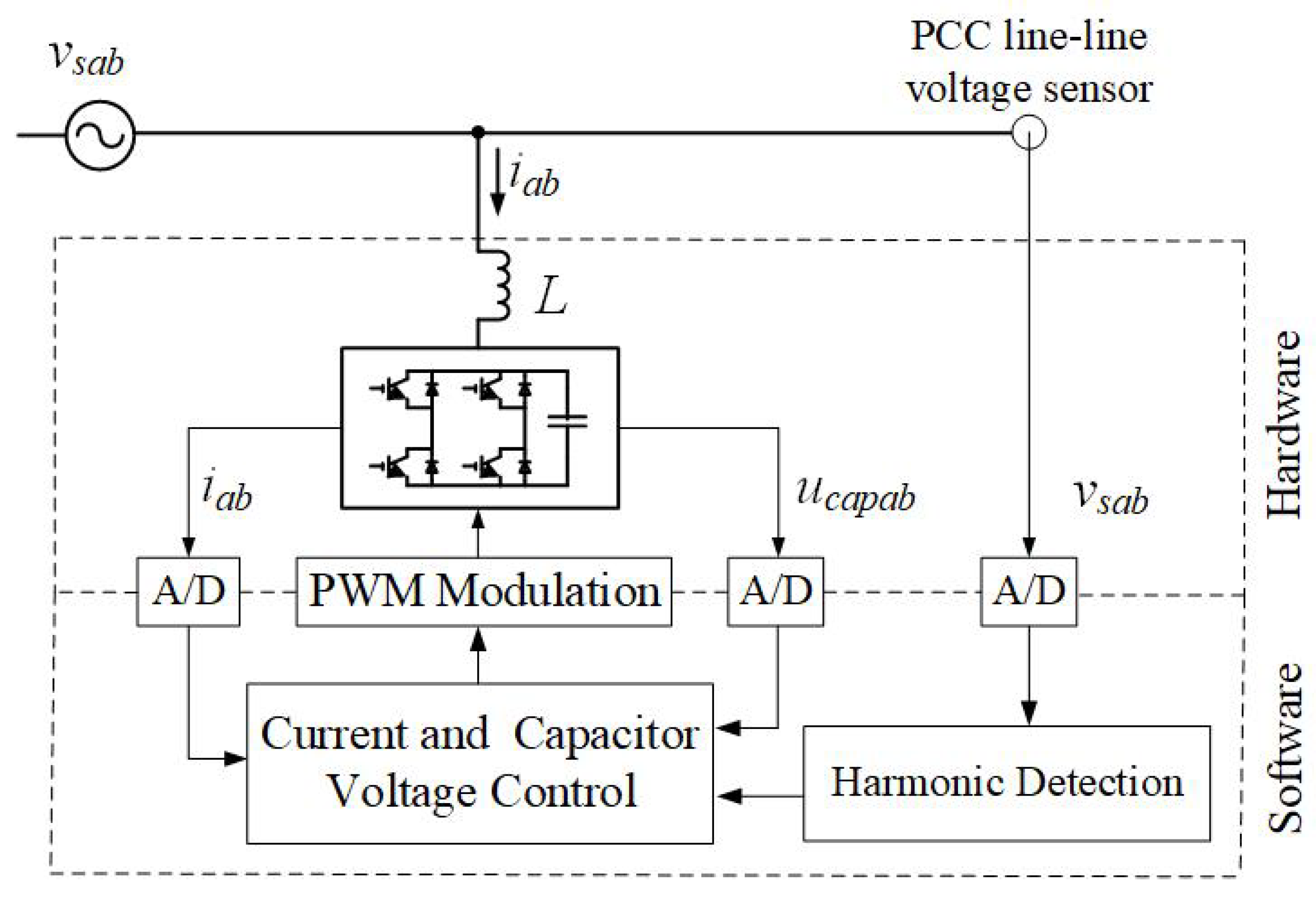

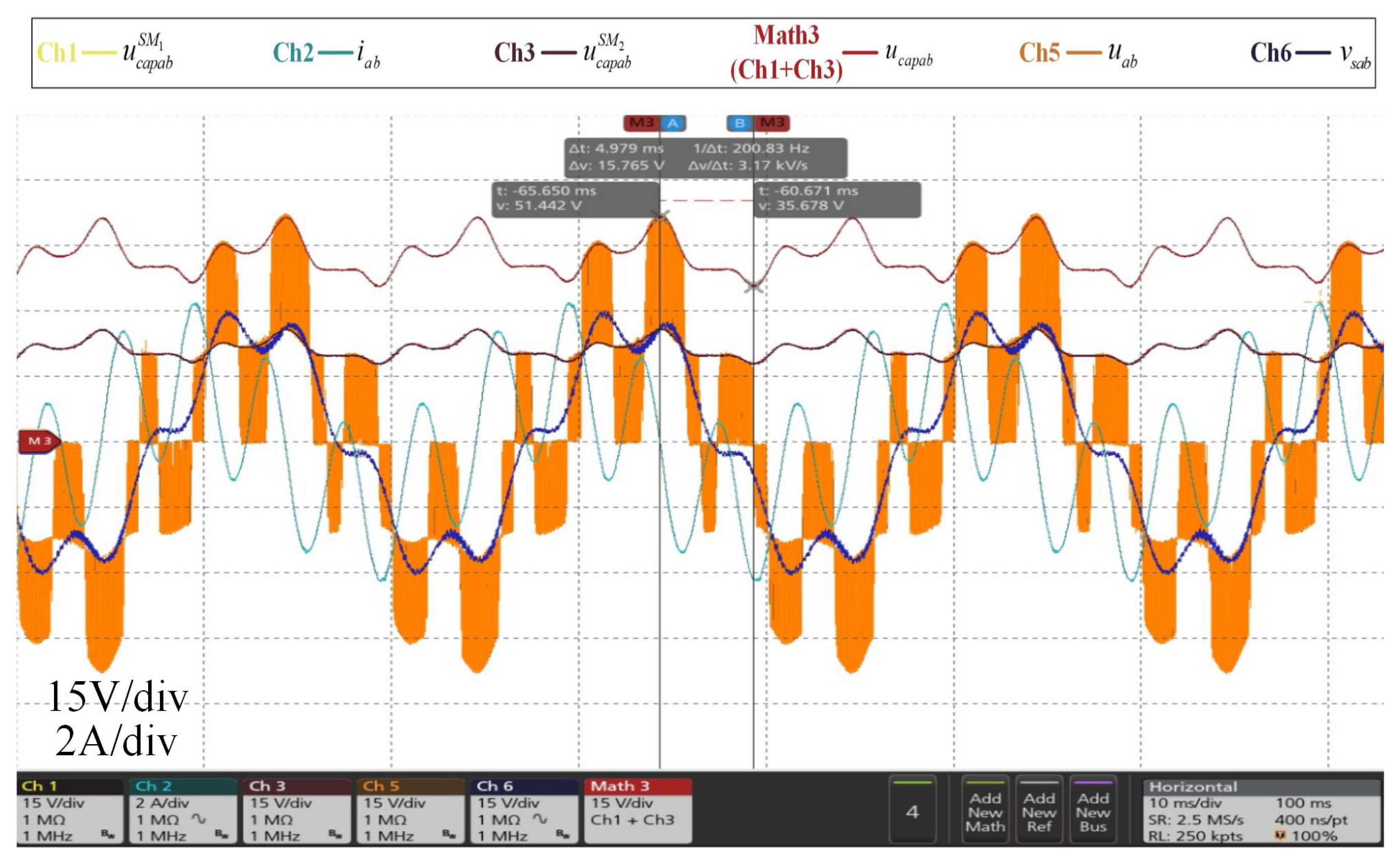

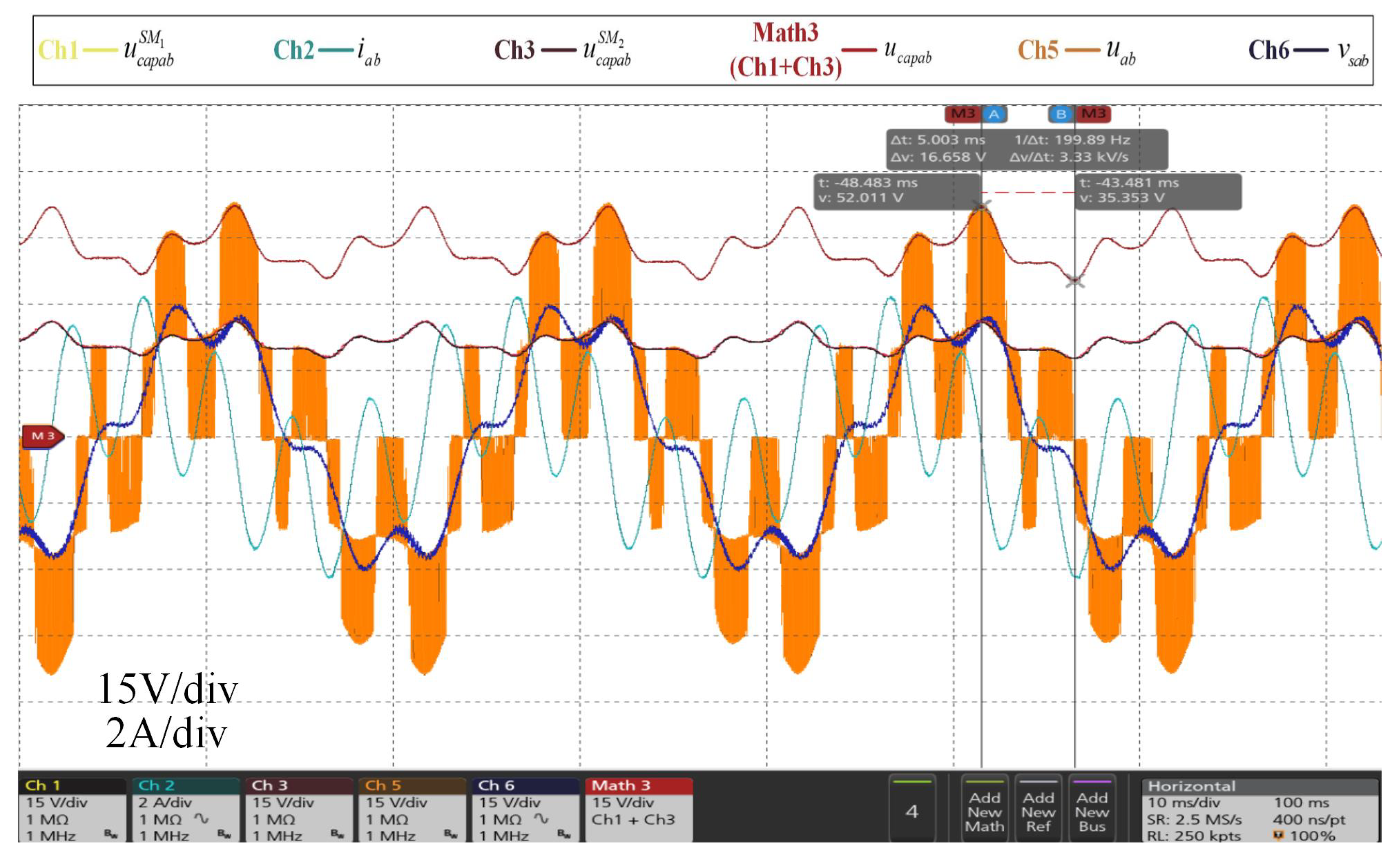

5. Experimental Verification

6. Discussion

7. Conclusions

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

References

- Rao, B.N.; Suresh, Y.; Panda, A.K.; Naik, B.S.; Jammala, V. Development of cascaded multilevel inverter based active power filter with reduced transformers. CPSS Trans. Power Electron. Appl. 2020, 5, 147–157. [Google Scholar] [CrossRef]

- Tarisciotti, L.; Formentini, A.; Gaeta, A.; Degano, M.; Zanchetta, P.; Rabbeni, R.; Pucci, M. Model Predictive Control for Shunt Active Filters With Fixed Switching Frequency. IEEE Trans. Ind. Appl. 2017, 53, 296–304. [Google Scholar] [CrossRef]

- Li, S.; Qi, W.; Tan, S.C.; Hui, S.Y. Integration of an Active Filter and a Single-Phase AC/DC Converter with Reduced Capacitance Requirement and Component Count. IEEE Trans. Power Electron. 2018, 31, 4121–4137. [Google Scholar] [CrossRef]

- Wang, H.; Blaabjerg, F. Reliability of Capacitors for DC-Link Applications in Power Electronic Converters—An Overview. IEEE Trans. Ind. Appl. 2014, 50, 3569–3578. [Google Scholar] [CrossRef]

- Angulo, M.; Ruiz-Caballero, D.A.; Lago, J.; Heldwein, M.L.; Mussa, S.A. Active Power Filter Control Strategy With Implicit Closed-Loop Current Control and Resonant Controller. IEEE Trans. Ind. Electron. 2013, 60, 2721–2730. [Google Scholar] [CrossRef]

- Mannen, T.; Fujita, H. Dynamic Control and Analysis of DC-Capacitor Voltage Fluctuations in Three-Phase Active Power Filters. IEEE Trans. Power Electron. 2016, 31, 6710–6718. [Google Scholar] [CrossRef]

- Bai, H.; Wang, X.; Blaabjerg, F. A Grid-Voltage-Sensorless Resistive-Active Power Filter With Series LC-Filter. IEEE Trans. Power Electron. 2018, 33, 4429–4440. [Google Scholar] [CrossRef]

- Kong, Z.; Huang, X.; Wang, Z.; Xiong, J.; Zhang, K. Active Power Decoupling for Submodules of a Modular Multilevel Converter. IEEE Trans. Power Electron. 2018, 33, 125–136. [Google Scholar] [CrossRef]

- Mellincovsky, M.; Yuhimenko, V.; Zhong, Q.C.; Mordechai Peretz, M.; Kuperman, A. Active DC Link Capacitance Reduction in Grid-Connected Power Conversion Systems by Direct Voltage Regulation. IEEE Access 2018, 6, 18163–18173. [Google Scholar] [CrossRef]

- Du, X.; Zhou, L.; Lu, H.; Tai, H.M. DC Link Active Power Filter for Three-Phase Diode Rectifier. IEEE Trans. Ind. Electron. 2012, 59, 1430–1442. [Google Scholar] [CrossRef]

- Bhus, V.; Lin, J.; Weiss, G. The modular active capacitor for high power ripple attenuation. CPSS Trans. Power Electron. Appl. 2021, 6, 251–262. [Google Scholar] [CrossRef]

- Jia, G.; Chen, M.; Tang, S.; Zhang, C.; Zhu, G. Active Power Decoupling for a Modified Modular Multilevel Converter to Decrease Submodule Capacitor Voltage Ripples and Power Losses. IEEE Trans. Power Electron. 2018, 36, 2835–2851. [Google Scholar] [CrossRef]

- Jin, C.; Tang, Y.; Wang, P.; Liu, X.; Zhu, D.; Frede. Reduction of dc-link capacitance for three-phase three-wire shunt active power filters. In Proceedings of the IECON 2013—39th Annual Conference of the IEEE Industrial Electronics Society, Vienna, Austria, 10–13 November 2013. [Google Scholar]

- Isobe, T.; Shiojima, D.; Kato, K.; Hernandez, Y.R.R.; Shimada, R. Full-Bridge Reactive Power Compensator With Minimized-Equipped Capacitor and Its Application to Static Var Compensator. IEEE Trans. Power Electron. 2016, 31, 224–234. [Google Scholar] [CrossRef]

- Liu, Z.; Li, K.J.; Wang, J.; Javid, Z.; Wang, M.; Sun, K. Research on Capacitance Selection for Modular Multi-Level Converter. IEEE Trans. Power Electron. 2019, 34, 8417–8434. [Google Scholar] [CrossRef]

- Aluminum Electrolytic Capacitors—General Technical Information; Technical Report, TDK Electronics AG. 2022. Available online: https://www.tdk-electronics.tdk.com/download/185386/e724fb43668a157bc547c65b0cff75f8/pdf-generaltechnicalinformation.pdf (accessed on 1 August 2022).

- Farivar, G.; Hredzak, B.; Agelidis, V.G. Reduced-Capacitance Thin-Film H-Bridge Multilevel STATCOM Control Utilizing an Analytic Filtering Scheme. IEEE Trans. Ind. Electron. 2015, 62, 6457–6468. [Google Scholar] [CrossRef]

- Oliveira, R.; Yazdani, A. An Enhanced Steady-State Model and Capacitor Sizing Method for Modular Multilevel Converters for HVdc Applications. IEEE Trans. Power Electron. 2018, 33, 4756–4771. [Google Scholar] [CrossRef]

- Marcos-Pastor, A.; Vidal-Idiarte, E.; Cid-Pastor, A.; Martínez-Salamero, L. Minimum DC-Link Capacitance for Single-Phase Applications With Power Factor Correction. IEEE Trans. Ind. Electron. 2020, 67, 5204–5208. [Google Scholar] [CrossRef]

- Wang, H.; Wang, F.; Gao, F.; Cheng, J. Submodule Capacitor Sizing for Cascaded H-Bridge STATCOM with Sum of Squares Formulation. In Proceedings of the 2022 International Power Electronics Conference (IPEC-Himeji 2022—ECCE Asia), Himeji, Japan, 15–19 May 2022. [Google Scholar]

- Wang, H.; Liu, S. Harmonic Interaction Analysis of Delta-Connected Cascaded H-Bridge-Based Shunt Active Power Filter. IEEE J. Emerg. Sel. Top. Power Electron. 2020, 67, 5204–5208. [Google Scholar] [CrossRef]

- Film Capacitors—General Technical Information; Technical Report, EPCOS AG. 2018. Available online: https://www.vishay.com/docs/26033/gentechinfofilm.pdf (accessed on 24 March 2022).

- Labit, Y.; Peaucelle, D.; Henrion, D. SEDUMI INTERFACE 1.02: A tool for solving LMI problems with SEDUMI. In Proceedings of the IEEE International Symposium on Computer Aided Control System Design, Hyderabad, India, 18–20 September 2002. [Google Scholar]

- Wang, H.; Liu, S. An optimal operation strategy for an active power filter using cascaded H-bridges in delta-connection. Electr. Power Syst. Res. 2019, 175, 105918. [Google Scholar] [CrossRef]

- Gulez, K.; Adam, A.A.; Pastaci, H. Torque Ripple and EMI Noise Minimization in PMSM Using Active Filter Topology and Field-Oriented Control. IEEE Trans. Ind. Electron. 2008, 55, 251–257. [Google Scholar] [CrossRef]

| Constraints (19), (25), (29), (30) | |||||

|---|---|---|---|---|---|

| µF | kV | kV | All constraints satisfied | ||

| µF | 51.7 kV | 35.9 kV | (19), (25),(30) satisfied, omitting (29) | ||

| µF | 50.1 kV | 37.3 kV | (19), (25),(29) satisfied, omitting (30) | ||

| µF | 52.2 kV | 35.5 kV | (19), (25) satisfied, omitting (29), (30) | ||

| µF | 66.7 kV | 17.7 kV | (19) satisfied, omitting (25), (29) and (30) |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2023 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Wang, H.; Gao, F. An Optimal Strategy for Submodule Capacitance Sizing of Cascaded H-Bridge-Based Active Power Filter. Electronics 2023, 12, 4444. https://doi.org/10.3390/electronics12214444

Wang H, Gao F. An Optimal Strategy for Submodule Capacitance Sizing of Cascaded H-Bridge-Based Active Power Filter. Electronics. 2023; 12(21):4444. https://doi.org/10.3390/electronics12214444

Chicago/Turabian StyleWang, Hengyi, and Fei Gao. 2023. "An Optimal Strategy for Submodule Capacitance Sizing of Cascaded H-Bridge-Based Active Power Filter" Electronics 12, no. 21: 4444. https://doi.org/10.3390/electronics12214444