Investigation of Source/Drain Recess Engineering and Its Impacts on FinFET and GAA Nanosheet FET at 5 nm Node

Abstract

:1. Introduction

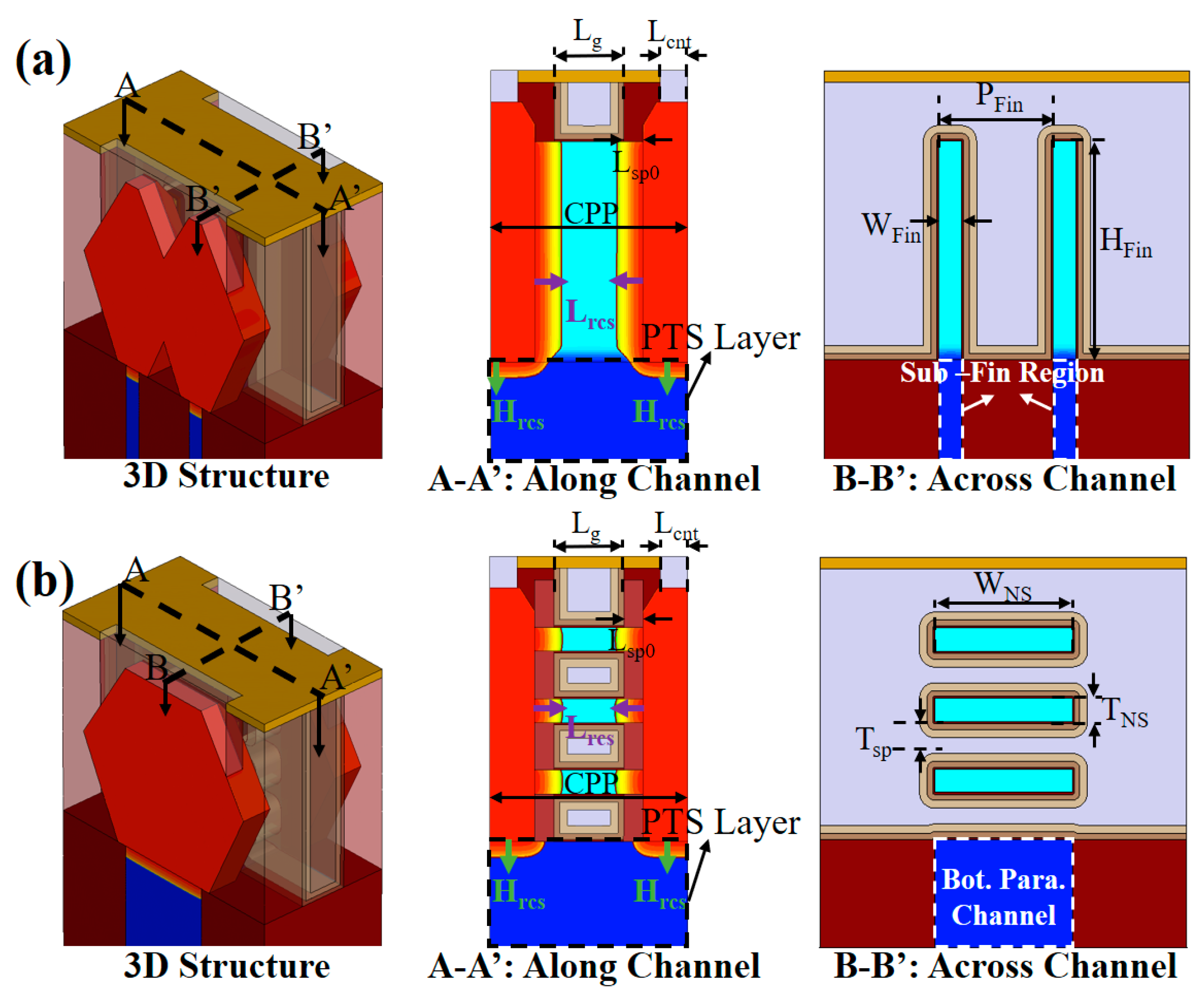

2. Device Structure and Simulation Methodology

3. Results and Discussion

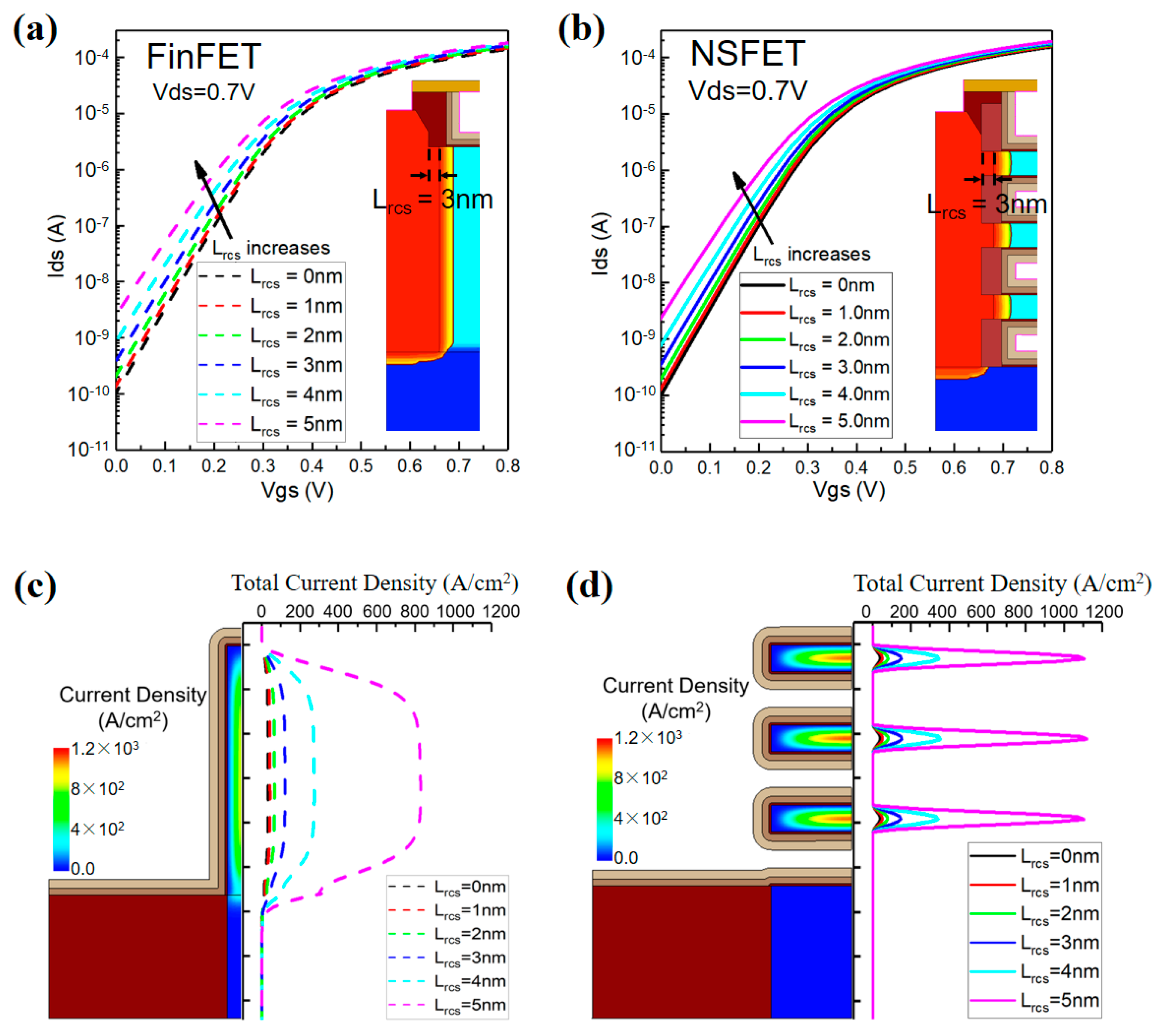

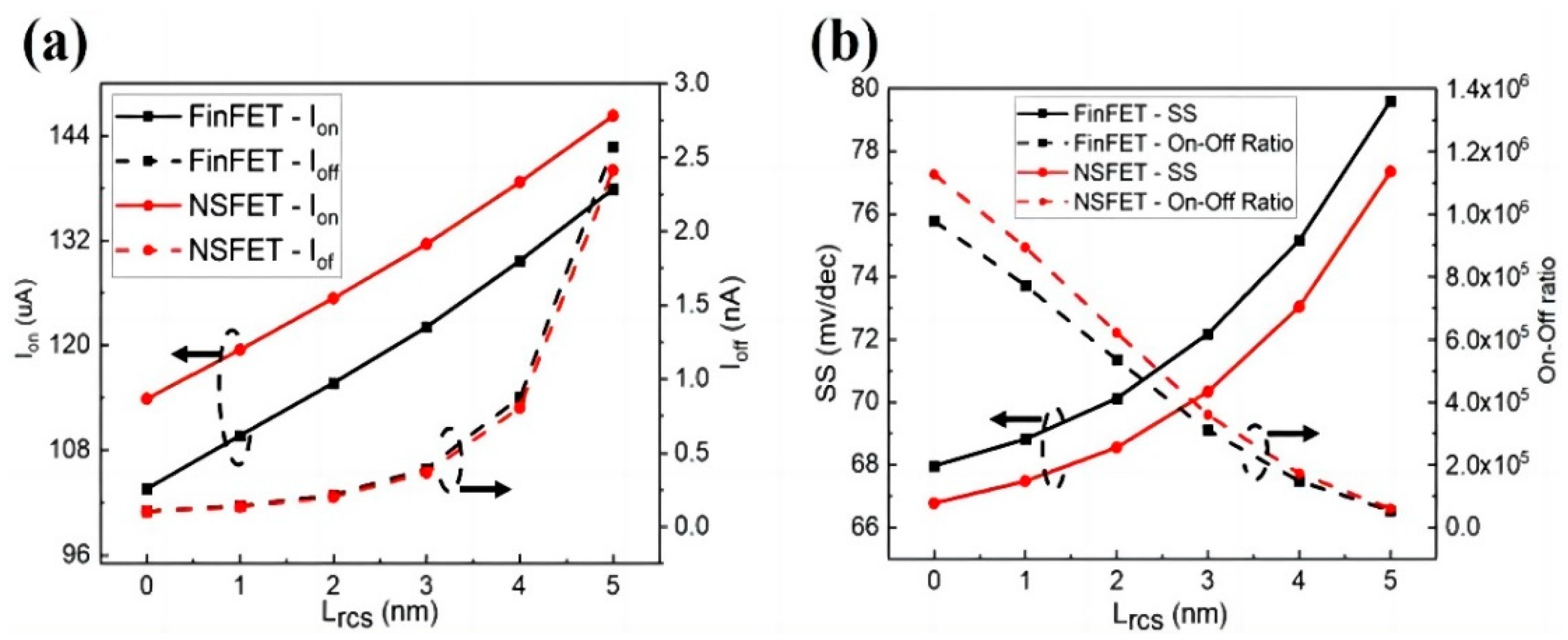

3.1. Lrcs Impacts on Device Performance

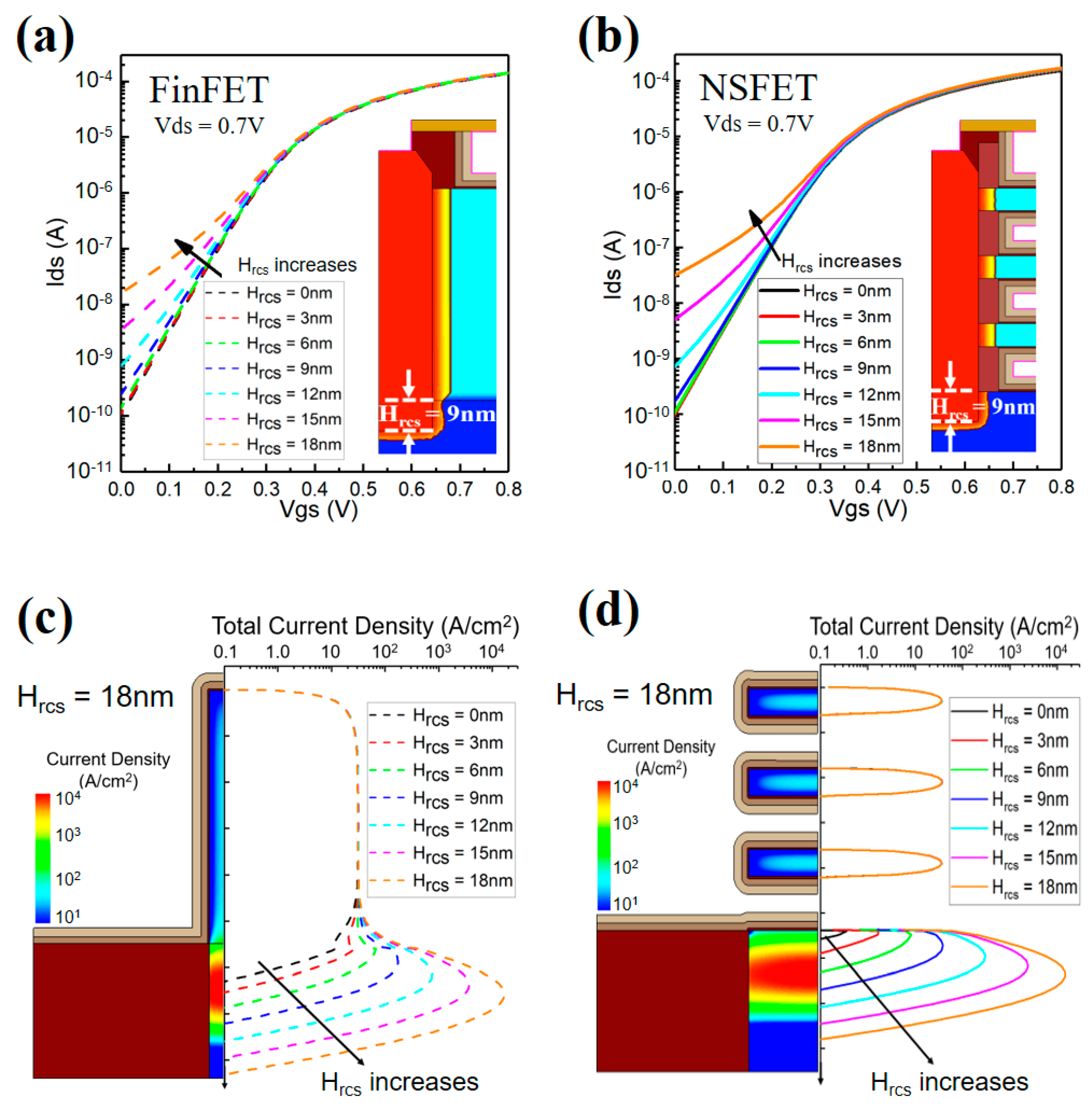

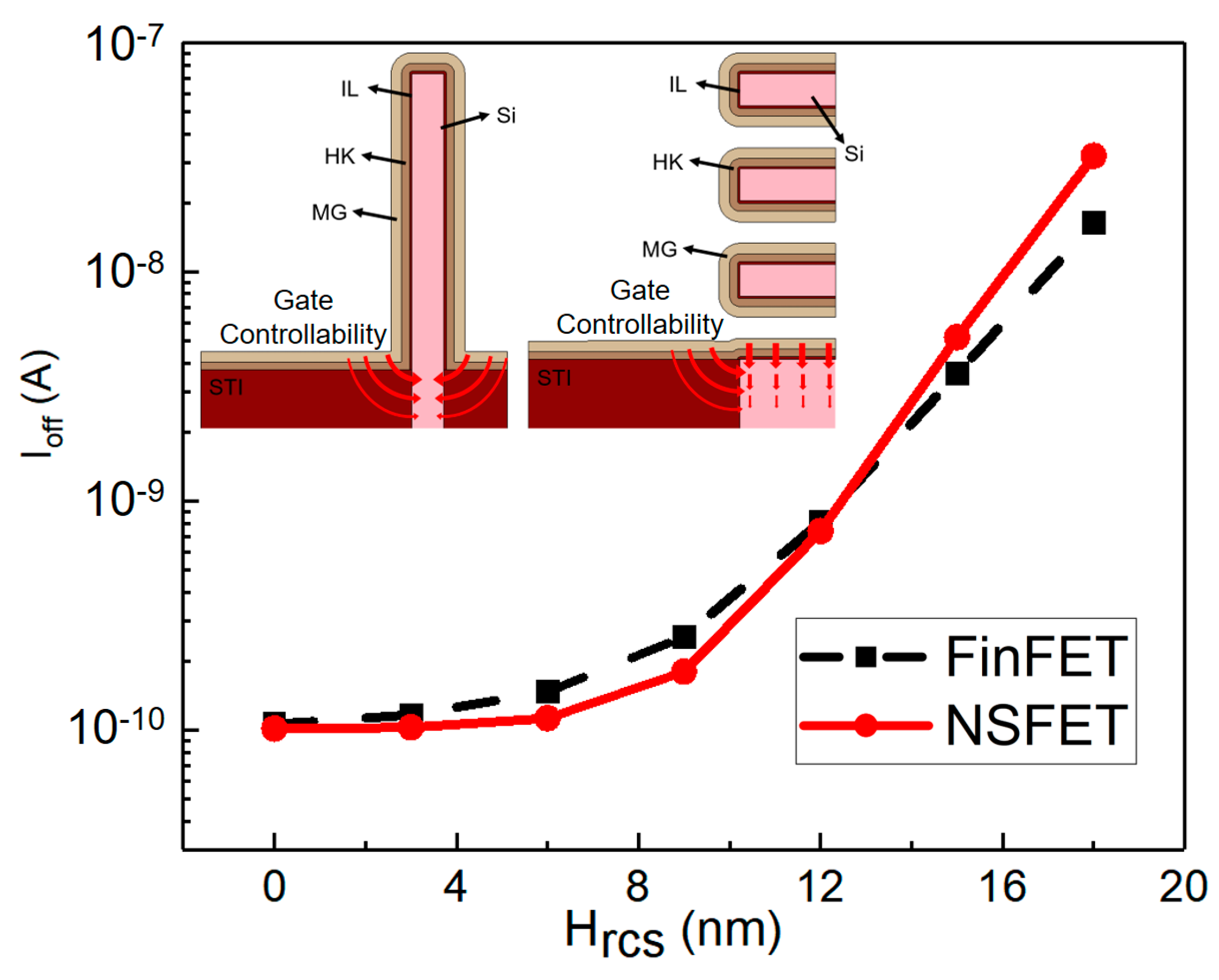

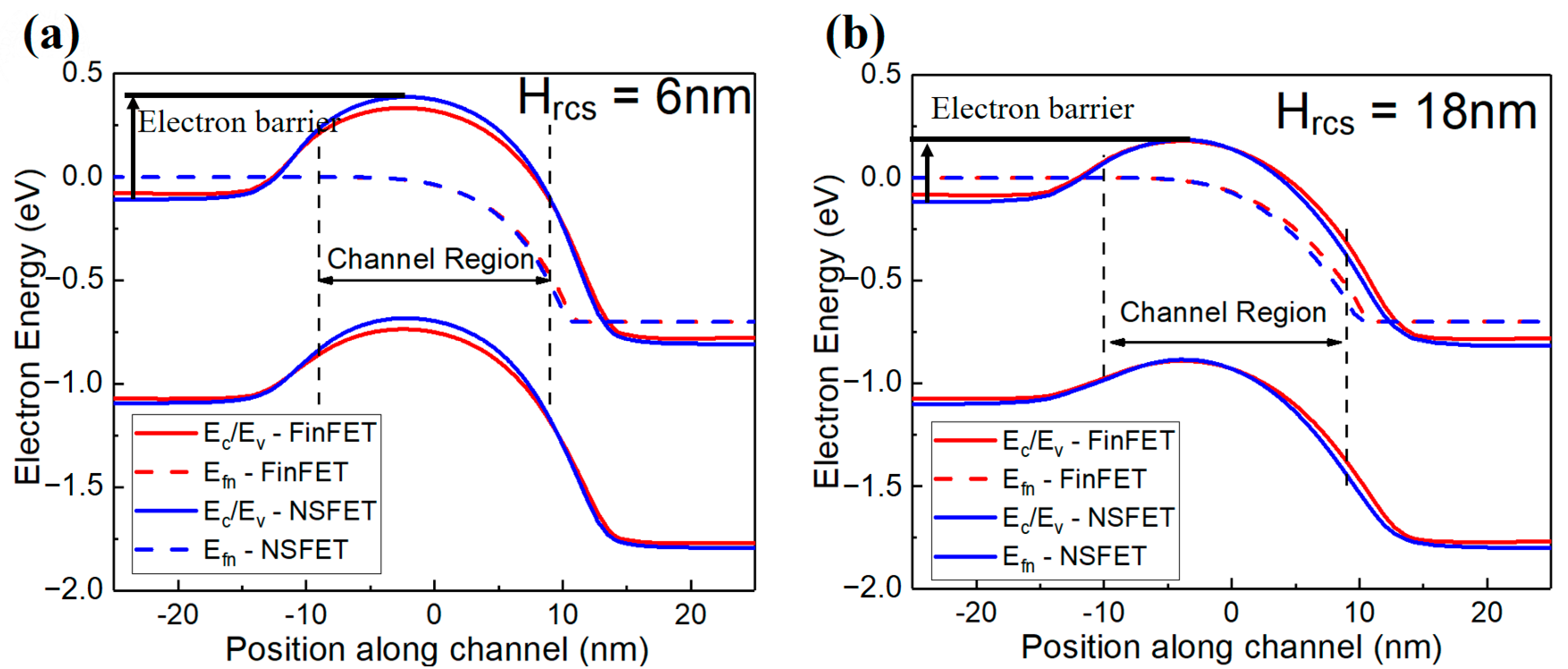

3.2. Hrcs Impacts on Device Performance

3.3. S/D Recess Overall Impacts

4. Conclusions

Author Contributions

Funding

Data Availability Statement

Acknowledgments

Conflicts of Interest

References

- Auth, C.; Allen, C.; Blattner, A.; Bergstrom, D.; Brazier, M.; Bost, M.; Buehler, M.; Chikarmane, V.; Ghani, T.; Glassman, T.; et al. A 22 nm high performance and low-power CMOS technology featuring fully-depleted tri-gate transistors, self-aligned contacts and high density MIM capacitors. In Proceedings of the 2012 Symposium on VLSI Technology (VLSIT), Honolulu, HI, USA, 12–14 June 2012; pp. 131–132. [Google Scholar]

- Natarajan, S.; Agostinelli, M.; Akbar, S.; Bost, M.; Bowonder, A.; Chikarmane, V.; Chouksey, S.; Dasgupta, A.; Fischer, K.; Fu, Q.; et al. A 14 nm logic technology featuring 2nd-generation FinFET, air-gapped interconnects, self-aligned double patterning and a 0.0588 µm2 SRAM cell size. In Proceedings of the 2014 IEEE International Electron Devices Meeting, San Francisco, CA, USA, 15–17 December 2014; pp. 71–73. [Google Scholar]

- Auth, C.; Aliyarukunju, A.; Asoro, M.; Bergstrom, D.; Bhagwat, V.; Birdsall, J.; Bisnik, N.; Buehler, M.; Chikarmane, V.; Ding, G.; et al. A 10nm high performance and low-power CMOS technology featuring 3rd generation FinFET transistors, self-aligned quad patterning, contact over active gate and cobalt local interconnects. In Proceedings of the 2017 IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 2–6 December 2017; pp. 673–676. [Google Scholar]

- Wen, T.Y.; Colombeau, B.; Li, C.I.; Liu, S.Y.; Guo, B.N.; Meer, H.V.; Hou, M.; Yang, B.; Feng, H.C.; Hsu, C.F.; et al. Fin Bending Mitigation and Local Layout Effect Alleviation in Advanced FinFET Technology through Material Engineering and Metrology Optimization. In Proceedings of the 2019 Symposium on VLSI Technology, Kyoto, Japan, 9–14 June 2019. [Google Scholar]

- Razavieh, A.; Zeitzoff, P.; Nowak, E.J. Challenges and Limitations of CMOS Scaling for FinFET and Beyond Architectures. IEEE Trans. Nanotechnol. 2019, 18, 999–1004. [Google Scholar] [CrossRef]

- Loubet, N.; Hook, T.; Montanini, P.; Yeung, C.-W.; Kanakasabapathy, S.; Guillorn, M.; Yamashita, T.; Zhang, J.; Miao, X.; Wang, J.; et al. Stacked nanosheet gate-all-around transistor to enable scaling beyond FinFET. In Proceedings of the 2017 Symposium on VLSI Technology, Kyoto, Japan, 5–8 June 2017; pp. T230–T231. [Google Scholar]

- Mertens, H.; Ritzenthaler, R.; Chasin, A.; Schram, T.; Kunnen, E.; Hikavyy, A.; Ragnarsson, L.-Å.; Dekkers, H.; Hopf, T.; Wostyn, K.; et al. Vertically stacked gate-all-around Si nanowire CMOS transistors with dual work function metal gates. In Proceedings of the 2016 IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 3–7 December 2016; pp. 19.17.11–19.17.14. [Google Scholar]

- Jang, D.; Yakimets, D.; Eneman, G.; Schuddinck, P.; Bardon, M.G.; Raghavan, P.; Spessot, A.; Verkest, D.; Mocuta, A. Device Exploration of NanoSheet Transistors for Sub-7-nm Technology Node. IEEE Trans. Electron Devices 2017, 64, 2707–2713. [Google Scholar] [CrossRef]

- Song, T.; Kim, H.; Rim, W.; Jung, H.; Park, C.; Lee, I.; Baek, S.; Jung, J. A 3-nm Gate-All-Around SRAM Featuring an Adaptive Dual-Bitline and an Adaptive Cell-Power Assist Circuit. IEEE J. Solid-State Circuits 2022, 57, 236–244. [Google Scholar] [CrossRef]

- Kim, S.; Kim, M.; Ryu, D.; Lee, K.; Kim, S.; Lee, J.; Lee, R.; Kim, S.; Lee, J.-H.; Park, B.-G. Investigation of Electrical Characteristic Behavior Induced by Channel-Release Process in Stacked Nanosheet Gate-All-Around MOSFETs. IEEE Trans. Electron Devices 2020, 67, 2648–2652. [Google Scholar] [CrossRef]

- Vincent, B.; Hathwar, R.; Kamon, M.; Ervin, J.; Schram, T.; Chiarella, T.; Demuynck, S.; Baudot, S.; Siew, Y.K.; Kubicek, S.; et al. Process Variation Analysis of Device Performance Using Virtual Fabrication: Methodology Demonstrated on a CMOS 14-nm FinFET Vehicle. IEEE Trans. Electron Devices 2020, 67, 5374–5380. [Google Scholar] [CrossRef]

- Rezali, F.A.M.; Othman, N.A.F.; Mazhar, M.; Hatta, S.W.M.; Soin, N. Performance and Device Design Based on Geometry and Process Considerations for 14/16-nm Strained FinFETs. IEEE Trans. Electron Devices 2016, 63, 974–981. [Google Scholar] [CrossRef]

- Kim, S.; Lee, K.; Kim, S.; Kim, M.; Lee, J.-H.; Kim, S.; Park, B.-G. Investigation of Device Performance for Fin Angle Optimization in FinFET and Gate-All-Around FETs for 3 nm-Node and Beyond. IEEE Trans. Electron Devices 2022, 69, 2088–2093. [Google Scholar] [CrossRef]

- Kranti, A.; Armstrong, G.A. Optimization of the source/drain extension region profile for suppression of short channel effects in sub-50 nm DG MOSFETs with high-κ gate dielectrics. Semicond. Sci. Technol. 2006, 21, 1563–1572. [Google Scholar] [CrossRef]

- Kranti, A.; Armstrong, G.A. Engineering source/drain extension regions in nanoscale double gate (DG) SOI MOSFETs: Analytical model and design considerations. Solid-State Electron. 2006, 50, 437–447. [Google Scholar] [CrossRef]

- Yang, J.-W.; Pham, D.; Zeitzoff, P.; Huff, H.; Brown, G. Optimization of Source/Drain Extension for Robust Speed Performance to Process Variation in Undoped Double-Gate CMOS. In Proceedings of the International Symposium on VLSI Technology, Systems, and Applications, Hsinchu, Taiwan, 24–26 April 2006; pp. 1–2. [Google Scholar]

- Jeong, J.; Yoon, J.-S.; Lee, S.; Baek, R.-H. Comprehensive Analysis of Source and Drain Recess Depth Variations on Silicon Nanosheet FETs for Sub 5-nm Node SoC Application. IEEE Access 2020, 8, 35873–35881. [Google Scholar] [CrossRef]

- Barraud, S.; Previtali, B.; Lapras, V.; Vizioz, C.; Hartmann, J.-M.; Martinie, S.; Lacord, J.; Cassé, M.; Dourthe, L.; Loup, V.; et al. Tunability of Parasitic Channel in Gate-All-Around Stacked Nanosheets. In Proceedings of the 2018 IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 1–5 December 2018; pp. 21.23.21–21.23.24. [Google Scholar]

- Gu, J.; Zhang, Q.; Wu, Z.; Luo, Y.; Cao, L.; Cai, Y.; Yao, J.; Zhang, Z.; Xu, G.; Yin, H.; et al. Narrow Sub-Fin Technique for Suppressing Parasitic-Channel Effect in Stacked Nanosheet Transistors. IEEE J. Electron Devices Soc. 2022, 10, 35–39. [Google Scholar] [CrossRef]

- Zhang, J.; Frougier, J.; Greene, A.; Miao, X.; Yu, L.; Vega, R.; Montanini, P.; Durfee, C.; Gaul, A.; Pancharatnam, S.; et al. Full Bottom Dielectric Isolation to Enable Stacked Nanosheet Transistor for Low Power and High Performance Applications. In Proceedings of the 2019 IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 7–11 December 2019; pp. 11.16.11–11.16.14. [Google Scholar]

- Wu, Y.-S.; Tsai, C.-H.; Miyashita, T.; Chen, P.-N.; Hsu, B.-C.; Wu, P.-H.; Hsu, H.-H.; Chiang, C.-Y.; Liu, H.-H.; Yang, H.-L.; et al. Optimization of fin profile and implant in bulk FinFET technology. In Proceedings of the International Symposium on VLSI Technology, Systems and Application (VLSI-TSA), Hsinchu, Taiwan, 25–27 April 2016; pp. 1–2. [Google Scholar]

- Wu, H.; Seo, S.-C.; Niu, C.; Wang, W.; Tsutsui, G.; Gluschenkov, O.; Liu, Z.; Petrescu, A.; Carr, A.; Choi, S.; et al. Integrated dual SPE processes with low contact resistivity for future CMOS technologies. In Proceedings of the 2017 IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 2–6 December 2017; pp. 22.23.21–22.23.24. [Google Scholar]

- Yoon, J.-S.; Lee, S.; Lee, J.; Jeong, J.; Yun, H.; Kang, B.; Baek, R.-H. Source/Drain Patterning FinFETs as Solution for Physical Area Scaling Toward 5-nm Node. IEEE Access 2019, 7, 172290–172295. [Google Scholar] [CrossRef]

- Lee, J.; Yoon, J.-S.; Lee, S.; Jeong, J.; Baek, R.-H. TCAD-Based Flexible Fin Pitch Design for 3-nm Node 6T-SRAM Using Practical Source/Drain Patterning Scheme. IEEE Trans. Electron Devices 2021, 68, 1031–1036. [Google Scholar] [CrossRef]

- Roy, K.; Mukhopadhyay, S.; Mahmoodi-Meimand, H. Leakage current mechanisms and leakage reduction techniques in deep-submicrometer CMOS circuits. Proc. IEEE 2003, 91, 305–327. [Google Scholar] [CrossRef]

- IRDS. International Roadmap for Devices and Systems 2020 (IRDS 2020). Available online: https://irds.ieee.org/ (accessed on 31 July 2021).

- Wang, L.; Brown, A.; Cheng, B.; Asenov, A. Simulation of 3D FinFET doping profiles introduced by ion implantation and the impact on device performance. In Proceedings of the 20th International Conference on Ion Implantation Technology (IIT), Portland, OR, USA, 26 June–4 July 2014; pp. 1–4. [Google Scholar]

- Eneman, G.; Hellings, G.; Keersgieter, A.D.; Collaert, N.; Thean, A. Quantum-barriers and ground-plane isolation: A path for scaling bulk-FinFET technologies to the 7 nm-node and beyond. In Proceedings of the 2013 IEEE International Electron Devices Meeting, Washington, DC, USA, 9–11 December 2013; pp. 12.13.11–12.13.14. [Google Scholar]

- Wu, H.; Gluschenkov, O.; Tsutsui, G.; Niu, C.; Brew, K.; Durfee, C.; Prindle, C.; Kamineni, V.; Mochizuki, S.; Lavoie, C.; et al. Parasitic Resistance Reduction Strategies for Advanced CMOS FinFETs Beyond 7 nm. In Proceedings of the 2018 IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 1–5 December 2018; pp. 35.34.31–35.34.34. [Google Scholar]

- Synopsys, Inc. TCAD Sentaurus Device User Guide; Synopsys Inc.: Mountain View, CA, USA, 2020. [Google Scholar]

- Klaassen, D.B.M.; Slotboom, J.W.; Graaff, H.C.D. Unified apparent bandgap narrowing in n- and p-type silicon. Solid-State Electron. 1992, 35, 125–129. [Google Scholar] [CrossRef]

- Ancona, M.G.; Tiersten, H.F. Macroscopic physics of the silicon inversion layer. Phys. Rev. B 1987, 35, 7959–7965. [Google Scholar] [CrossRef]

- Ancona, M.G.; Iafrate, G.J. Quantum correction to the equation of state of an electron gas in a semiconductor. Phys. Rev. B 1989, 39, 9536–9540. [Google Scholar] [CrossRef]

- Hurkx, G.A.M.; Klaassen, D.B.M.; Knuvers, M.P.G. A new recombination model for device simulation including tunneling. IEEE Trans. Electron Devices 1992, 39, 331–338. [Google Scholar] [CrossRef]

- Oldiges, P.; Vega, R.A.; Utomo, H.K.; Lanzillo, N.A.; Wassick, T.; Li, J.; Wang, J.; Shahidi, G.G. Chip Power-Frequency Scaling in 10/7 nm Node. IEEE Access 2020, 8, 154329–154337. [Google Scholar] [CrossRef]

- Wu, S.-Y.; Lin, C.Y.; Chiang, M.C.; Liaw, J.J.; Cheng, J.Y.; Chang, C.H.; Chang, V.S.; Pan, K.H.; Tsai, C.H.; Yao, C.H.; et al. Demonstration of a sub-0.03 um2 High Density 6-T SRAM with Scaled Bulk FinFETs for Mobile SOC Applications Beyond 10 nm Node. In Proceedings of the 2016 IEEE Symposium on VLSI Technology, Honolulu, HI, USA, 14–16 June 2016; pp. 1–2. [Google Scholar]

- Gupta, M.K.; Weckx, P.; Schuddinck, P.; Jang, D.; Chehab, B.; Cosemans, S.; Ryckaert, J.; Dehaene, W. A Comprehensive Study of Nanosheet and Forksheet SRAM for Beyond N5 Node. IEEE Trans. Electron Devices 2021, 68, 3819–3825. [Google Scholar] [CrossRef]

- Nibhanupudi, S.S.T.; Prasad, D.; Das, S.; Zografos, O.; Robinson, A.; Gupta, A.; Spessot, A.; Debacker, P.; Verkest, D.; Ryckaert, J.; et al. A Holistic Evaluation of Buried Power Rails and Back-Side Power for Sub-5 nm Technology Nodes. IEEE Trans. Electron Devices 2022, 69, 4453–4459. [Google Scholar] [CrossRef]

- Yoon, J.-S.; Jeong, J.; Lee, S.; Baek, R.-H. Systematic DC/AC Performance Benchmarking of Sub-7-nm Node FinFETs and Nanosheet FETs. IEEE J. Electron Devices Soc. 2018, 6, 942–947. [Google Scholar] [CrossRef]

| Parameters | Value | |

|---|---|---|

| Both | Contact gate pitch (CPP) | 51 nm |

| Gate length (Lg) | 18 nm | |

| Spacer length (Lsp0) | 5 nm | |

| Contact length (Lcnt) | 14 nm | |

| S/D doping (Nsd) | 2 × 1020 cm−3 | |

| Channel Doping (Nch) | 1 × 1015 cm−3 | |

| Punch-Through Stop Doping (NPTS) | 2 × 1018 cm−3 | |

| Fin | Number of Fin | 2 |

| Fin width (WFin) | 6 nm | |

| Fin height (HFin) | 56 nm | |

| Fin pitch (PFin) | 30 nm | |

| GAA | Number of Nanosheet | 3 |

| NS width (WNS) | 36 nm | |

| NS Thickness (TNS) | 6 nm | |

| NS Spacing (Tsp) | 12 nm |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2023 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Wang, D.; Sun, X.; Liu, T.; Chen, K.; Yang, J.; Wu, C.; Xu, M.; Zhang, W. Investigation of Source/Drain Recess Engineering and Its Impacts on FinFET and GAA Nanosheet FET at 5 nm Node. Electronics 2023, 12, 770. https://doi.org/10.3390/electronics12030770

Wang D, Sun X, Liu T, Chen K, Yang J, Wu C, Xu M, Zhang W. Investigation of Source/Drain Recess Engineering and Its Impacts on FinFET and GAA Nanosheet FET at 5 nm Node. Electronics. 2023; 12(3):770. https://doi.org/10.3390/electronics12030770

Chicago/Turabian StyleWang, Dawei, Xin Sun, Tao Liu, Kun Chen, Jingwen Yang, Chunlei Wu, Min Xu, and Wei (David) Zhang. 2023. "Investigation of Source/Drain Recess Engineering and Its Impacts on FinFET and GAA Nanosheet FET at 5 nm Node" Electronics 12, no. 3: 770. https://doi.org/10.3390/electronics12030770