Analyzing Power Losses and Performance of an Isolated DC-DC Converter for Renewable Energies Systems

Abstract

:1. Introduction

- (1)

- Easy implementation.

- (2)

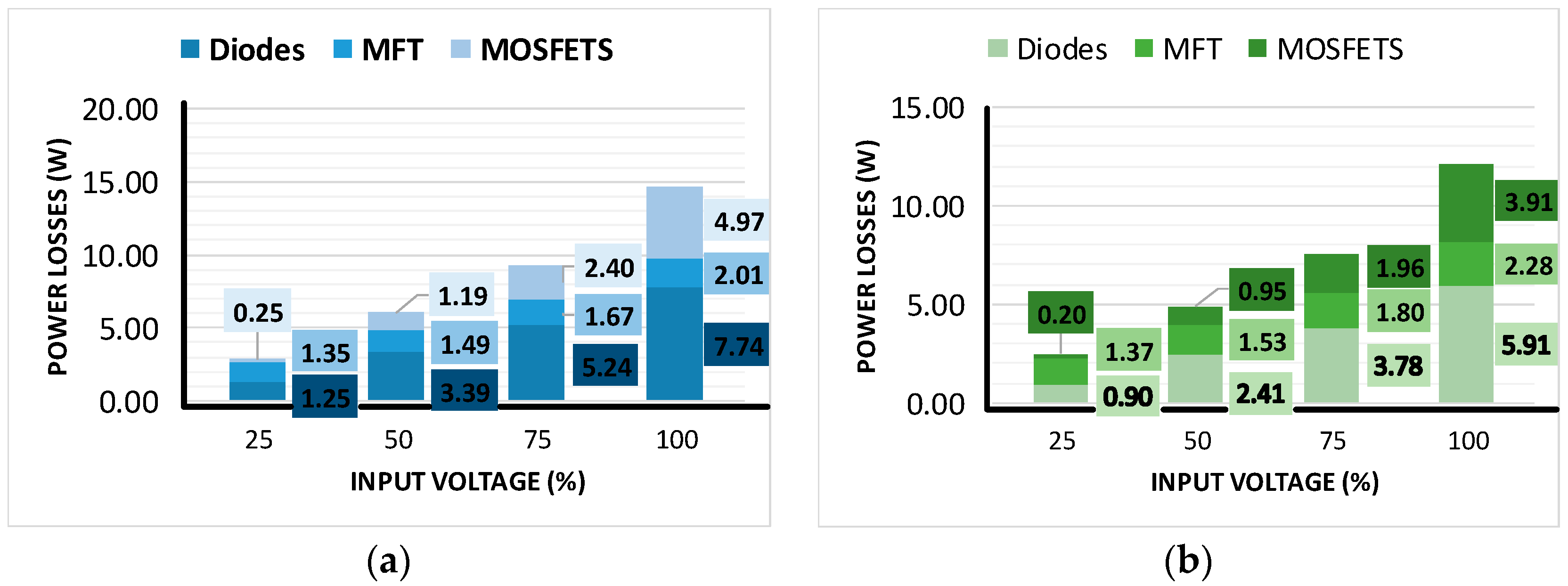

- The individual losses in each element (passive, active and transformer semiconductors) were considered.

- (3)

- Low-loss, high-efficiency DC-DC converter.

- (4)

- Isolated DC-DC converter.

- (5)

- DC-DC converter subjected to different THD values in the central stage (MFT).

- (6)

- Validation in simulation and laboratory.

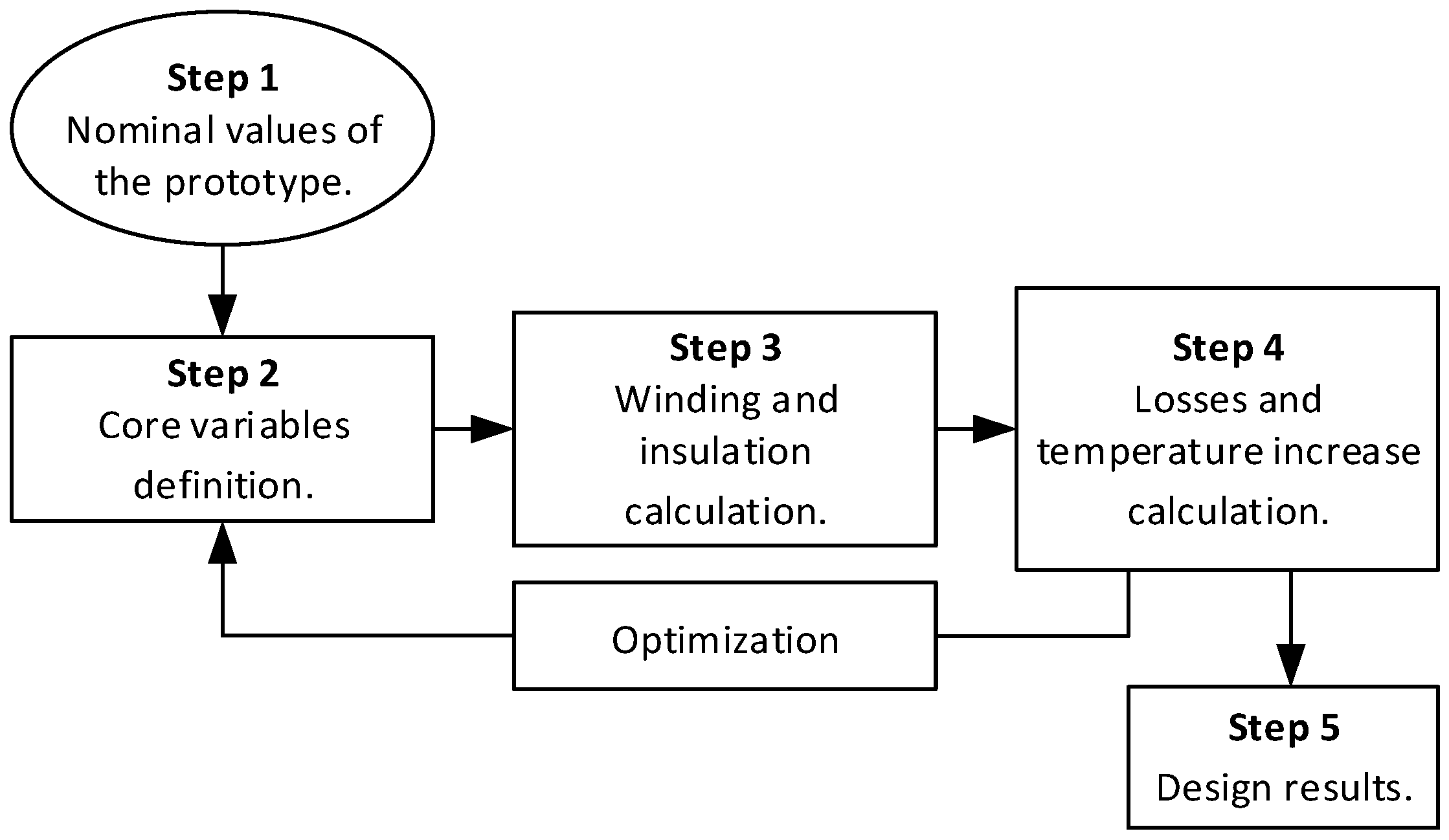

2. MFT Design Methodology with 2L and 3L Feeding

2.1. Multilevel Topologies

2.2. Full-Bridge Converter (FBDC)

2.3. Estimation of Semiconductors Losses

- ID(RMS): RMS current flowing through the MOSFET.

- ID(ON): current through the MOSFET.

- D: MOSFET duty cycle.

- RDS(ON): MOSFET turn-on resistor.

- PON: MOSFET turn-on losses.

- POFF: MOSFET turn-off losses.

- fSW: switching frequency.

- VDD: Blocking voltage on the MOSFET.

- tON: MOSFET turn-on time.

- tOFF: MOSFET turn-off time.

- VF: diode activation voltage.

- IF(AVG): current flowing in the diode.

- IF(RMS): RMS current flowing in the diode.

- δ: diode duty cycle.

- RD(ON): diode-on resistor.

- IMAX: maximum current in direct polarization in the diode.

- IMIN: minimum current in direct polarization in the diode.

3. FBDC Converter, Simulation, and Experimentation Results

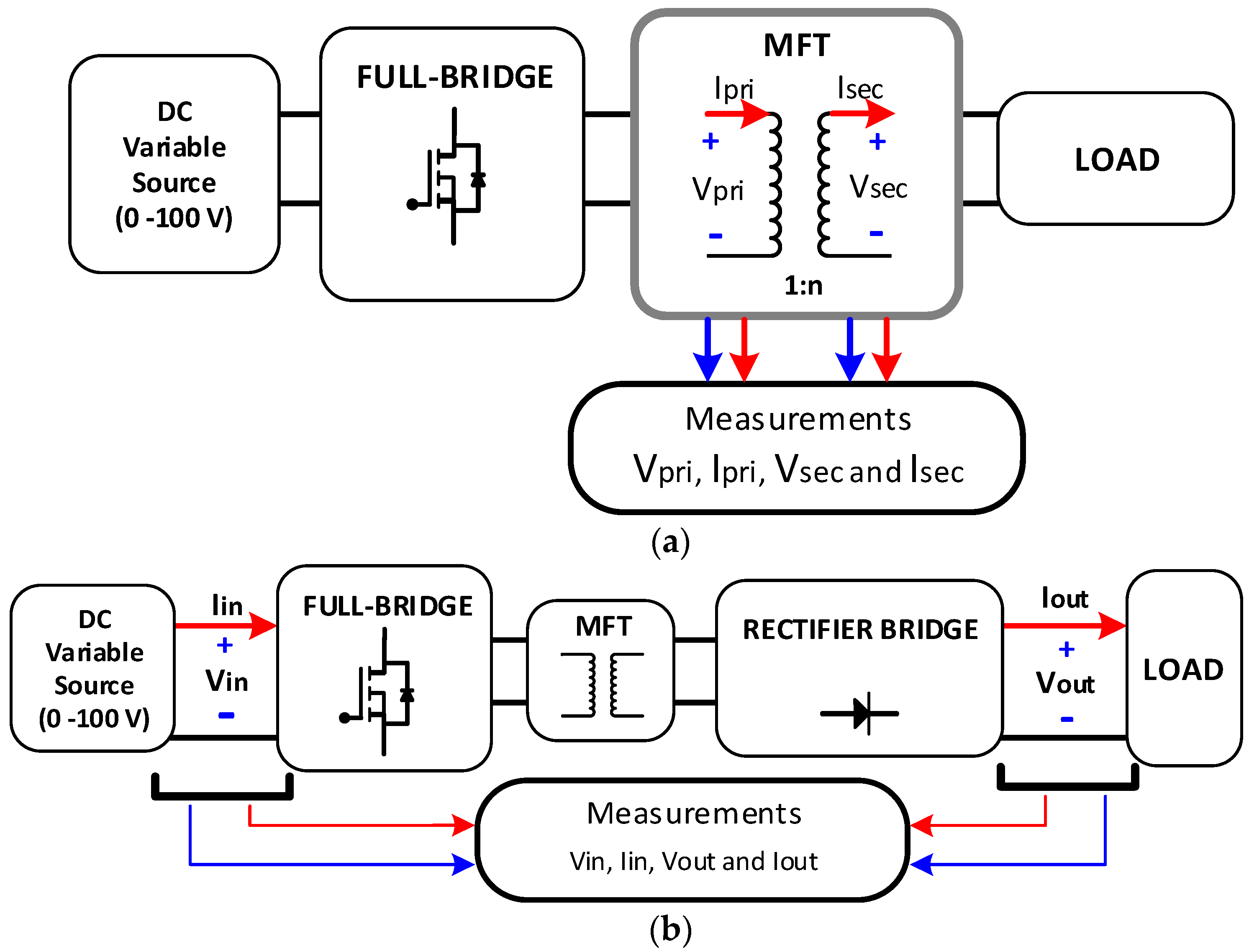

3.1. MFT Analysis under Power Supply with Different THD

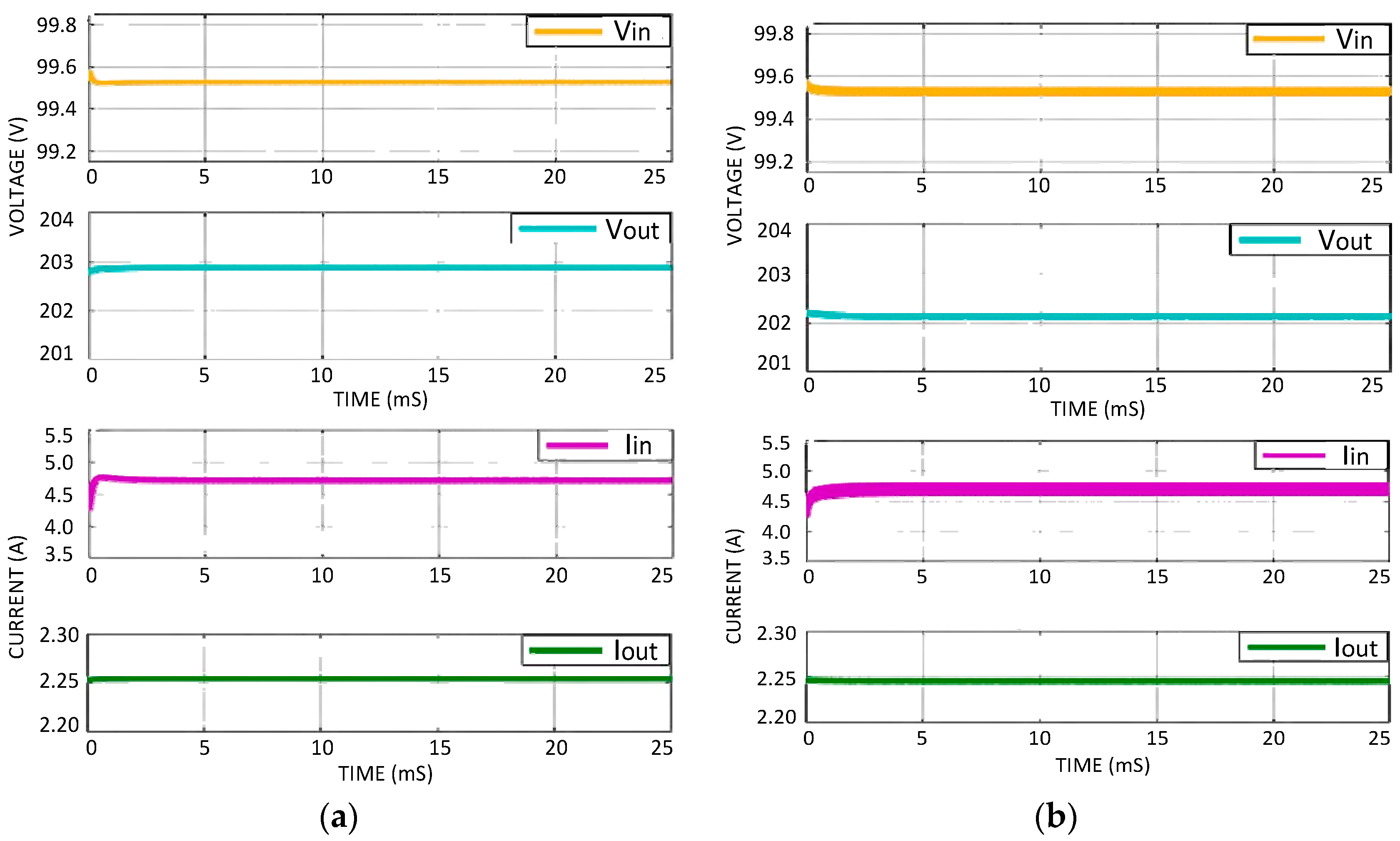

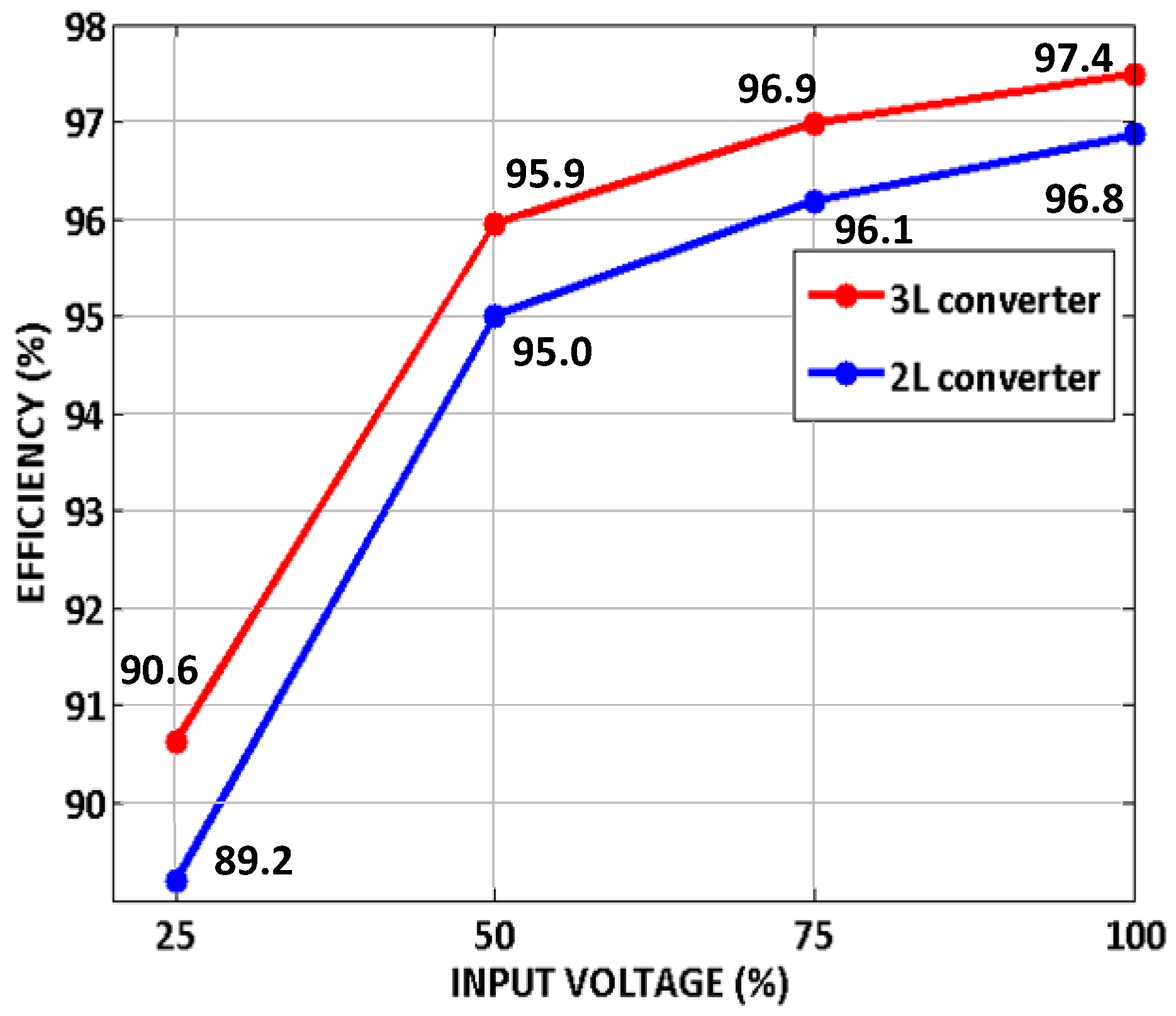

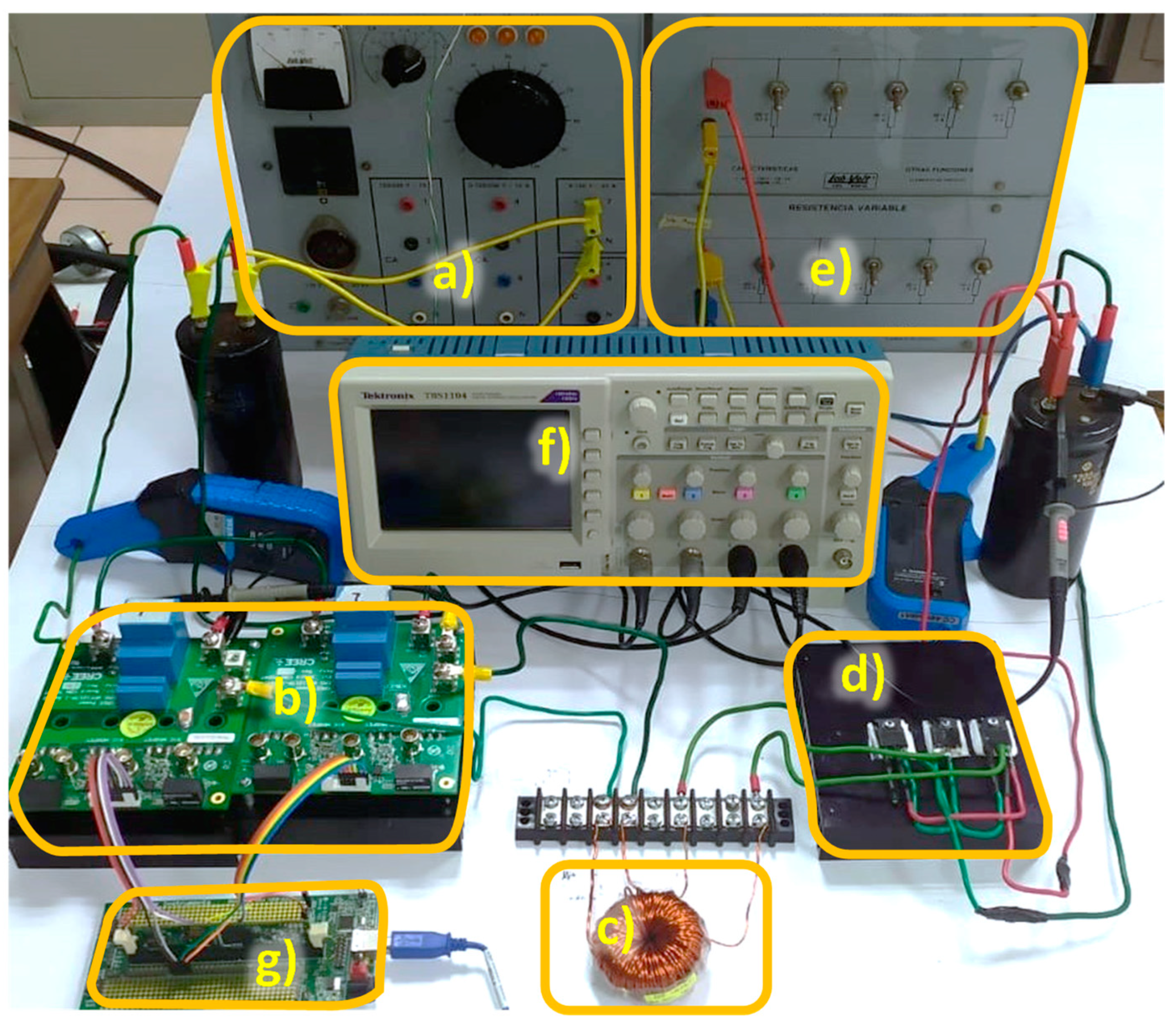

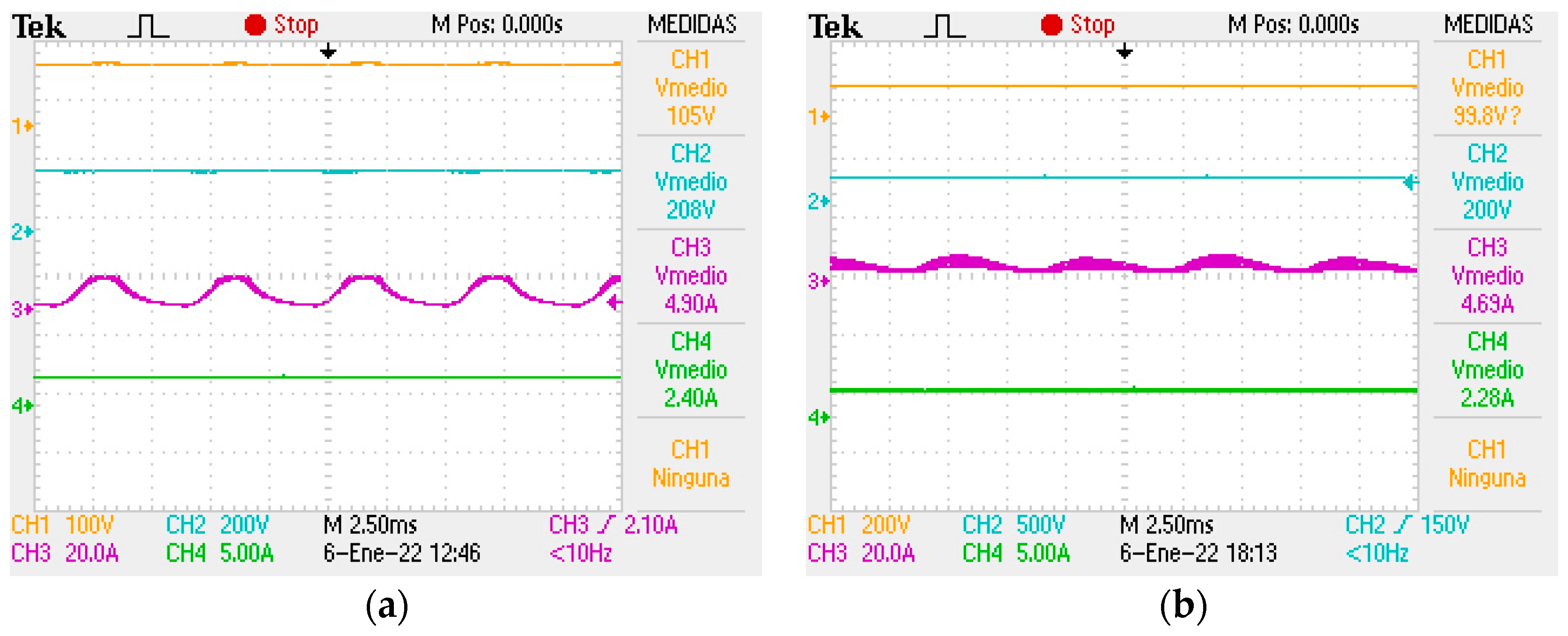

3.2. Experimental Results

4. Discussion

5. Conclusions

Author Contributions

Funding

Data Availability Statement

Acknowledgments

Conflicts of Interest

References

- Luo, J.; Bu, S.; Chung, C. Design and comparison of auxiliary resonance controllers for mitigating modal resonance of power systems integrated with wind generation. IEEE Trans. Power Syst. 2021, 36, 3372–3383. [Google Scholar] [CrossRef]

- Raghavendra, K.V.G.; Zeb, K.; Muthusamy, A.; Krishna, T.N.V.; Prabhudeva Kumar, S.V.S.V.; Kim, D.-H.; Kim, M.-S.; Cho, H.-G.; Kim, H.-J. A comprehensive review of DC–DC converter topologies and modulation strategies with recent advances in solar photovoltaic systems. Electronics 2020, 9, 31. [Google Scholar] [CrossRef] [Green Version]

- Sai, T.; Moon, Y.; Sugimoto, Y. Improved Quasi-Z-Source High Step-Up DC–DC Converter Based on Voltage-Doubler Topology. Sensors 2022, 22, 9893. [Google Scholar] [CrossRef] [PubMed]

- Kim, D.; Kim, M.-S.; Nengroo, S.H.; Kim, C.-H.; Kim, H.-J. LLC resonant converter for LEV (Light Electric Vehicle) fast chargers. Electronics 2019, 8, 362. [Google Scholar] [CrossRef] [Green Version]

- Hong, T.; Zhi, G.; Qi, K.; Zhao, X.; Ambrosio, J.; Gu, D. A Wide Range Unidirectional Isolated DC-DC Converter for Fuel Cell Electric Vehicles. IEEE Trans. Ind. Electron. 2021, 68, 5932–5943. [Google Scholar] [CrossRef]

- Srivastava, M.; Kumar, A.; Singh, P. Design and analysis of customised pulse width modulation based dc–dc converter for EV battery charging application. IET Power Electron. 2020, 13, 3549–3559. [Google Scholar] [CrossRef]

- Zhao, L.; Luo, Z.; Fan, Z.; Shi, Y. A dual half-bridge converter with hybrid rectifier for DC power supply in railway systems. IEEE Trans. Power Electron. 2019, 35, 4579–4587. [Google Scholar] [CrossRef]

- Marzang, V.; Hashemzadeh, S.; Alavi, P.; Khoshkbar-Sadigh, A.; Hosseini, S.; Malik, M.Z. A Modified Triple-Switch Triple-Mode High Step-Up DC–DC Converter. IEEE Trans. Ind. Electron. 2022, 69, 8015–8027. [Google Scholar] [CrossRef]

- Alhurayyis, I.; Elkhateb, A.; Morrow, J. Isolated and nonisolated DC-to-DC converters for medium-voltage DC networks: A review. IEEE J. Emerg. Sel. Top. Power Electron. 2020, 9, 7486–7500. [Google Scholar] [CrossRef]

- Mumtaz, F.; Yahaya, N.Z.; Meraj, S.T.; Singh, B.; Kannan, R.; Ibrahim, O. Review on non-isolated DC-DC converters and their control techniques for renewable energy applications. Ain Shams Eng. J. 2021, 12, 3747–3763. [Google Scholar] [CrossRef]

- Hashemzadeh, S.M.; Marzang, V.; Pourjafar, S.; Hosseini, S.H. An Ultra High Step-Up Dual-Input Single-Output DC–DC Converter Based on Coupled Inductor. IEEE Trans. Ind. Electron. 2022, 69, 11023–11034. [Google Scholar] [CrossRef]

- Ram, B.; Paul, A.; Kulkarni, S. Soft magnetic materials and their applications in transformers. Magnet. and Mag. Mat. 2021, 537, 168210. [Google Scholar] [CrossRef]

- Chen, H.; Divan, D. High-frequency transformer design for the soft-switching solid state transformer (S4T). In Proceedings of the 2017 IEEE Applied Power Electronics Conference and Exposition (APEC), Tampa, FL, USA, 26–30 March 2017; pp. 2534–2541. [Google Scholar] [CrossRef]

- Huang, P.; Mao, C.; Wang, D.; Wang, L.; Duan, Y.; Qiu, J.; Xu, G.; Cai, H. Optimal design and implementation of high-voltage high-power silicon steel core medium-frequency transformer. IEEE Trans. Ind. Electron. 2017, 64, 4391–4401. [Google Scholar] [CrossRef]

- Ruiz, D.; Venegas-Rebollar, V.; Anaya-Ruiz, A.; Moreno-Goytia, E.L.; Rodríguez-Rodríguez, J.R. Design and prototyping medium-frequency transformers featuring a nanocrystalline core for dc–dc converters. Energies 2018, 11, 2081. [Google Scholar] [CrossRef] [Green Version]

- Ruiz, D.; Ortíz, J.; Moreno, E.; Fuerte, C.; Venegas, V.; Vargas, A.; Vergara, H. Ferrites and Nanocrystalline Alloys Applied to DC–DC Converters for Renewable Energies. Appl. Sci. 2022, 12, 709. [Google Scholar] [CrossRef]

- Rodriguez, J.; Sheng, J.; Zheng, F. Multilevel inverters: A survey of topologies, controls, and applications. IEEE Trans. Ind. Electron. 2002, 49, 724–738. [Google Scholar] [CrossRef] [Green Version]

- Yan, Y.; Huang, Y.; Chen, R.; Bai, H. Building Common-Mode Analytical Model for Dual Active Bridge Incorporating with Different Modulation Strategies. IEEE Trans. Power Electron. 2021, 36, 12608–12619. [Google Scholar] [CrossRef]

- Moonem, M.; Pechacek, C.; Hernandez, R.; Krishnaswami, H. Analysis of a multilevel dual active bridge (ML-DAB) DC-DC converter using symmetric modulation. Electronics 2015, 4, 239–260. [Google Scholar] [CrossRef] [Green Version]

- Lin, B. DC–DC converter implementation with wide output voltage operation. J. Power Electron. 2020, 20, 376–387. [Google Scholar] [CrossRef]

- Han, J.; Moon, G. High-efficiency phase-shifted full-bridge converter with a new coupled inductor rectifier (CIR). IEEE Trans. Power Electron. 2019, 34, 8468–8480. [Google Scholar] [CrossRef]

- Ozdemir, S.; Balci, S.; Altin, N.; Sefa, I. Design and performance analysis of the three-level isolated DC-DC converter with the nanocyrstalline core transformer. Int. J. Hydrog. Energy 2017, 42, 17801–17812. [Google Scholar] [CrossRef]

- Liu, D.; Wang, Y.; Deng, F.; Chen, Z. Triple-phase-shift modulation strategy for diode-clamped full-bridge three-level isolated DC/DC converter. IEEE Access 2019, 8, 2750–2759. [Google Scholar] [CrossRef]

- Liu, D.; Wang, Y.; Zhang, Q.; Chen, Z. ZVZCS full-bridge three-level DC/DC converter with reduced device count. IEEE Trans. Power Electron. 2020, 35, 9965–9970. [Google Scholar] [CrossRef]

- Zhao, L.; Chen, J.; Chen, T.; Shi, Y.; Fan, Z.; Zhuang, Z. Zero-voltage and zero-current switching dual-transformer-based full-bridge converter with current doubler rectifier. IEEE Trans. Power Electron. 2020, 35, 12949–12958. [Google Scholar] [CrossRef]

- Liu, D.; Deng, F.; Zhang, Q.; Chen, Z. Periodically swapping modulation (PSM) strategy for three-level (TL) DC/DC converters with balanced switch currents. IEEE Trans. Ind. Electron. 2017, 65, 412–423. [Google Scholar] [CrossRef] [Green Version]

- Shi, Y.; Wang, X.; Xi, J.; Gui, X.; Yang, X. Wide load range ZVZCS three-level DC–DC converter with compact structure. IEEE Trans. Power Electron. 2018, 34, 5032–5037. [Google Scholar] [CrossRef]

- Liu, P.; Chen, C.; Duan, S.; Jin, L.; Zhu, W. A three-level rectifier structure with flying capacitors for DC–DC converter in high-voltage output application. IEEE Trans. Ind. Electron. 2017, 65, 2122–2134. [Google Scholar] [CrossRef]

- McLyman, C. Power Transformer Design. In Transformer and Inductor Design Handbook; CRC Press: Boca Raton, FL, USA, 2011; ISBN 978-1-4398-3688-0. [Google Scholar]

- Hilzinger, R. Magnetic Materials; Germany Publishing: Erlangen, Germany, 2013; ISBN 978-3895783524. [Google Scholar]

- Colak, I.; Kabalci, E.; Bayindir, R. Review of multilevel voltage source inverter topologies and control schemes. Energy Convers. Manag. 2011, 52, 1114–1128. [Google Scholar] [CrossRef]

- Rana, R.; Patel, S.A.; Muthusamy, A.; Lee, C.W.; Kim, H.-J. Review of multilevel voltage source inverter topologies and analysis of harmonics distortions in FC-MLI. Electronics 2019, 8, 1329. [Google Scholar] [CrossRef] [Green Version]

- Revathi, B.; Mahalingam, P.; Gonzalez, F. Interleaved high gain DC-DC converter for integrating solar PV source to DC bus. Sol. Energy 2019, 188, 924–934. [Google Scholar] [CrossRef]

- Ahmed, M.; Wang, M.; Shehzad, M.; Ullah, I. Power loss model and efficiency analysis of three-phase inverter based on SiC MOSFETs for PV applications. IEEE Access 2019, 7, 75768–75781. [Google Scholar] [CrossRef]

- Hafezi, H.; Faranda, R. A new approach for power losses evaluation of IGBT/diode module. Electronics 2021, 10, 280. [Google Scholar] [CrossRef]

| Variable | Value |

|---|---|

| Pnom | 500 VA |

| V1 | 100 V |

| V2 | 200 V |

| f | 20 kHz |

| R1 | 16.5 mΩ |

| R2 | 68.5 mΩ |

| Ld1 | 0.5 µH |

| Ld2 | 2.1 µH |

| Rm | 8832 Ω |

| Lm | 35.4 mH |

| Levels | Vpri Vin | Vsec Vout | Ipri Iin | Isec Iout | Efficiency | |

|---|---|---|---|---|---|---|

| MFT | 2L | 99.3 V | 197.8 V 200.3 V | 4.41 A 4.46 A | 2.2 A 2.23 A | 99.54% 99.55% |

| 3L | 100.5 V | |||||

| DC-DC Converter | 2L | 99.5 V 99.5 V | 202.9 V 202.2 V | 4.75 A 4.71 A | 2.25 A 2.25 A | 96.8% 97.4% |

| 3L |

| Parameter | Value |

|---|---|

| Core material | Nanocrystalline (Vitroperm 500F, W514) |

| Frequency | 20 kHz |

| Core type | Toroidal |

| Core dimensions | 3 × 2 × 1.5 cm |

| Np | 20 turns |

| Ns | 41 turns |

| Primary winding calibre | 15 AWG |

| Secondary winding calibre | 18 AWG |

| Flux density | 0.8 T |

| Permeability | 53, 355 |

| Ref. | Freq. (kHz) | Power (W) | No. Devices | Converter Efficciency (%) | Transformer | Year | |||

|---|---|---|---|---|---|---|---|---|---|

| Semi- Conductor | Passive | Design | Material | Efficiency (%) | |||||

| [4] | 30–100 | 1000 | 8 | 4 | 96.4/96.2/96.4 | – | – | – | 2019 |

| [5] | 100 | 2500 | 8 | 5 | 94.5 | – | Ferrites | 98.2 | 2021 |

| [6] | 80 | 540 | 8 | 3 | 91.4 | ✓ | Ferrites | – | 2020 |

| [19] | 5 | 3340 | 16 | 4 | 88.0 | ✓ | Amorphous | 93.0 | 2015 |

| [22] | 10 | 5000 | 8/16 | 2/4 | 81.0/92.0 | ✓ | Nanocryst. | 94.0/96.0 | 2017 |

| [23] | 50 | 1000 | 16 | 7 | 93.3 | – | – | – | 2019 |

| [27] | 100 | 1100 | 10 | 6 | 95.0 | – | – | – | 2018 |

| This proposal | 20 | 500 | 8 | 2 | 96.6/97.0 | ✓ | Nanocryst. | 99.6/99.7 | |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2023 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Ortíz-Marín, J.; Gallo-Reyes, D.; Ruiz-Robles, D.; Venegas-Rebollar, V. Analyzing Power Losses and Performance of an Isolated DC-DC Converter for Renewable Energies Systems. Electronics 2023, 12, 1110. https://doi.org/10.3390/electronics12051110

Ortíz-Marín J, Gallo-Reyes D, Ruiz-Robles D, Venegas-Rebollar V. Analyzing Power Losses and Performance of an Isolated DC-DC Converter for Renewable Energies Systems. Electronics. 2023; 12(5):1110. https://doi.org/10.3390/electronics12051110

Chicago/Turabian StyleOrtíz-Marín, Jorge, Diego Gallo-Reyes, Dante Ruiz-Robles, and Vicente Venegas-Rebollar. 2023. "Analyzing Power Losses and Performance of an Isolated DC-DC Converter for Renewable Energies Systems" Electronics 12, no. 5: 1110. https://doi.org/10.3390/electronics12051110