In recent years, microwave wireless power transfer (MWPT) has attracted much attention as a method of powering sensor ICs of IoT devices [

1]. Using 1 trillion sensor ICs per year is predicted in the near future by development of 5G and Artificial Intelligence [

2]. If each of these devices is equipped with batteries, a large number of sensor ICs will need to be maintained for the battery with a significant cost increase. MWPT can reduce this cost, and ultimately, reduce this to zero. In addition, because MWPT uses electromagnetic (EM) waves for the power source, a wireless communication network can be built in the same time to receive and transmit sensed data. A MWPT system mainly consists of a transmitter for radiating EM waves and a receiver with a receiving antenna and a rectifier for capturing the radiated EM waves. This combination of receiving antenna and rectifier is called a rectenna [

3].

Figure 1 shows a block diagram of a rectenna.

This research aims at extending the transmission distance focused on the rectifier part of rectenna circuit for low power application, or at reducing the lower operating power limit of rectennas, with a rectifier circuit area small enough to be integrated in sensor ICs. According to Friis’s formula, transmission distance is inversely proportional to received power squared [

4]. By extending the transmission distance, powering to increased sensor ICs in a wide range such as factories is enabled with only one transmitter.

Research on MWPT techniques has been conducted on a wide range of topics, including optimal rectenna design methodology and improving the performance of rectifier circuits. In [

5], it was reported that a circuit topology of minimizing the junction capacitance of diodes to achieve higher conversion efficiency under the condition of constant antenna impedance was used. The most significant parameter for conversion efficiency was analyzed in [

6], and the circuit topology proposed in [

5] in accordance with this analysis. In [

7], the optimal rectenna design is conducted on considering parasitic elements generated by integration for combination of specific antenna and specific on-chip rectifier. The authors of [

8] proposed the design methodology for selecting the optimum rectifier from multiple types for specific antenna types to explore a larger design space than in [

5,

6,

7]. Furthermore, the authors of [

9] proposed a methodology to select the best combination of multiple types of antennas and rectifiers by using the model calculation. The analysis covering a wider range of design conditions can be conducted in a shorter time than in [

8]. These works focused on the optimum rectenna design. In [

10], a circuit topology was proposed to cancel the threshold voltage by connecting the gates of NMOS and PMOS in each stage of the rectifier unit to the output and input terminals, respectively, because threshold voltage has a great effect on the conversion efficiency of on-chip rectifier. However, under the high-power operation condition, there is a disadvantage—reverse leakage current becomes large because of the gate bias is excessive. The authors of [

11] added a second rectifying path to store excessive charges in a storage capacitor when the input power is extremely large. When the input power is not sufficient, sensor ICs are operated with the energy in the storage capacitor stored in advance. This method realized −29.0 dBm sensitivity under a 0.44 V/1.9 µA output condition. However, it is necessary to input −15.4 dBm or higher beforehand. In [

12], a LC-oscillator-driven rectifier is proposed to increase the output voltage even with very low input power. A −34.5 dBm sensitivity under a 1.6 V/0.89 µA instantaneous output condition by supplying additional low DC voltage of 0.3 V is reported in this work. In [

13], sensitivity was improved by using an RF–DC charge pump (CP) with 50 stages of the simplest diode-connected transistors. This work reported that a low input power of −32.1 dBm is required to obtain the output voltage 1 V for a capacitive load. The authors of [

14] reported high sensitivity can be achieved with only six rectification stages by applying self-bias to the gates of rectifying transistors. Although the number of stages are not many, the area becomes large because more transistors and capacitors are needed in the bias circuit. A −30.0 dBm sensitivity is reported in this work under a 1 V output condition for a capacitive load. In [

15], it is reported that high sensitivity and tolerance against temperature fluctuation and process corner variations are achieved by connecting five stages of a voltage doubler with two types of rectifying diodes. This work reports that an input power of −33.0 dBm is required to obtain the output voltage 1 V for a 1 GΩ load. Another design approach is adopting an on-chip transformer together with an on-chip rectifier [

16]. With the proposed design procedure, the input impedance of the on-chip transformer can be matched with that of the antenna.

In this research, both a small rectifier circuit and high sensitivity are prioritized. The design starts with an initial assumption of a sufficiently small capacitor per stage of RF–DC CP but sufficiently large so as not to be affected by parasitic capacitance such as junction capacitance and wring capacitance. The rest design parameters are determined one by one under the condition that the input power required to generate 1 V at the output terminal of the RF–DC CP is minimized.

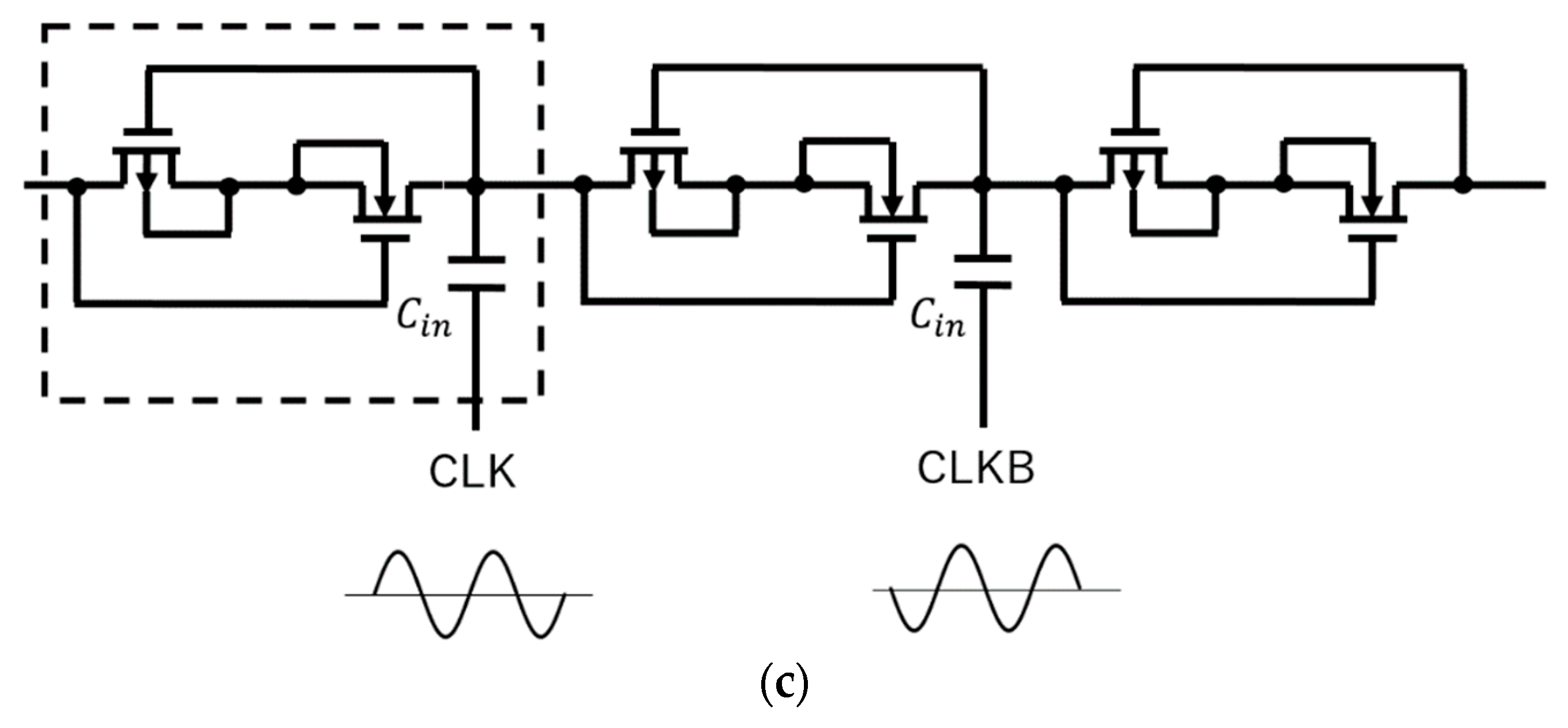

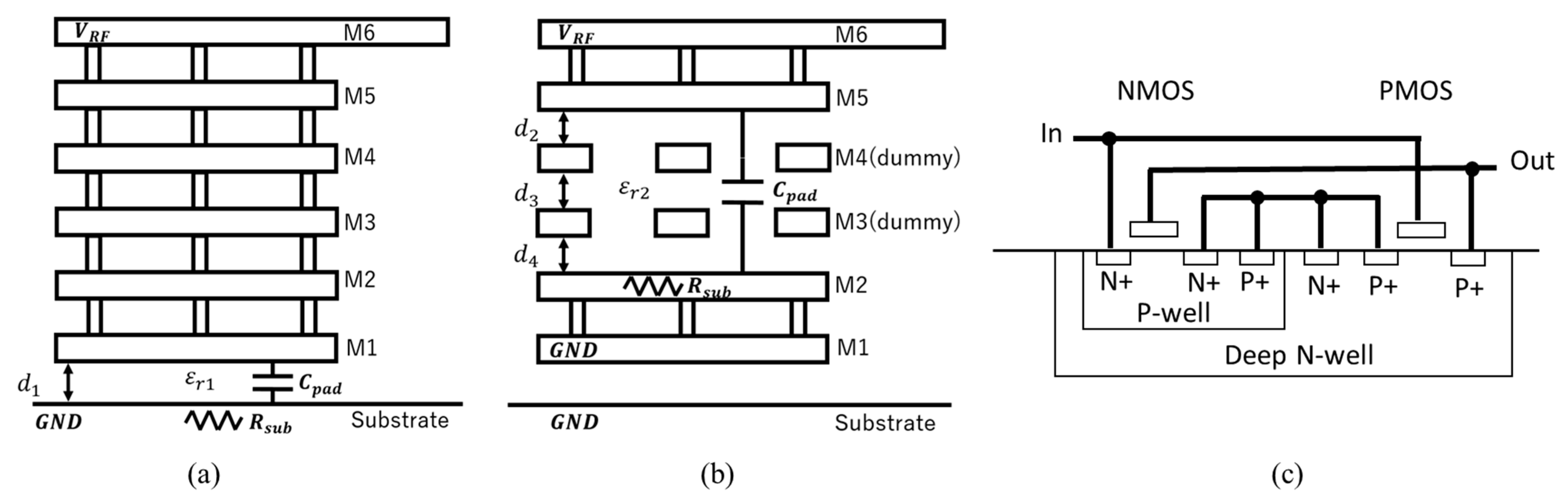

Section 2 shows the characteristics and schematics of rectifiers composing each stage to be optimized.

Section 3 explains the optimization flow of the rectifier unit and determined optimum circuit parameters.

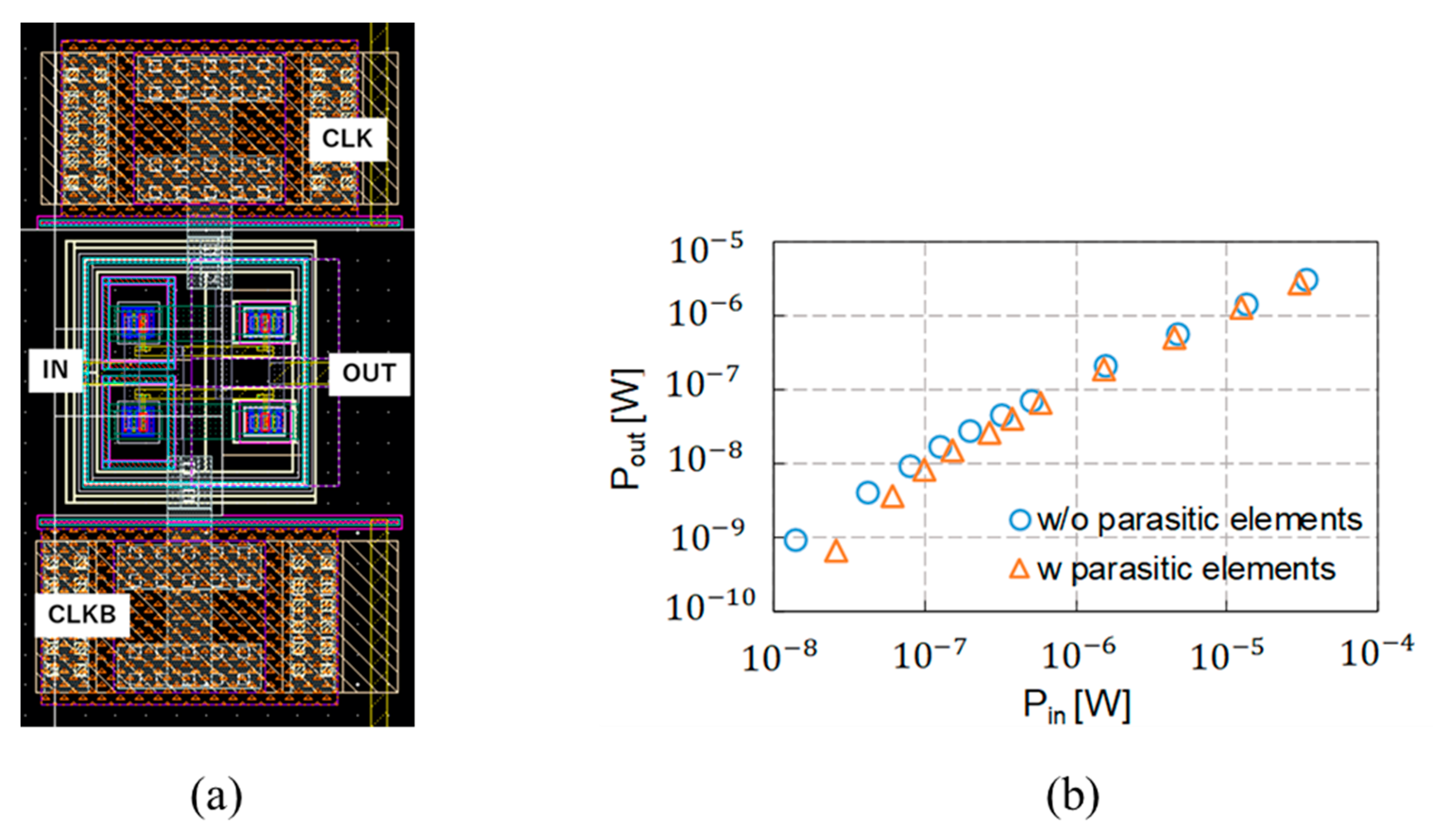

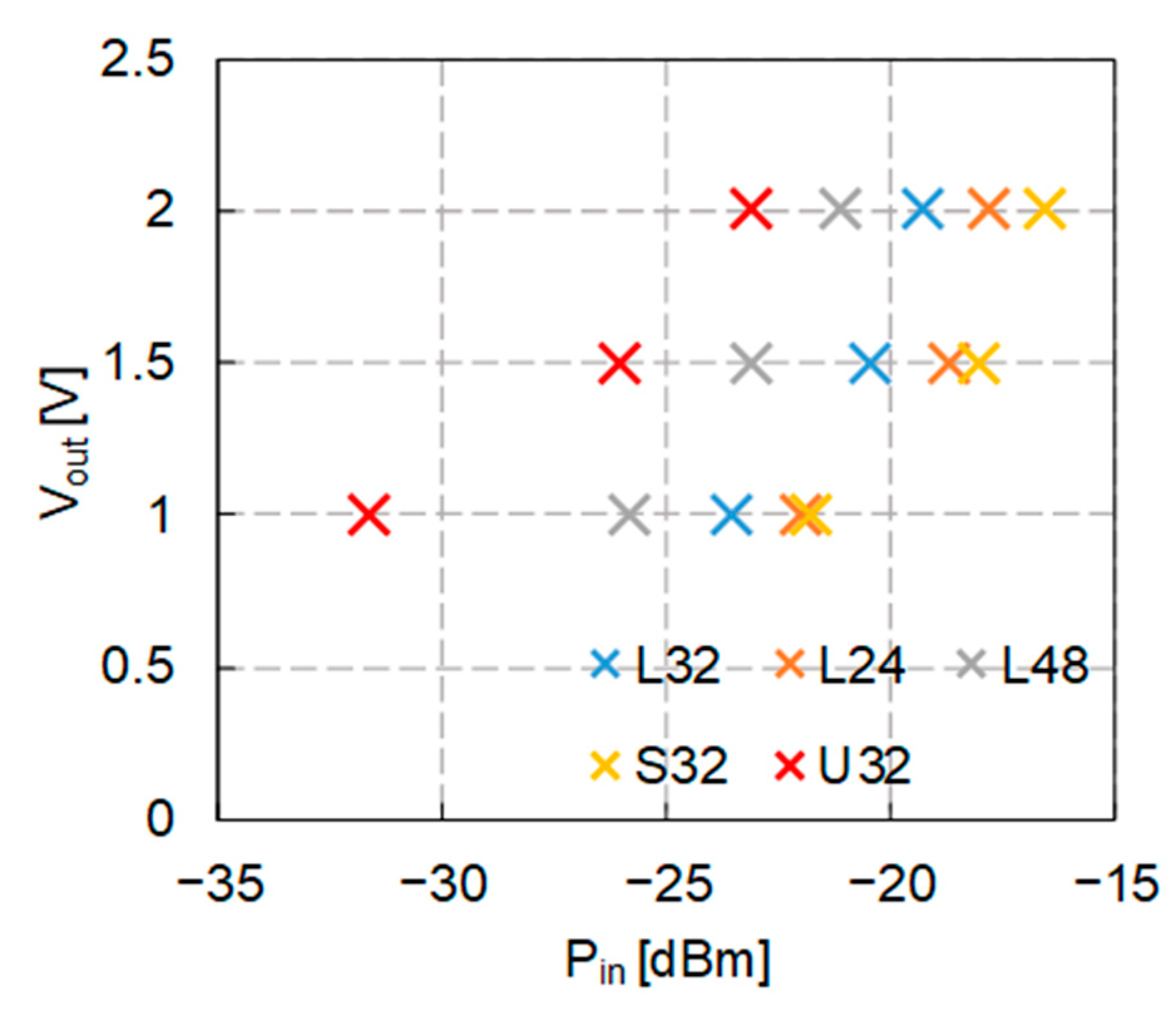

Section 4 presents fabricated circuits and measurement results.

Section 5 shows the comparison result of previous works with this work from both perspectives of area and input sensitivity.

Section 6 summarizes this research.