Constant-Voltage and Constant-Current Controls of the Inductive Power Transfer System for Electric Vehicles Based on Full-Bridge Synchronous Rectification

Abstract

:1. Introduction

- (1)

- Compared to the SS topology, the DLCC topology incorporates LC links, enhancing parameter design flexibility and potential output power. The proposed method facilitates the transition from CC to CV output while stabilizing the output voltage. By substituting four diodes of the rectifier bridge with MOSFETs, the circuit adopts a symmetrical topology, enabling bidirectional energy flow with proper control.

- (2)

- In the method presented herein, switch conduction time is regulated to effectuate the transition from CC to CV output. Additionally, a synchronous signal sampling circuit is introduced to achieve Zero-Voltage Switching (ZVS) conditions in the rectifier bridge, thereby controlling switch conduction sequence. Building upon the conduction time sequence, an output voltage regulation model is derived. A Proportional-Integral-Derivative (PID) control algorithm is employed for CV regulation.

- (3)

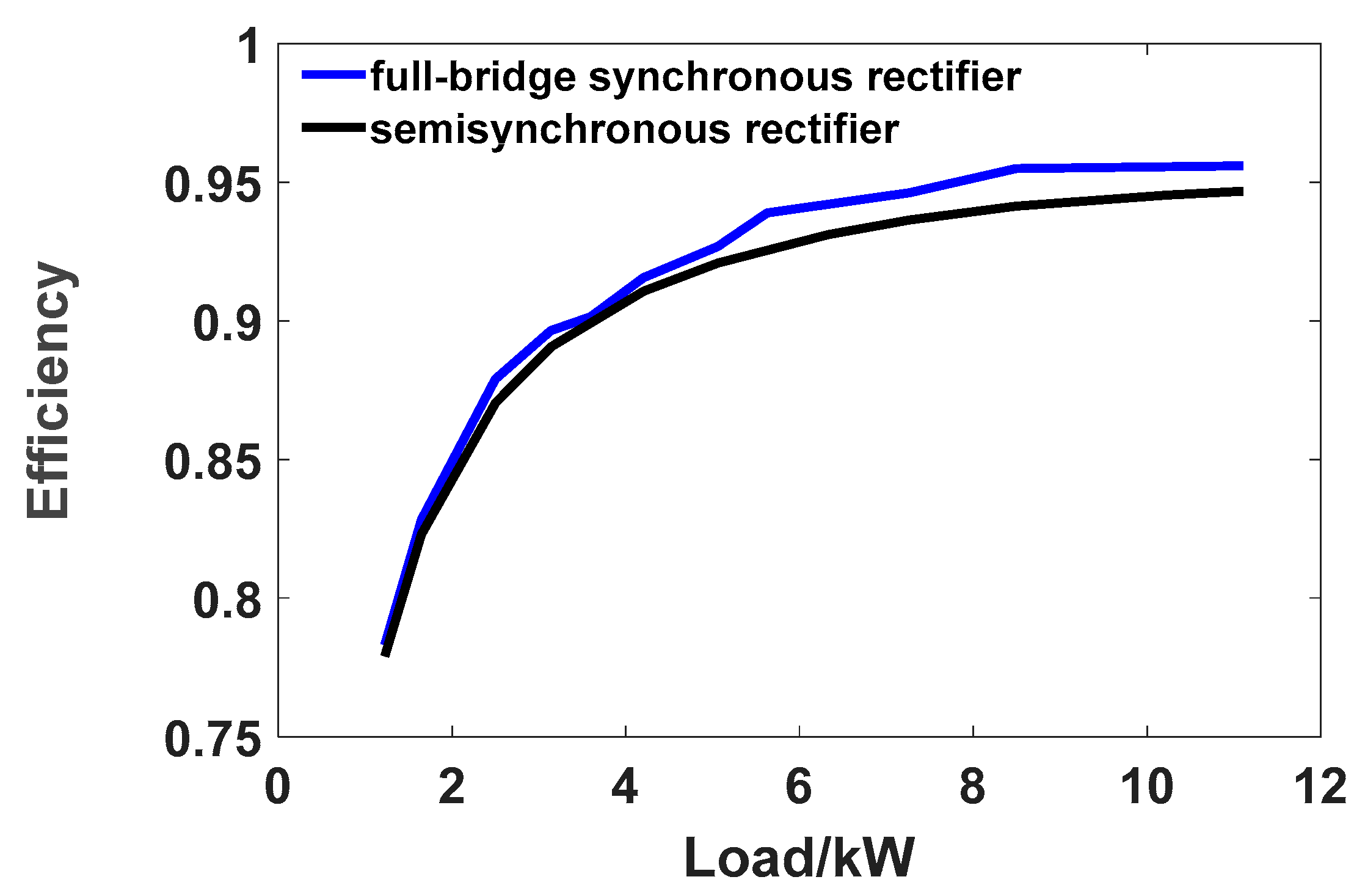

- A simulation model and an 11 kW prototype were constructed to validate the proposed design methodology. Results demonstrate that the proposed control method successfully transitions from CC to CV output while maintaining output voltage stability within certain deviations. Moreover, the efficiency of the proposed method surpasses that of the semi-synchronous rectifier.

2. Circuit Topological Structure and Theoretical Analysis

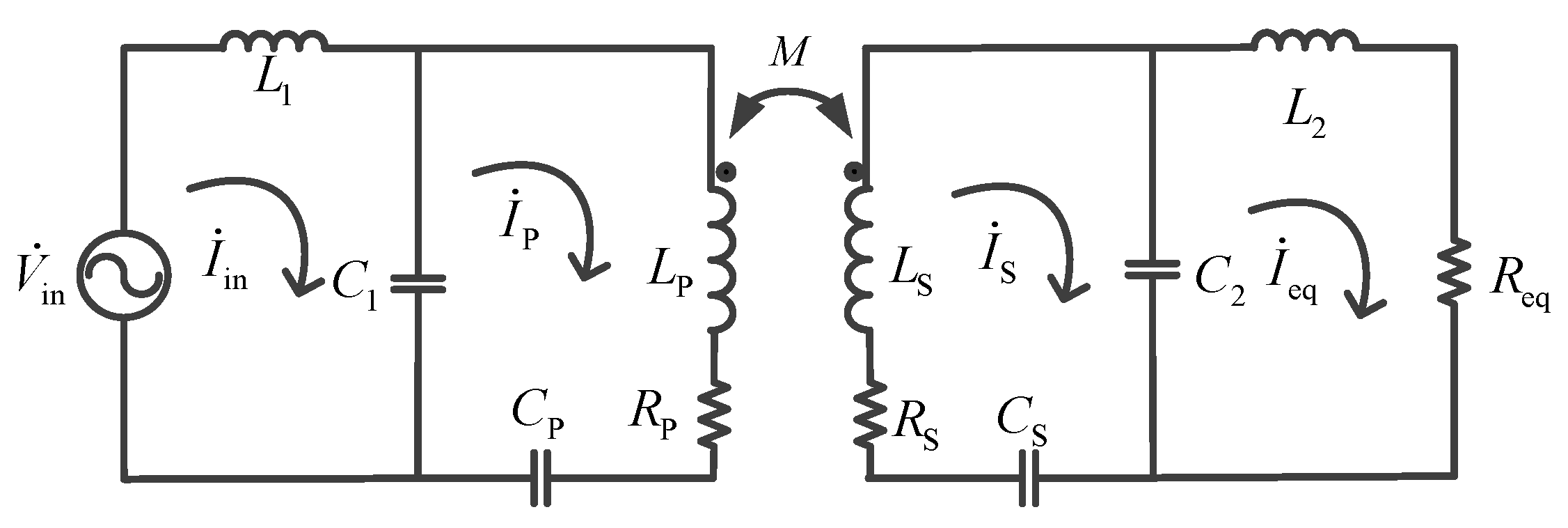

2.1. Circuit Topological Structure Analysis

2.2. Analysis of Input and Output Characteristics

3. The CVCC Control Method Based on Full-Bridge Synchronous Rectification

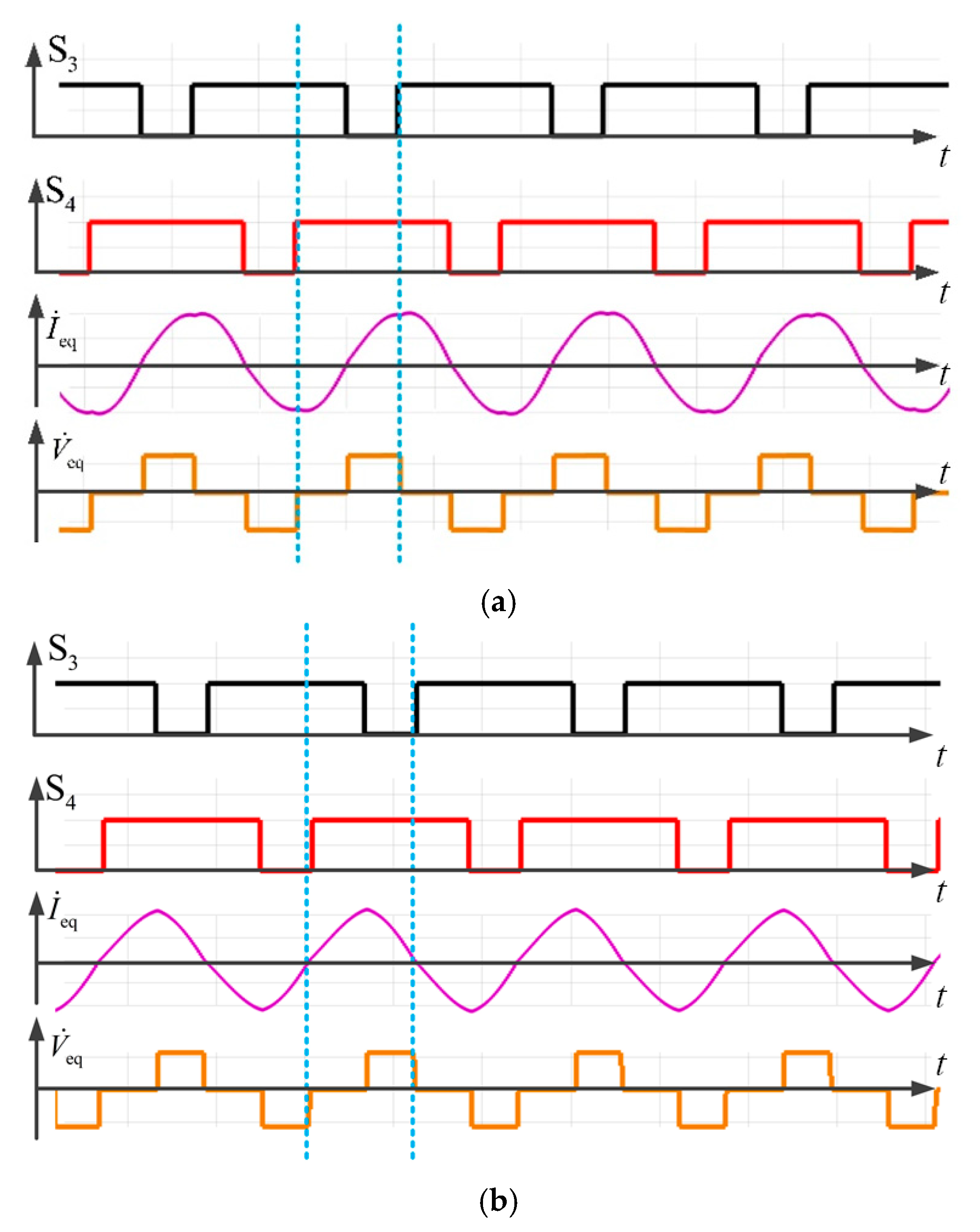

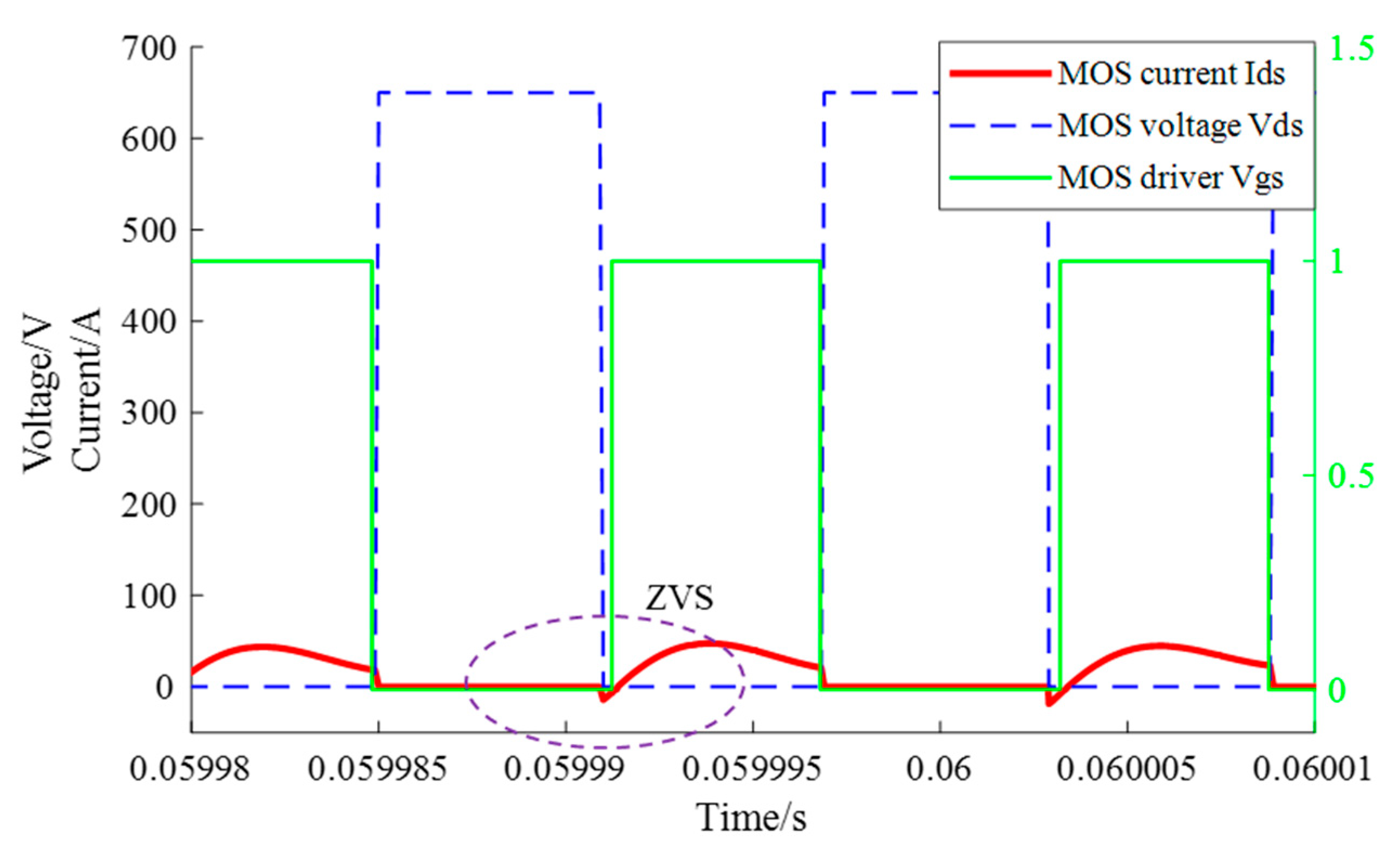

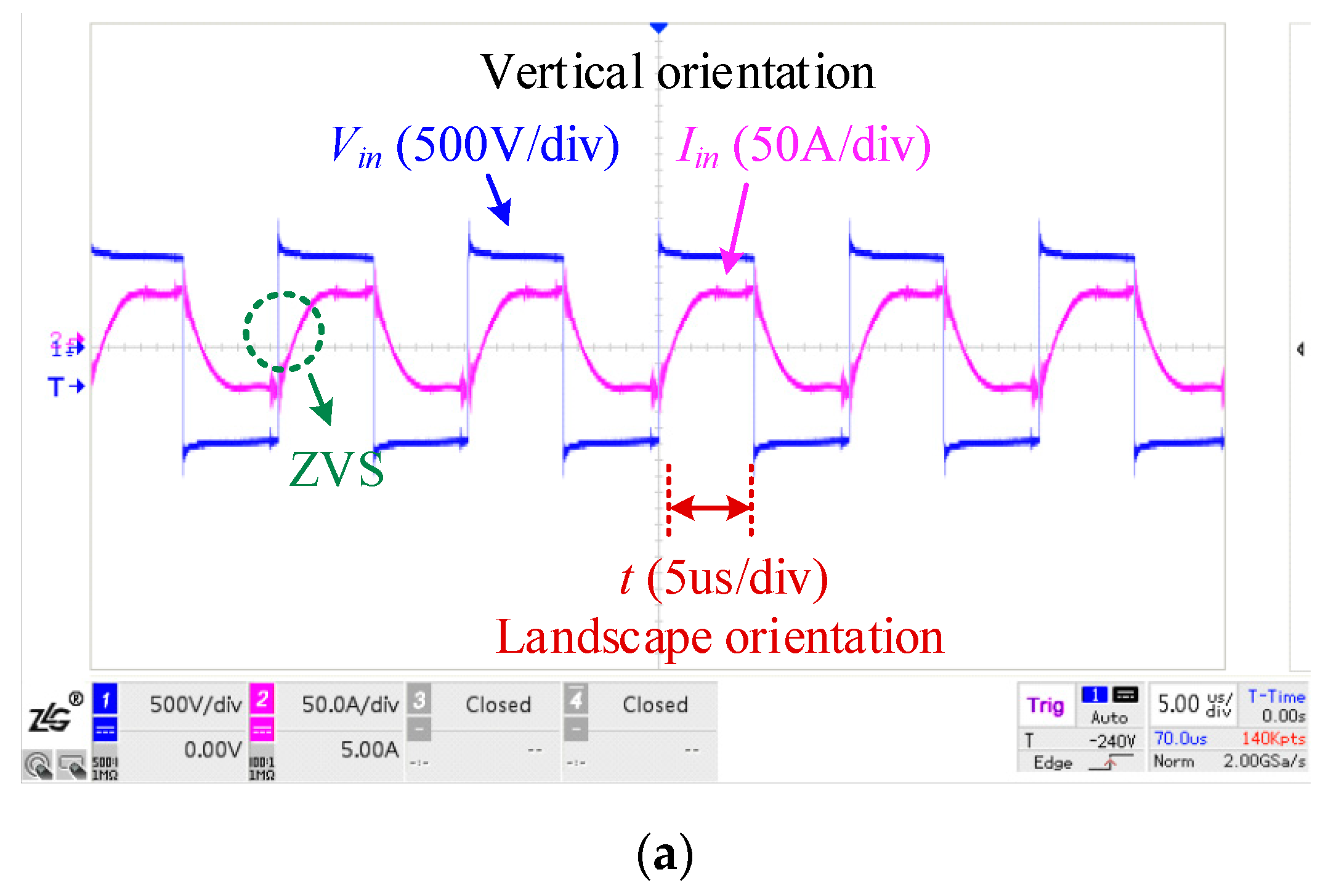

3.1. The Condition with ZVS

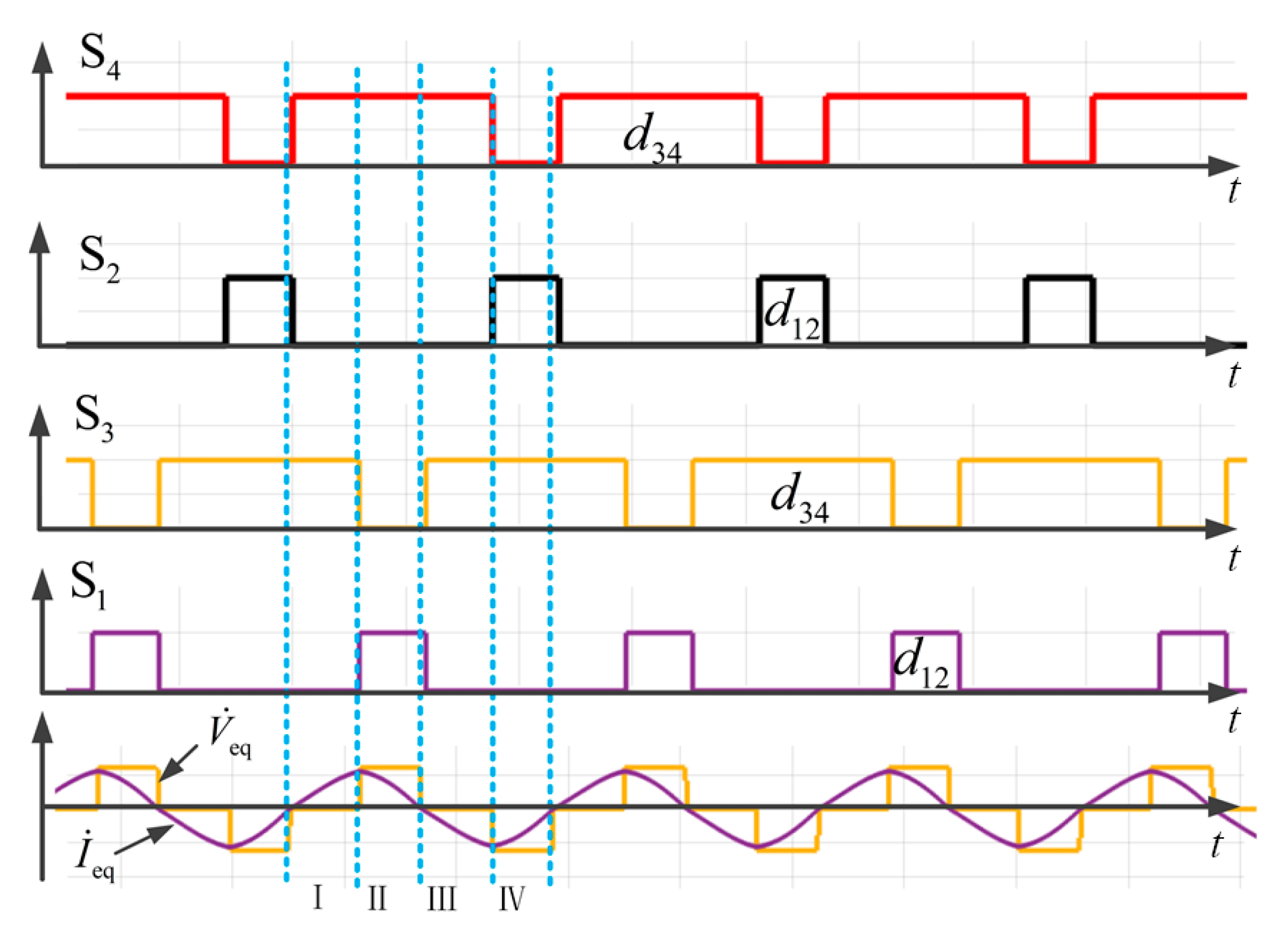

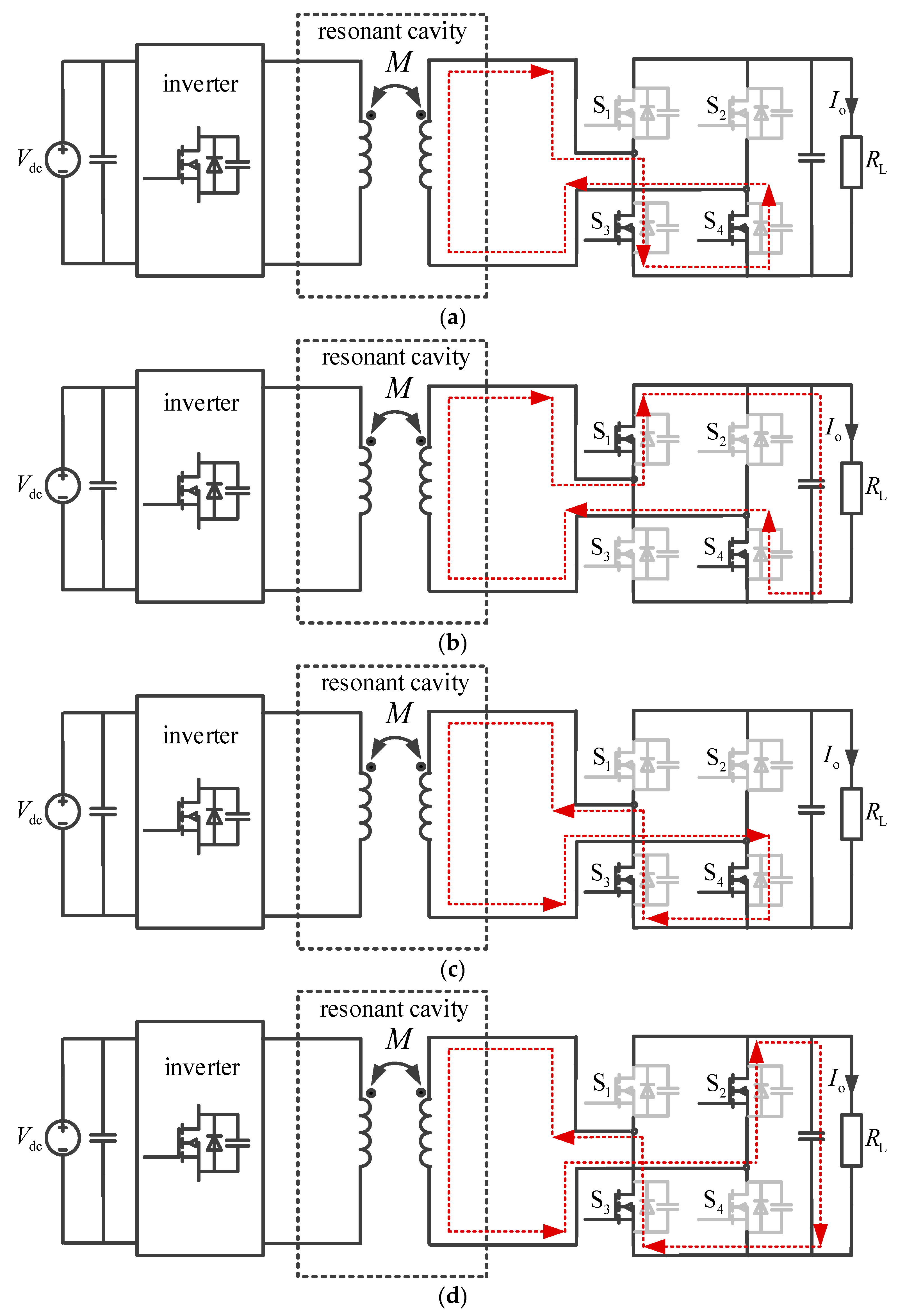

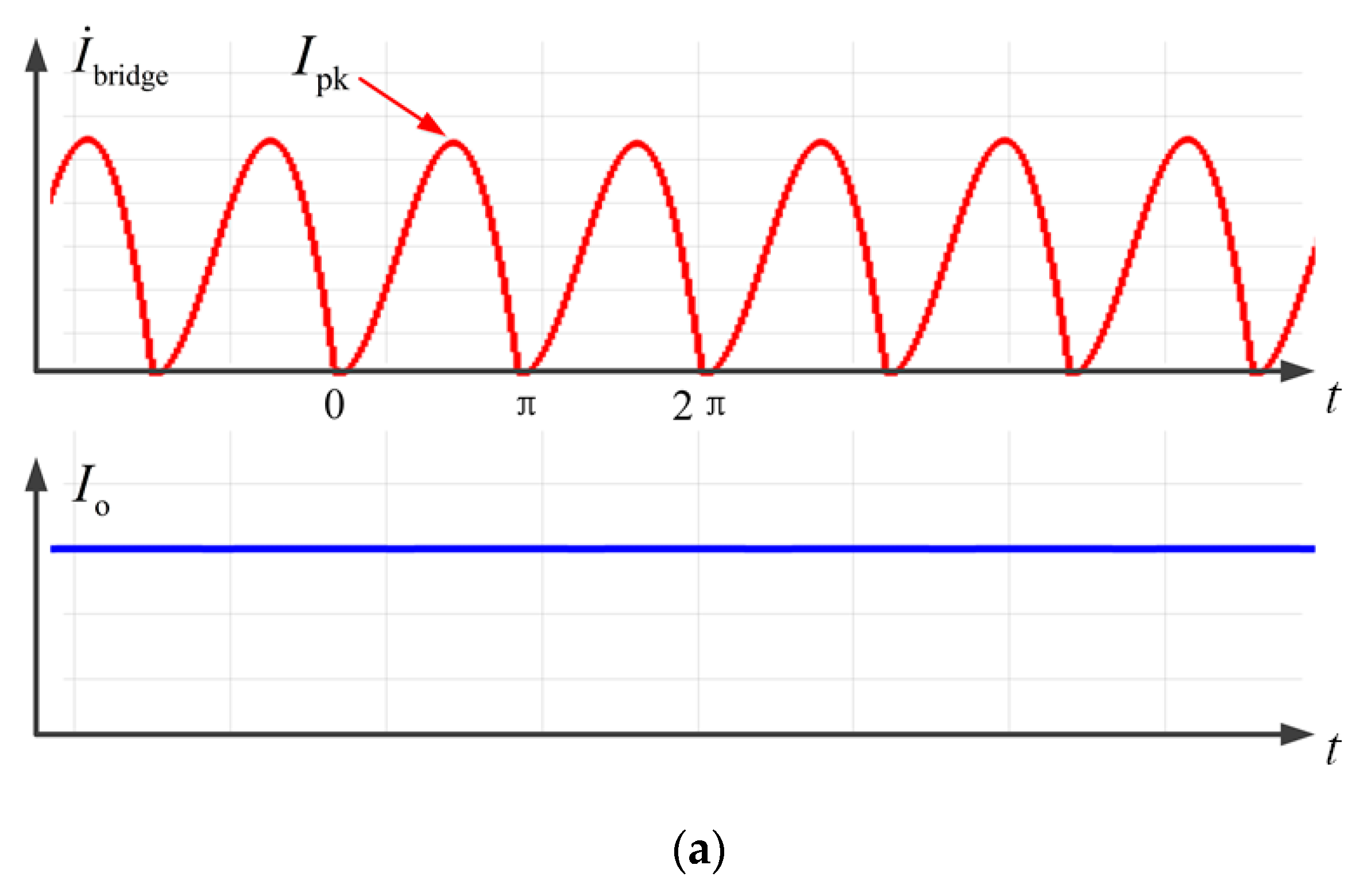

3.2. Operating Mode Analysis

3.3. Output Voltage Regulation Model

4. Compensation Network Design Development of the Synchronous Rectifier

4.1. Controllable Rectifier Design

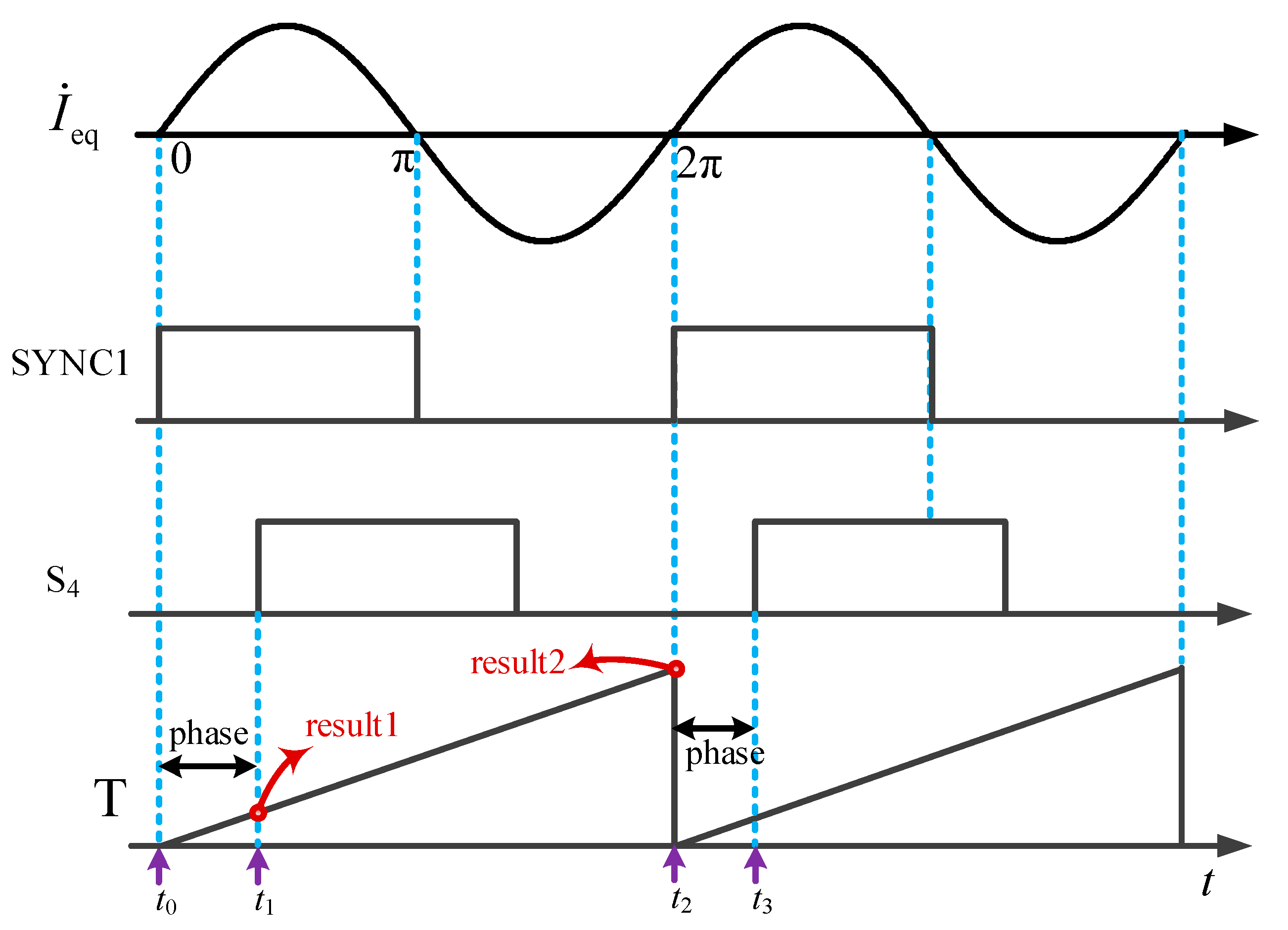

4.2. Implementation of Phase-Locked Loop

5. Simulation and Experimental Validation

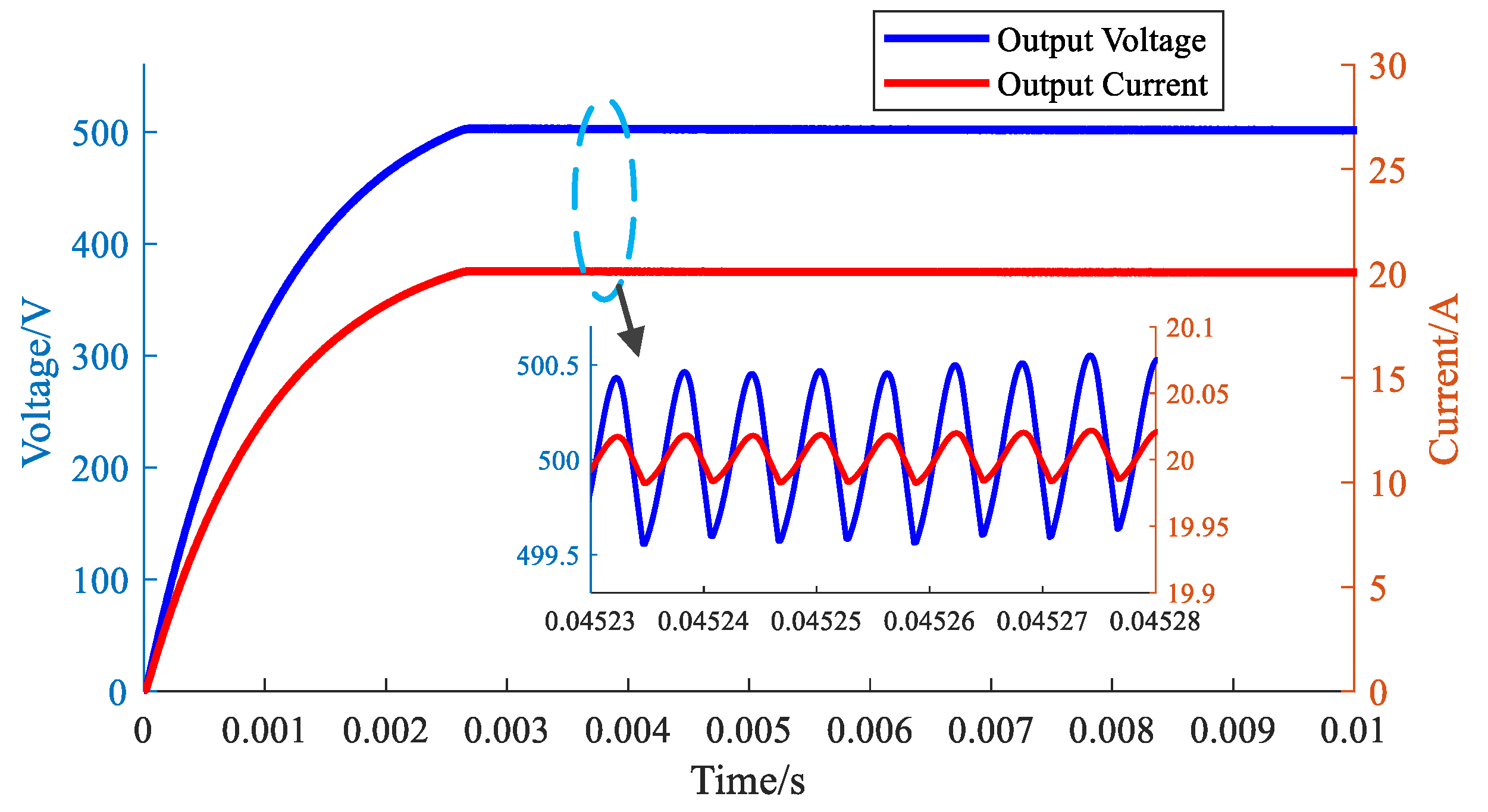

5.1. Simulation Analysis of the Soft Startup Process

5.2. Simulation Analysis of Dynamic Characteristics

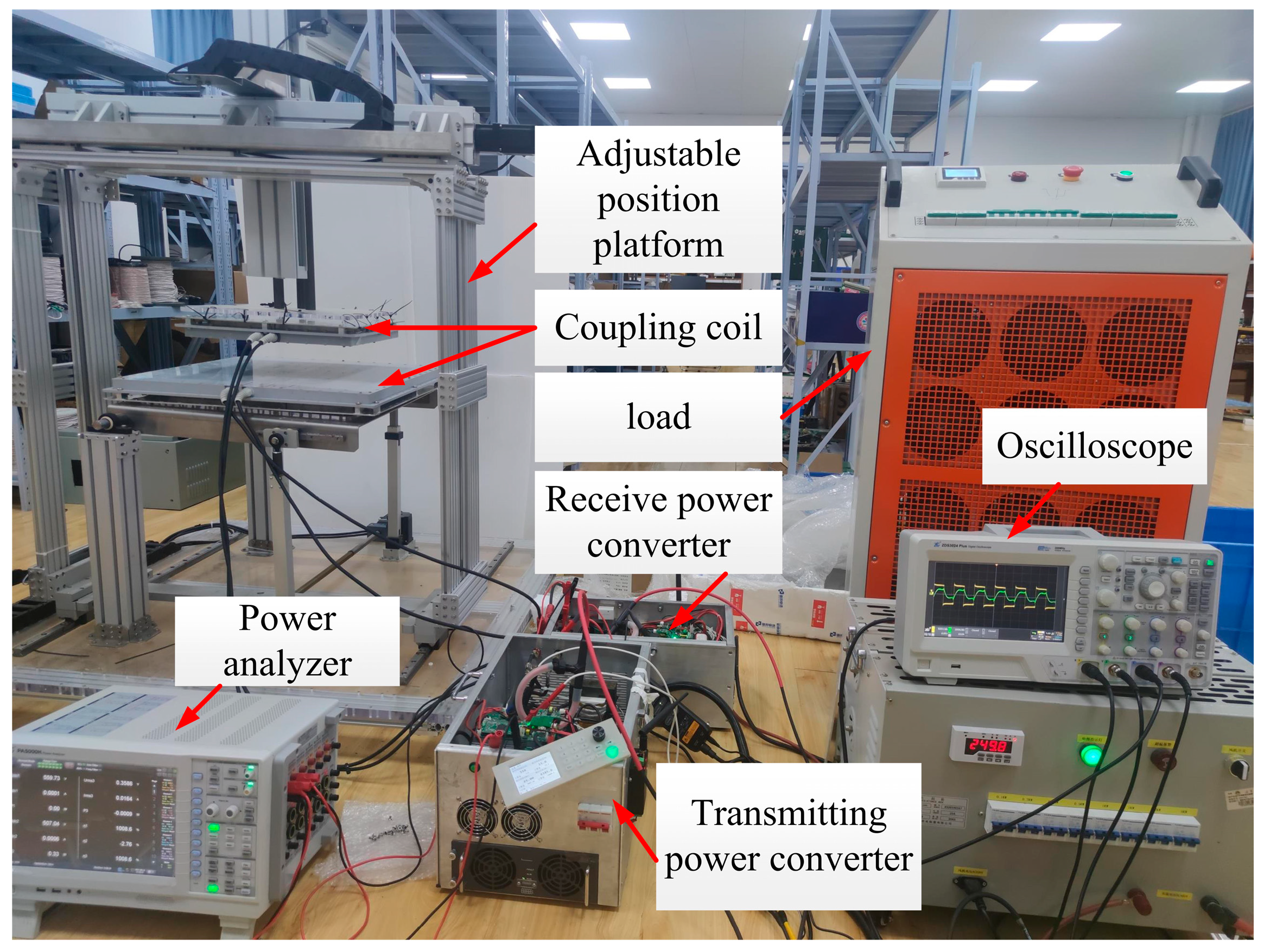

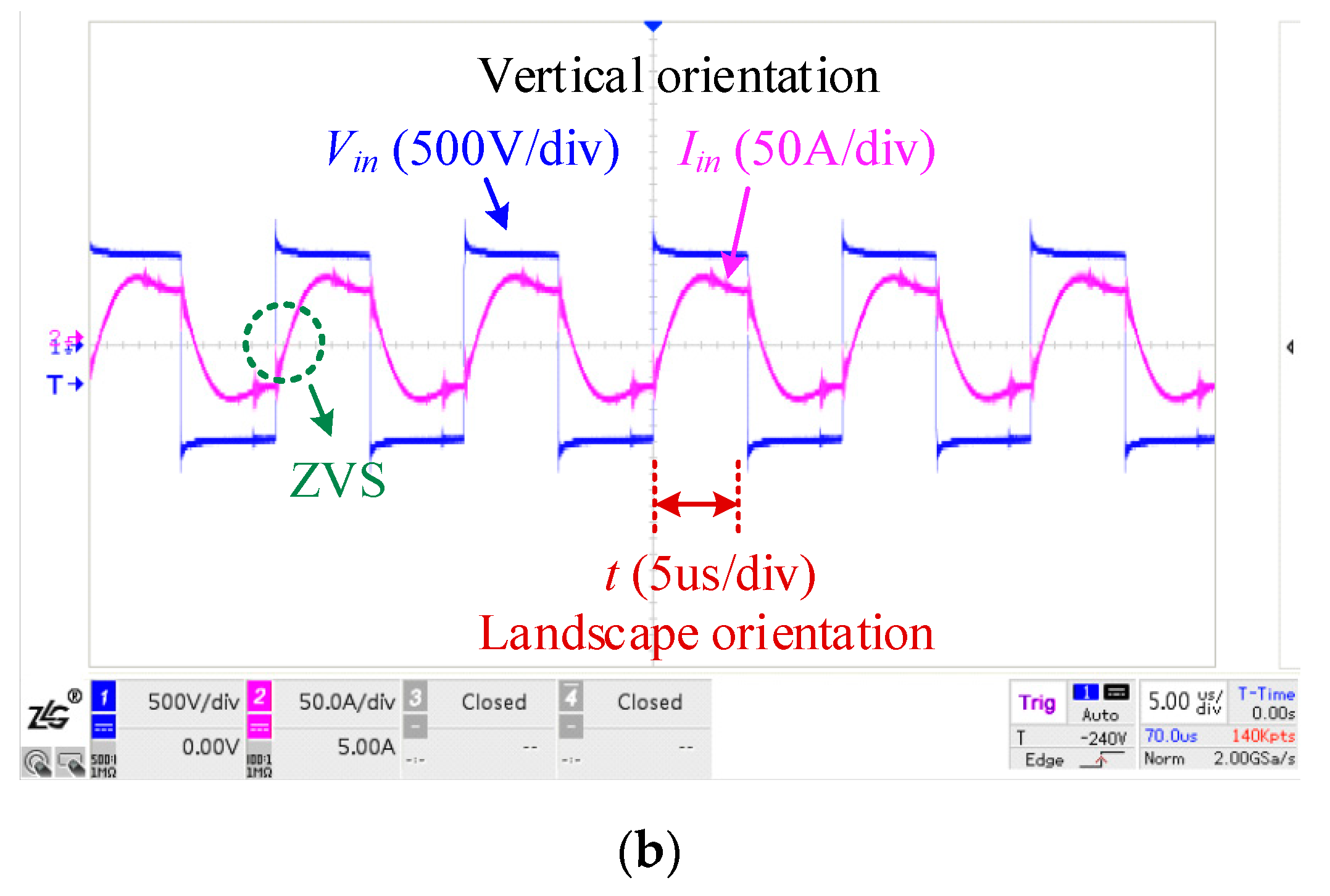

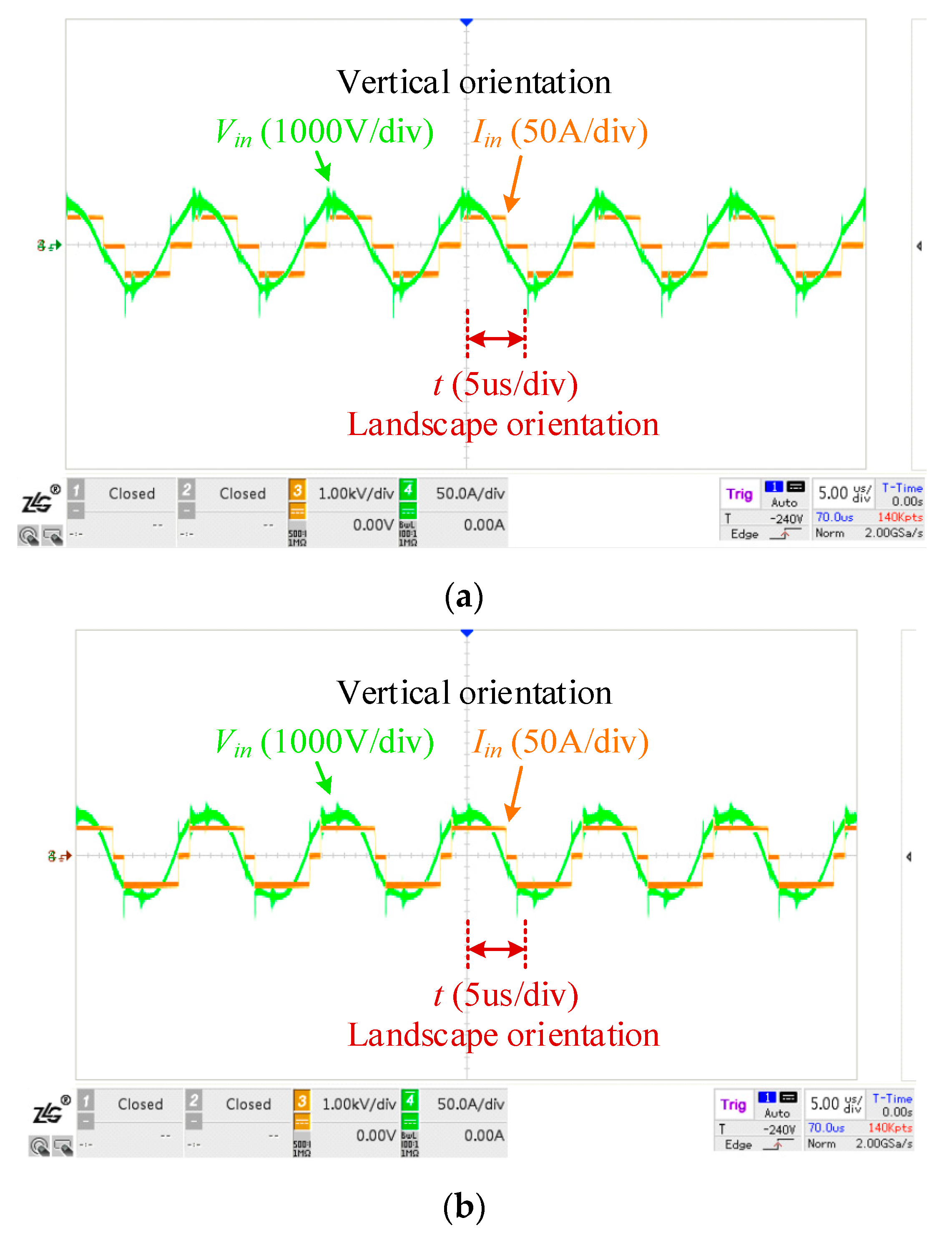

5.3. Analysis of Experimental Results

6. Discussion

7. Conclusions

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

References

- Mansouri, A.; El Magri, A.; Lajouad, R.; Giri, F. Control design and multimode power management of WECS connected to HVDC transmission line through a Vienna rectifier. Int. J. Electr. Power-Energy Syst. 2024, 155, 109563. [Google Scholar] [CrossRef]

- Mansouri, A.; El Magri, A.; Lajouad, R.; Myasse, I.E.; Younes, E.K.; Giri, F. Wind energy based conversion topologies and maximum power point tracking: A comprehensive review and analysis. e-Prime-Adv. Electri. Eng. Electron. Energy 2023, 6, 100351. [Google Scholar] [CrossRef]

- Xie, R.; Liu, R.; Chen, X.; Mao, X.; Li, X.; Zhang, Y. An Interoperable Wireless Power Transmitter for Unipolar and Bipolar Receiving Coils Based on Three-Switch Dual-Output Inverter. IEEE Trans. Power Electron. 2024, 39, 1985–1989. [Google Scholar] [CrossRef]

- Zhou, W.; Tang, D.; Chen, Z.; Mai, R.; He, Z. Nonisolation Model and Load Virtual-Grounding Design Method for Capacitive Power Transfer System with Asymmetric Four-Plate Coupling Interface. IEEE J. Emerg. Sel. Top. Power Electron. 2024, 12, 208–218. [Google Scholar] [CrossRef]

- Liao, Z.-J.; Wu, F.; Jiang, C.-H.; Chen, Z.-R.; Xia, C.-Y. Analysis and Design of Ideal Transformer-Like Magnetic Coupling Wireless Power Transfer Systems. IEEE Trans. Power Electron. 2022, 37, 15728–15739. [Google Scholar] [CrossRef]

- Li, S.; Duan, H.; Xia, J.; Xiong, L. Analysis and Case Study of National Economic Evaluation of Expressway Dynamic Wireless Charging. Energies 2022, 15, 6924. [Google Scholar] [CrossRef]

- Chen, Y.; Zhang, Z.; Yang, B.; Zhang, B.; Fu, L.; He, Z.; Mai, R. A Clamp Circuit-Based Inductive Power Transfer System with Reconfigurable Rectifier Tolerating Extensive Coupling Variations. IEEE Trans. Power Electron. 2024, 39, 1942–1946. [Google Scholar] [CrossRef]

- Zhou, Y.; Qiu, M.; Wang, Q.; Ma, Z.; Sun, H.; Zhang, X. Research on Double LCC Compensation Network for Multi-Resonant Point Switching in Underwater Wireless Power Transfer System. Electronics 2023, 12, 2798. [Google Scholar] [CrossRef]

- Li, T.; Li, S.; Liu, Z.; Fang, Y.; Xiao, Z.; Shafiq, Z.; Lu, S. Enhancing V2G Applications: Analysis and Optimization of a CC/CV Bidirectional IPT System with Wide Range ZVS. IEEE Trans. Transp. Electrif. 2024, in press. [CrossRef]

- Lu, J.; Zhu, G.; Lin, D.; Zhang, Y.; Mi, C.C. Unified Load-Independent ZPA Analysis and Design in CC and CV Modes of Higher Order Resonant Circuits for WPT Systems. IEEE Trans. Transp. Electrif. 2019, 5, 977–987. [Google Scholar] [CrossRef]

- Lu, J.; Zhu, G.; Lin, D.; Wong, S.; Jiang, J. Load-Independent Voltage and Current Transfer Characteristics of High-Order Resonant Network in IPT System. IEEE J. Emerg. Sel. Top. Power Electron. 2019, 7, 422–436. [Google Scholar] [CrossRef]

- Li, G.; Jo, C.-H.; Shin, C.-S.; Jo, S.; Kim, D.-H. A Load-Independent Current/Voltage IPT Charger with Secondary Side-Controlled Hybrid-Compensated Topology for Electric Vehicles. Appl. Sci. 2022, 12, 10899. [Google Scholar] [CrossRef]

- Yang, L.; Geng, Z.; Jiang, S.; Wang, C. Analysis and Design of an S/PS−Compensated WPT System with Constant Current and Constant Voltage Charging. Electronics 2022, 11, 1488. [Google Scholar] [CrossRef]

- Vu, V.-B.; Tran, D.-H.; Choi, W. Implementation of the Constant Current and Constant Voltage Charge of Inductive Power Transfer Systems with the Double-Sided LCC Compensation Topology for Electric Vehicle Battery Charge Applications. IEEE Trans. Power Electron. 2018, 33, 7398–7410. [Google Scholar] [CrossRef]

- Rong, C.; Duan, X.; Chen, M.; Wang, Q.; Yan, L.; Wang, H.; Xia, C.; He, X.; Zeng, Y.; Liao, Z. Critical Review of Recent Development of Wireless Power Transfer Technology for Unmanned Aerial Vehicles. IEEE Access 2023, 11, 132982–133003. [Google Scholar] [CrossRef]

- Zhou, W.; Gao, Q.; Mai, R.; He, Z.; Hu, P. Design and Analysis of a CPT System with Extendable Pairs of Electric Field Couplers. IEEE Trans. Power Electron. 2022, 37, 7443–7455. [Google Scholar] [CrossRef]

- Xia, J.; Yuan, X.; Lu, S.; Dai, W.; Li, T.; Li, J.; Li, S. A General Parameter Optimization Method for a Capacitive Power Transfer System with an Asymmetrical Structure. Electronics 2022, 11, 922. [Google Scholar] [CrossRef]

- Rong, E.; Sun, P.; Qiao, K.; Zhang, X.; Yang, G.; Wu, X. Six-Plate and Hybrid-Dielectric Capacitive Coupler for Underwater Wireless Power Transfer. IEEE Trans. Power Electron. 2024, 39, 2867–2881. [Google Scholar] [CrossRef]

- Qiao, K.; Rong, E.; Sun, P.; Zhang, X.; Sun, J. Design of LCC-P Constant Current Topology Parameters for AUV Wireless Power Transfer. Energies 2022, 15, 5249. [Google Scholar] [CrossRef]

- Dai, X.; Sun, Y. An accurate frequency tracking method based on short current detection for inductive power transfer system. IEEE Trans. Ind. Electron. 2014, 776–783. [Google Scholar] [CrossRef]

- Xia, C.; Wang, W.; Chen, G.; Wu, X.; Zhou, S.; Sun, Y. Robust Control for the Relay ICPT System Under External Disturbance and Parametric Uncertainty. IEEE Trans. Control. Syst. Technol. 2017, 25, 2168–2175. [Google Scholar] [CrossRef]

- Hu, H.; Cai, T.; Duan, S.; Zhang, X.; Niu, J.; Feng, H. An Optimal Variable Frequency Phase Shift Control Strategy for ZVS Operation Within Wide Power Range in IPT Systems. IEEE Trans. Power Electron. 2020, 35, 5517–5530. [Google Scholar] [CrossRef]

- Huang, Z.; Wong, S.-C.; Tse, C.K. Comparison of Basic Inductive Power Transfer Systems with Linear Control Achieving Optimized Efficiency. IEEE Trans. Power Electron. 2020, 35, 3276–3286. [Google Scholar] [CrossRef]

- Dai, X.; Li, X.; Li, Y.; Hu, A.P. Maximum Efficiency Tracking for Wireless Power Transfer Systems with Dynamic Coupling Coefficient Estimation. IEEE Trans. Power Electron. 2018, 33, 5005–5015. [Google Scholar] [CrossRef]

- Boys, J.T.; Covic, G.A. The inductive power transfer story at the University of Auckland. IEEE Circuits Syst. Mag. 2015, 15, 6–27. [Google Scholar] [CrossRef]

- Zhang, H.; Chen, Y.; Kim, D.H.; Li, Z.; Zhang, M.; Li, G. Variable Inductor Control for Misalignment Tolerance and Constant Current/Voltage Charging in Inductive Power Transfer System. IEEE J. Emerg. Sel. Top. Power Electron. 2023, 11, 4563–4573. [Google Scholar] [CrossRef]

- Zhong, W.; Hui, S.Y.R. Charging Time Control of Wireless Power Transfer Systems Without Using Mutual Coupling Information and Wireless Communication System. IEEE Trans. Ind. Electron. 2017, 64, 228–235. [Google Scholar] [CrossRef]

- Pang, B.; Deng, J.; Liu, P.; Wang, Z. Secondary-side power control method for double-side LCC compensation topology in wireless EV charger application. In Proceedings of the IECON 2017—43rd Annual Conference of the IEEE Industrial Electronics Society, Beijing, China, 29 October–1 November 2017. [Google Scholar] [CrossRef]

- Huang, C.-Y.; Boys, J.T.; Covic, G.A.; Ren, S. LCL pick-up circulating current controller for inductive power transfer systems. In Proceedings of the 2010 IEEE Energy Conversion Congress and Exposition, Atlanta, GA, USA, 12 September 2010; pp. 640–646. [Google Scholar] [CrossRef]

- Li, S.; Li, W.; Deng, J.; Nguyen, T.D.; Mi, C.C. A Double-Sided LCC Compensation Network and Its Tuning Method for Wireless Power Transfer. IEEE Trans. Veh. Technol 2015, 64, 2261–2273. [Google Scholar] [CrossRef]

| Parameter | Value |

|---|---|

| DC input voltage (V) | 560 |

| Rated load (kW) | 11 |

| Zero-offset coupling coefficient | 0.19 |

| Transmitting coil’s self-induction LP (μH) | 116.40 |

| Compensation capacitor at the primary side CP (nF) | 44.45 |

| Compensating inductance at the primary side L1 (μH) | 37.17 |

| Compensation capacitor at the primary side C1 (nF) | 94.41 |

| Operating frequency (kHz) | 85 |

| Operating distance (mm) | 100 |

| Resistance range (Ω) | 25–100 |

| Receiving coil’s self-induction LS (μH) | 172.98 |

| Compensation capacitor at the secondary side CS (nF) | 24.80 |

| Compensating inductance at the secondary side L2 (μH) | 25.78 |

| Compensation capacitor at the secondary side C2 (nF) | 136.00 |

| Dimensions of the transmitting coil (mm) | 580 × 580 × 32 |

| Dimensions of the receiving coil (mm) | 360 × 360 × 32 |

| The plane offset distance of receiving and transmitting coil (mm) | 0–100 |

| Ref. | Topology | Power | Efficiency |

|---|---|---|---|

| [10] | LCC-S + Uncontrolled rectifier | 3.3 kW | 89.2% |

| [11] | DLCC + Uncontrolled rectifier | 3.3 kW | 92.9% |

| [12] | LCC-S + DLCC + Uncontrolled rectifier | 0.12 kW | 92.2% |

| [26] | LCC-S + Uncontrolled rectifier + Boost Converter | 0.5 kW | 92.9% |

| [29] | DLCC + Semi-synchronous rectifier | 2.5 kW | 88% |

| This work | DLCC + Controllable synchronous rectifier | 11 kW | 95.6% |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2024 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Cai, J.; Sun, P.; Ji, K.; Wu, X.; Ji, H.; Wang, Y.; Rong, E. Constant-Voltage and Constant-Current Controls of the Inductive Power Transfer System for Electric Vehicles Based on Full-Bridge Synchronous Rectification. Electronics 2024, 13, 1686. https://doi.org/10.3390/electronics13091686

Cai J, Sun P, Ji K, Wu X, Ji H, Wang Y, Rong E. Constant-Voltage and Constant-Current Controls of the Inductive Power Transfer System for Electric Vehicles Based on Full-Bridge Synchronous Rectification. Electronics. 2024; 13(9):1686. https://doi.org/10.3390/electronics13091686

Chicago/Turabian StyleCai, Jin, Pan Sun, Kai Ji, Xusheng Wu, Hang Ji, Yuxiao Wang, and Enguo Rong. 2024. "Constant-Voltage and Constant-Current Controls of the Inductive Power Transfer System for Electric Vehicles Based on Full-Bridge Synchronous Rectification" Electronics 13, no. 9: 1686. https://doi.org/10.3390/electronics13091686