Transformerless Quasi-Z-Source Inverter to Reduce Leakage Current for Single-Phase Grid-Tied Applications

Abstract

:1. Introduction

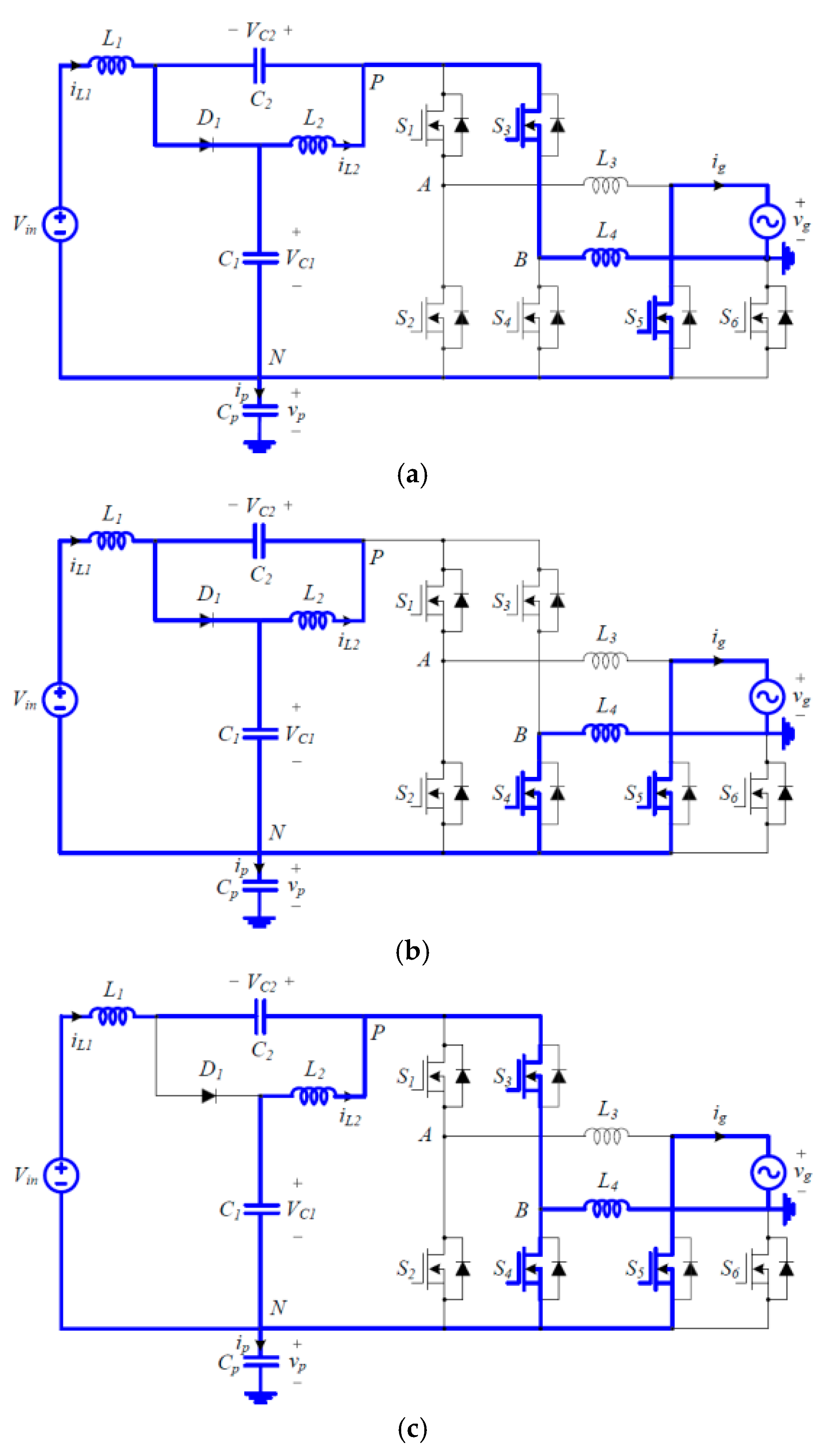

2. Proposed Inverter

2.1. Operation Principle

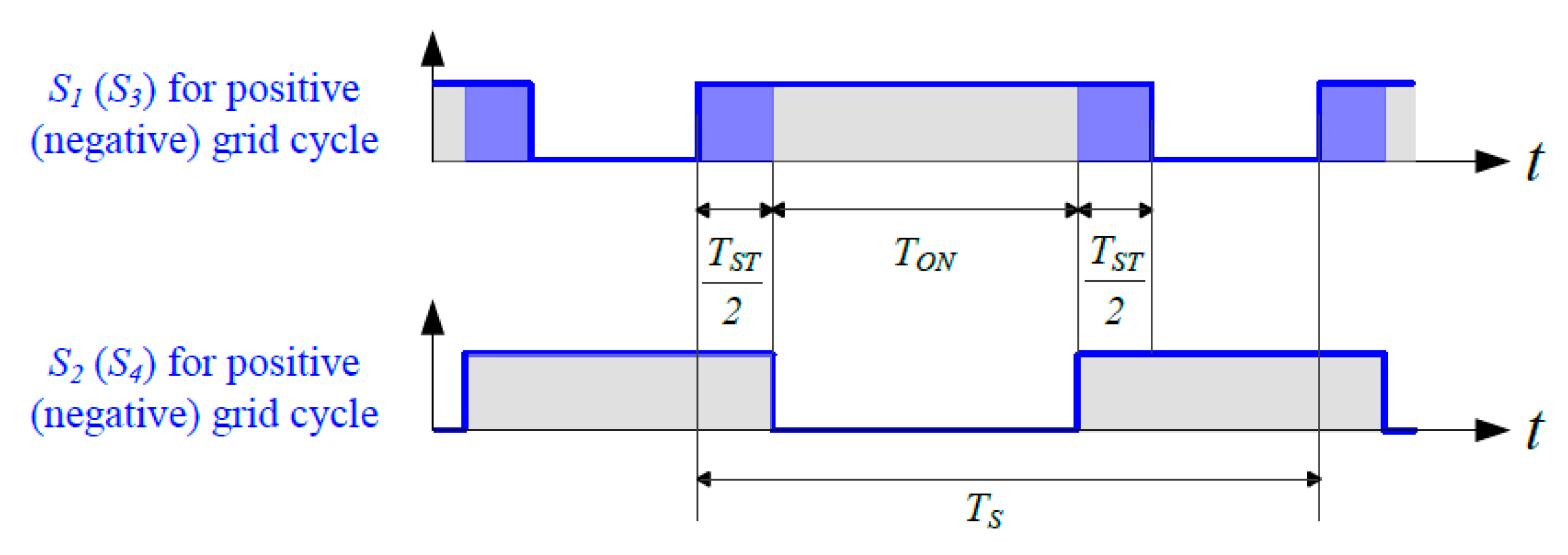

2.2. Control Strategy

3. Experimental Results

4. Discussion

4.1. Power Loss Comparison

4.2. Topological Investigation

5. Conclusions

Author Contributions

Funding

Conflicts of Interest

References

- Anderson, J.; Peng, F.Z. A class of quasi-Z-source inverters. In Proceedings of the IEEE Industry Applications Society Annual Meeting, Edmonton, AB, Canada, 5–9 October 2008; pp. 1–7. [Google Scholar]

- Zhou, Y.; Li, H.; Li, H. A single-phase PV quasi-Z-source inverter with reduced capacitance using modified modulation and double-frequency ripple suppression control. IEEE Trans. Power Electron. 2016, 31, 2166–2173. [Google Scholar] [CrossRef]

- Gu, Y.; Chen, Y.; Zhang, B. Enhanced-boost quasi-Z-source inverter with an active switched Z-network. IEEE Trans. Ind. Electron. 2018, 65, 8372–8381. [Google Scholar] [CrossRef]

- Komurcugil, H.; Bayhan, S.; Bagheri, F.; Kukrer, S.; Abu-Rub, H. Model-based current control for single-phase grid-tied quasi-Z-source inverters with virtual time constant. IEEE Trans. Ind. Electron. 2018, 65, 8277–8286. [Google Scholar] [CrossRef]

- Xiao, H.; Xie, S. Leakage current analytical model and application in single-phase transformerless photovoltaic grid-connected inverter. IEEE Trans. Electromagn. Compat. 2010, 52, 902–913. [Google Scholar] [CrossRef]

- Bozorgi, A.M.; Hakemi, A.; Farasat, M.; Monfared, M. Modulation techniques for common-mode voltage reduction in the Z-source ultra-sparse matrix converters. IEEE Trans. Power Electron. 2019, 34, 958–970. [Google Scholar] [CrossRef]

- Noroozi, N.; Zolghadri, M.R. Three-phase quasi-Z-source inverter with constant common-mode voltage for photovoltaic application. IEEE Trans. Ind. Electron. 2018, 65, 4790–4798. [Google Scholar] [CrossRef]

- Mohan, N. Power Electronics: A First Course; John Wiley & Sons: Hoboken, NJ, USA, 2012; pp. 1–270. [Google Scholar]

- Li, W.; Ge, Y.; Luo, H.; Cui, W.; He, X.; Xia, C. Topology review and derivation methodology of single-phase transformerless photovoltaic inverters for leakage current suppression. IEEE Trans. Ind. Electron. 2015, 62, 4537–4551. [Google Scholar] [CrossRef]

- Saridakis, S.; Koutroulis, E.; Blaabjerg, F. Optimization of SiC-based H5 and conergy-NPC transformerless PV inverters. IEEE J. Emerg. Sel. Top. Power Electron. 2015, 3, 555–567. [Google Scholar] [CrossRef]

- Kerekes, T.; Teodorescu, R.; Rodriguez, P.; Vazquez, G.; Aldabas, E. A new high-efficiency single-phase transformerless PV inverter topology. IEEE Trans. Ind. Electron. 2011, 58, 184–191. [Google Scholar] [CrossRef]

- Gonzalez, R.; Lopez, J.; Sanchis, P.; Marroyo, L. Transformerless inverter for single-phase photovoltaic systems. IEEE Trans. Power Electron. 2007, 22, 693–697. [Google Scholar] [CrossRef]

- Li, K.; Shen, Y.; Yang, Y.; Qin, Z.; Blaabjerg, F. A transformerless single-phase symmetrical Z-source HERIC inverter with reduced leakage currents for PV systems. In Proceedings of the IEEE Applied Power Electronics Conference and Exposition (APEC), San Antonio, TX, USA, 4–8 March 2018; pp. 356–361. [Google Scholar]

- Meraj, M.; Iqbal, A.; Brahim, L.; Alammari, R.; Abu-Rub, H. A high efficiency and high reliability single-phase modified quasi Z-source inverter for non-isolated grid connected applications. In Proceedings of the IEEE IECON, Yokohama, Japan, 9–12 November 2015; pp. 4305–4310. [Google Scholar]

- Meraj, M.; Rahman, S.; Iqbal, A.; Ben-Brahim, L. Common mode voltage reduction in a single-phase quasi Z-source inverter for transformerless grid-connected solar PV applications. IEEE J. Emerg. Sel. Top. Power Electron. 2018. [Google Scholar] [CrossRef]

- Guo, X. A novel CH5 inverter for single-phase transformerless photovoltaic system applications. IEEE Trans. Circ. Syst. Ii Express Briefs 2017, 64, 1197–1201. [Google Scholar] [CrossRef]

- Zhang, J.; Ding, H.; Wang, B.; Guo, X.; Padmanaban, S. Active power decoupling for current source converters: An overview scenario. Electronics 2019, 8, 197. [Google Scholar] [CrossRef]

- Peng, F.Z. Z-source inverter. IEEE Trans. Ind. Appl. 2003, 39, 504–510. [Google Scholar] [CrossRef]

- Ellabban, O.; Mierlo, J.V.; Lataire, P. A DSP-based dual-loop peak dc-link voltage control strategy of the Z-source inverter. IEEE Trans. Power Electron. 2012, 27, 4088–4097. [Google Scholar] [CrossRef]

- Golestan, S.; Monfared, M.; Freijedo, F.D.; Guerrero, J.M. Design and tuning of a modified power-based PLL for single-phase grid-connected power conditioning systems. IEEE Trans. Power Electron. 2012, 27, 3639–3650. [Google Scholar] [CrossRef]

- Guo, X.; Yang, Y.; Zhu, T. ESI: A novel three-phase inverter with leakage current attenuation for transformerless PV systems. IEEE Trans. Ind. Electron. 2018, 65, 2967–2974. [Google Scholar] [CrossRef]

- Guo, X.; Zhang, X.; Guan, H.; Kerekes, T.; Blaabjerg, F. Three-phase ZVR topology and modulation strategy for transformerless PV system. IEEE Trans. Power Electron. 2019, 34, 1017–1021. [Google Scholar] [CrossRef]

- Guo, X.; Jia, X. Hardware-based cascaded topology and modulation strategy with leakage current reduction for transformerless PV systems. IEEE Trans. Ind. Electron. 2016, 63, 7823–7832. [Google Scholar] [CrossRef]

- Ge, B.; Liu, Y.; Abu-Rub, H.; Peng, F.Z. State-of-charge balancing control for a battery-energy-stored quasi-Z-source cascaded-multilevel-inverter-base photovoltaic power system. IEEE Trans. Ind. Electron. 2018, 65, 2268–2279. [Google Scholar] [CrossRef]

- Sun, D.; Ge, B.; Liang, W.; Abu-Rub, H.; Peng, F.Z. An energy stored quasi-Z-source cascade multilevel inverter-based photovoltaic power generation system. IEEE Trans. Ind. Electron. 2015, 62, 5458–5467. [Google Scholar] [CrossRef]

© 2019 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Choi, W.-Y.; Yang, M.-K. Transformerless Quasi-Z-Source Inverter to Reduce Leakage Current for Single-Phase Grid-Tied Applications. Electronics 2019, 8, 312. https://doi.org/10.3390/electronics8030312

Choi W-Y, Yang M-K. Transformerless Quasi-Z-Source Inverter to Reduce Leakage Current for Single-Phase Grid-Tied Applications. Electronics. 2019; 8(3):312. https://doi.org/10.3390/electronics8030312

Chicago/Turabian StyleChoi, Woo-Young, and Min-Kwon Yang. 2019. "Transformerless Quasi-Z-Source Inverter to Reduce Leakage Current for Single-Phase Grid-Tied Applications" Electronics 8, no. 3: 312. https://doi.org/10.3390/electronics8030312