A Fault Tolerant Voter for Approximate Triple Modular Redundancy

Abstract

:1. Introduction

- We highlight the reliability of ATMR, in contrast with TMR.

- A compact, low-power, high-speed, and fault-tolerant voter for ATMR is designed.

- A new metric, Quality of Circuit (QoC), is proposed. It holds immense significance to have prior insight of a circuit’s intrinsic aptitude towards assurance of fault free output for certain input vectors. Hence, we present a metric that acknowledges the inherent capability of a digital circuit to mask all possible internal faults for a given input vector.

- We present a transistor-level analysis of fault-tolerant voters, considering all possible states of the voter inputs and evaluate them through a comparison with the proposed voter.

2. Motivation

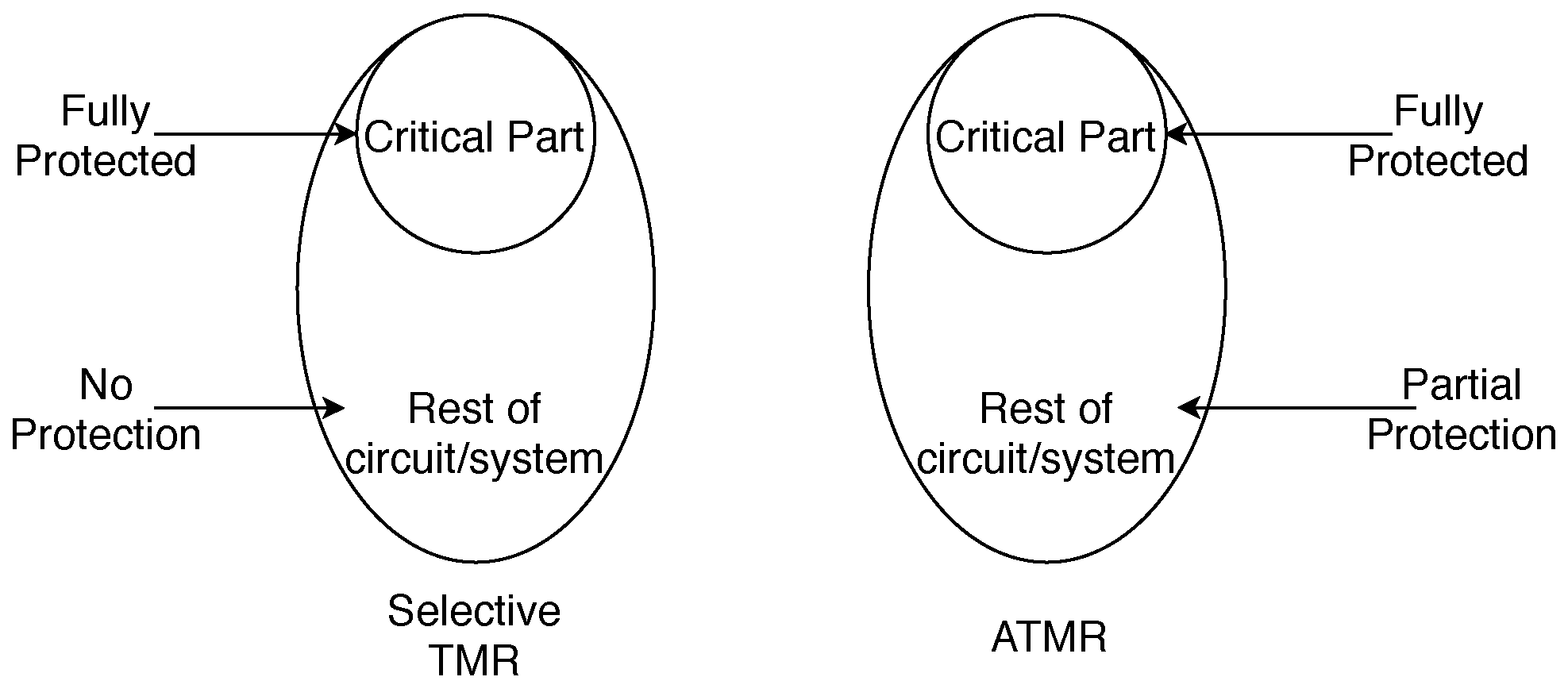

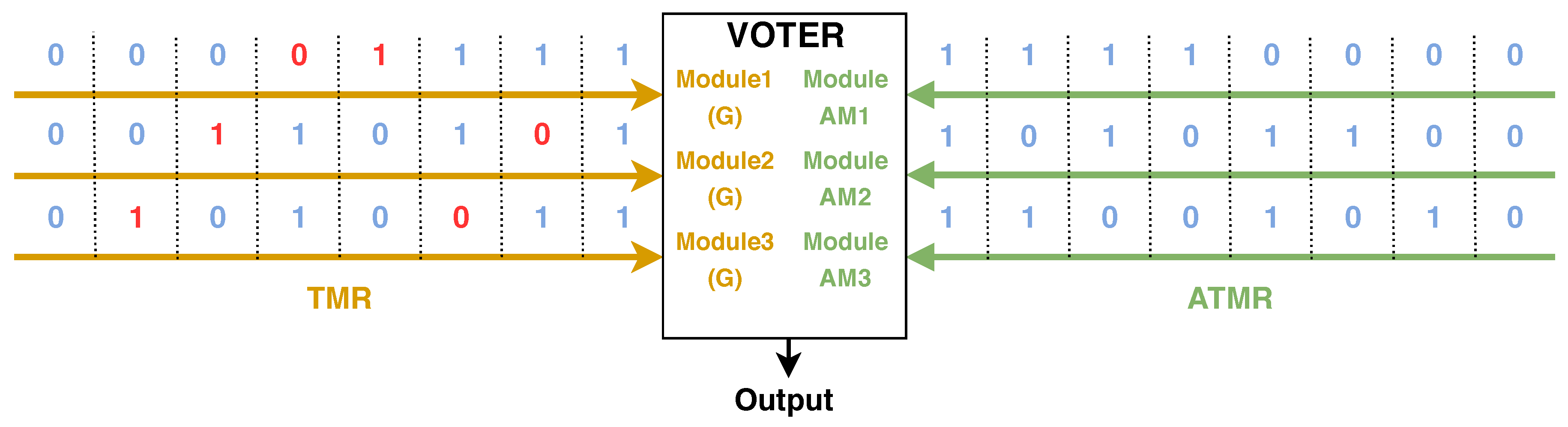

2.1. TMR, Voter, and Reliability

2.2. ATMR, Voter, and Reliability

3. Fault-Tolerant Voter for ATMR

4. Analysis of Fault-Tolerant Voters

4.1. Simulation Setup

4.2. Analysis of Simulation Results

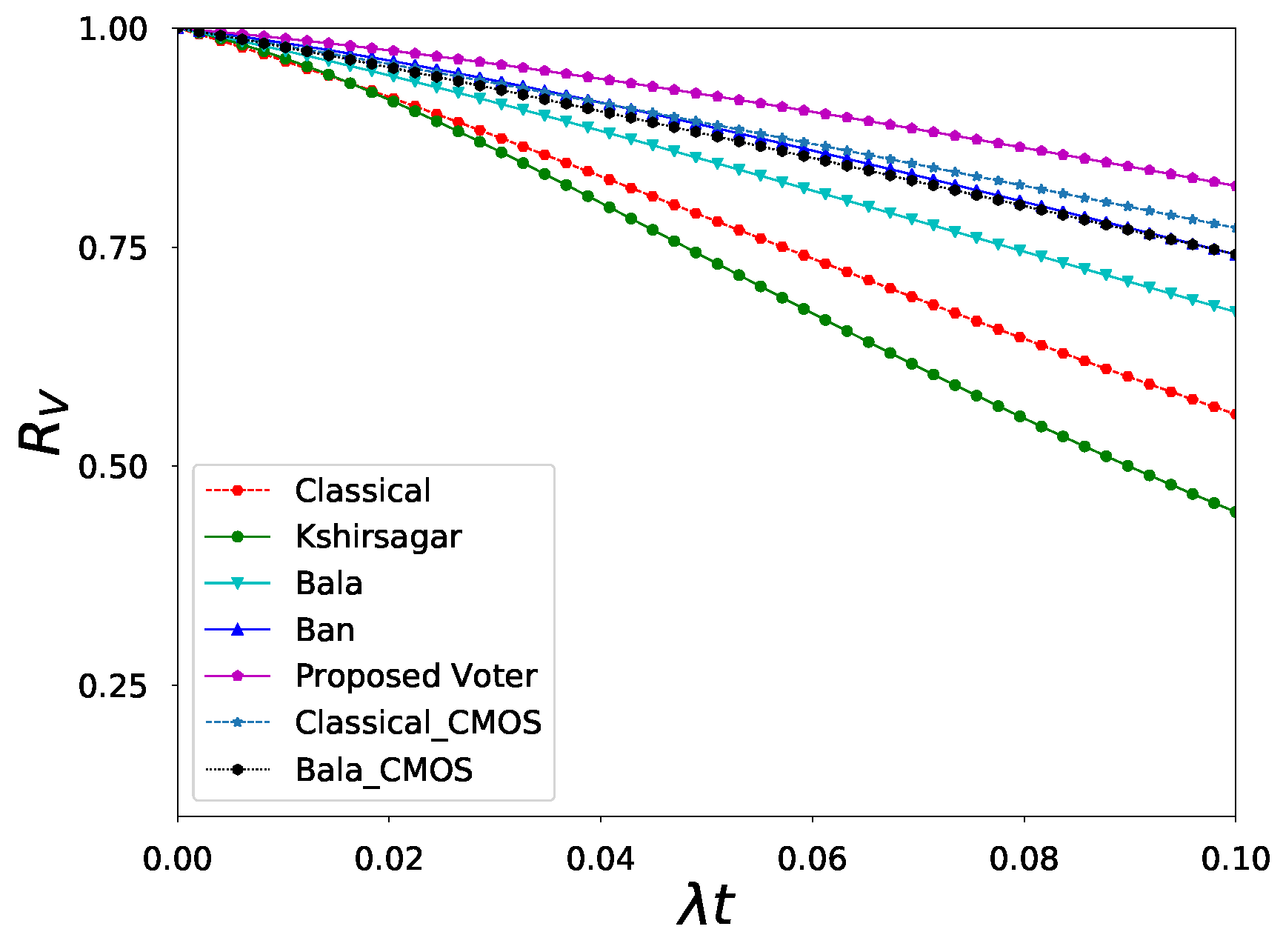

4.3. Reliability Calculations

5. Conclusions

Author Contributions

Funding

Conflicts of Interest

References

- Kshirsagar, R.V.; Patrikar, R.M. Design of a novel fault-tolerant voter circuit for TMR implementation to improve reliability in digital circuits. Microelectron. Reliab. 2009, 49, 1573–1577. [Google Scholar] [CrossRef]

- Oliveira, I.F.; Schvittz, R.B.; Butzen, P.F. Fault masking ratio analysis of majority voters topologies. In Proceedings of the 2018 IEEE 19th Latin-American Test Symposium (LATS), Sao Paulo, Brazil, 12–14 March 2018; pp. 1–6. [Google Scholar]

- Blanke, M.; Kinnaert, M.; Lunze, J.; Staroswiecki, M.; Schröder, J. Diagnosis and Fault-Tolerant Control; Springer: Berlin/Heidelberg, Germany, 2006; Volume 2. [Google Scholar]

- Isermann, R. Fault-Diagnosis Systems: An Introduction from Fault Detection to Fault Tolerance; Springer Science & Business Media: Berlin/Heidelberg, Germany, 2006. [Google Scholar]

- Balasubramanian, P.; Naayagi, R. Redundant logic insertion and fault tolerance improvement in combinational circuits. In Proceedings of the 2017 International Conference on Circuits, System and Simulation (ICCSS), London, UK, 14–17 July 2017; pp. 6–13. [Google Scholar]

- Lala, P.; Bu-Saba, F.; Xie, A.; Yarlagadda, K. Design of a fault-tolerant universal cell. Int. J. Electron. 1992, 72, 467–470. [Google Scholar] [CrossRef]

- Hassan, A.S.; Afzaal, U.; Arifeen, T.; Lee, J.A. Input-Aware Implication Selection Scheme Utilizing ATPG for Efficient Concurrent Error Detection. Electronics 2018, 7, 258. [Google Scholar] [CrossRef]

- Balasubramanian, P.; Prasad, K. A Fault Tolerance Improved Majority Voter for TMR System Architectures. WSEAS Trans. Circuits Syst. 2016, 15, 108–122. [Google Scholar]

- Balasubramanian, P.; Maskell, D.; Mastorakis, N. Majority and Minority Voted Redundancy Scheme for Safety-Critical Applications with Error/No-Error Signaling Logic. Electronics 2018, 7, 272. [Google Scholar] [CrossRef]

- Gomes, I.A.; Martins, M.G.; Reis, A.I.; Kastensmidt, F.L. Exploring the use of approximate TMR to mask transient faults in logic with low area overhead. Microelectron. Reliab. 2015, 9, 2072–2076. [Google Scholar] [CrossRef]

- Hassan, A.S.; Arifeen, T.; Moradian, H.; Lee, J.A. Generation Methodology for Good-Enough Approximate Modules of ATMR. J. Electron. Test. 2018, 34, 651–665. [Google Scholar] [CrossRef]

- Sánchez-Clemente, A.J.; Entrena, L.; García-Valderas, M. Partial TMR in FPGAs using approximate logic circuits. IEEE Trans. Nucl. Sci. 2016, 63, 2233–2240. [Google Scholar] [CrossRef]

- Polian, I.; Hayes, J.P. Selective hardening: Toward cost-effective error tolerance. IEEE Des. Test Comput. 2011, 28, 54–63. [Google Scholar] [CrossRef]

- Albandes, I.; Serrano-Cases, A.; Martins, M.; Martínez-Álvarez, A.; Cuenca-Asensi, S.; Kastensmidt, F.L. Design of approximate-TMR using approximate library and heuristic approaches. Microelectron. Reliab. 2018, 88, 898–902. [Google Scholar] [CrossRef]

- Arifeen, T.; Hassan, A.S.; Moradian, H.; Lee, J.A. Input Vulnerability-Aware Approximate Triple Modular Redundancy: Higher Fault Coverage, Improved Search Space, and Reduced Area Overhead. Electron. Lett. 2018, 54, 934–936. [Google Scholar] [CrossRef]

- Ruano, O.; Maestro, J.; Reviriego, P. A methodology for automatic insertion of selective TMR in digital circuits affected by SEUs. IEEE Trans. Nucl. Sci. 2009, 56, 2091–2102. [Google Scholar] [CrossRef]

- Pagliarini, S.N.; Naviner, L.A.d.B.; Naviner, J.F. Selective hardening methodology for combinational logic. In Proceedings of the 2012 13th Latin American Test Workshop (LATW), Quito, Ecuador, 10–13 April 2012; pp. 1–6. [Google Scholar]

- Ban, T.; de Barros Naviner, L.A. A simple fault-tolerant digital voter circuit in TMR nanoarchitectures. In Proceedings of the 2010 8th IEEE International NEWCAS Conference (NEWCAS), Montreal, QC, Canada, 20–23 June 2010; pp. 269–272. [Google Scholar]

- El-Maleh, A.H.; Al-Hashimi, B.M.; Melouki, A.; Al-Yamani, A. Transistor-level based defect-tolerance for reliable nanoelectronics. In Robust Computing with Nano-Scale Devices; Springer: Dordrecht, The Netherlands, 2010; pp. 29–49. [Google Scholar]

- Mukherjee, A.; Dhar, A.S. Triple transistor based fault tolerance for resource constrained applications. Microelectron. J. 2017, 68, 1–6. [Google Scholar] [CrossRef]

- Lee, H.; Ha, D. Atalanta: An Efficient ATPG for Combinational Circuits; Technical Report, 93-12; Dep’t of Electrical Eng., Virginia Polytechnic Institute and State University: Blacksburg, VA, USA, 1993. [Google Scholar]

- Danilov, I.A.; Gorbunov, M.S.; Antonov, A.A. SET tolerance of 65 nm CMOS majority voters: a comparative study. IEEE Trans. Nucl. Sci. 2014, 61, 1597–1602. [Google Scholar] [CrossRef]

- FreePDK45. North Carolina State University. 2011. Available online: https://www.eda.ncsu.edu/wiki/FreePDK45:Contents (accessed on 15 September 2018).

- Dubrova, E. Fault Tolerant Design: An Introduction; Department of Microelectronics and Information Technology, Royal Institute of Technology: Stockholm, Sweden, 2008. [Google Scholar]

| Input Vectors | Original Circuit | Approximate | Approximate TMR Approximate | Approximate | Voter Output | ||

|---|---|---|---|---|---|---|---|

| I | J | K | Output (G) | Module 1 (AM1=A) | Module 2 (AM2=B) | Module 3 (AM3=C) | [ATMR Output] |

| 0 | 0 | 0 | 1 | 1 | 1 | 0 | 1 |

| 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 |

| 0 | 1 | 0 | 0 | 1 | 0 | 0 | 0 |

| 0 | 1 | 1 | 0 | 0 | 0 | 0 | 0 |

| 1 | 0 | 0 | 1 | 1 | 1 | 1 | 1 |

| 1 | 0 | 1 | 1 | 1 | 0 | 1 | 1 |

| 1 | 1 | 0 | 1 | 1 | 1 | 1 | 1 |

| 1 | 1 | 1 | 0 | 0 | 1 | 0 | 0 |

© 2019 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Arifeen, T.; Hassan, A.S.; Lee, J.-A. A Fault Tolerant Voter for Approximate Triple Modular Redundancy. Electronics 2019, 8, 332. https://doi.org/10.3390/electronics8030332

Arifeen T, Hassan AS, Lee J-A. A Fault Tolerant Voter for Approximate Triple Modular Redundancy. Electronics. 2019; 8(3):332. https://doi.org/10.3390/electronics8030332

Chicago/Turabian StyleArifeen, Tooba, Abdus Sami Hassan, and Jeong-A Lee. 2019. "A Fault Tolerant Voter for Approximate Triple Modular Redundancy" Electronics 8, no. 3: 332. https://doi.org/10.3390/electronics8030332