Analysis and Design of Harmonic Rejection Low Noise Amplifier with an Embedded Notch Filter

Abstract

:1. Introduction

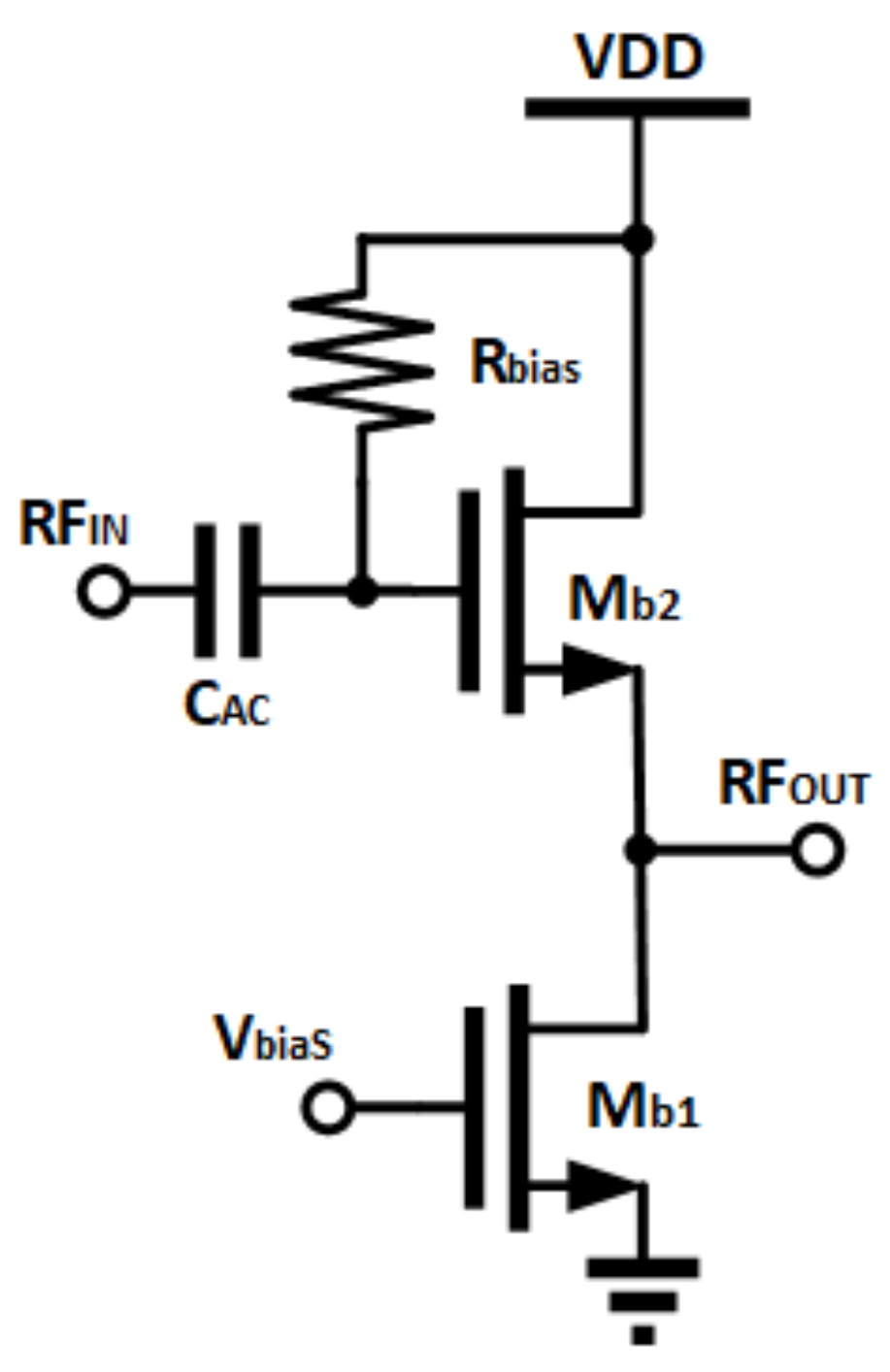

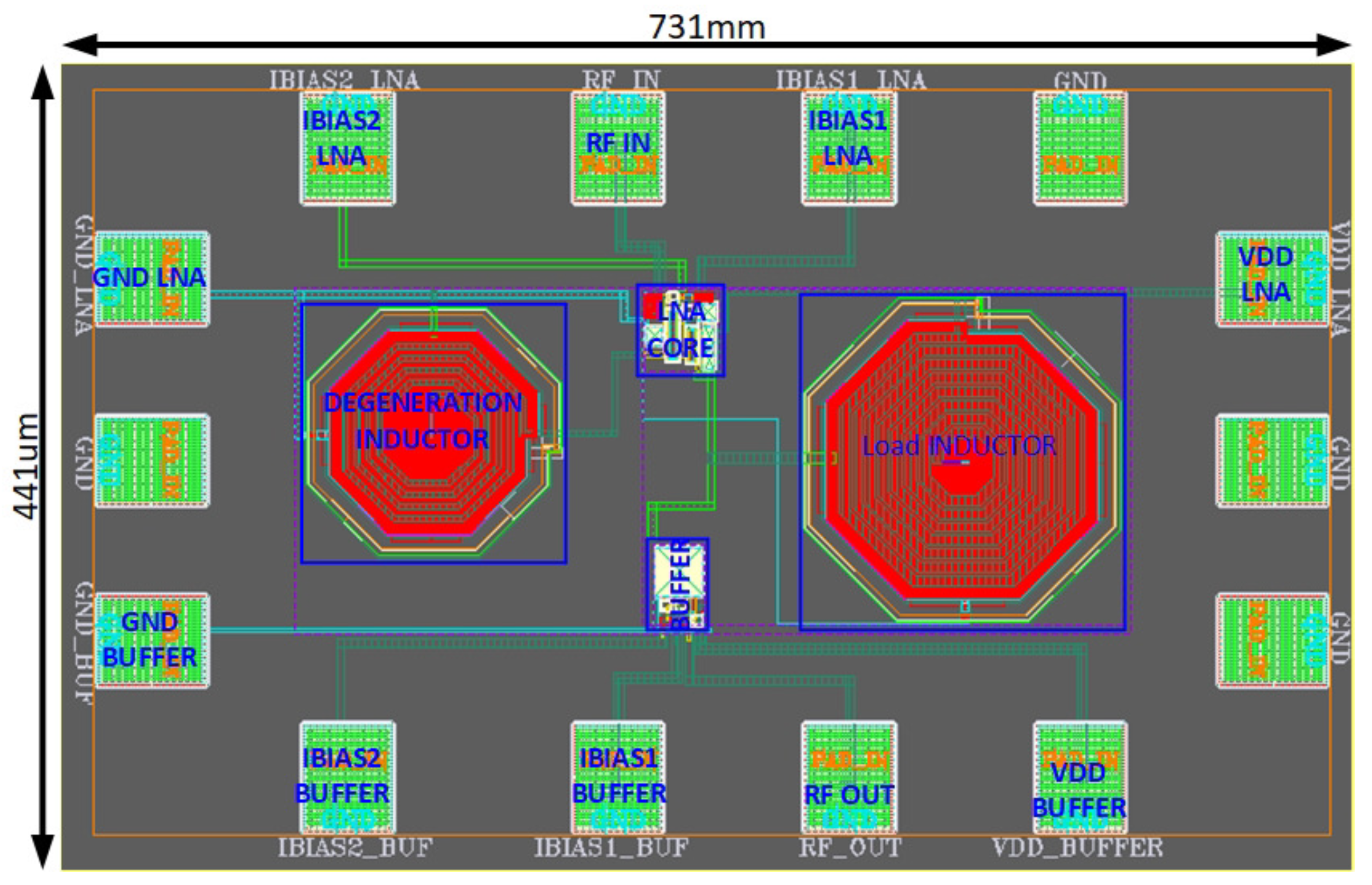

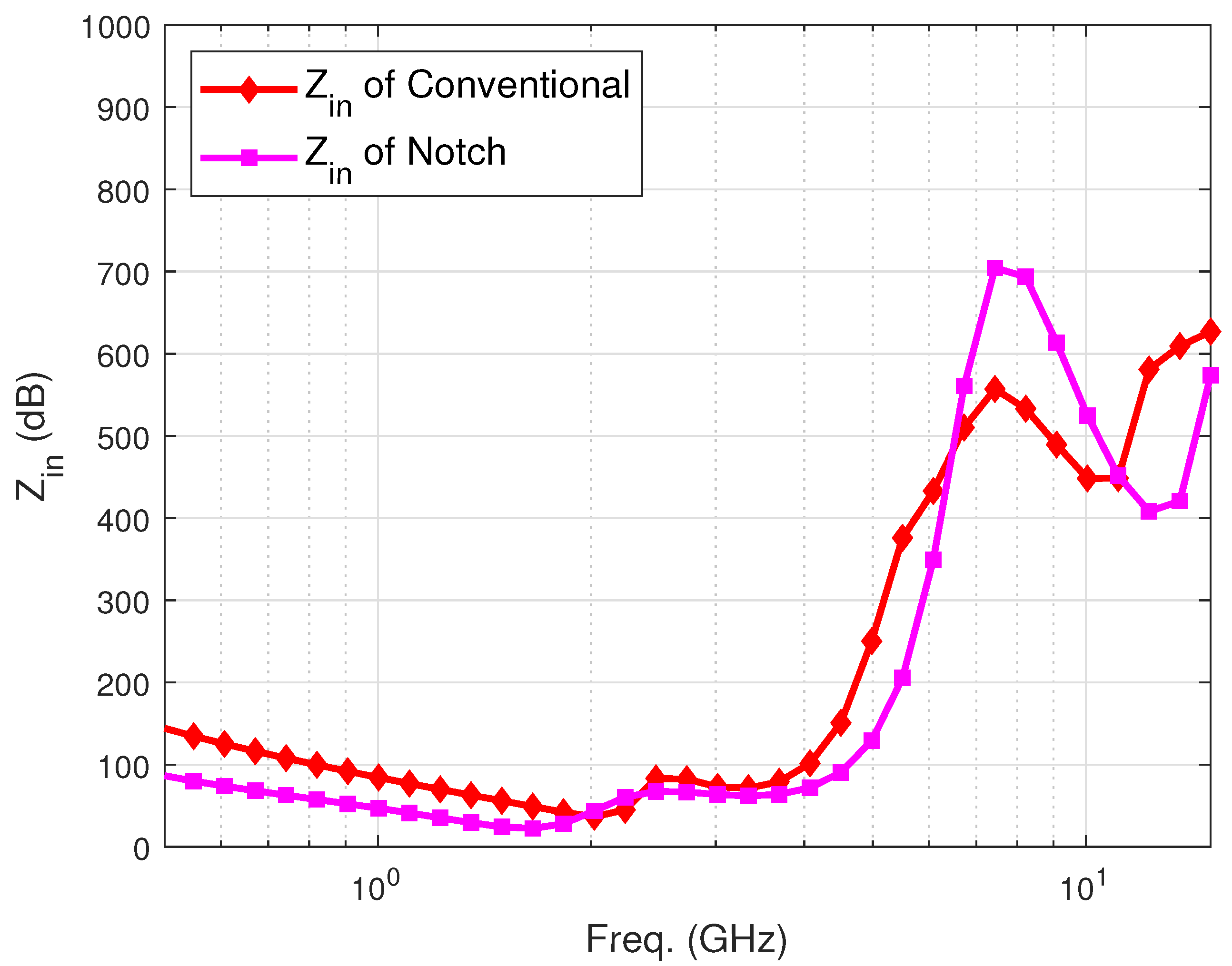

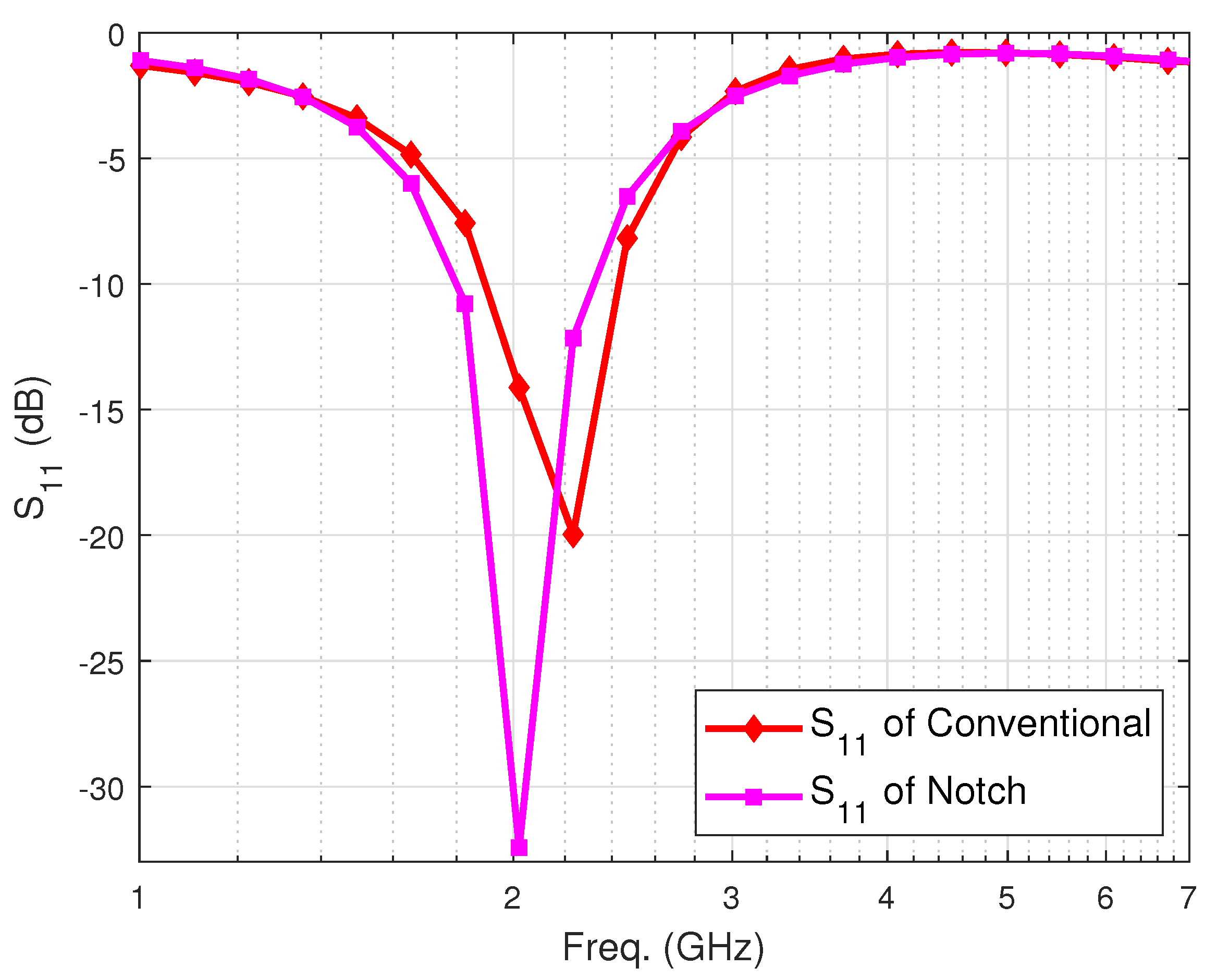

2. Proposed Notch LNA

3. Verifications

4. Conclusions

Author Contributions

Funding

Acknowledgments

Conflicts of Interest

References

- Kim, J.; Silva-Martinez, J. Low-power, low-cost CMOS direct-conversion receiver front-end for multi-standard applications. IEEE J. Solid-State Circuits. 2013, 48, 2090–2103. [Google Scholar]

- Kulkarni, R.; Kim, J.; Jeon, H.-J.; Xiao, J.; Silva-Martinez, J. UHF receiver front-end: Implementation and analog baseband design considerations. IEEE Trans. Very Large Scale Integr. (Vlsi) Syst. 2013, 20, 197–210. [Google Scholar] [CrossRef]

- Kim, J. Broadband RF Front-End Design for Multi-Standard Receiver with High-Linearity and Low-Noise Techniques. Ph.D. Thesis, Texas A&M University, College Station, TX, USA, 2012. [Google Scholar]

- Behzad, R. RF Microelectronics, 2nd ed.; Prentice Hall: Upper Saddle River, NJ, USA, 1998; pp. 63–70. [Google Scholar]

- Aslam, A.R.; Alessandro, P.; Peter, V.; Tyson, T. A harmonic rejection mixer robust to RF device mismatches. In Proceedings of the International Solid-State Circuit Conference, San Francisco, CA, USA, 20–24 February 2011; pp. 66–67. [Google Scholar]

- Ru, Z.; Klumperink, E.A.M.; Wienk, G.J.M.; Nauta, B. A software-defined radio receiver architecture robust to out-of-band interference. In Proceedings of the International Solid-State Circuit Conference, San Francisco, CA, USA, 8–12 February 2009; pp. 230–231. [Google Scholar]

- Andreas, G.; Silvester, S.; Stefan, T.; Krzysztof, D.; Harald, P.; Mario, H. A harmonic rejection strategy for 25% Duty-Cycle IQ-mixers using digital-to-time converters. In IEEE Transactions on Circuits and Systems II: Express Briefs (Early Access); IEEE: Piscataway, NJ, USA, 2019. [Google Scholar] [CrossRef]

- Cha, H.-K.; Kwon, K.; Choi, J.; Kim, H.-T.; Lee, K. A CMOS wideband RF front-end with mismatch calibrated harmonic rejection mixer for terrestrial digital TV tuner applications. IEEE Trans. Microw. Theory Tech. 2010, 58, 2143–2151. [Google Scholar] [CrossRef]

- Shaeffer, D.K.; Lee, T.H. A 1.5-V, 1.5-GHz CMOS low noise amplifier. IEEE J. Solid-State Circuits 1997, 32, 745–759. [Google Scholar] [CrossRef] [Green Version]

- Schaumann, R.; Van Valkenburg, M.E.; Xiao, H. Design of Analog Filters, 1st ed.; Oxford University Press: New York, NY, USA, 2001; pp. 125–129. [Google Scholar]

- Lee, T.H.; Samavati, H.; Rategh, H.R. 5-GHz CMOS Wireless LANs. IEEE Trans. Microw. Theory Tech. 2002, 50, 268–280. [Google Scholar] [CrossRef]

- Huang, Z.Y.; Huang, C.C. CMOS Dual-Wideband Low-Noise Amplifier with Notch Filter for 3.1 GHz-10.6 GHz Ultra-Wideband Wireless Receiver. In Proceedings of the 7th International Conference on ASIC, Guilin, China, 22–25 October 2007; pp. 415–418. [Google Scholar]

- Jeon, Y.; Yoon, S.W.; Kim, C.; Moon, H.; Nam, I. A Wideband Digital TV Receiver front-end with On-chip Notch Filter. Int. Conf. Electron. Inf. Commun. (ICEIC) 2019, 415–418. [Google Scholar]

- Park, J.W.; Razavi, B. A Harmonic-Rejection CMOS LNA for Broadband Radios. IEEE J. Solid-State Circuits 2013, 48, 1072–1084. [Google Scholar] [CrossRef]

- Sepidband, P.; Entesari, K. A CMOS Wideband Receiver Resilient to Out-of-Band Blockers Using Blocker Detection and Rejection. IEEE Trans. Microw. Theory Tech. 2018, 66, 2340–2355. [Google Scholar] [CrossRef]

- Kwon, K.; Kim, S.; Son, K.Y. A Hybrid Transformer-Based CMOS Duplexer With a Single-Ended Notch-Filtered LNA for Highly Integrated Tunable RF Front-Ends. IEEE Microw. Wirel. Components Lett. 2018, 28, 1032–1034. [Google Scholar] [CrossRef]

- Hamasawa, A.; Kanaya, H. Dual-band differential outputs CMOS Low Noise Amplifier. In Proceedings of the IEEE 20th Electronics Packaging Technology Conference (EPTC), Singapore, 28 February 2019; pp. 661–664. [Google Scholar]

| Component | Size |

|---|---|

| M1 | (450 m/40nm) |

| M2 | (300 m/40nm) |

| 1.7 nH | |

| 500 fF | |

| 4 nH | |

| 700 fF | |

| 15 nH | |

| (3 m/40nm) | |

| (13.5 m/40nm) | |

| 4.2 pF | |

| 2.0 k |

| Architecture | Frequency | Sensed at V (dBm) | Sensed at V (dBm) |

|---|---|---|---|

| Conventional | 2.1 (GHz) | −39.7 | −37.98 |

| 6.3 (GHz) | −55.64 | −65 | |

| Notch | 2.1 (GHz) | −39.54 | −38.7 |

| 6.3 (GHz) | −65.44 | −87 |

| Specification | This Work | [11] | [12] | [13] | [14] | [15] | [16] | [17] |

|---|---|---|---|---|---|---|---|---|

| Harmonic Rejection (dBc) | 37 | 12 | 14 | 10 | >20 | 20 | 28 | 18 |

| Gain (dB) | 11 | 18.7 | 10.34 | 30 | 12–24 | 13.4–14 | 24.2 | 16.5 and 11.1 |

| NF (dB) | 3.1 | 4.8 | 3 | 2.8 | 3.5–5.84 | 4.4 | 6.4 | 3.1 and 3.7 |

| Supply (V) | 1.2 | 1.2 | 1.8 | 1.2 | 1.2 | 1 | 1.2 | NA |

| IIP3 (dBm) | 0.5 | −2 | −27, −22 | −11 | −15 to −12 | -3.3 to −2.8 | −12.5 | −4.84 −8.31 |

| P (mW) | 19 | 12.4 | 24.1 | 14 | 8.64 | 23.8 | 9.6 | NA |

| Technology (CMOS) | 40 nm | 240 nm | 180 nm | 130 nm | 65 nm | 65 nm | 65 nm | 180 nm |

© 2020 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Gyaang, R.; Lee, D.-H.; Kim, J. Analysis and Design of Harmonic Rejection Low Noise Amplifier with an Embedded Notch Filter. Electronics 2020, 9, 596. https://doi.org/10.3390/electronics9040596

Gyaang R, Lee D-H, Kim J. Analysis and Design of Harmonic Rejection Low Noise Amplifier with an Embedded Notch Filter. Electronics. 2020; 9(4):596. https://doi.org/10.3390/electronics9040596

Chicago/Turabian StyleGyaang, Raymond, Dong-Ho Lee, and Jusung Kim. 2020. "Analysis and Design of Harmonic Rejection Low Noise Amplifier with an Embedded Notch Filter" Electronics 9, no. 4: 596. https://doi.org/10.3390/electronics9040596