Layout Strengthening the ESD Performance for High-Voltage N-Channel Lateral Diffused MOSFETs

Abstract

:1. Introduction

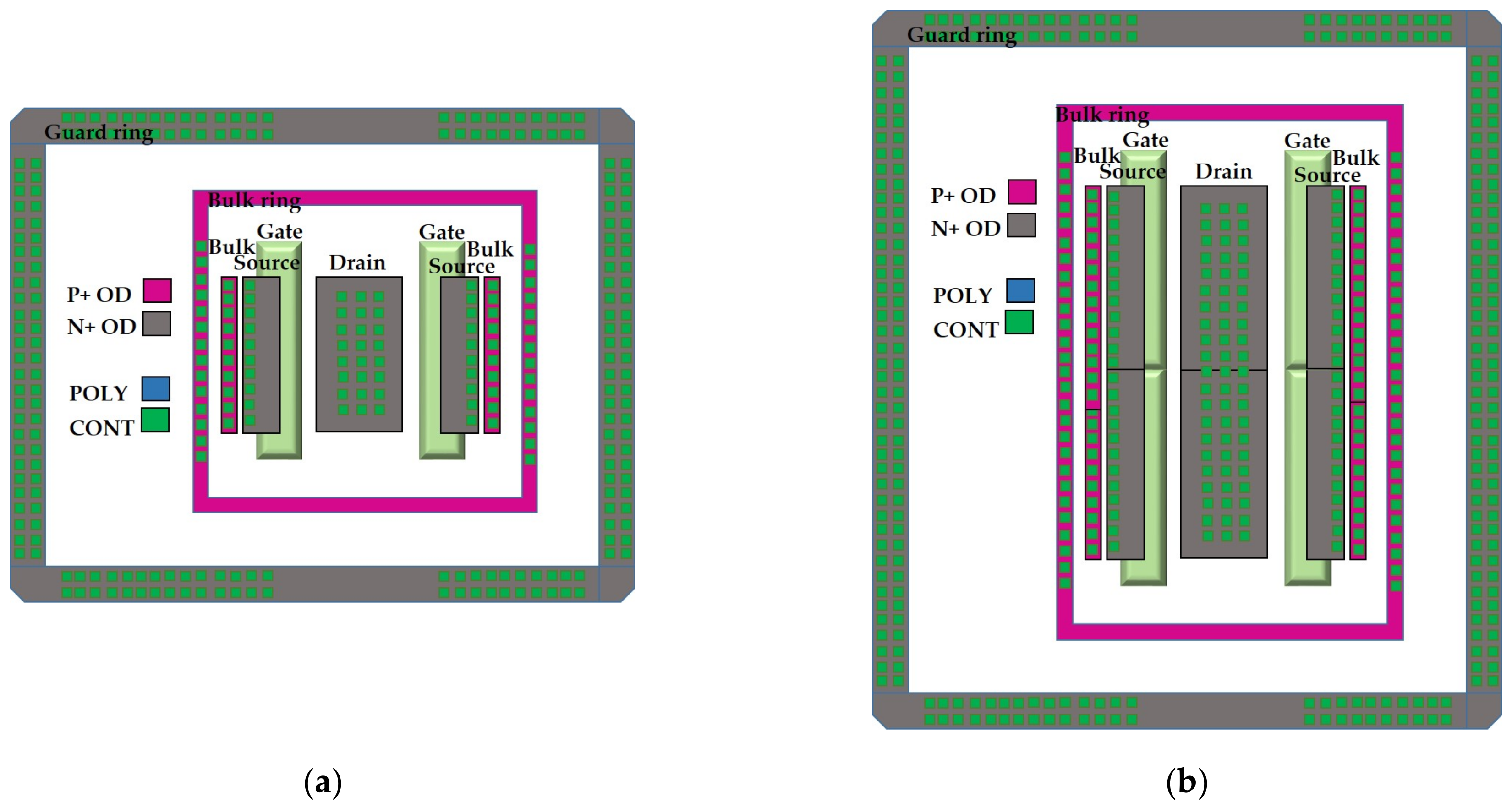

2. Cell Design of the HV nLDMOSs

2.1. HV nLDMOS Reference Device

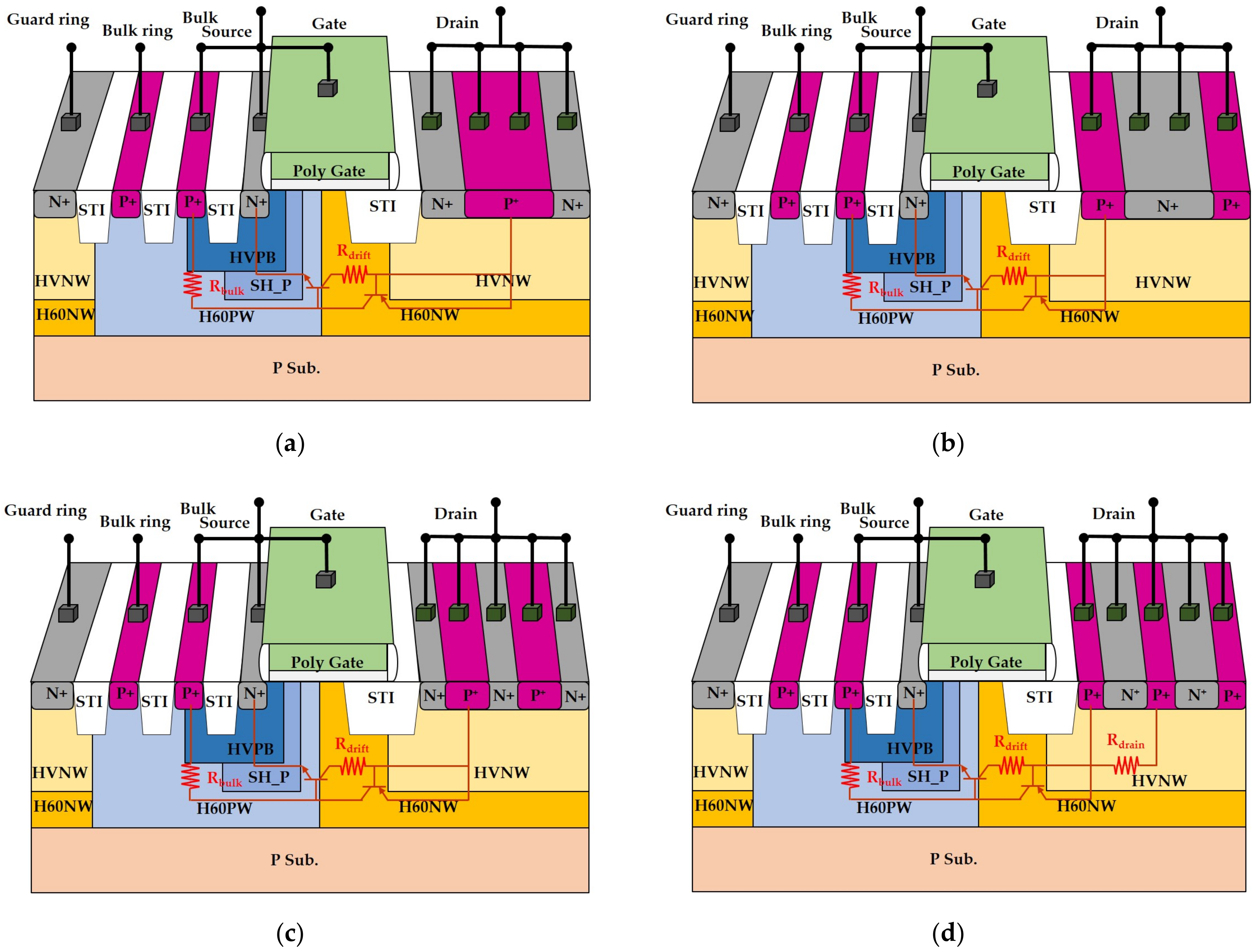

2.2. HV nLDMOS DUTs with Drift Region Modulation (Operating Voltage Modulation)

2.3. HV nLDMOS DUTs with Channel Width Modulation

2.4. HV nLDMOS DUTs with Embedded SCR Modulation

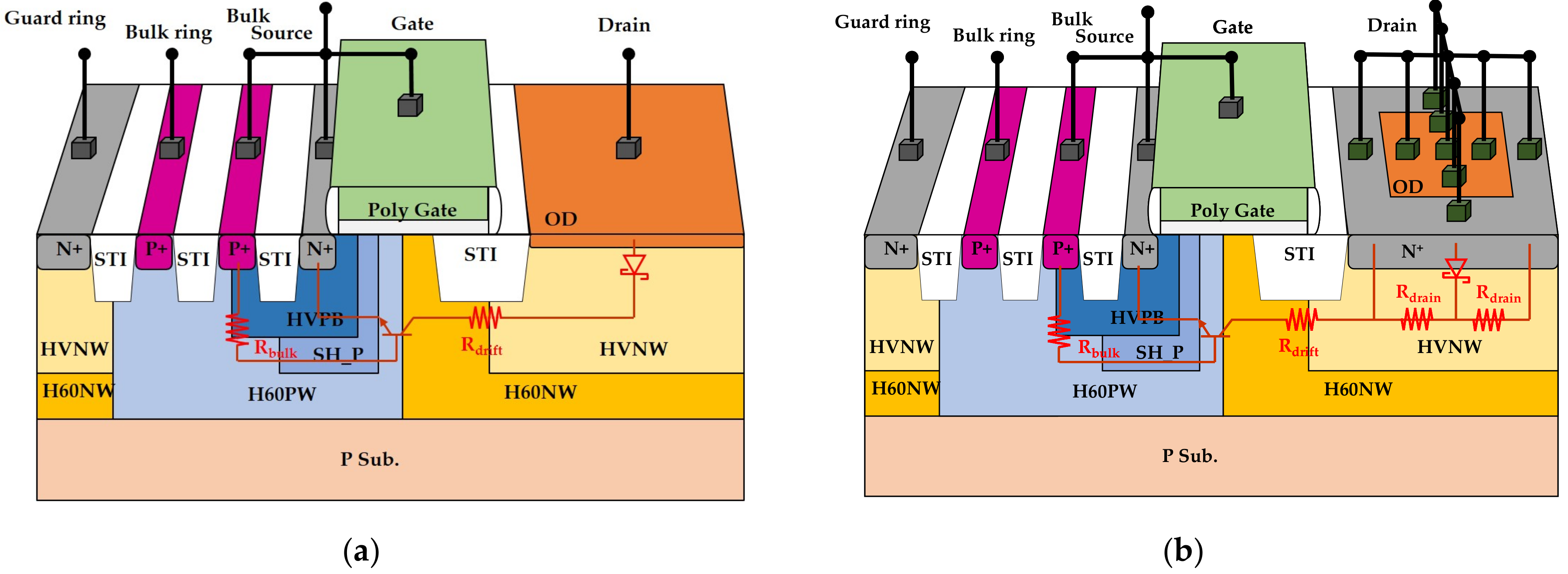

2.5. HV nLDMOS DUTs with Embedded Schottky-Diode Modulation

3. Experimental Testing Systems

4. Experimental Results

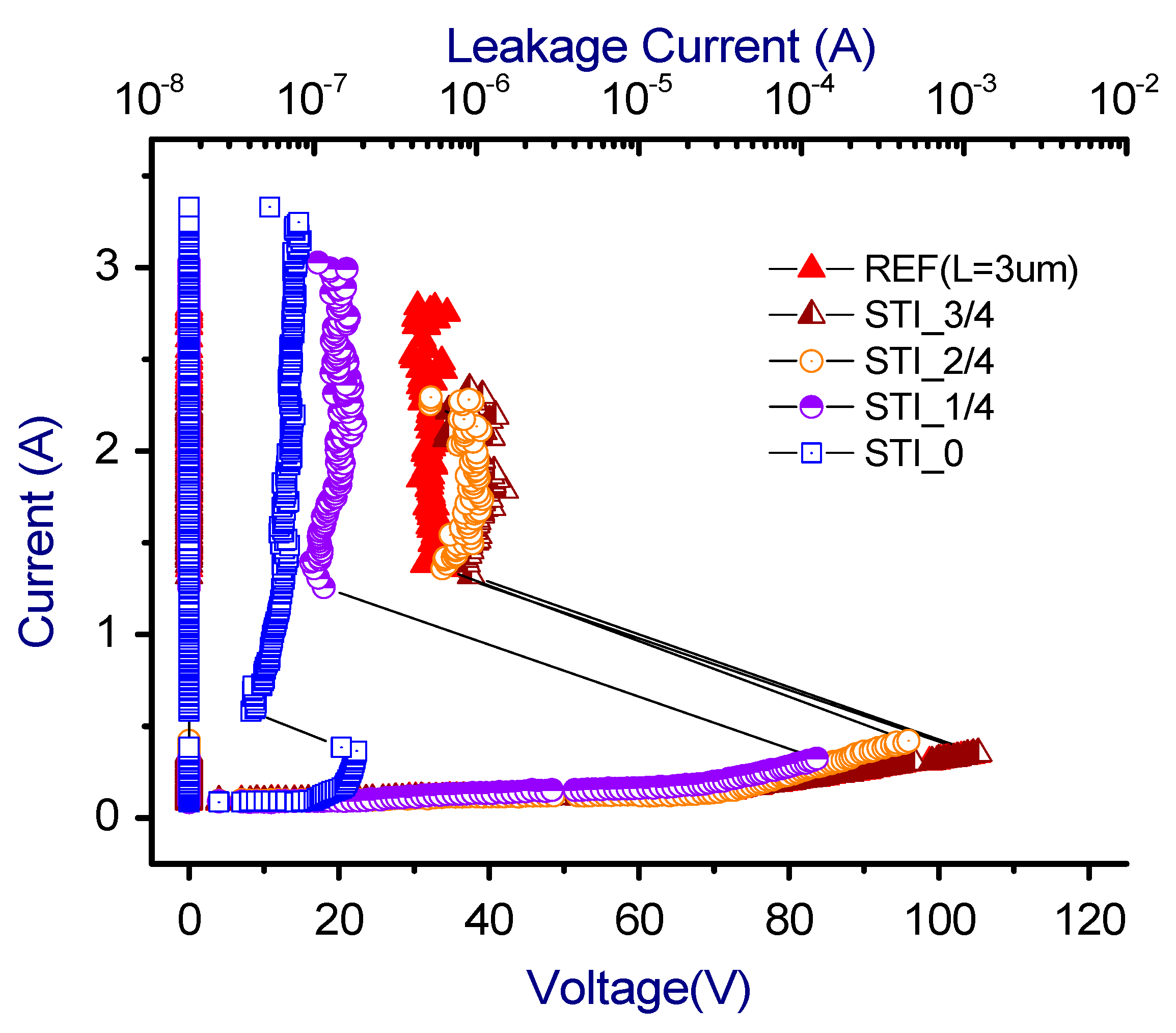

4.1. ESD Capability of HV nLDMOS DUTs with Drift-Region Modulation (Operating-Voltage Modulation)

4.2. ESD Capability of HV nLDMOS DUTs with Channel-width Modulation

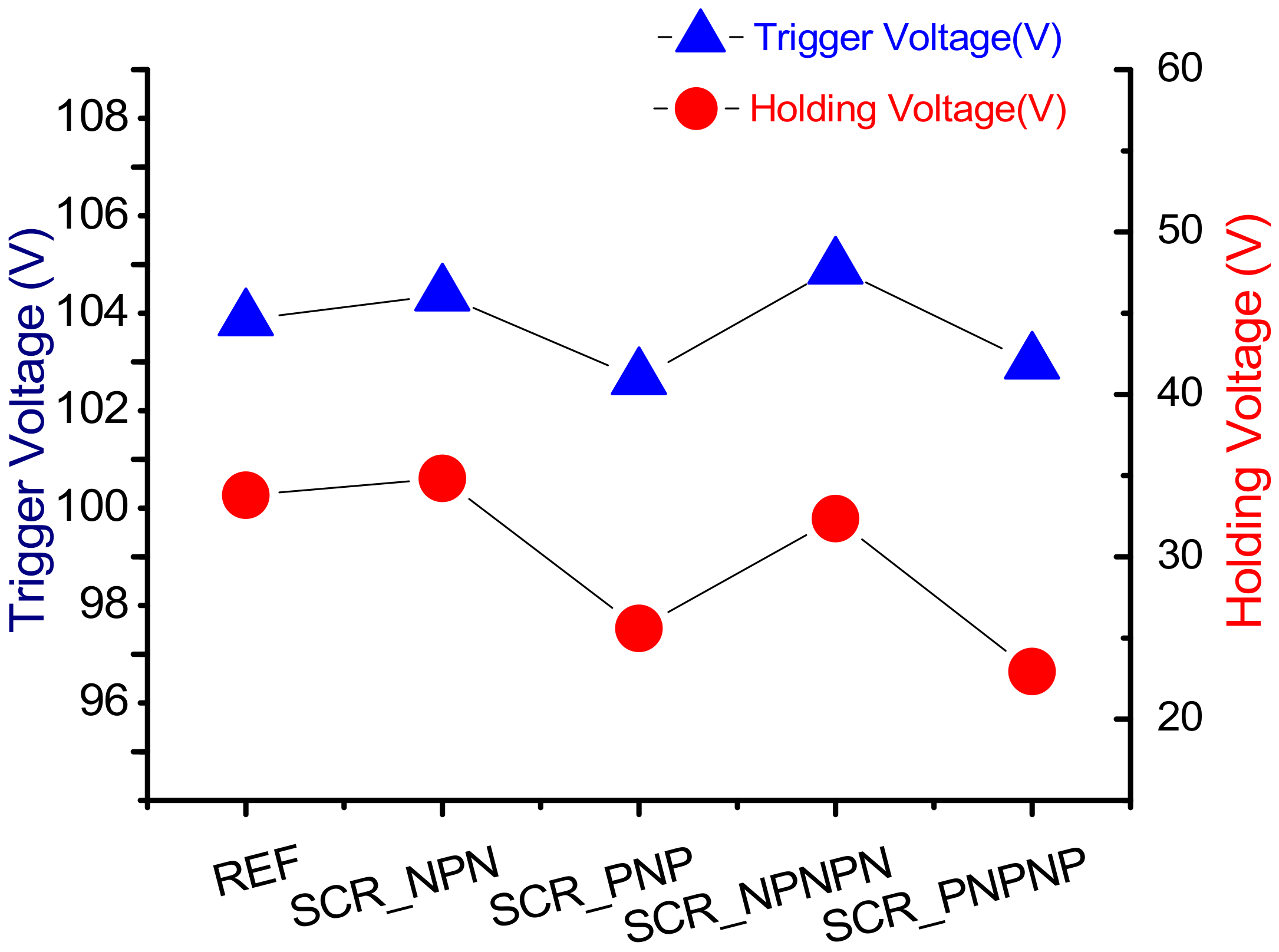

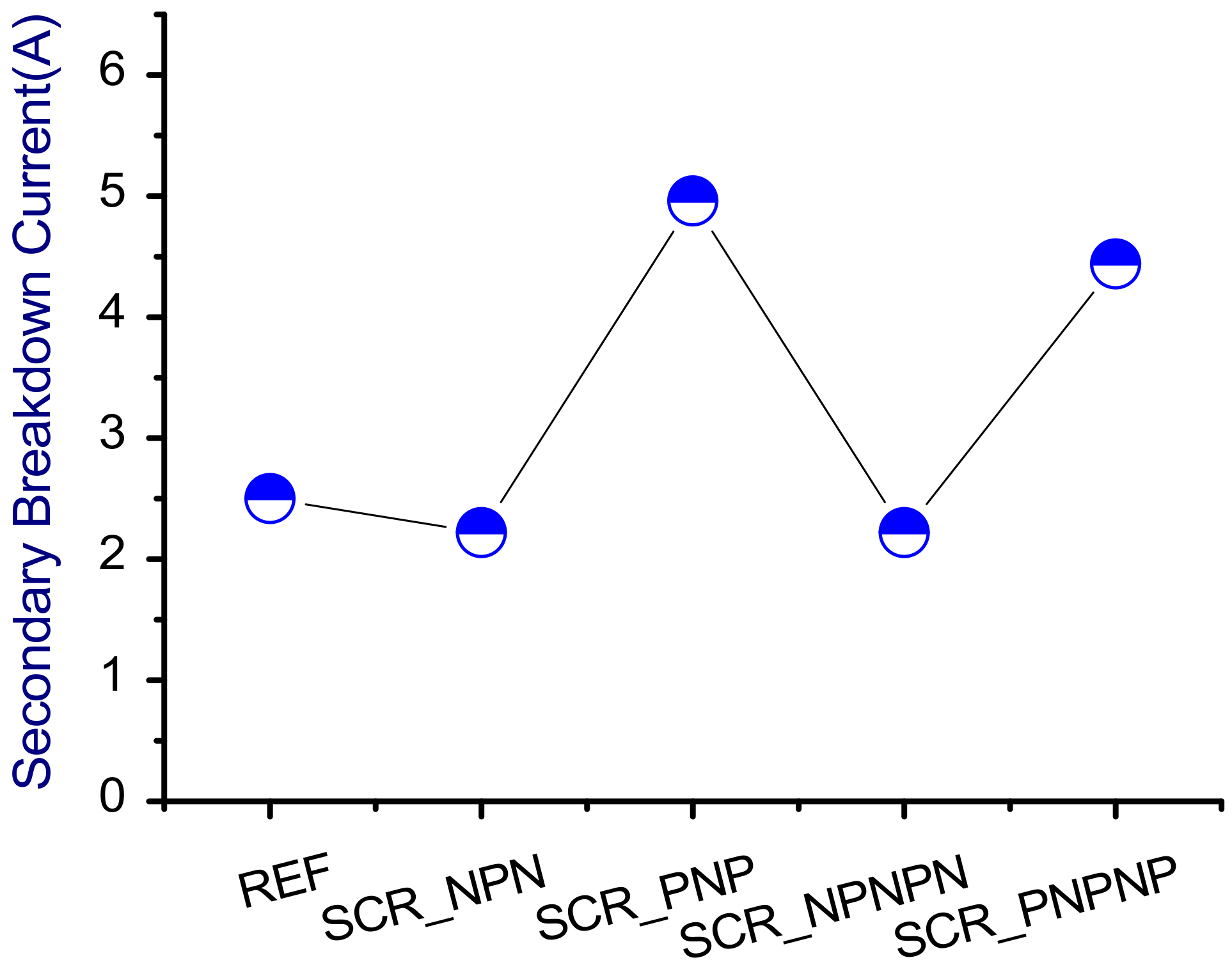

4.3. ESD Capability of HV nLDMOS DUTs with Embedded SCR Modulation

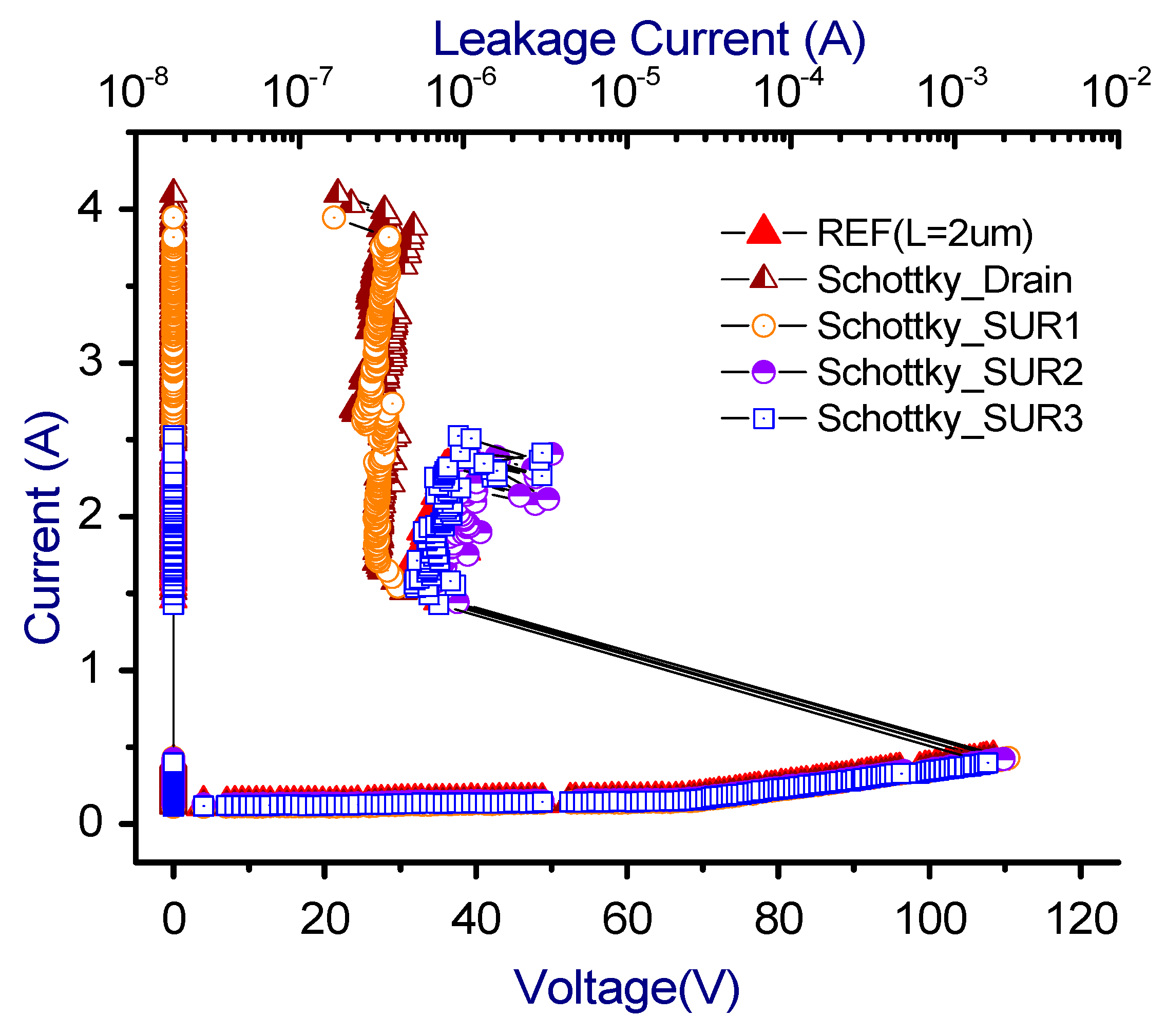

4.4. ESD Capability of HV nLDMOS DUTs with Embedded Schottky-Diode Modulation

5. TCAD Simulation and Verification

6. Conclusions

Author Contributions

Funding

Acknowledgments

Conflicts of Interest

Abbreviation

| Symbol | Meaning |

| BCD | Bipolar-Complementary metal-oxide-semiconductor-Double-diffused MOSFET |

| BJT | Bipolar-junction transistor |

| DUT | Device under test |

| ESD | Electrostatic discharge |

| FOM | Figure of merit |

| GGnMOS Gate | Grounded nMOSFET |

| HV nLDMOS | High voltage n-channel lateral diffused MOSFET |

| HBM | Human-body model |

| It2 | Secondary breakdown current |

| IC | Integrated circuit |

| IoT | Internet of things |

| LU | Latch-up |

| SCR | Silicon-controlled rectifier |

| STI | Shallow trench isolation |

| TLP | Transmission-line pulse system |

| Vbk | Breakdown voltage |

| Vh | Holding voltage |

| Vt1 | Trigger voltage |

References

- Lee, M.; Uhm, Y.; Kim, Y.; Kim, G.; Park, S. Intelligent power management device with middleware based living pattern learning for power reduction. IEEE Trans. Consum. Electron. 2009, 55, 2081–2089. [Google Scholar] [CrossRef]

- Murphey, Y.; Park, J.; Kiliaris, L.; Kuang, M.; Masrur, M.; Phillips, A.; Wang, Q. Intelligent Hybrid Vehicle Power Control—Part II: Online Intelligent Energy Management. IEEE Trans. Veh. Technol. 2013, 62, 69–79. [Google Scholar] [CrossRef]

- Vidya, V.; Dharmana, M. Model reference based intelligent control of an active suspension system for vehicles. In Proceedings of the International Conference on Circuit, Power and Computing Technologies, Kollam, India, 20–21 April 2017; pp. 1–5. [Google Scholar]

- Yang, L. Research on Design of Weak Current Protection Circuit in Intelligent Home Control Circuit under the Background of Internet of Things. In Proceedings of the International Conference on Mechanical, Control and Computer Engineering, Huhhot, China, 14–16 September 2018; pp. 189–191. [Google Scholar]

- Yi, D.; Su, J.; Liu, C.; Chen, W. Trajectory Clustering Aided Personalized Driver Intention Prediction for Intelligent Vehicles. IEEE Trans. Ind. Inf. 2019, 15, 3693–3702. [Google Scholar] [CrossRef] [Green Version]

- Vdovic, H.; Babic, J.; Podobnik, V. Automotive Software in Connected and Autonomous Electric Vehicles: A Review. IEEE Access 2019, 7, 166365–166379. [Google Scholar] [CrossRef]

- Zhongzheng, T.; Yangzi, S.; Silong, W. Design of Power Production Safety Monitoring System Based on Intelligent Internet of Things. In Proceedings of the International Conference on Smart Grid and Electrical Automation, Xiangtan, China, 10–11 August 2019; pp. 73–77. [Google Scholar]

- Lu, T.; Chen, X.; Bai, W. Research on environmental monitoring and control technology based on intelligent Internet of Things perception. J. Eng. 2019, 23, 8946–8950. [Google Scholar] [CrossRef]

- Sun, Z.; Xing, X.; Wang, T.; Lv, Z.; Yan, B. An Optimized Clustering Communication Protocol Based on Intelligent Computing in Information-Centric Internet of Things. IEEE Access 2019, 7, 28238–28249. [Google Scholar] [CrossRef]

- Zhang, Y.; Pendharkar, S.; Hower, P.; Giombanco, S.; Amoroso, A.; Marino, F. A RESURF P-N bimodal LDMOS suitable for high voltage power switching applications. In Proceedings of the International Symposium on Power Semiconductor Devices & IC’s, Hong Kong, China, 10–14 May 2015; pp. 61–64. [Google Scholar]

- Kojima, J.; Matsuda, J.; Kamiyama, M.; Tsukiji, N.; Kobayashi, H. Optimization and analysis of high reliability 30–50 V dual RESURF LDMOS. In Proceedings of the International Conference on Solid-State and Integrated Circuit Technology, Hangzhou, China, 25–28 October 2016; pp. 1–3. [Google Scholar]

- Matsuda, J.; Kuwana, A.; Kojima, J.; Tsukiji, N.; Kobayashi, H. Wide SOA and High Reliability 60–100 V LDMOS Transistors with Low Switching Loss and Low Specific On-Resistance. In Proceedings of the International Conference on Solid-State and Integrated Circuit Technology, Qingdao, China, 31 October–3 November 2018; pp. 1–3. [Google Scholar]

- Zhang, G.; Zhang, W.; He, J.; Zhu, X.; Zhang, S.; Zhao, J.; Zhang, Z.; Qiao, M.; Zhou, X.; Li, Z.; et al. Experiments of a Novel low on-resistance LDMOS with 3-D Floating Vertical Field Plate. In Proceedings of the International Symposium on Power Semiconductor Devices and ICs, Shanghai, China, 19–23 May 2019; pp. 507–510. [Google Scholar]

- Guo, S.; Chen, X. A Novel p-LDMOS Additionally Conducting Electrons by Control ICs. IEEE J. Electron Devices Soc. 2019, 7, 710–716. [Google Scholar] [CrossRef]

- Bhoir, M.; Kaushal, K.; Panda, S.; Singh, A.; Jatana, H.; Mohapatra, N. Source Underlap—A Novel Technique to Improve Safe Operating Area and Output-Conductance in LDMOS Transistors. IEEE Trans. Electron Devices 2019, 66, 4823–4828. [Google Scholar] [CrossRef]

- Wei, Y.; Luo, X.; Ge, W.; Zhao, Z.; Ma, Z.; Wei, J. A Split Triple-Gate Power LDMOS with Improved Static-State and Switching Performance. IEEE Trans. Electron Devices 2019, 66, 2669–2674. [Google Scholar] [CrossRef]

- Duvvury, C.; Carvajal, F.; Jones, C.; Briggs, D. Lateral DMOS design for ESD robustness. In Proceedings of the International Electron Devices Meeting. IEDM Technical Digest, Washington, DC, USA, 10–10 December 1997; pp. 1–4. [Google Scholar]

- Kawamoto, K.; Takahashi, S.; Fujino, S.; Shirakawa, I. A no-snapback LDMOSFET with automotive ESD endurance. IEEE Trans. Electron Devices 2002, 49, 2047–2053. [Google Scholar] [CrossRef]

- Wang, C.; Ker, M. ESD Protection Design with Lateral DMOS Transistor in 40-V BCD Technology. IEEE Trans. Electron Devices 2010, 57, 3395–3404. [Google Scholar] [CrossRef]

- Chen, W.; Ker, M. New Layout Arrangement to Improve ESD Robustness of Large-Array High-Voltage nLDMOS. IEEE Electron Device Lett. 2010, 31, 159–161. [Google Scholar] [CrossRef]

- Chen, W.; Ker, M. Improving Safe Operating Area of nLDMOS Array With Embedded Silicon Controlled Rectifier for ESD Protection in a 24-V BCD Process. IEEE Trans. Electron Devices 2011, 58, 2944–2951. [Google Scholar] [CrossRef]

- Malobabic, S.; Salcedo, J.; Hajjar, J.; Liou, J. NLDMOS ESD Scaling Under Human Metal Model for 40-V Mixed-Signal Applications. IEEE Electron Device Lett. 2012, 33, 1595–1597. [Google Scholar] [CrossRef]

- Ye, R.; Liu, S.; Sun, W.; Su, W.; Lin, F.; Sun, G.; Lin, Z. ESD failure mechanism and optimiztion for the LDMOS with low on-resistance and large geometric array used as output device. In Proceedings of the International Symposium on Power Semiconductor Devices and ICs, Prague, Czech Republic, 12–16 June 2016; pp. 239–242. [Google Scholar]

- Chen, S.; Lee, M. Reliability Analysis of P+ Pickup on Anti-ESD Performance in Four CMOS Low-voltage Technology Nodes. IETE J. Res. 2016, 62, 752–761. [Google Scholar] [CrossRef]

- Kumar, B.; Shrivastava, M. Part II: RF, ESD, HCI, SOA, and Self Heating Concerns in LDMOS Devices Versus Quasi-Saturation. IEEE Trans. Electron Devices 2018, 65, 199–206. [Google Scholar] [CrossRef]

- Lee, J.; Prabhu, M.; Natarajan, M. Engineering ESD Robust LDMOS SCR Devices in FinFET Technology. IEEE Electron Device Lett. 2018, 39, 1011–1013. [Google Scholar] [CrossRef]

- Kranthi, N.; Kumar, B.; Salman, A.; Boselli, G.; Shrivastava, M. Physical Insights into the Low Current ESD Failure of LDMOS-SCR and its Implication on Power Scalability. In Proceedings of the International Reliability Physics Symposium, Monterey, CA, USA, 31 March–4 April 2019; pp. 1–5. [Google Scholar]

- Jin, X.; Wang, Y.; Zhong, Z. Optimization of LDMOS-SCR Device for ESD Protection Based On 0.5 μm CMOS Process. In Proceedings of the International Workshop on the Electromagnetic Compatibility of Integrated Circuits, Hangzhou, China, 21–23 October 2019; pp. 195–197. [Google Scholar]

- Oh, K.; Duvvury, C.; Salling, C.; Banerjee, K.; Dutton, R. Non-uniform bipolar conduction in single finger NMOS transistors and implications for deep submicron ESD design. In Proceedings of the International Reliability Physics Symposium Proceedings, Orlando, FL, USA, 30 April–3 May 2001; pp. 226–234. [Google Scholar]

- Oh, K.; Banerjee, K.; Duvvury, C.; Dutton, R. Non-uniform conduction induced reverse channel length dependence of ESD reliability for silicided NMOS transistors. In Proceedings of the International Electron Devices Meeting, San Francisco, CA, USA, USA, 8–11 December 2002; pp. 341–344. [Google Scholar]

- Ker, M.; Chen, J. Self-Substrate-Triggered Technique to Enhance Turn-On Uniformity of Multi-Finger ESD Protection Devices. IEEE J. Solid-State Circuits 2006, 41, 2601–2609. [Google Scholar] [CrossRef]

- Ker, M.; Hsu, K. Overview of on-chip electrostatic discharge protection design with SCR-based devices in CMOS integrated circuits. IEEE Trans. Device Mater. Reliab. 2005, 5, 235–249. [Google Scholar]

- Liang, H.; Gu, X.; Dong, S.; Liou, J. RC-Embedded LDMOS-SCR with High Holding Current for High-Voltage I/O ESD Protection. IEEE Trans. Device Mater. Reliab. 2015, 15, 495–499. [Google Scholar] [CrossRef]

- Do, K.; Woo, J.; Koo, Y.; Lee, K. A Study of Dual-Directional SCR with Low Dynamic Resistance and High Holding Voltage for Low-Voltage Application. In Proceedings of the International Conference on Electrical Engineering and Photonics, San Francisco, St. Petersburg, Russia, 17–18 October 2019; pp. 5–8. [Google Scholar]

- Guan, J.; Wang, Y.; Hao, S.; Zheng, Y.; Jin, X. A Novel High Holding Voltage Dual-Direction SCR with Embedded Structure for HV ESD Protection. IEEE Electron Device Lett. 2017, 38, 1716–1719. [Google Scholar] [CrossRef]

- Huang, C.; Chiu, F.; Ou, C.; Chen, Q.; Huang, Y.; Tseng, J. ESD and Latchup Optimization of an Embedded-Floating-pMOS SCR-Incorporated BJT. IEEE Trans. Electron Devices 2016, 63, 3036–3043. [Google Scholar]

| nLDMOS | N+ (%) | Schottky (%) |

|---|---|---|

| Schottky_Drain | 0 | 100 |

| Schottky_SUR1 | 72 | 28 |

| Schottky_SUR2 | 84 | 16 |

| Schottky_SUR3 | 91 | 9 |

| Ref. DUT (L= 2 μm) | 100 | 0 |

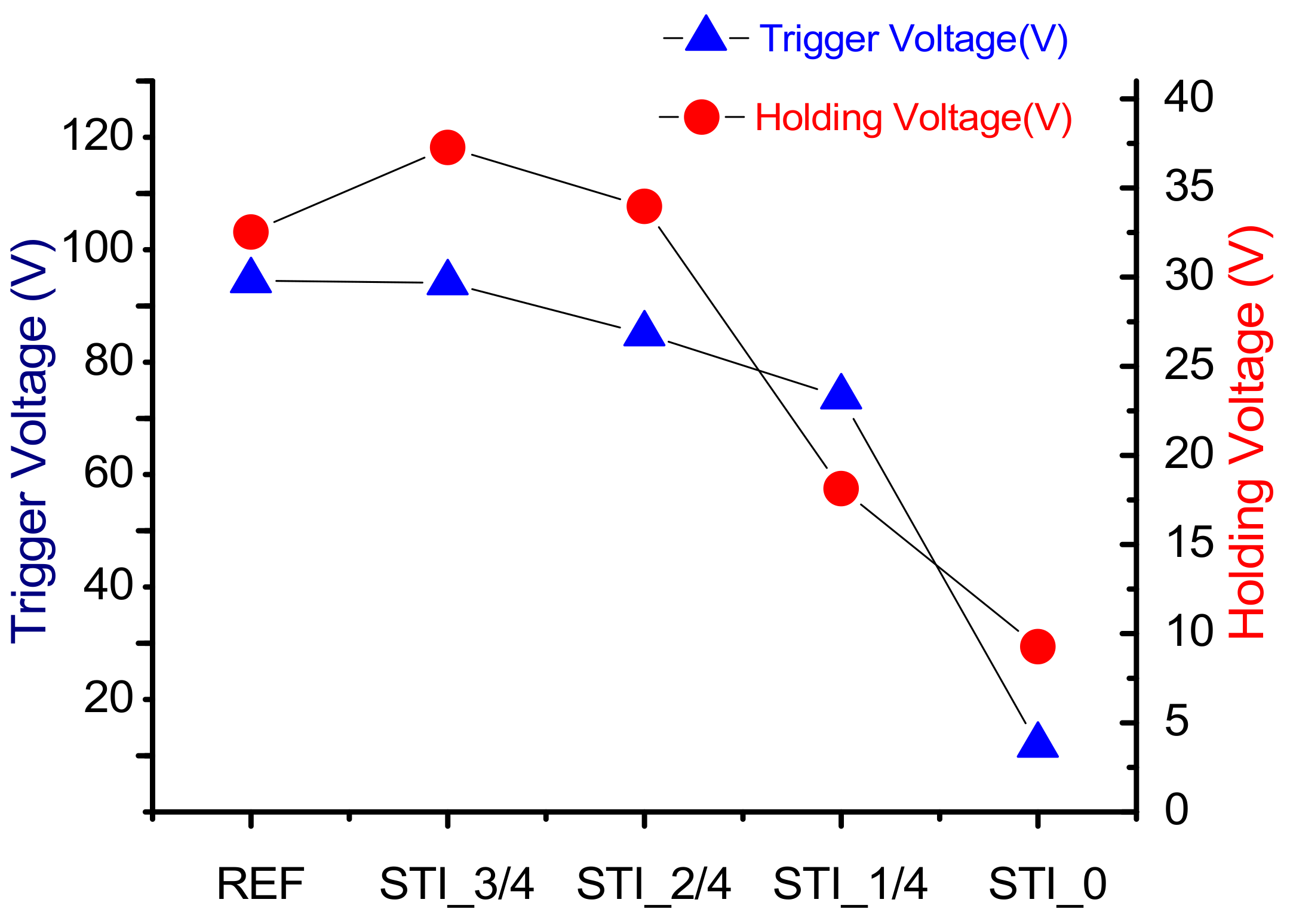

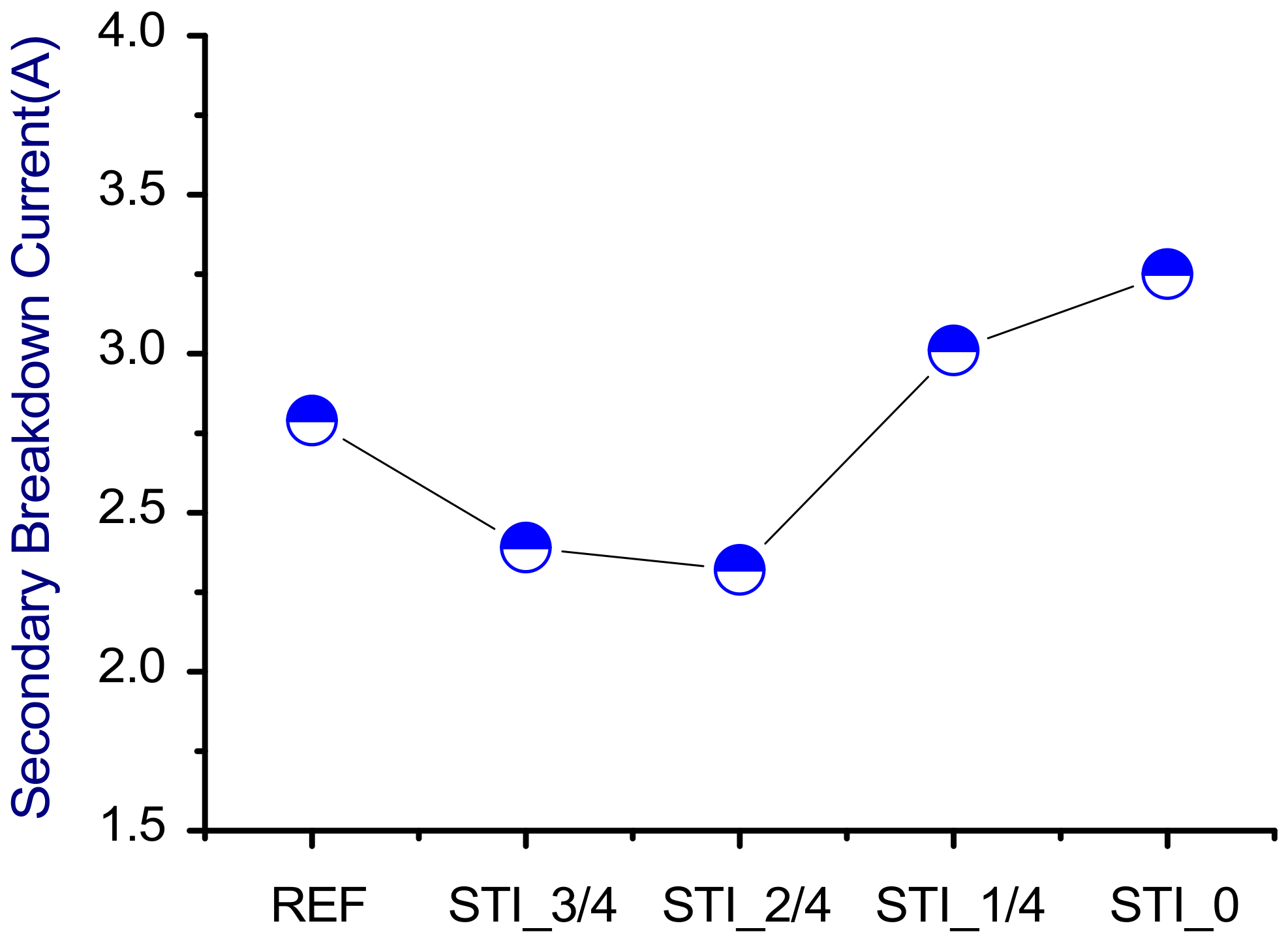

| nLDMOS | Vt1 (V) | Vh (V) | Vt1-Vh (V) | It2 (A) | Vbk (V) | FOM (μA × V/μm2) |

|---|---|---|---|---|---|---|

| Ref (L = 3 μm) | 104.47 | 32.53 | 71.94 | 2.79 | 23.52 | 2938.50 |

| STI_3/4 | 104.10 | 37.27 | 66.83 | 2.39 | 23.45 | 3045.68 |

| STI_2/4 | 95.02 | 33.97 | 61.05 | 2.32 | 23.40 | 2948.87 |

| STI_1/4 | 83.82 | 18.13 | 65.69 | 3.01 | 23.10 | 2194.21 |

| STI0 | 21.85 | 9.27 | 12.58 | 3.25 | 11.12 | 1309.59 |

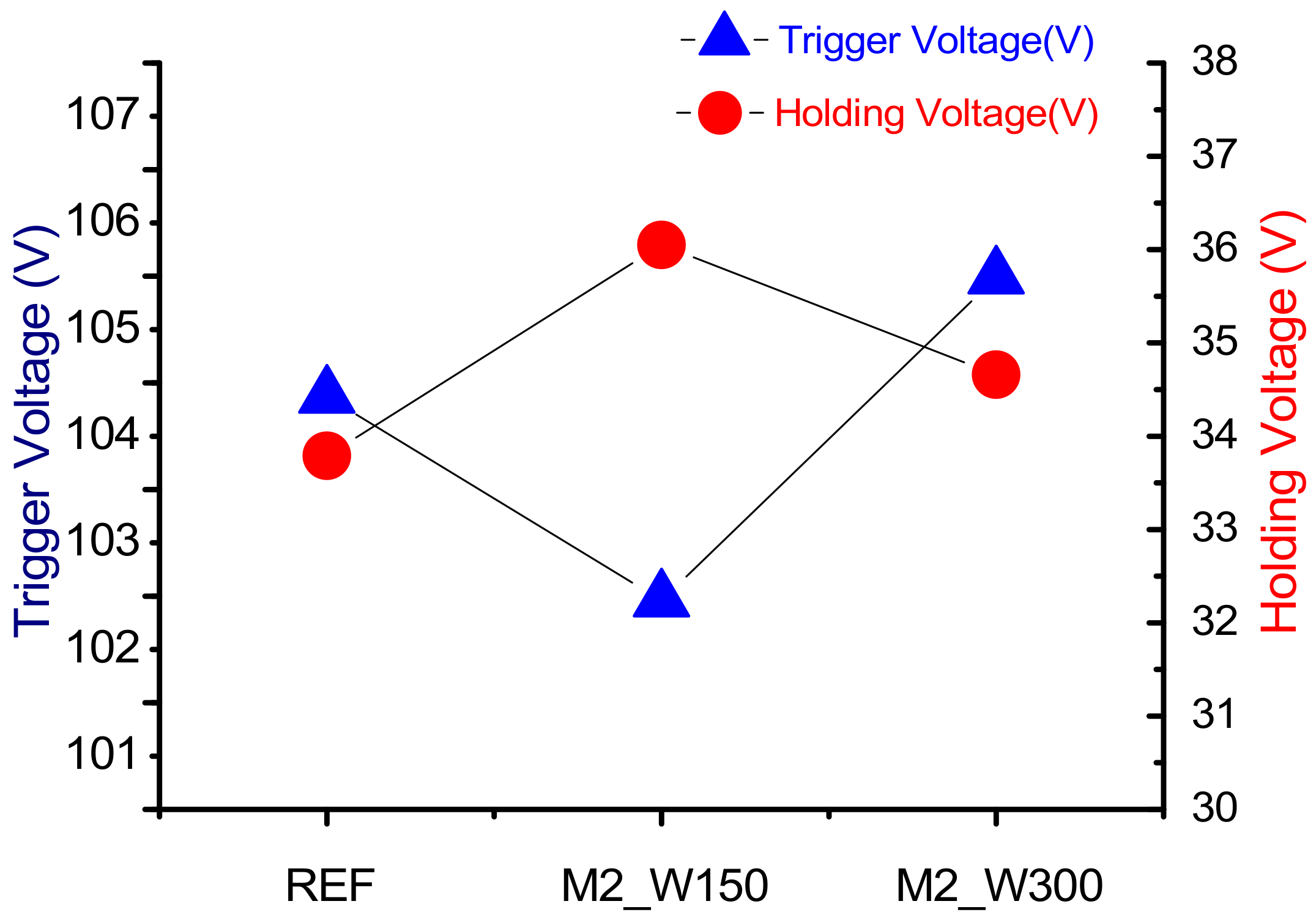

| nLDMOS | Vt1 (V) | Vh (V) | It2 (A) | FOM (μA × V/μm2) |

|---|---|---|---|---|

| Ref. (M4_W300, L = 2.75 μm) | 104.87 | 33.79 | 2.50 | 2836.95 |

| M2_W150 | 102.96 | 36.05 | 2.45 | 4691.93 |

| M2_W300 | 105.99 | 34.66 | 2.73 | 3257.45 |

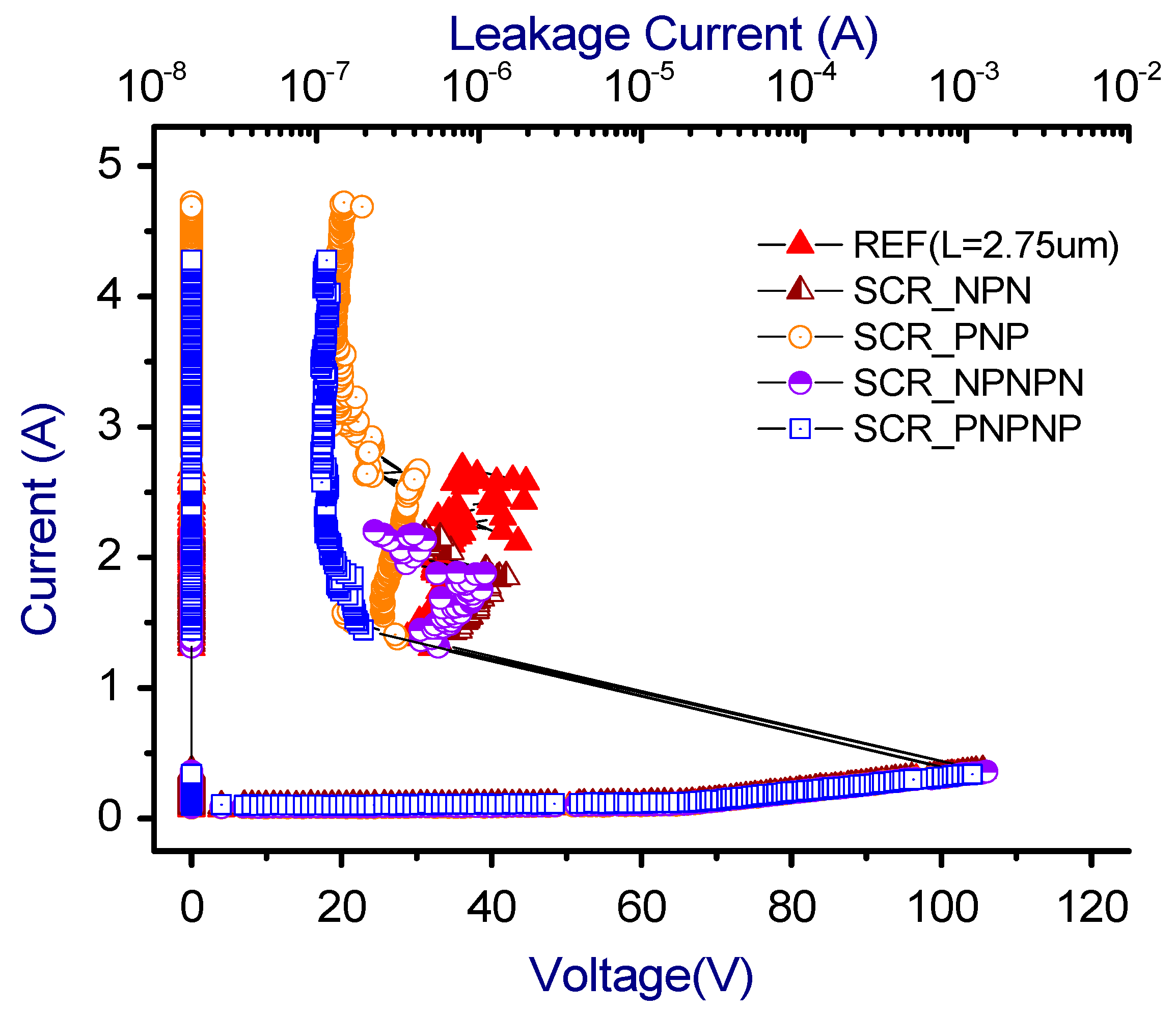

| nLDMOS | Vt1 (V) | Vh (V) | It2 (A) | FOM (μA × V/μm2) |

|---|---|---|---|---|

| REF (L = 2.75 μm) | 104.87 | 33.79 | 2.50 | 2831.83 |

| SCR_NPN | 105.38 | 34.83 | 2.22 | 2587.60 |

| SCR_PNP | 103.66 | 25.59 | 4.96 | 4255.51 |

| SCR_NPNPN | 105.93 | 32.35 | 2.22 | 2406.87 |

| SCR_PNPNP | 103.98 | 22.93 | 4.44 | 3410.64 |

| nLDMOS | Vt1 (V) | Vh (V) | It2 (A) | FOM (μA × V/μm2) |

|---|---|---|---|---|

| Schottky_Drain | 109.43 | 32.54 | 3.98 | 4341.27 |

| Schottky_SUR1 | 109.28 | 29.66 | 3.75 | 3728.36 |

| Schottky_SUR2 | 109.22 | 33.32 | 2.40 | 2680.60 |

| Schottky_SUR3 | 108.51 | 32.88 | 2.34 | 2579.07 |

| Ref. (L = 2 μm) | 107.92 | 31.27 | 2.29 | 2400.38 |

| Samples | FOM (μA × V/μm2) | Improvement |

|---|---|---|

| Method-1: STI_3/4 | 3045.68 | 3.65% ↑ |

| Method-2: M2_W150 | 4691.93 | 65.39% ↑ |

| Method-3: SCR_PNP | 4255.51 | 50.27% ↑ |

| Method-4: Schottky_Drain | 4341.27 | 80.86% ↑ |

© 2020 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Fan, S.-K.; Chen, S.-L.; Lin, P.-L.; Chen, H.-W. Layout Strengthening the ESD Performance for High-Voltage N-Channel Lateral Diffused MOSFETs. Electronics 2020, 9, 718. https://doi.org/10.3390/electronics9050718

Fan S-K, Chen S-L, Lin P-L, Chen H-W. Layout Strengthening the ESD Performance for High-Voltage N-Channel Lateral Diffused MOSFETs. Electronics. 2020; 9(5):718. https://doi.org/10.3390/electronics9050718

Chicago/Turabian StyleFan, Sheng-Kai, Shen-Li Chen, Po-Lin Lin, and Hung-Wei Chen. 2020. "Layout Strengthening the ESD Performance for High-Voltage N-Channel Lateral Diffused MOSFETs" Electronics 9, no. 5: 718. https://doi.org/10.3390/electronics9050718