Performance Analysis of Harmonic-Reduced Modified PUC Multi-Level Inverter Based on an MPC Algorithm

Abstract

:1. Introduction

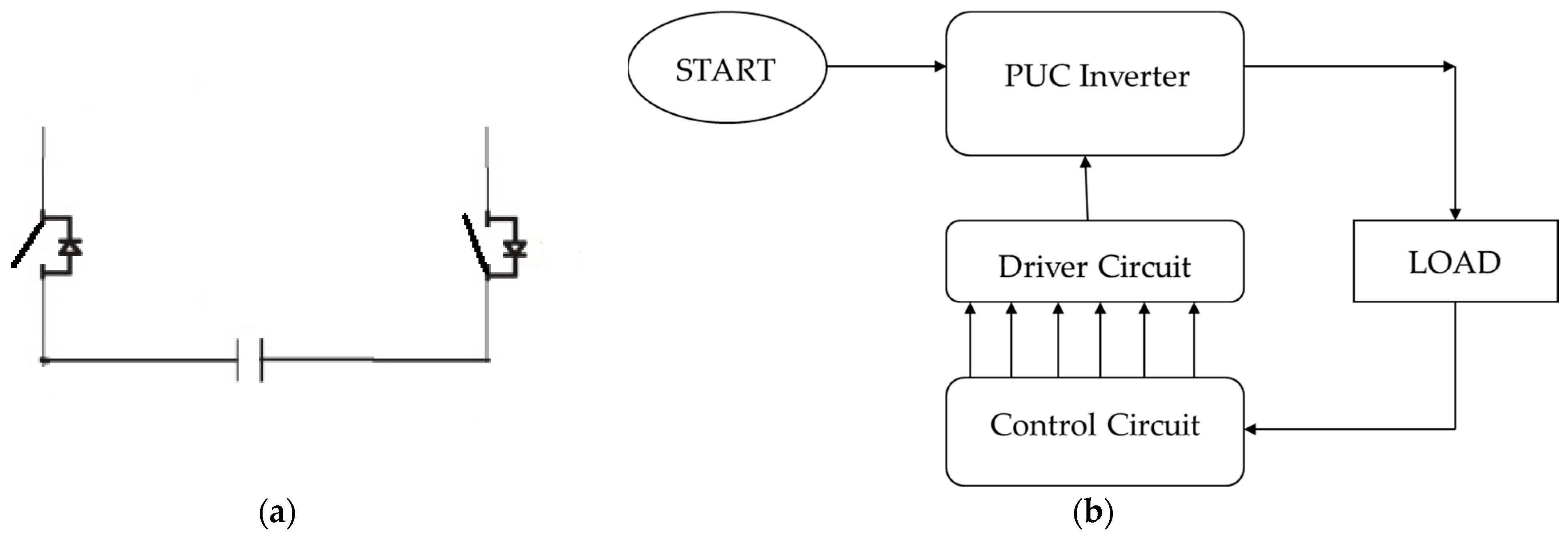

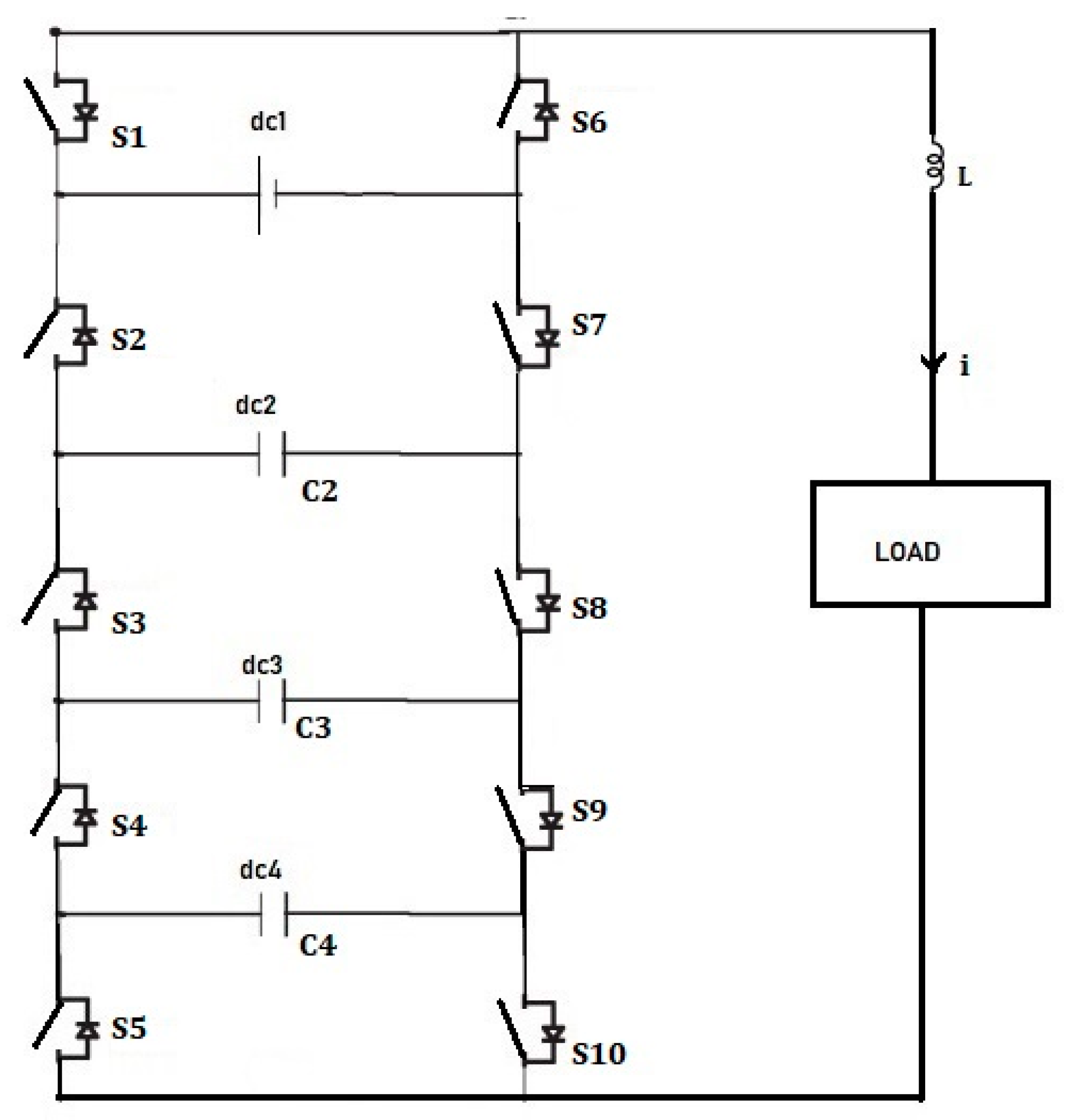

2. Materials and Methods

2.1. A 31-Level MPUC Inverter

- dc2 = 7/15(dc1);

- dc3 = 3/15(dc1);

- dc4 = 1/15(dc1).

2.2. Modulation Technique

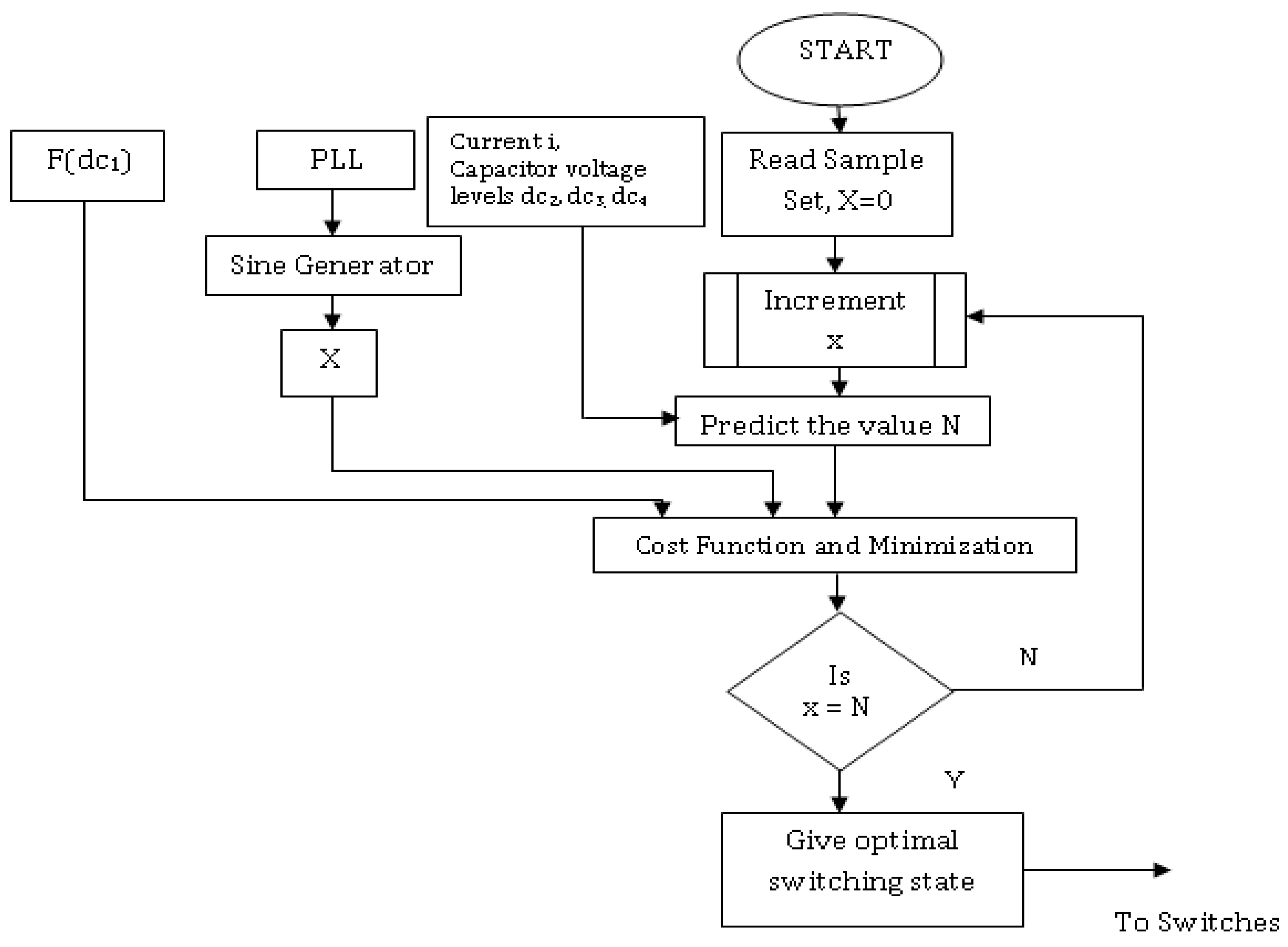

2.3. Model Predictive Controller

2.4. Model Predictive Controller for 31-Level MPUC Inverter

3. Results

3.1. Simulation Results

3.1.1. Simulation of 9-Level MLI

3.1.2. Output Voltage and Current

3.2. Simulation Result for the Proposed System

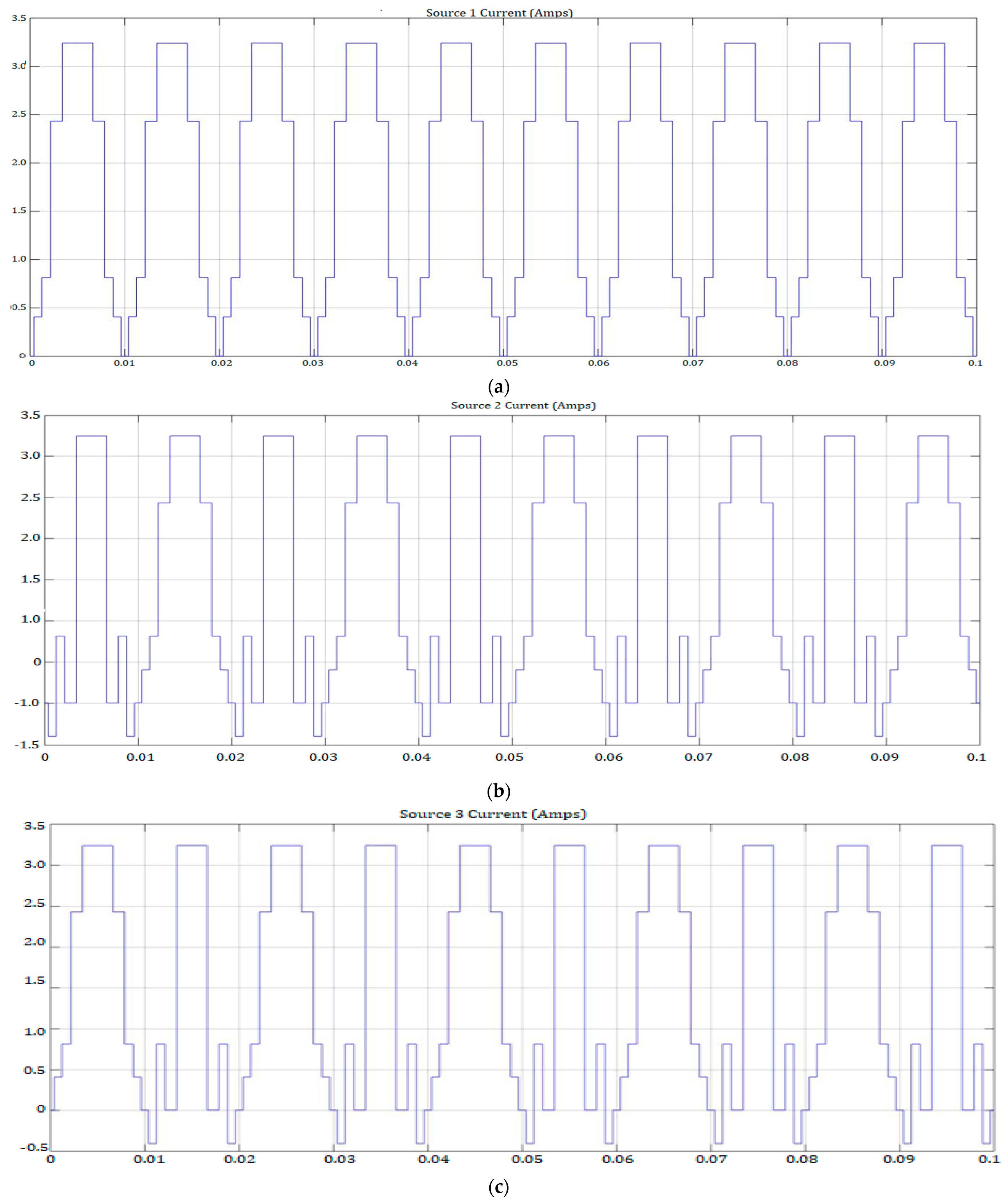

3.2.1. Input Sources

3.2.2. Output Voltage and Current

3.3. Total Harmonic Distortion Study by FFT Analysis

3.4. Hardware Results

3.4.1. Switching Pulses

3.4.2. Input Source Voltage

3.4.3. Multi-Level Inverter Output

4. Discussion

5. Conclusions

Author Contributions

Funding

Data Availability Statement

Acknowledgments

Conflicts of Interest

References

- Franquelo, L.G.; Rodriguez, J.; Leon, J.I.; Kouro, S.; Portillo, R.; Prats, M.A. The age of multilevel converters arrives. IEEE Ind. Electron. Mag. 2008, 2, 28–39. [Google Scholar] [CrossRef] [Green Version]

- Ribeiro, E.; Barbi, I. Harmonic Voltage Reduction Using a Series Active Filter Under Different Load Conditions. IEEE Trans. Power Electron. 2006, 21, 1394–1402. [Google Scholar] [CrossRef]

- Abu-Rub, H.; Holtz, J.; Rodriguez, J.; Baoming, G. Medium-Voltage Multilevel Converters—State of the Art, Challenges, and Requirements in Industrial Applications. IEEE Trans. Ind. Electron. 2010, 57, 2581–2596. [Google Scholar] [CrossRef]

- Kouro, S.; Malinowski, M.; Gopakumar, K.; Pou, J.; Franquelo, L.G.; Wu, B.; Rodriguez, J.; Perez, M.A.; Leon, J.I. Recent Advances and Industrial Applications of Multilevel Converters. IEEE Trans. Ind. Electron. 2010, 57, 2553–2580. [Google Scholar] [CrossRef]

- Ounejjar, Y.; Al-Haddad, K.; Grégoire, L.-A. Packed U Cells Multilevel Converter Topology: Theoretical Study and Experimental Validation. IEEE Trans. Ind. Electron. 2010, 58, 1294–1306. [Google Scholar] [CrossRef]

- Abu-Rub, H.; Mariusz, M.; Al-Haddad, K. Power Electronics for Renewable Energy Systems, Transportation and Industrial Applications; John Wiley & Sons: Hoboken, NJ, USA, 2014. [Google Scholar]

- Mohamad, A.S.; Mariun, N.; Sulaiman, N.; Radzi, M.A.M. A new cascaded multilevel inverter topology with minimum number of conducting switches. In Proceedings of the 2014 IEEE Innovative Smart Grid Technologies—Asia (ISGT ASIA), Kuala Lumpur, Malaysia, 20–23 May 2014; pp. 164–169. [Google Scholar] [CrossRef]

- Vahedi, H.; Kanaan, H.Y.; Al-Haddad, K. PUC converter review: Topology, control and applications. In Proceedings of the IECON 2015—41st Annual Conference of the IEEE Industrial Electronics Society, Yokohama, Japan, 9–12 November 2015; pp. 004334–004339. [Google Scholar] [CrossRef]

- Kumar, P.R.; Kaarthik, R.S.; Gopakumar, K.; Leon, J.I.; Franquelo, L.G. Seventeen-Level Inverter Formed by Cascading Flying Capacitor and Floating Capacitor H-Bridges. IEEE Trans. Power Electron. 2015, 30, 3471–3478. [Google Scholar] [CrossRef]

- Vazquez, S.; Rodriguez, J.; Rivera, M.; Franquelo, L.G.; Norambuena, M. Model Predictive Control for Power Converters and Drives: Advances and Trends. IEEE Trans. Ind. Electron. 2017, 64, 935–947. [Google Scholar] [CrossRef] [Green Version]

- Vahedi, H.; Labbé, P.-A.; Al-Haddad, K. Sensor-Less Five-Level Packed U-Cell (PUC5) Inverter Operating in Stand-Alone and Grid-Connected Modes. IEEE Trans. Ind. Inform. 2016, 12, 361–370. [Google Scholar] [CrossRef]

- Kumar, R.; Singh, B. Single Stage Solar PV Fed Brushless DC Motor Driven Water Pump. IEEE J. Emerg. Sel. Top. Power Electron. 2017, 5, 1377–1385. [Google Scholar] [CrossRef]

- Vahedi, H.; Al-Haddad, K. Method and System for Operating a Multilevel Inverter. U.S. Patent US9923484B2, 20 March 2018. [Google Scholar]

- Narendrababu, A.; Yalla, N.; Agarwal, P. A modified T-type single phase five-level inverter with reduced switch voltage stress. In Proceedings of the 2018 International Conference on Power, Instrumentation, Control and Computing (PICC), Thrissur, India, 18–20 January 2018; pp. 1–5. [Google Scholar] [CrossRef]

- Sulake, N.R.; Venkata, A.K.D.; Choppavarapu, S.B. FPGA Implementation of a Three-Level Boost Converter-fed Seven-Level DC-Link Cascade H-Bridge inverter for Photovoltaic Applications. Electronics 2018, 7, 282. [Google Scholar] [CrossRef] [Green Version]

- Kang, J.-W.; Hyun, S.-W.; Ha, J.-O.; Won, C.-Y. Improved Neutral-Point Voltage-Shifting Strategy for Power Balancing in Cascaded NPC/H-Bridge Inverter. Electronics 2018, 7, 167. [Google Scholar] [CrossRef] [Green Version]

- Lee, S.; Kim, J. Optimized Modeling and Control Strategy of the Single-Phase Photovoltaic Grid-Connected Cascaded H-bridge Multilevel Inverter. Electronics 2018, 7, 207. [Google Scholar] [CrossRef] [Green Version]

- Hu, J.; Shan, Y.; Guerrero, J.M.; Ioinovici, A.; Chan, K.W.; Rodriguez, J. Model predictive control of microgrids—An overview. Renew. Sustain. Energy Rev. 2021, 136, 110422. [Google Scholar] [CrossRef]

- Shyam, D.; Premkumar, K.; Sivamani, D.; Nazarali, A.; Narendiran, S.; Ramkumar, R. PUC Optimal Switching Strategies for Renewable Applications in Single Phase Inverter. In Proceedings of the IEEE 9th Uttar Pradesh Section International Conference on Electrical, Electronics and Computer Engineering (UPCON), Prayagraj, India, 2–4 December 2022; pp. 1–5. [Google Scholar] [CrossRef]

- Iqbal, H.; Tariq, M.; Sarfraz, M.; Anees, M.A.; Alhosaini, W.; Sarwar, A. Model predictive control of Packed U-Cell inverter for microgrid applications. Energy Rep. 2022, 8, 813–830. [Google Scholar] [CrossRef]

- Abarzadeh, M.; Peyghami, S.; Al-Haddad, K.; Weise, N.; Chang, L.; Blaabjerg, F. Reliability and Performance Improvement of PUC Converter Using a New Single-Carrier Sensor less PWM Method with Pseudo Reference Functions. Electrical and Computer Engineering Faculty Research and Publications. (681) 2021. Available online: https://epublications.marquette.edu/electric_fac/681 (accessed on 1 March 2023).

- Phukan, H.; Debela, T.; Singh, J. A modified seven-level cross-connected PUC boost multilevel inverter with reduced cost factor and device count. Int. J. Emerg. Electr. Power Syst. 2022. [Google Scholar] [CrossRef]

- Upreti, S.; Singh, B.; Kumar, N. Harmonics Minimization in PUC Type Solar Multilevel Converter with Multicarrier Switching Schemes. IETE J. Res. 2022. [Google Scholar] [CrossRef]

- Junior, S.C.S.; Jacobina, C.; Fabricio, E.L.L. A Single-Phase 35-levels Cascaded PUC Multilevel Inverter Fed by a Single DC-Source. In Proceedings of the IEEE Energy Conversion Congress and Exposition (ECCE), Vancouver, BC, Canada, 10–14 October 2021; pp. 2467–2474. [Google Scholar] [CrossRef]

- Muthukuri, N.K.; Mopidevi, S. Optimal Controller Design of PUC-15 MLI Topology for Smart Grid Applications with Reduced Power Components. In Proceedings of the International Conference on Smart Technologies and Systems for Next Generation Computing (ICSTSN), Virtual, 25–26 March 2022; pp. 1–4. [Google Scholar] [CrossRef]

- Owona, J.L.; Fendji, M.D.; Effa, J.Y.; Fankem, E.D.K. Control of Reduced Switches Count and Classical Multilevel Inverters: A Comparison. E3S Web Conf. 2022, 354, 02002. [Google Scholar] [CrossRef]

- Venkedesh, R.; Kumar, A.; Renukadevi, G. Multilevel Inverter Design with Reduced Switches & THD Using Fuzzy Logic Controller. Int. J. Electr. Electron. Eng. 2022, 9, 1–21. [Google Scholar] [CrossRef]

- Bellah, F.A.; Abouloifa, A.; Echalih, S.; Hekss, Z.; Naftahi, K.; Lachkar, I. Control Design of a Seven-Level Packed U Cell Inverter. IFAC-PapersOnLine 2022, 55, 677–682. [Google Scholar] [CrossRef]

- Khan, F.A.; Shees, M.M.; Alsharekh, M.F.; Alyahya, S.; Saleem, F.; Baghel, V.; Sarwar, A.; Islam, M.; Khan, S. Open-Circuit Fault Detection in a Multilevel Inverter Using Sub-Band Wavelet Energy. Electronics 2021, 11, 123. [Google Scholar] [CrossRef]

- Kumar, A.; Jain, S. Predictive Switching Control for Multilevel Inverter using CNN-LSTM for Voltage Regulation. ADBU J. Eng. Technol. (AJET) 2022, 11, 0110203197. [Google Scholar]

- Mukundan, C.M.N.; Jayaprakash, P.; Subramaniam, U.; Almakhles, D.J. Binary Hybrid Multilevel Inverter-Based Grid Integrated Solar Energy Conversion System with Damped SOGI Control. IEEE Access 2020, 8, 37214–37228. [Google Scholar] [CrossRef]

- Salem, M.; Richelli, A.; Yahya, K.; Hamidi, M.N.; Ang, T.-Z.; Alhamrouni, I. A Comprehensive Review on Multilevel Inverters for Grid-Tied System Applications. Energies 2022, 15, 6315. [Google Scholar] [CrossRef]

- Komurcugil, H.; Bayhan, S.; Guler, N.; Abu-Rub, H.; Bagheri, F. A simplified sliding-mode control method for multi-level transformerless DVR. IET Power Electron. 2022, 15, 764–774. [Google Scholar] [CrossRef]

- Azeem, A.; Ansari, M.K.; Tariq, M.; Sarwar, A.; Ashraf, I. Design and Modeling of Solar Photovoltaic System using Seven-Level Packed U-Cell (PUC) Multilevel Inverter and Zeta Converterfor Off-Grid Application in India. Electrica 2019, 19, 101–112. [Google Scholar] [CrossRef]

- Jeevanantham, Y.A.; Srinath, S. ANN Based Reduced Switch Multilevel Inverter in UPQC for Power Quality Improvement. Intell. Autom. Soft Comput. 2022, 33, 909–921. [Google Scholar] [CrossRef]

- Fahad, M.; Tariq, M.; Faizan, M.; Ali, A.; Sarwar, A.; Tafti, H.D.; Ahmad, S.; Mohamed, A.S.N. A Dual Source Switched-Capacitor Multilevel Inverter with Reduced Device Count. Electronics 2021, 11, 67. [Google Scholar] [CrossRef]

- Abari, I.; Hamouda, M.; Sleiman, M.; Slama, J.B.H.; Kanaan, H.Y.; Al-Haddad, K. Open-Circuit Fault Detection and Isolation Method for Five-Level PUC Inverter Based on the Wavelet Packet Transform of the Radiated Magnetic Field. IEEE Trans. Instrum. Meas. 2022, 71, 1–11. [Google Scholar] [CrossRef]

- Kaymanesh, A.; Chandra, A. Computationally Efficient MPC Technique for PUC-Based Inverters Without Weighting Factors. In Proceedings of the 2021 IEEE Industry Applications Society Annual Meeting (IAS), Vancouver, BC, Canada, 10–14 October 2021; pp. 1–5. [Google Scholar] [CrossRef]

- Mohamed-Seghir, M.; Krama, A.; Refaat, S.S.; Trabelsi, M.; Abu-Rub, H. Artificial Intelligence-Based Weighting Factor Autotuning for Model Predictive Control of Grid-Tied Packed U-Cell Inverter. Energies 2020, 13, 3107. [Google Scholar] [CrossRef]

- Khawaja, R.; Sebaaly, F.; Kanaan, H.Y. Design of a 7-Level Single-Stage/Phase PUC Grid-Connected PV Inverter with FS-MPC Control. In Proceedings of the 2020 IEEE International Conference on Industrial Technology (ICIT), Buenos Aires, Argentina, 26–28 February 2020; pp. 751–756. [Google Scholar] [CrossRef]

- Sahli, A.; Krim, F.; Laib, A.; Talbi, B. Energy management and power quality enhancement in grid-tied single-phase PV system using modified PUC converter. IET Renew. Power Gener. 2019, 13, 2512–2521. [Google Scholar] [CrossRef]

- Trabelsi, M.; Ghanes, M.; Mansouri, M.; Bayhan, S.; Abu-Rub, H. An original observer design for reduced sensor control of Packed U Cells based renewable energy system. Int. J. Hydrogen Energy 2017, 42, 17910–17916. [Google Scholar] [CrossRef]

| Inverter topology | Number of power switches | Number of capacitors | Number of dc sources |

| Manufacturer | Formax Electronics pvt ltd | Asoka Electronics | Generic Electronics |

| Component Description | 15 V, 1 A MOSFET switches | 1000uF/100V Electrolytic Capacitor | KBPC1510 15 A 1000 V Bridge Rectifier |

| Packed U Cell | 8 | 2 | 1 |

| Cascaded H Bridge | 16 | 0 | 4 |

| Flying Capacitor | 16 | 36 | 1 |

| ±(-dc4) | ±(-dc3 + dc4) | ±(-dc3) | ±(-dc2 + dc3) | ±(-dc2 + dc3-dc4) |

| ±(-dc2 + dc4) | ±(-dc2) | ±(-dc1 + dc2) | ±(-dc1 + dc2-dc4) | ±(-dc1 + dc2-dc3 + dc4) |

| ±(-dc1 + dc2-dc3) | ±(-dc1 + dc3) | ±(-dc1 + dc3-dc4) | ±(-dc1 + dc4) | ±(-dc1) and zero |

| Input Current (Peak) in Amps | Output (Peak Values) | |||

|---|---|---|---|---|

| Source 1 | Source 2 | Source 3 | Voltage in V | Current in I |

| 3.24 | 3.24 | 3.24 | 325 | 3.24 |

| Input Current (Peak) in Amps | Output (Peak Values) | ||||

|---|---|---|---|---|---|

| Source 1 | Source 2 | Source 3 | Source 4 | Voltage in V | Current in I |

| 3.24 | 1.5 | 2.3 | 2.8 | 325 | 3.24 |

| Si. No. | Modulation Index | 9-Level THD% | 31-Level THD% |

|---|---|---|---|

| 1 | 0.4 | 28.51% | 6.37% |

| 2 | 0.6 | 16.71% | 4.31% |

| 3 | 0.8 | 11.54% | 3.27% |

| 4 | 1.0 | 9.36% | 2.61% |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2023 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Krishnamoorthy, U.; Pitchaikani, U.; Rusu, E.; Fayek, H.H. Performance Analysis of Harmonic-Reduced Modified PUC Multi-Level Inverter Based on an MPC Algorithm. Inventions 2023, 8, 90. https://doi.org/10.3390/inventions8040090

Krishnamoorthy U, Pitchaikani U, Rusu E, Fayek HH. Performance Analysis of Harmonic-Reduced Modified PUC Multi-Level Inverter Based on an MPC Algorithm. Inventions. 2023; 8(4):90. https://doi.org/10.3390/inventions8040090

Chicago/Turabian StyleKrishnamoorthy, Umapathi, Ushaa Pitchaikani, Eugen Rusu, and Hady H. Fayek. 2023. "Performance Analysis of Harmonic-Reduced Modified PUC Multi-Level Inverter Based on an MPC Algorithm" Inventions 8, no. 4: 90. https://doi.org/10.3390/inventions8040090