Research by Fondazione Bruno Kessler on Strategies to Improve the Yield in Plasma Focused Ion Beam Circuit Editing †

Abstract

:1. Introduction

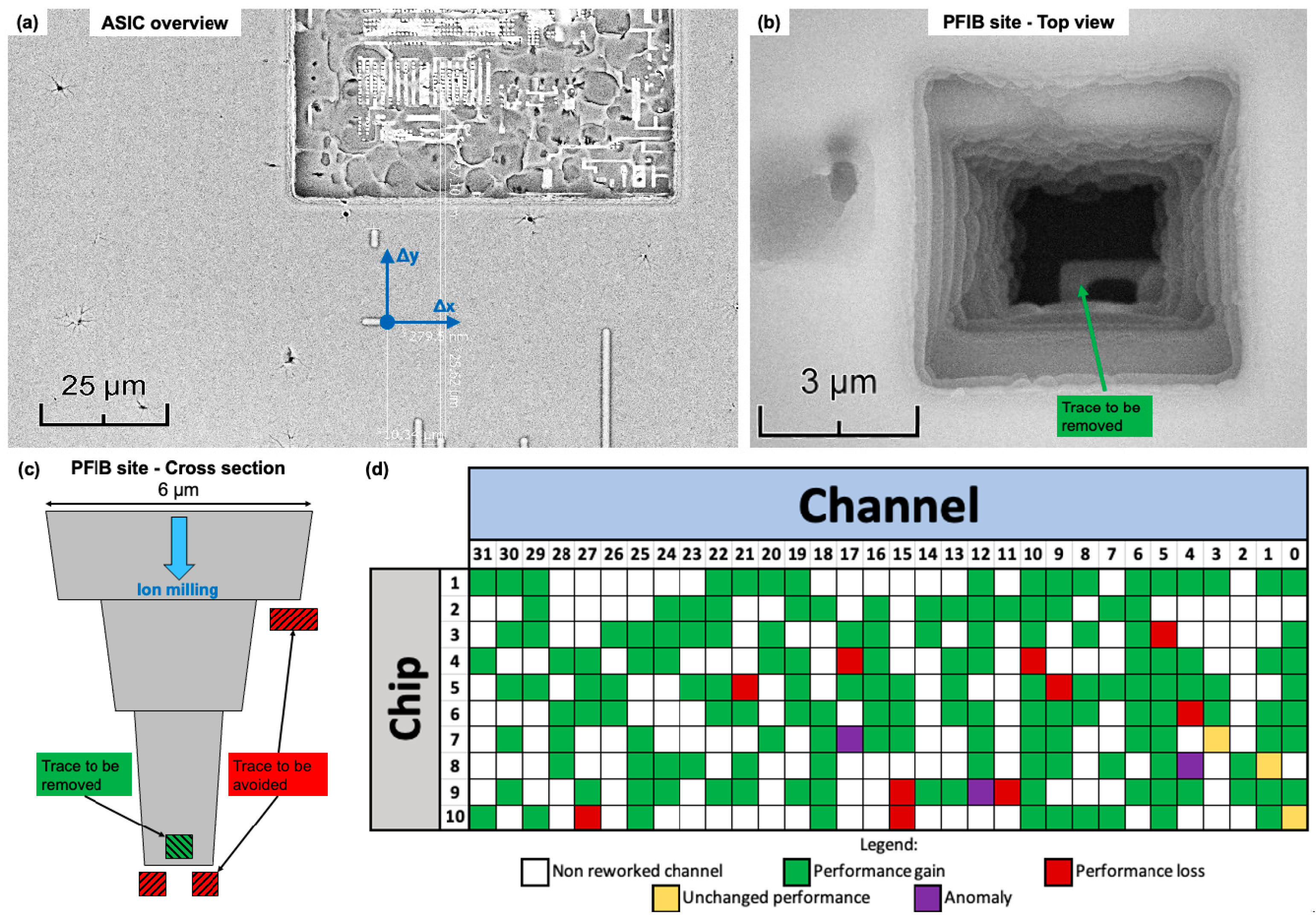

2. Materials and Methods

3. Discussion

Author Contributions

Funding

Institutional Review Board Statement

Informed Consent Statement

Data Availability Statement

Conflicts of Interest

References

- Liu, T.C.; Chen, C.; Liu, S.T.; Chang, M.L.; Lin, J. Innovative methodologies of circuit edit by focused ion beam (FIB) on wafer-level chip- scale-package (WLCSP) devices. J. Mater. Sci. Mater. Electron. 2011, 22, 1536–1541. [Google Scholar] [CrossRef]

- Chen, L.; Longoria, A.; Cha, G.; Tovar, G.; Ramirez, E.; Fang, P.; Liu, Y.; Torres, A.; Alcantara, M.; Penley, C. Application of Plasma Focused Ion Beam Technique in Advanced Technology Nodes. In International Symposium for Testing and Failure Analysis; ASM International: Almere, The Netherlands, 2022. [Google Scholar]

- Novel, D.; Demenev, E.; Ferrario, L. PFIB capabilities and potential for circuit edit and 3D integration at FBK. In Proceedings of the 48th International conference on Micro and Nano Engineering—Eurosensors (MNE-ES), Leuven, Belgium, 19–23 September 2022. [Google Scholar]

- Gaiardo, A.; Novel, D.; Scattolo, E.; Crivellari, M.; Picciotto, A.; Ficorella, F.; Iacob, E.; Bucciarelli, A.; Petti, L.; Lugli, P.; et al. Optimization of a Low-Power Chemoresistive Gas Sensor: Predictive Thermal Modelling and Mechanical Failure Analysis. Sensors 2021, 21, 783. [Google Scholar] [CrossRef] [PubMed]

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2024 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Novel, D.; Demenev, E.; Ferrario, L. Research by Fondazione Bruno Kessler on Strategies to Improve the Yield in Plasma Focused Ion Beam Circuit Editing. Proceedings 2024, 97, 59. https://doi.org/10.3390/proceedings2024097059

Novel D, Demenev E, Ferrario L. Research by Fondazione Bruno Kessler on Strategies to Improve the Yield in Plasma Focused Ion Beam Circuit Editing. Proceedings. 2024; 97(1):59. https://doi.org/10.3390/proceedings2024097059

Chicago/Turabian StyleNovel, David, Evgeny Demenev, and Lorenza Ferrario. 2024. "Research by Fondazione Bruno Kessler on Strategies to Improve the Yield in Plasma Focused Ion Beam Circuit Editing" Proceedings 97, no. 1: 59. https://doi.org/10.3390/proceedings2024097059