Electronic Implementation of a Deterministic Small-World Network: Synchronization and Communication

Abstract

1. Introduction

2. Brief Review on Synchronization of Complex Networks

2.1. Synchronization of Complex Network

2.2. Synchronization Conditions

3. Generator Algorithm of DSWN

4. Synchronization of a DSWN with Chaotic Chua’s Circuits as Node

4.1. Chaotic Chua’s Circuit

4.2. Synchronization of 24 Chaotic Chua’s Circuits in a DSWN

Numerical Simulations of DSWN with 24 Chaotic Chua’s Circuits

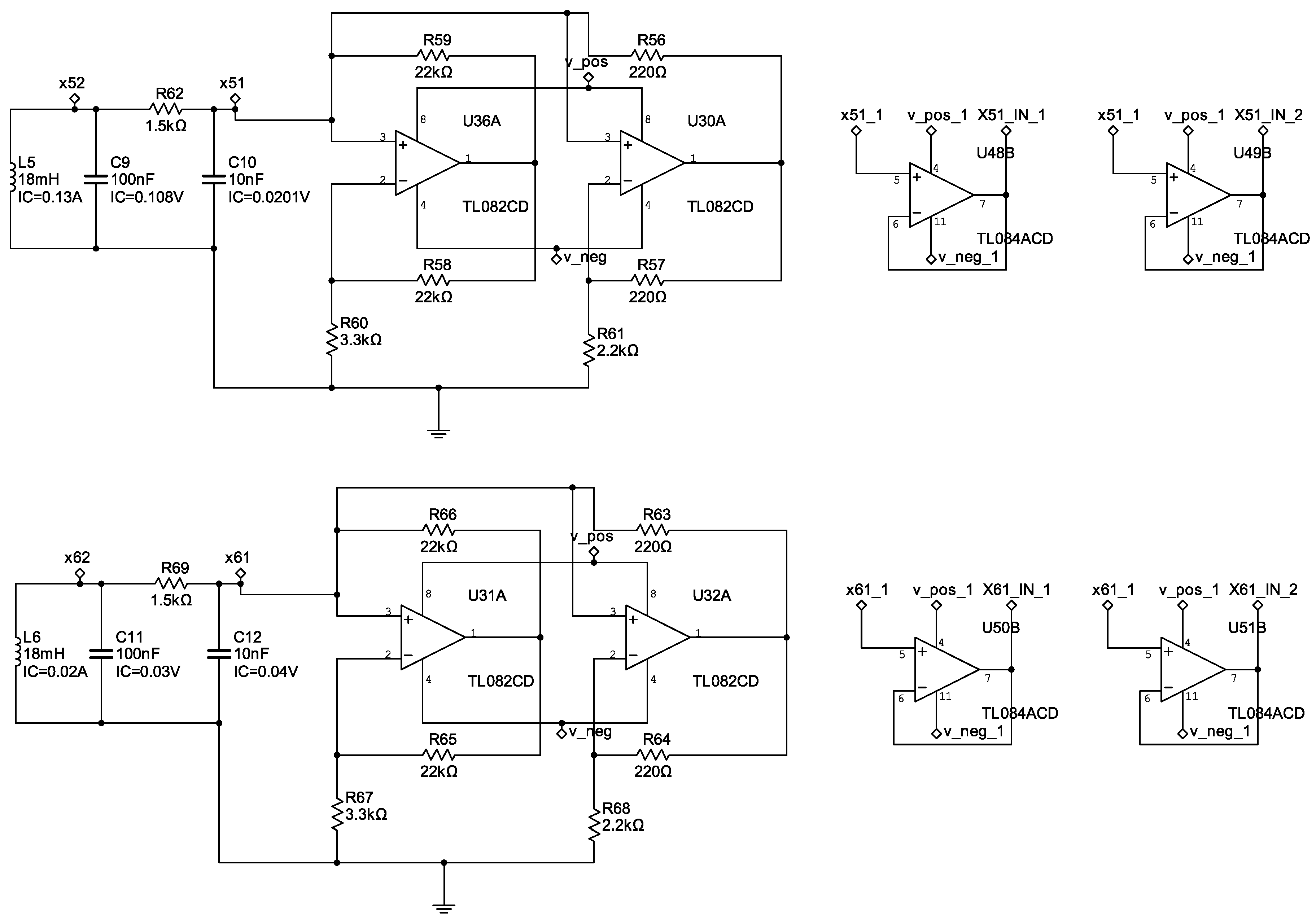

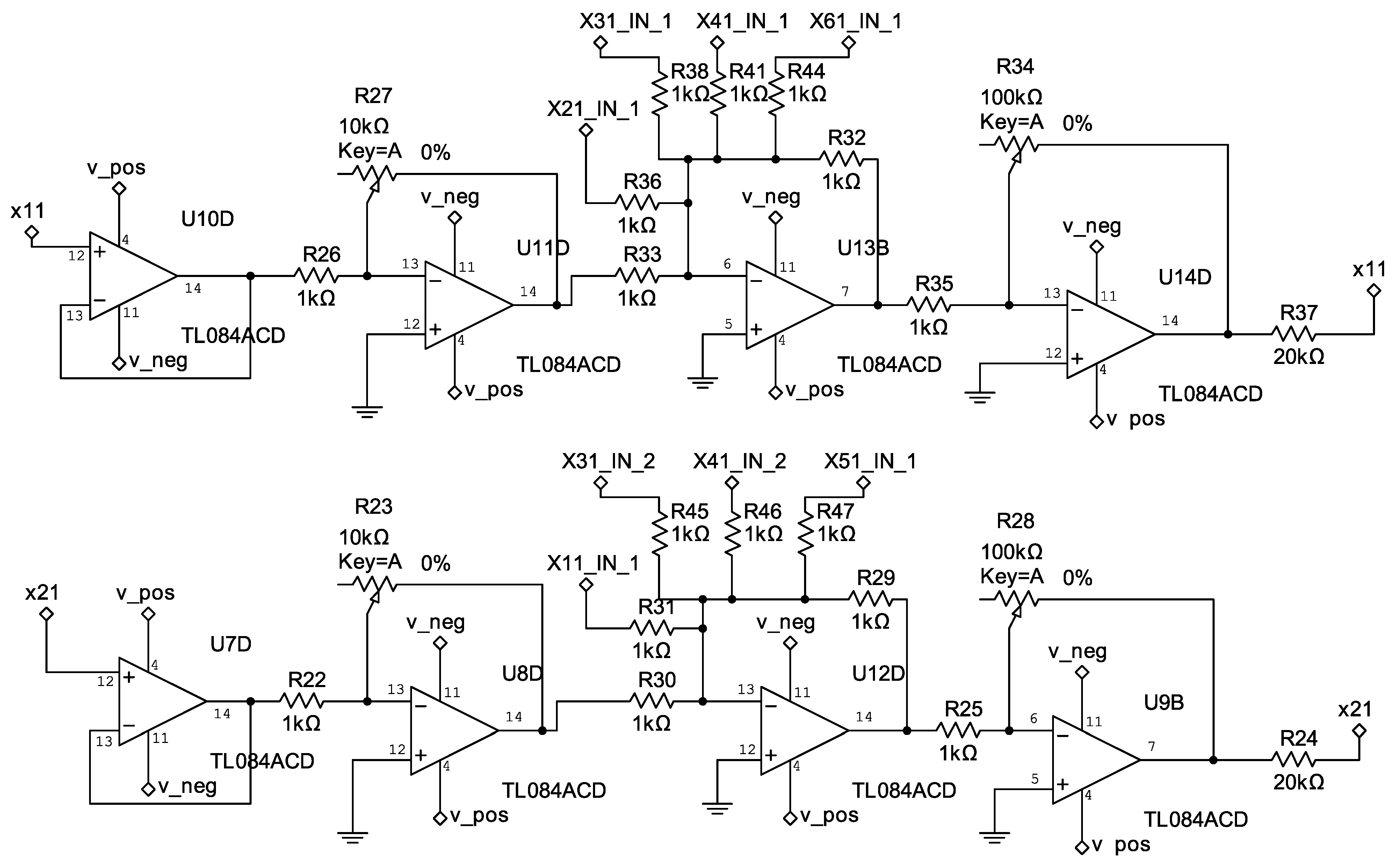

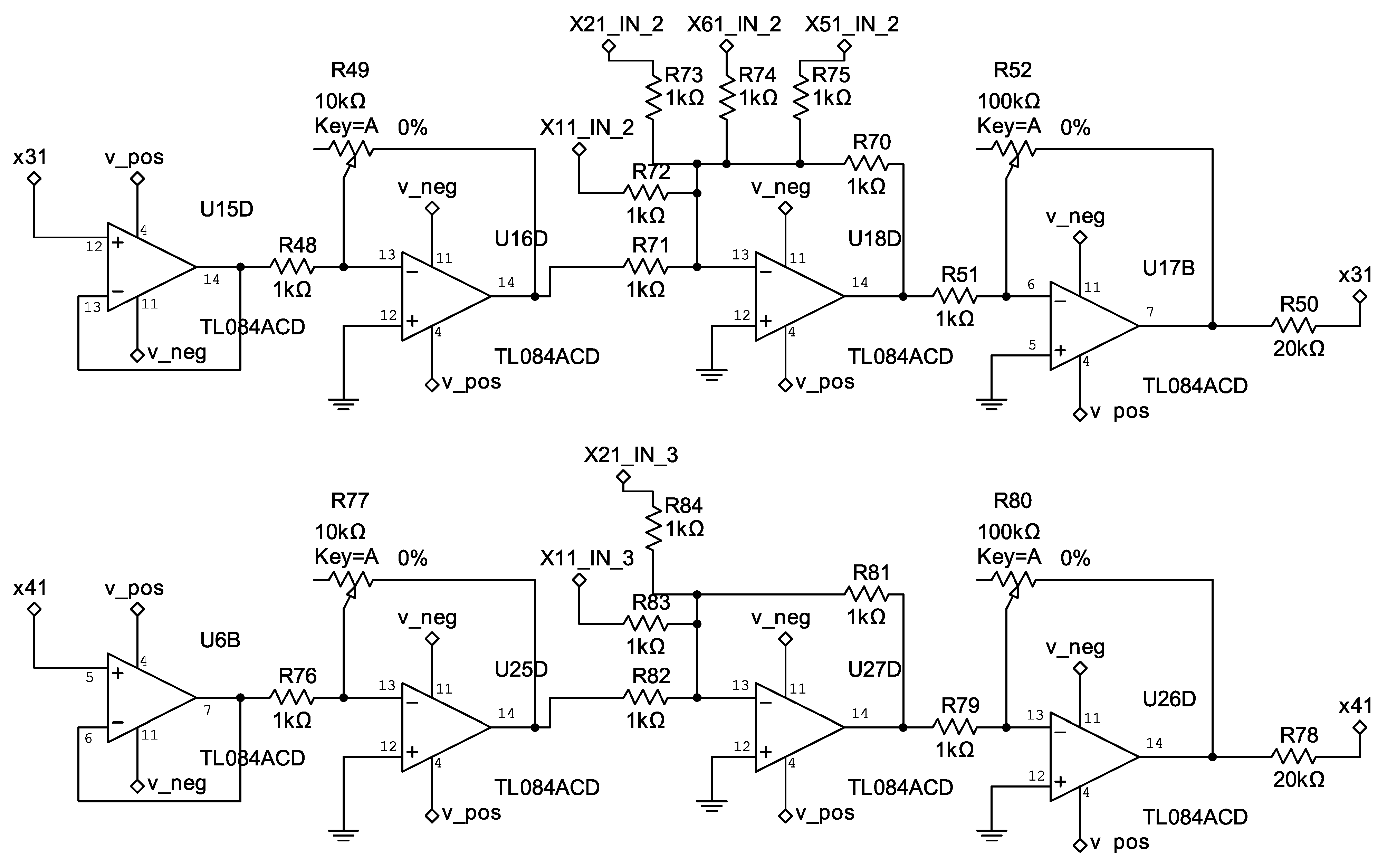

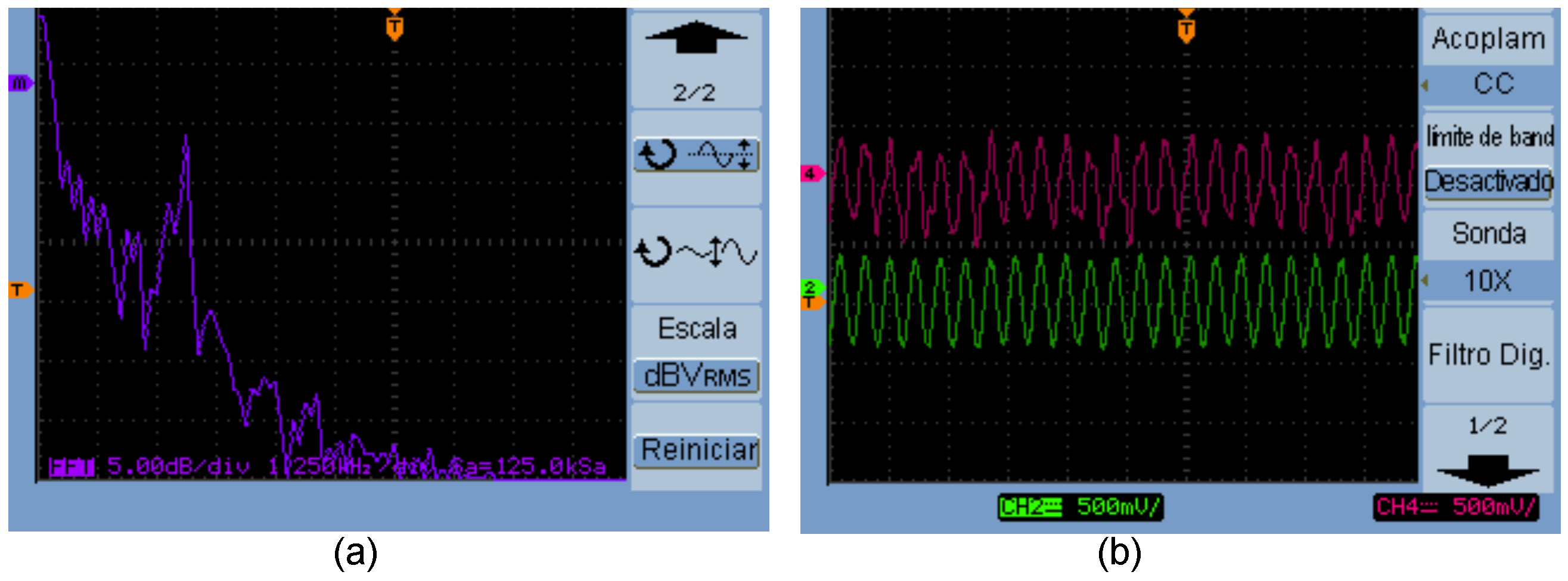

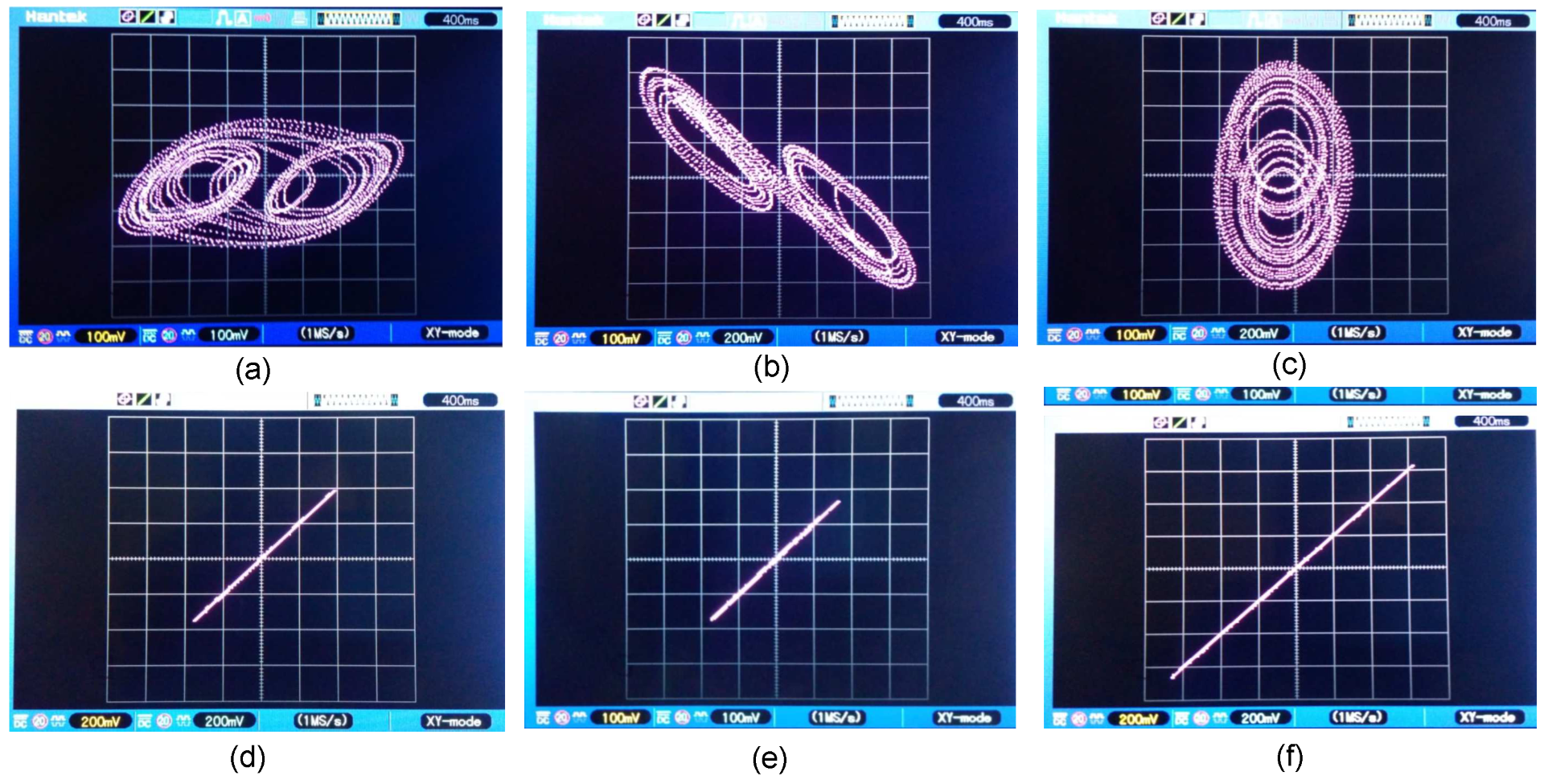

5. Analog Synchronization of Six Chua’s Circuits in a DSWN

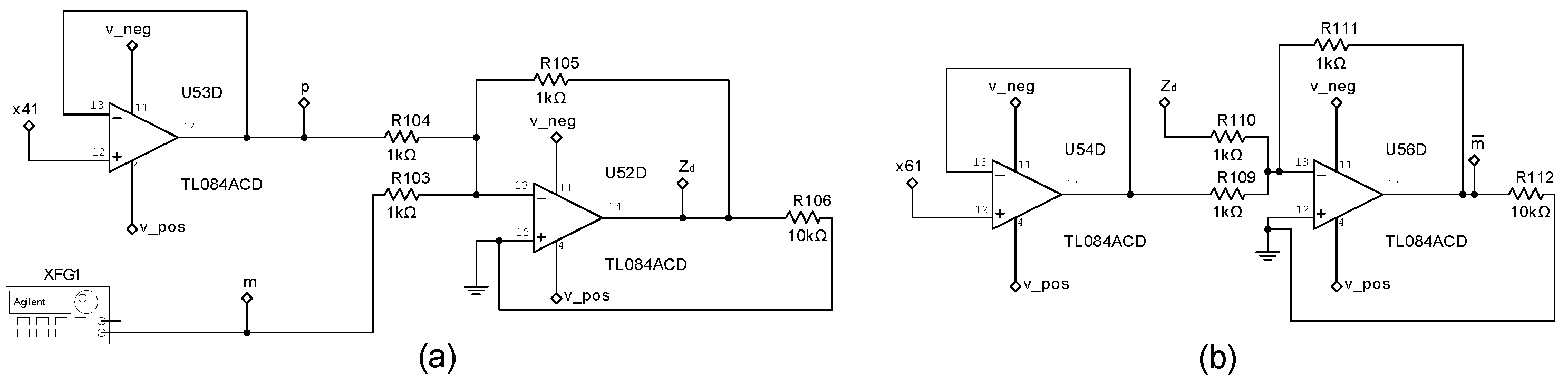

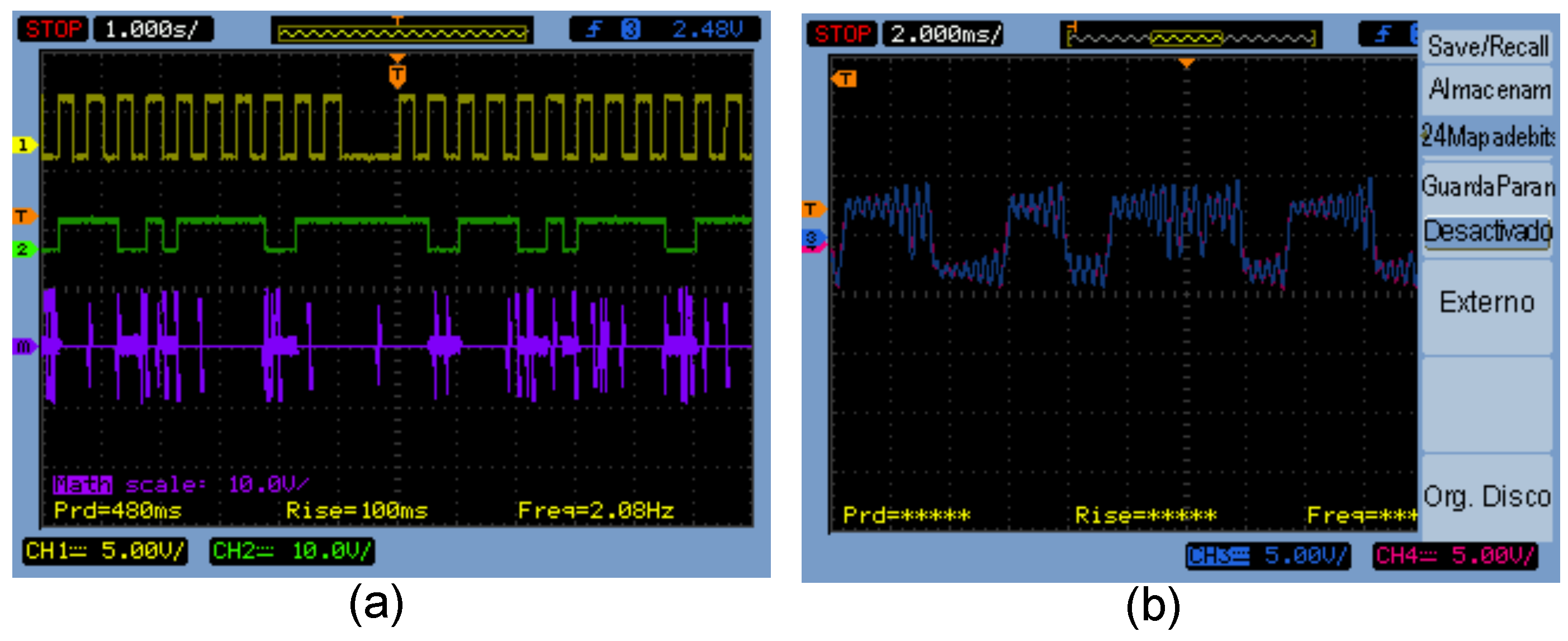

5.1. Experimental Application for analog Encryption in a DSWN

5.2. Experimental Application for Bit Encryption in a DSWN

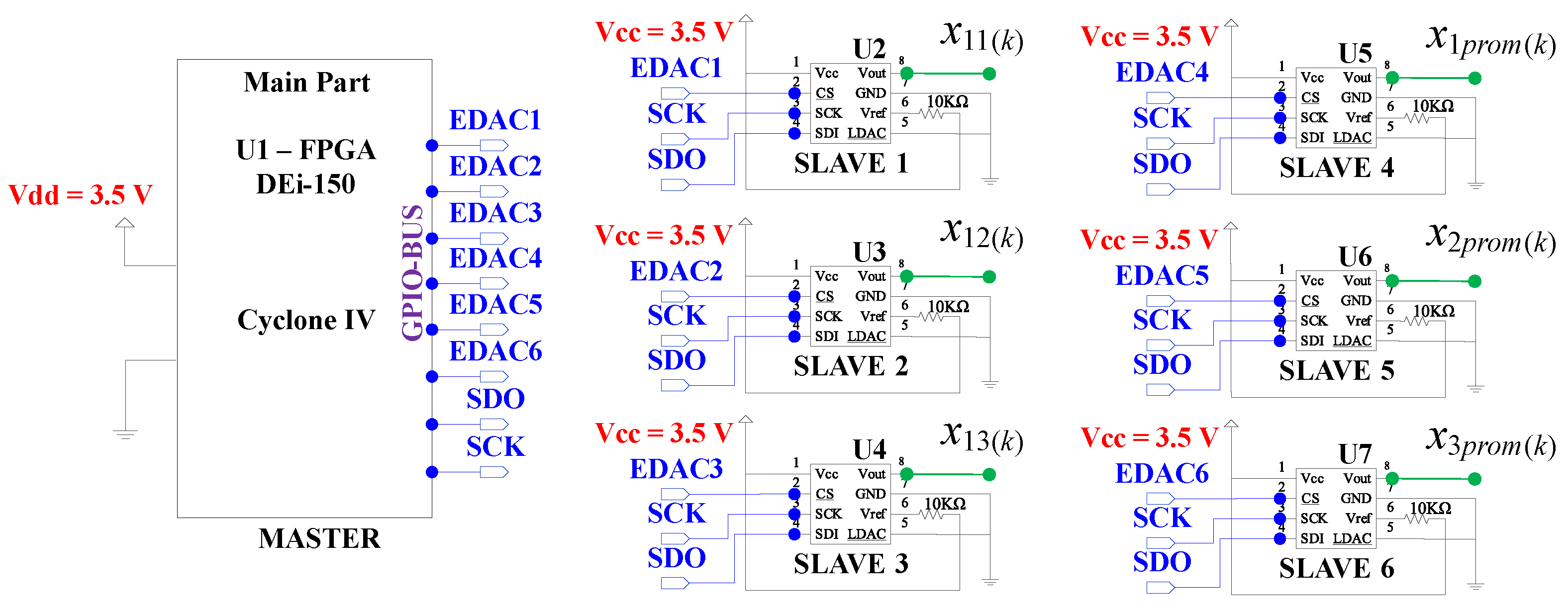

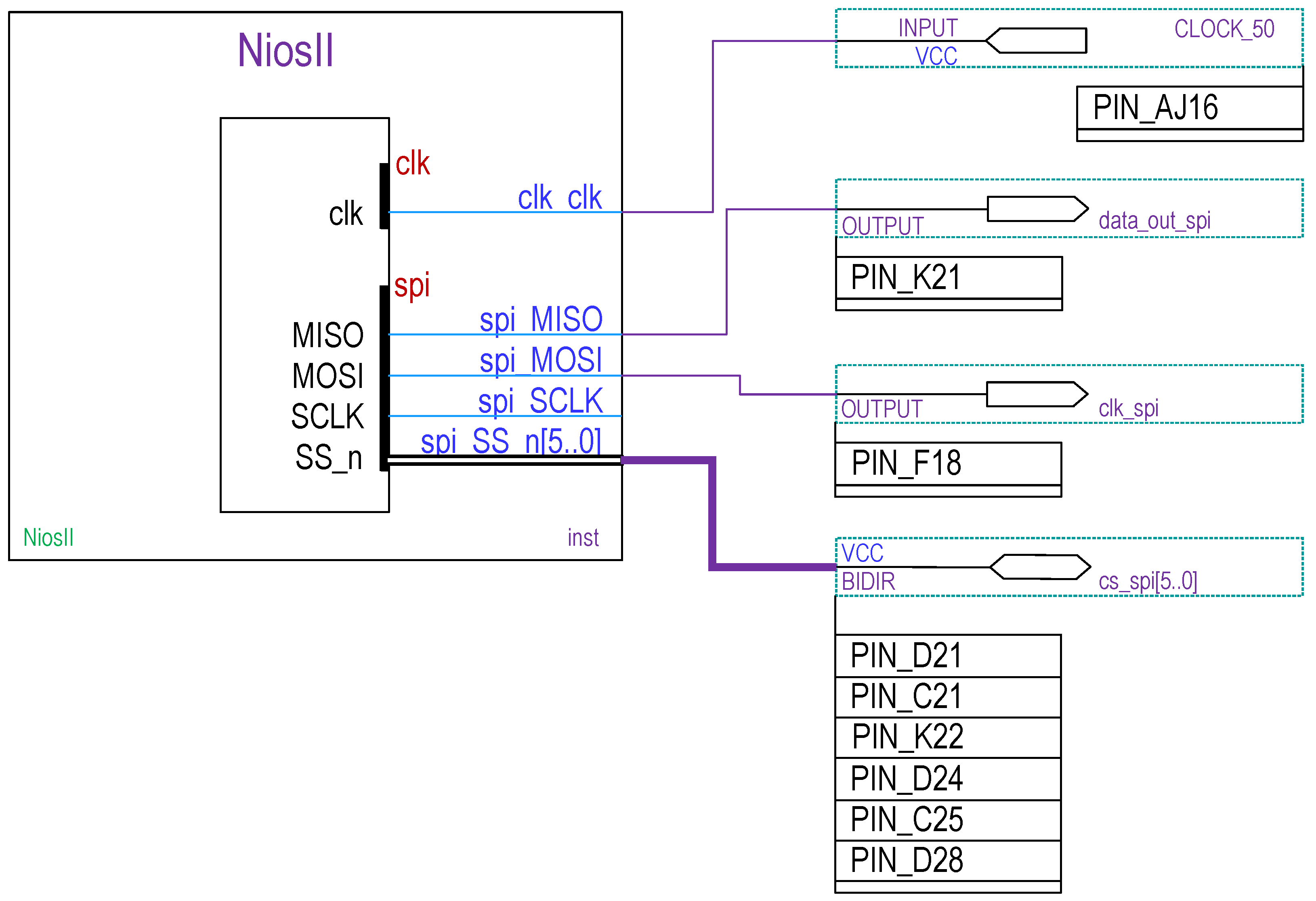

6. Digital Synchronization and Communication of a DSWN Implemented in FPGA

6.1. Uncoupled Nodes

6.2. Coupled Nodes

6.3. Digital Application in Communications Using FPGA in a DSWN

7. Conclusions

Author Contributions

Funding

Institutional Review Board Statement

Data Availability Statement

Acknowledgments

Conflicts of Interest

References

- Watts, D.J.; Strogatz, S.H. Collective dynamics of small-world networks. Nature 1998, 393, 440–442. [Google Scholar] [CrossRef] [PubMed]

- Uzun, R.; Yilmaz, E.; Ozer, M. Effects of autapse and ion channel block on the collective firing activity of Newman–Watts small-world neuronal networks. Phys. A Stat. Mech. Its Appl. 2017, 486, 386–396. [Google Scholar] [CrossRef]

- Ismail, A.A.O.O.; Amouzandeh, G.; Grant, S.C. Structural connectivity within neural ganglia: A default small-world network. Neuroscience 2016, 337, 276–284. [Google Scholar] [CrossRef] [PubMed]

- Arellano-Delgado, A.; Cruz-Hernández, C.; López-Gutierrez, R.M.; Posadas-Castillo, C. Outer synchronization of nearest-neighbor and small-world chaotic networks. Ifac. Papers Online 2015, 48, 227–232. [Google Scholar] [CrossRef]

- Ferreira, D.S.; Papa, A.R.; Menezes, R. Small world picture of worldwide seismic events. Phys. A Stat. Mech. Its Appl. 2014, 408, 170–180. [Google Scholar] [CrossRef]

- Liao, X.; Vasilakos, A.V.; He, Y. Small-world human brain networks: Perspectives and challenges. Neurosci. Biobehav. Rev. 2017, 77, 286–300. [Google Scholar] [CrossRef] [PubMed]

- Ruan, Y.; Li, A. A new small-world network created by Cellular Automata. Phys. A Stat. Mech. Its Appl. 2016, 456, 106–111. [Google Scholar] [CrossRef]

- Comellas, F.; Ozon, J.; Peters, J.G. Deterministic small-world communication networks. Inf. Process. Lett. 2000, 76, 83–90. [Google Scholar] [CrossRef]

- Comellas, F.; Sampels, M. Deterministic small-world networks. Phys. A Stat. Mech. Its Appl. 2002, 309, 231–235. [Google Scholar] [CrossRef]

- Zhang, Z.; Rong, L.; Guo, C. A deterministic small-world network created by edge iterations. Phys. A 2006, 363, 567–572. [Google Scholar] [CrossRef]

- Zhang, Y.; Zhang, Z.; Zhou, S.; Guan, J. Deterministic weighted scale-free small-world networks. Phys. A Stat. Mech. Its Appl. 2010, 389, 3316–3324. [Google Scholar] [CrossRef]

- Cruz-Hernández, C. Synchronization of time-delay Chua’s oscillator with application to secure communication. Nonlinear Dyn. Syst. Theory 2004, 4, 1–13. [Google Scholar]

- Posadas-Castillo, C.; López-Gutiérrez, R.M.; Cruz-Hernández, C. Synchronization of chaotic solid-state Nd:YAG lasers: Application to secure communication. Commun. Nonlinear Sci. Numer. Simul. 2008, 13, 1655–1667. [Google Scholar] [CrossRef]

- Gámez-Guzmán, L.; Cruz-Hernéz, C.; López-Gutiérrez, R.M.; García-Guerrero, E.E. Synchronization of Chua’s circuits with multi-scroll attractors: Application to communication. Commun. Nonlinear Sci. Numer. Simul. 2009, 14, 2765–2775. [Google Scholar] [CrossRef]

- Cruz-Hernández, C.; Romero-Haros, N. Communicating via synchronized time-delay Chua’s circuits. Commun. Nonlinear Sci. Numer. Simul. 2008, 13, 645–659. [Google Scholar] [CrossRef]

- Wang, X.F.; Chen, G. Synchronization in small-world dynamical networks. Int. J. Bifurc. Chaos 2002, 12, 187–192. [Google Scholar] [CrossRef]

- Wang, X.F. Complex networks: Topology, dynamics and synchronization. Int. J. Bifurc. Chaos 2002, 12, 885–916. [Google Scholar] [CrossRef]

- Reyes-De la Cruz, D.; Cruz-Hernández, C.; Posadas-Castillo, C.; Martínez-Clark, R. Encriptado caótico en una red determinista de mundo pequeño. In Proceedings of the Congreso Latinoamericano de Control Automático 2014, Cancún Quintana Roo, Mexico, 14–17 October 2014. [Google Scholar]

- Rabinder, M. (Ed.) Chua’s Circuit: A Paradigm for Chaos; World Scientific: Singapore, 1993. [Google Scholar]

- Arellano-Delgado, A.; López-Gutiérrez, R.M.; Cruz-Hernández, C.; Posadas-Castillo, C. Experimental network synhronization via plastic optical fiber. Opt. Fiber Technol. 2013, 19, 93–108. [Google Scholar] [CrossRef]

- Méndez-Ramírez, R.; Arellano-Delgado, A.; Cruz-Hernández, C.; Abundiz-Pxexrez, F.; Martxixnez-Clark, R. Chaotic digital cryptosystem using serial peripheral interface protocol and its dsPIC implementation. Front. Inf. Technol. Electron. Eng. 2018, 19, 165–179. [Google Scholar] [CrossRef]

- Méndez-Ramírez, R.; Cruz-Hernández, C.; Arellano-Delgado, A.; López-Gutixexrrez, R.M. Degradation Analysis of Generalized Chua′s Circuit Generator of Multi-Scroll Chaotic Attractors and its Implementation on PIC32. In Proceedings of the Future Technologies Conference 2016, San Francisco, CA, USA, 6–7 December 2016. [Google Scholar]

- Cyclone IV Device Handbook Home Page. Available online: https://www.intel.com/content/www/us/en/content-details/653974/cyclone-iv-device-handbook.html?wapkw=cyclone%20iv (accessed on 16 February 2023).

- Intel® Quartus® II Web Edition Design Software Version 13.1 for Windows Home Page. Available online: https://www.intel.com/content/www/us/en/software-kit/666221/intel-quartus-ii-web-edition-design-software-version-13-1-for-windows.html (accessed on 16 February 2023).

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2023 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Reyes-De la Cruz, D.; Méndez-Ramírez, R.; Arellano-Delgado, A.; Cruz-Hernández, C. Electronic Implementation of a Deterministic Small-World Network: Synchronization and Communication. Entropy 2023, 25, 709. https://doi.org/10.3390/e25050709

Reyes-De la Cruz D, Méndez-Ramírez R, Arellano-Delgado A, Cruz-Hernández C. Electronic Implementation of a Deterministic Small-World Network: Synchronization and Communication. Entropy. 2023; 25(5):709. https://doi.org/10.3390/e25050709

Chicago/Turabian StyleReyes-De la Cruz, Daniel, Rodrigo Méndez-Ramírez, Adrian Arellano-Delgado, and César Cruz-Hernández. 2023. "Electronic Implementation of a Deterministic Small-World Network: Synchronization and Communication" Entropy 25, no. 5: 709. https://doi.org/10.3390/e25050709

APA StyleReyes-De la Cruz, D., Méndez-Ramírez, R., Arellano-Delgado, A., & Cruz-Hernández, C. (2023). Electronic Implementation of a Deterministic Small-World Network: Synchronization and Communication. Entropy, 25(5), 709. https://doi.org/10.3390/e25050709