Negative Design Margin Realization through Deep Path Activity Detection Combined with Dynamic Voltage Scaling in a 55 nm Near-Threshold 32-Bit Microcontroller

Abstract

:1. Introduction

2. Overview of EDaC Techniques

2.1. Error Detection

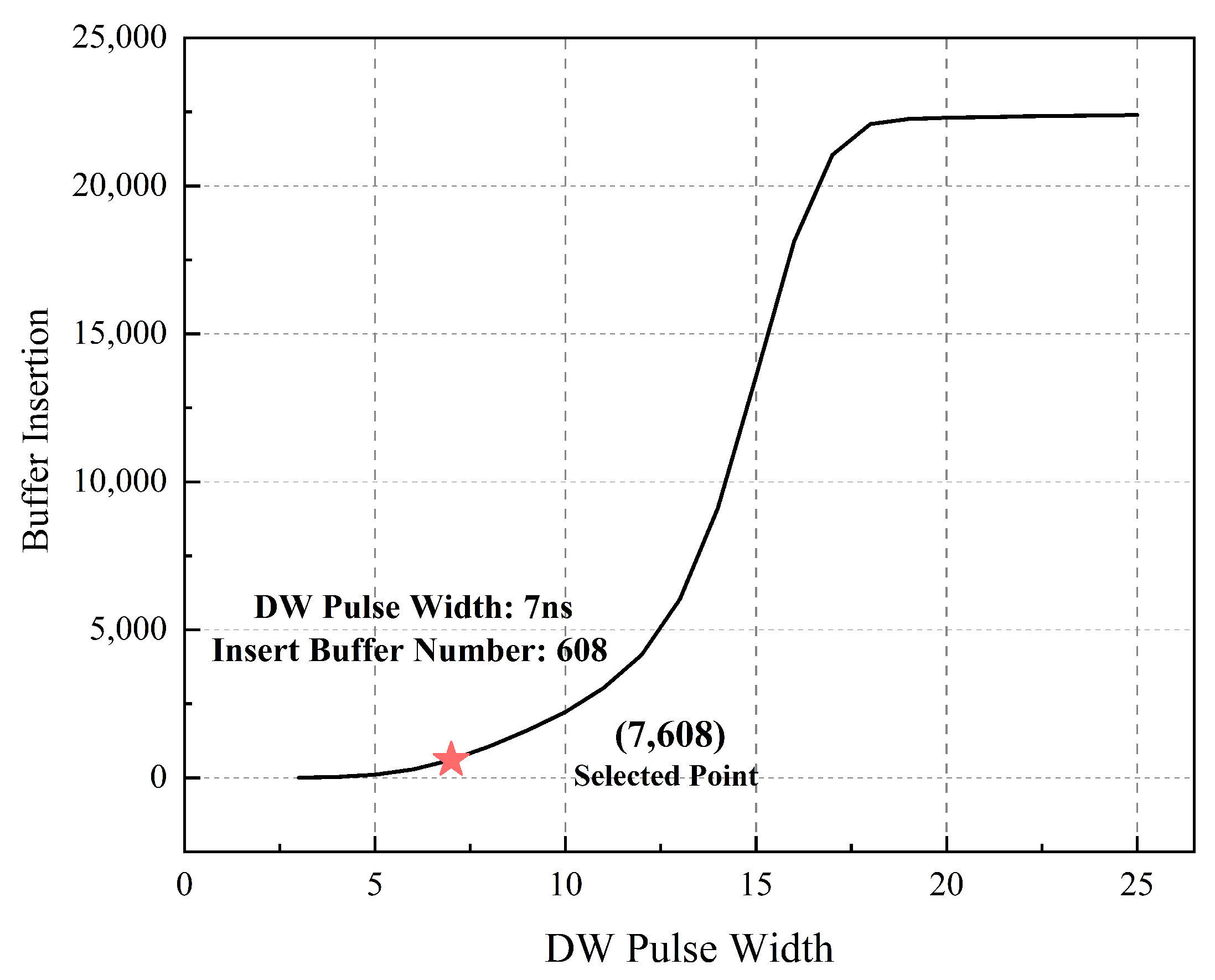

2.2. Detection Window

2.3. Error Correction

3. Presented Concept and Analysis

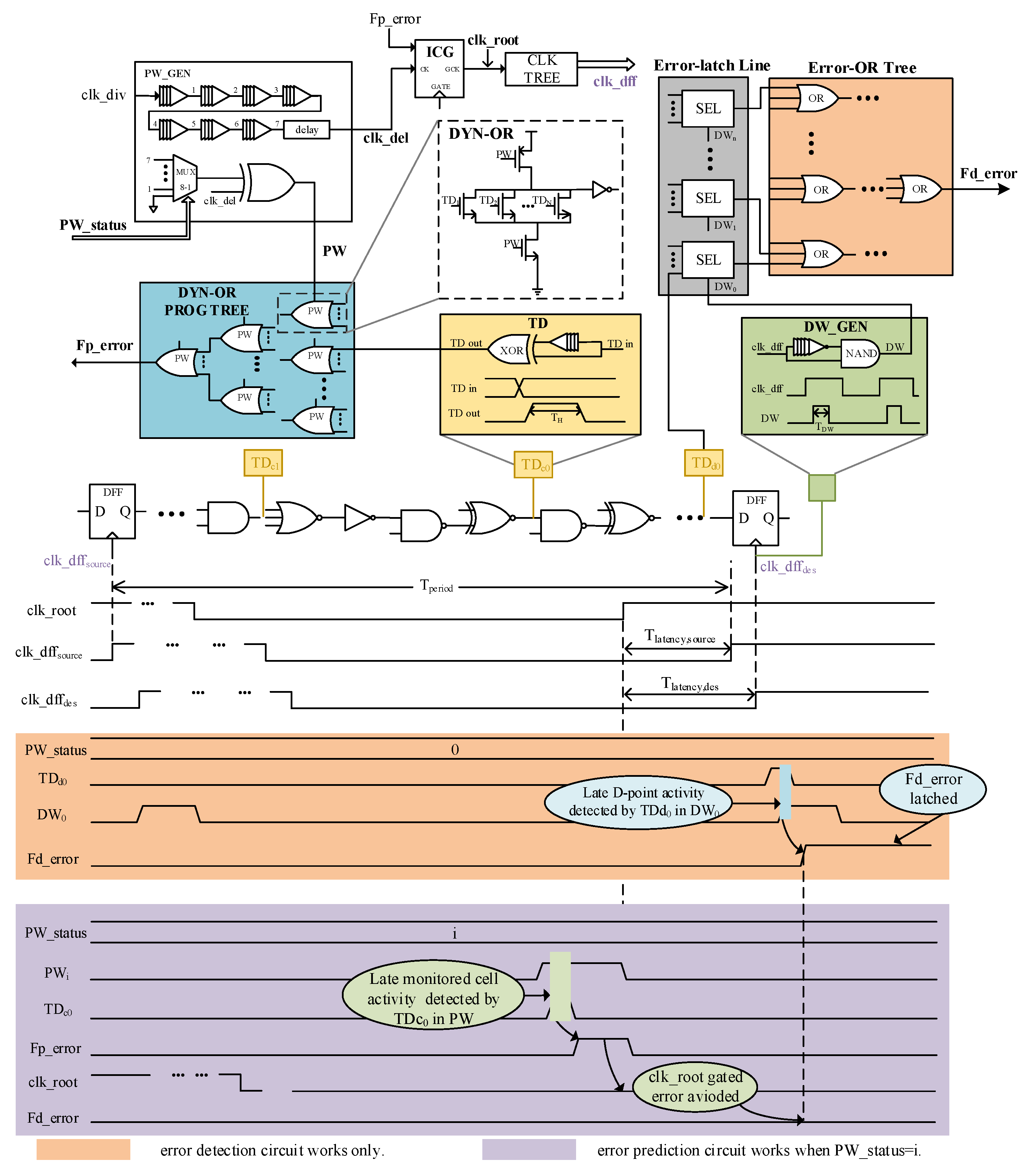

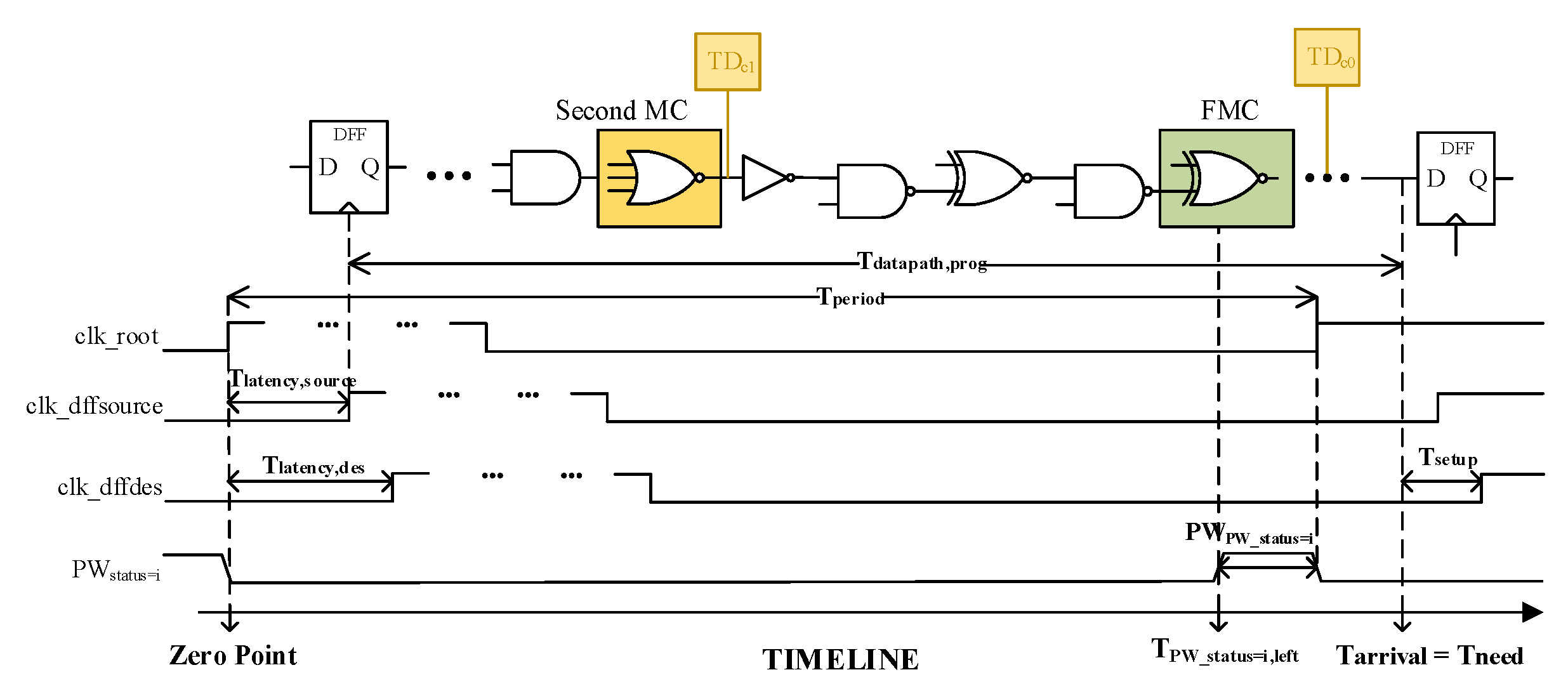

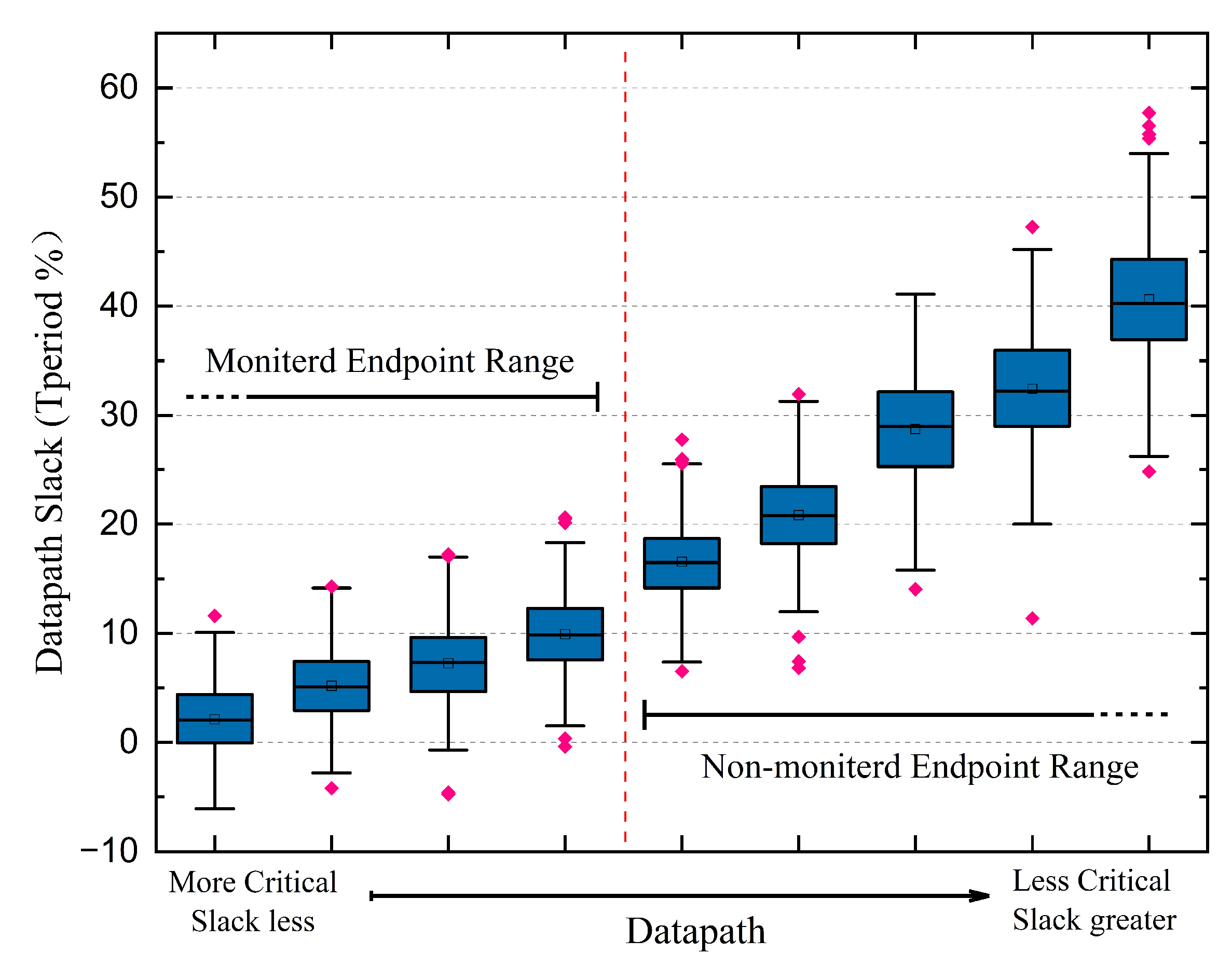

3.1. Error Prediction Circuit (EPC) Concept

- As the supply decreases after power-up, timing errors are gradually detected by EDC, and increases accordingly until one of the TDs’ outputs is covered. Therefore, the difference between adjacent PW width should be greater than a TD’s output pulse width , which needs to be satisfied at different PVT corners:

- A minimum pulse width constraint applies on the . This constraint equals the sum of the worst case propagation delay for DYN-OR TREE and setup time for Integrated Clock Gating (ICG) cell:

3.2. Error Detection Circuit (EDC) Concept

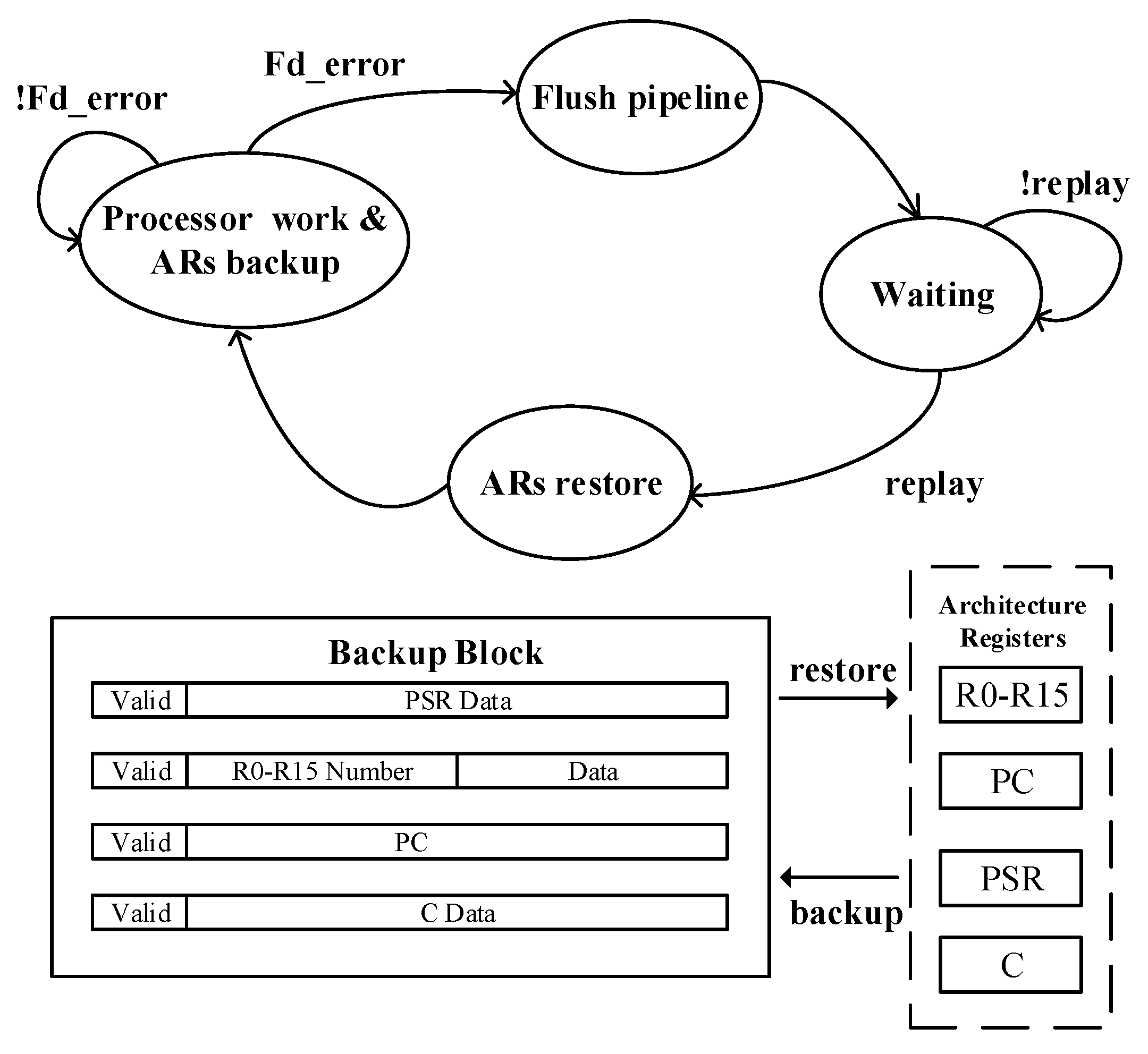

3.3. Error Correction Circuit (ECC) Concept

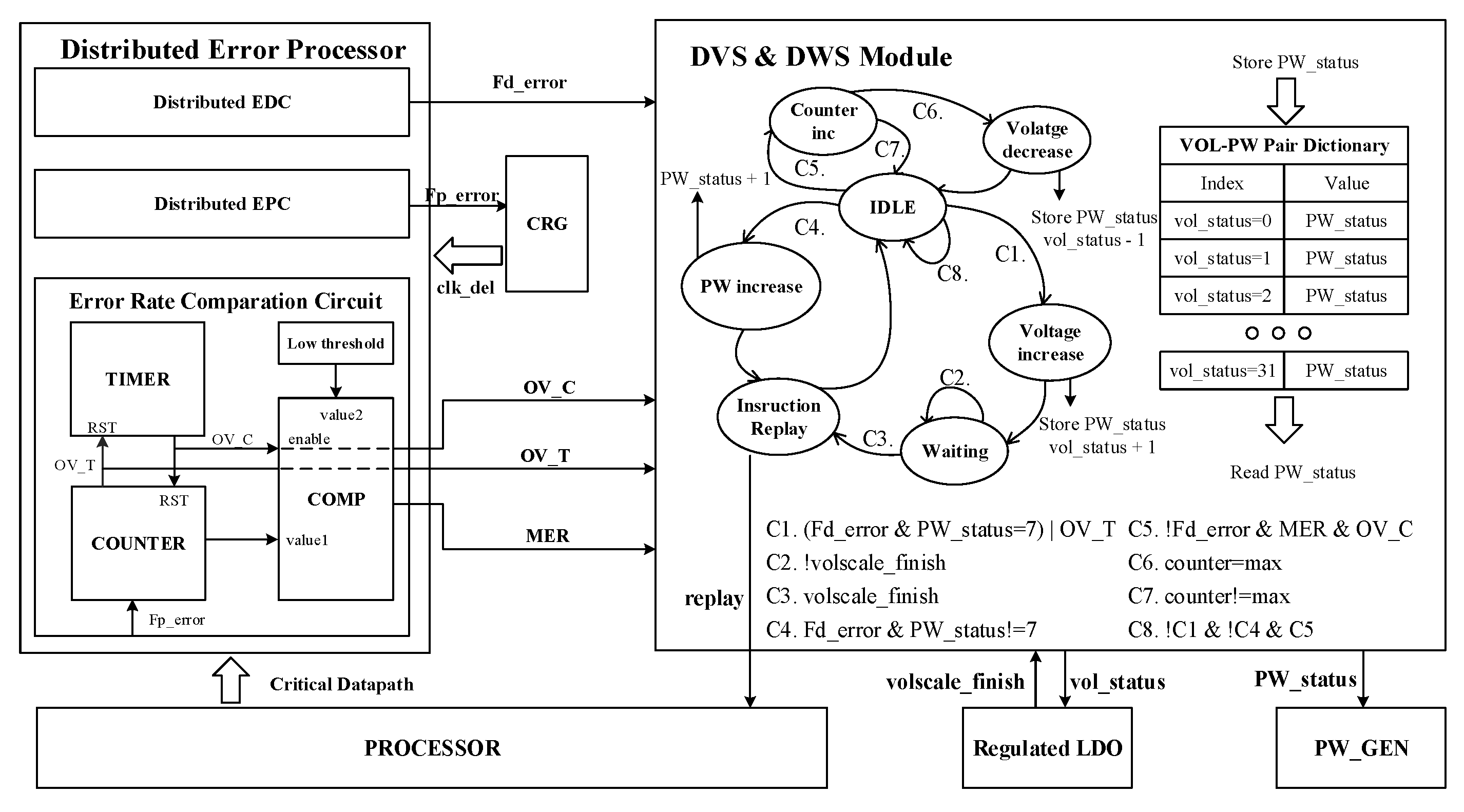

3.4. DVS and DWS Module

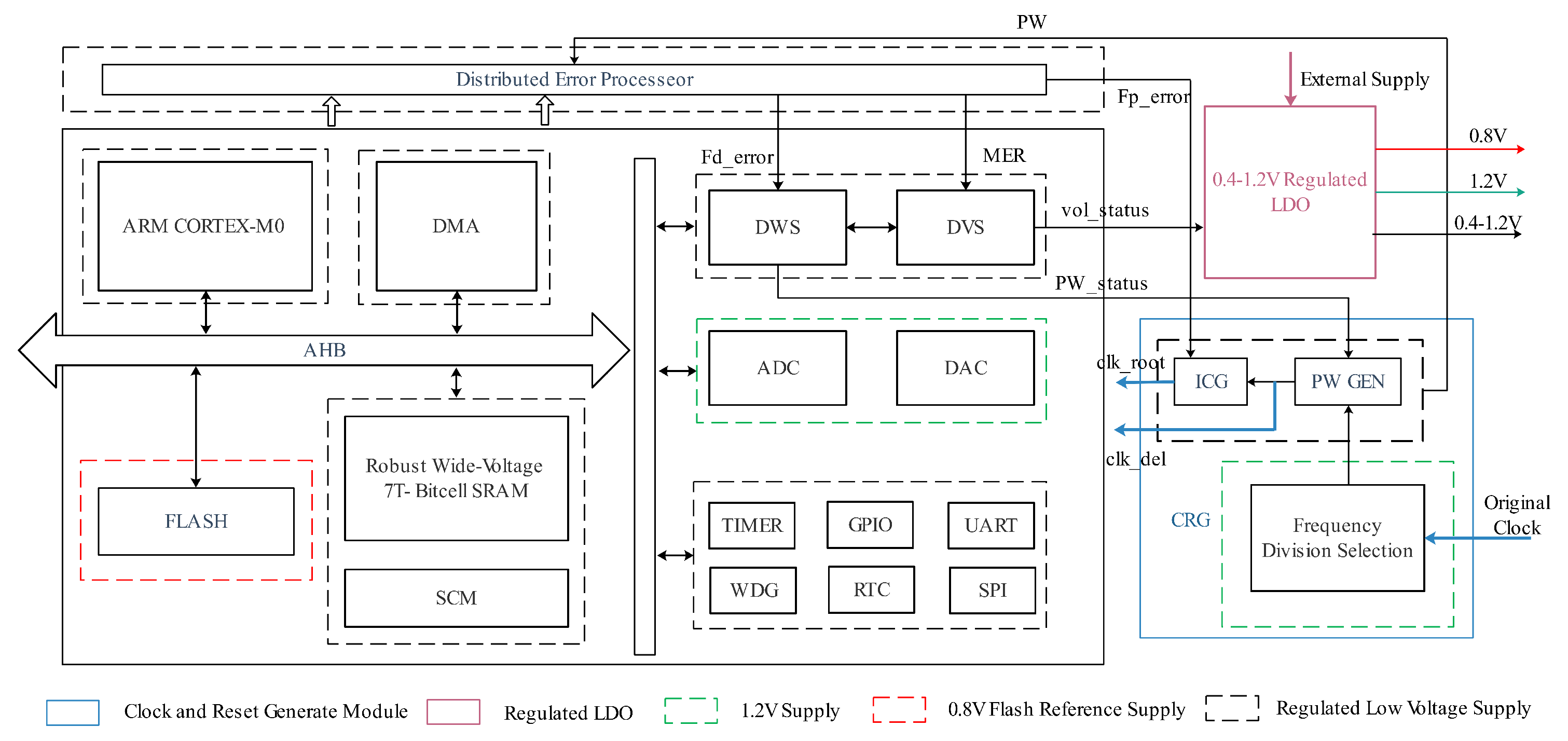

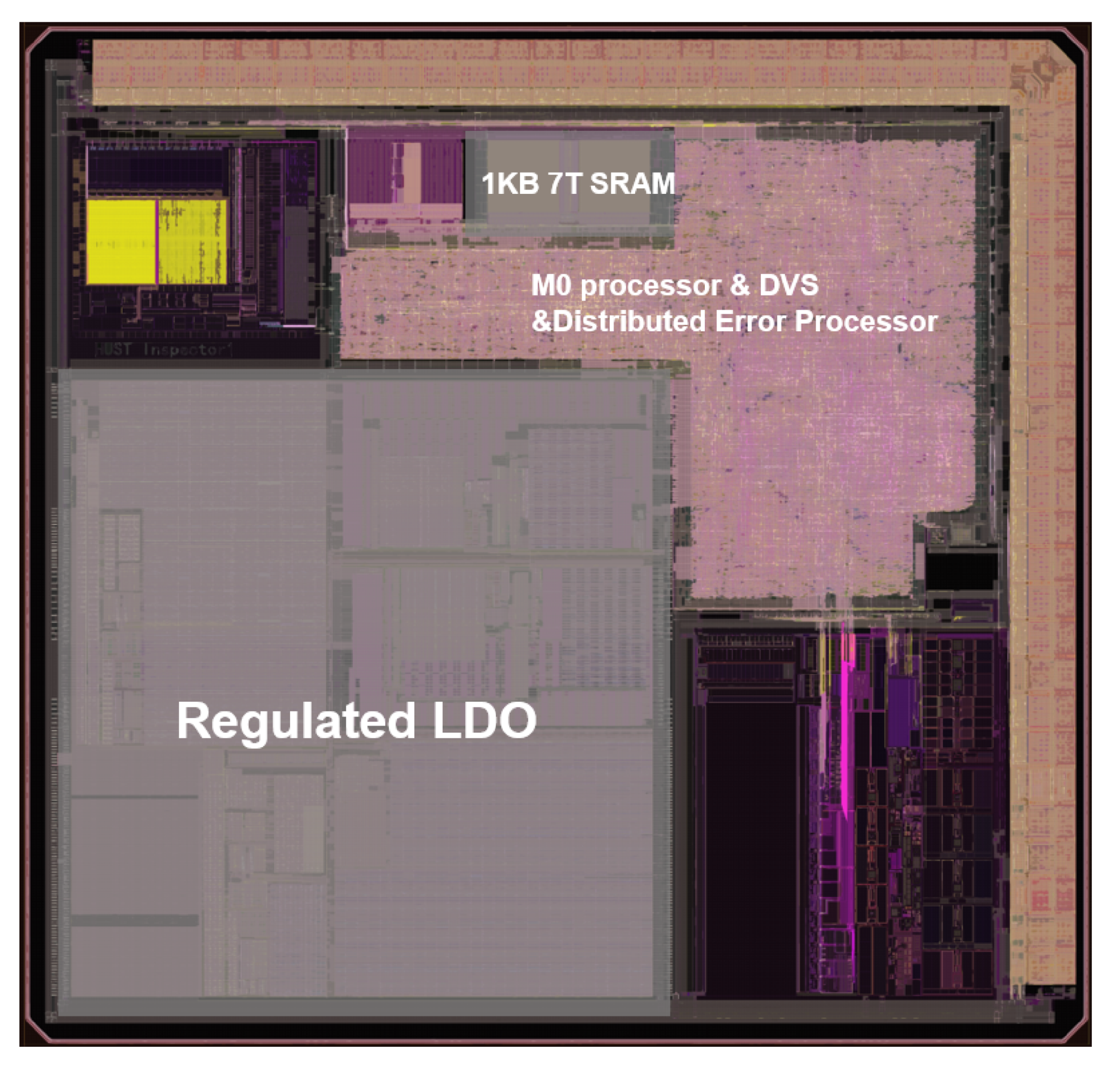

4. Implementation

4.1. Ultra-Low Voltage Implementation

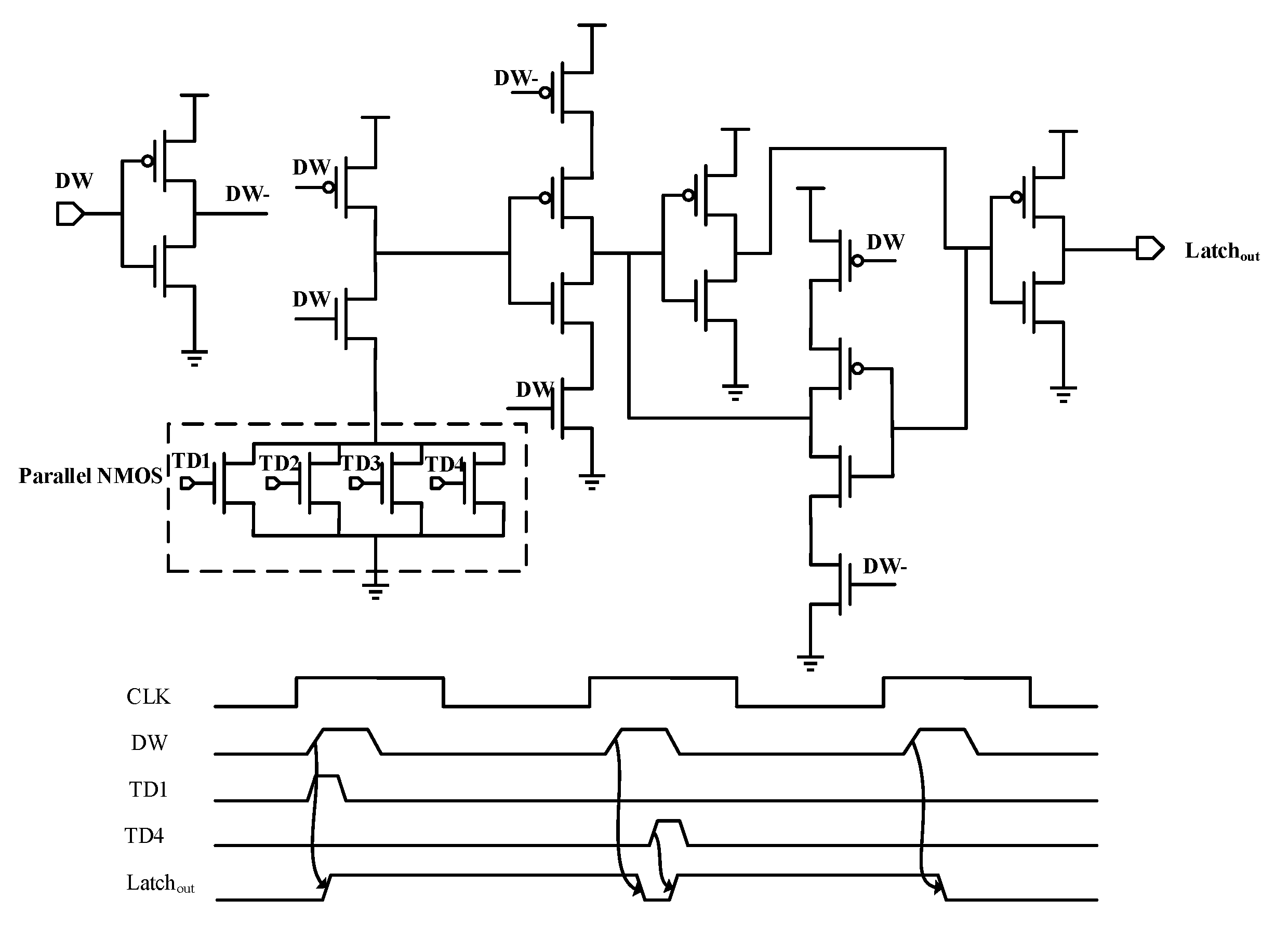

4.2. EDC Design Details

4.3. EPC Design Details

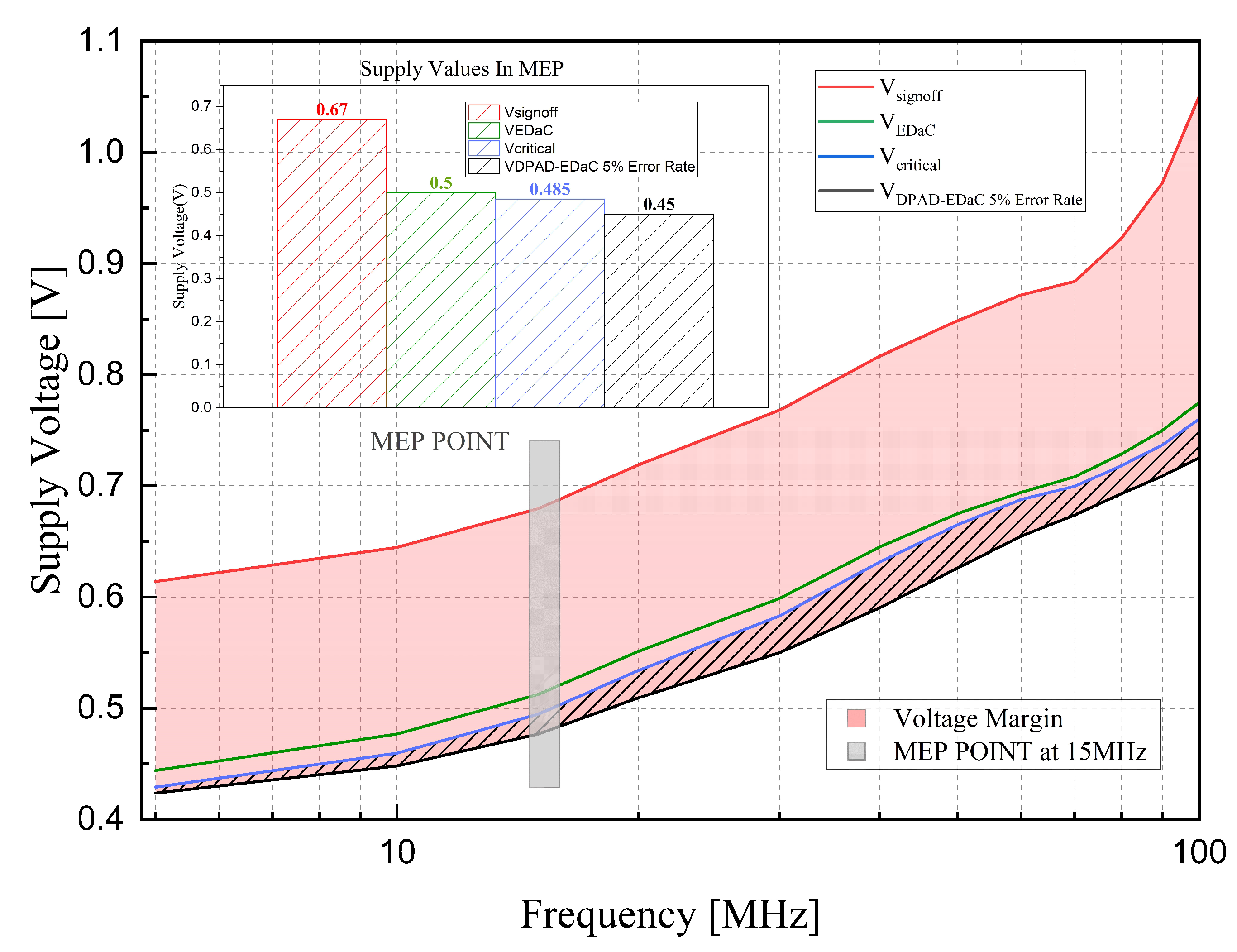

5. Experimental Results

5.1. Experimental Setup

5.2. Operation Comparison under Four Conditions

5.3. Comparison

6. Conclusions

Author Contributions

Funding

Institutional Review Board Statement

Informed Consent Statement

Data Availability Statement

Acknowledgments

Conflicts of Interest

Abbreviations

| EDaC | Error Detection and Correction |

| DVS | Dynamic Voltage Scaling |

| MEP | Minimum Energy Point |

| NTC | Near-Threshold Computing |

| DW | Detection Window |

| EP | Error Prediction |

| PW | Prediction Window |

| EDC | Error Detection Circuit |

| EPC | Error Prediction Circuit |

| ECC | Error Correction Circuit |

| ARs | Architecture Registers |

| SoTA | State-of-The-Art |

| DS | Double Sampling |

| TD | Transition Detection |

| IO | Input–Output |

| PoFF | Point of First Failure |

| DPAD–EDaC | Deep Path Activity Detection–EDaC |

| SEL | Shared Error Latch |

| DEP | Distributed Error Processor |

| RTL | Register Transfer Level |

| MC | Monte Carlo |

| STA | Static Timing Analysis |

References

- Kim, J.K.; Knag, P.; Chen, T.; Zhang, Z. A 640M pixel/s 3.65 mW sparse event-driven neuromorphic object recognition processor with on-chip learning. In Proceedings of the 2015 Symposium on VLSI Circuits (VLSI Circuits), Montpellier, France, 8–10 July 2015; pp. C50–C51. [Google Scholar]

- Jun, J.; Song, J.; Kim, C. A near-threshold voltage oriented digital cell library for high-energy efficiency and optimized performance in 65 nm CMOS process. IEEE Trans. Circuits Syst. Regul. Pap. 2017, 65, 1567–1580. [Google Scholar] [CrossRef]

- Jain, S.; Khare, S.; Yada, S.; Ambili, V.; Salihundam, P.; Ramani, S.; Muthukumar, S.; Srinivasan, M.; Kumar, A.; Gb, S.K.; et al. A 280 mV-to-1.2 V wide-operating-range IA-32 processor in 32 nm CMOS. In Proceedings of the 2012 IEEE International Solid-State Circuits Conference, San Francisco, CA, USA, 19–23 February 2012; pp. 66–68. [Google Scholar]

- Dasgupta, A.; Sepulveda, J.L. Accurate Results in the Clinical Laboratory: A Guide to Error Detection and Correction; Elsevier: Amsterdam, The Netherlands, 2019. [Google Scholar]

- Bowman, K.A.; Tschanz, J.W.; Lu, S.L.L.; Aseron, P.A.; Khellah, M.M.; Raychowdhury, A.; Geuskens, B.M.; Tokunaga, C.; Wilkerson, C.B.; Karnik, T.; et al. A 45 nm resilient microprocessor core for dynamic variation tolerance. IEEE J. Solid-State Circuits 2010, 46, 194–208. [Google Scholar] [CrossRef]

- Bull, D.; Das, S.; Shivashankar, K.; Dasika, G.S.; Flautner, K.; Blaauw, D. A power-efficient 32 bit ARM processor using timing-error detection and correction for transient-error tolerance and adaptation to PVT variation. IEEE J. Solid-State Circuits 2010, 46, 18–31. [Google Scholar] [CrossRef]

- Das, S.; Roberts, D.; Lee, S.; Pant, S.; Blaauw, D.; Austin, T.; Flautner, K.; Mudge, T. A self-tuning DVS processor using delay-error detection and correction. IEEE J. Solid-State Circuits 2006, 41, 792–804. [Google Scholar] [CrossRef]

- Shan, W.; Dai, W.; Zhang, C.; Cai, H.; Liu, P.; Yang, J.; Shi, L. TG-SPP: A one-transmission-gate short-path padding for wide-voltage-range resilient circuits in 28-nm CMOS. IEEE J. Solid-State Circuits 2019, 55, 1422–1436. [Google Scholar] [CrossRef]

- Pawlowski, R.; Krimer, E.; Crop, J.; Postman, J.; Moezzi-Madani, N.; Erez, M.; Chiang, P. A 530 mV 10-lane SIMD processor with variation resiliency in 45 nm SOI. In Proceedings of the 2012 IEEE International Solid-State Circuits Conference, San Francisco, CA, USA, 19–23 February 2012; pp. 492–494. [Google Scholar]

- Choudhury, M.; Chandra, V.; Mohanram, K.; Aitken, R. TIMBER: Time borrowing and error relaying for online timing error resilience. In Proceedings of the 2010 Design, Automation & Test in Europe Conference & Exhibition (DATE 2010), Dresden, Germany, 8–12 March 2010; pp. 1554–1559. [Google Scholar]

- Das, S.; Tokunaga, C.; Pant, S.; Ma, W.H.; Kalaiselvan, S.; Lai, K.; Bull, D.M.; Blaauw, D.T. RazorII: In situ error detection and correction for PVT and SER tolerance. IEEE J. Solid-State Circuits 2008, 44, 32–48. [Google Scholar] [CrossRef]

- Bowman, K.A.; Tschanz, J.W.; Kim, N.S.; Lee, J.C.; Wilkerson, C.B.; Lu, S.L.L.; Karnik, T.; De, V.K. Energy-efficient and metastability-immune resilient circuits for dynamic variation tolerance. IEEE J. Solid-State Circuits 2008, 44, 49–63. [Google Scholar] [CrossRef]

- Kim, S.; Seok, M. Variation-tolerant, ultra-low-voltage microprocessor with a low-overhead, within-a-cycle in-situ timing-error detection and correction technique. IEEE J. Solid-State Circuits 2015, 50, 1478–1490. [Google Scholar] [CrossRef]

- Drake, A.; Senger, R.; Deogun, H.; Carpenter, G.; Ghiasi, S.; Nguyen, T.; James, N.; Floyd, M.; Pokala, V. A distributed critical-path timing monitor for a 65nm high-performance microprocessor. In Proceedings of the 2007 IEEE International Solid-State Circuits Conference, San Francisco, CA, USA, 11–15 February 2007; pp. 398–399. [Google Scholar]

- Felice, M.; Briscoe, T. Towards a standard evaluation method for grammatical error detection and correction. In Proceedings of the 2015 Conference of the North American Chapter of the Association for Computational Linguistics: Human Language Technologies, Denver, CO, USA, 31 May–5 June 2015; pp. 578–587. [Google Scholar]

- Kim, S.; Cerqueira, J.P.; Seok, M. A 450 mV timing-margin-free waveform sorter based on body swapping error correction. In Proceedings of the 2016 IEEE Symposium on VLSI Circuits (VLSI-Circuits), Honolulu, HI, USA, 15–17 June 2016; pp. 1–2. [Google Scholar]

- Kwon, I.; Kim, S.; Fick, D.; Kim, M.; Chen, Y.P.; Sylvester, D. Razor-lite: A light-weight register for error detection by observing virtual supply rails. IEEE J. Solid-State Circuits 2014, 49, 2054–2066. [Google Scholar] [CrossRef]

- Reyserhove, H.; Dehaene, W. Margin elimination through timing error detection in a near-threshold enabled 32-bit microcontroller in 40-nm CMOS. IEEE J. Solid-State Circuits 2018, 53, 2101–2113. [Google Scholar] [CrossRef]

- Kim, S.; Cerqueira, J.P.; Seok, M. A Near-Threshold Spiking Neural Network Accelerator With a Body-Swapping-Based In-Situ Error Detection and Correction Technique. IEEE Trans. Very Large Scale Integr. (VLSI) Syst. 2019, 27, 1886–1896. [Google Scholar] [CrossRef]

- Hong, C.Y.; Liu, T.T. A variation-resilient microprocessor with a two-level timing error detection and correction system in 28-nm CMOS. IEEE J. Solid-State Circuits 2019, 55, 2285–2294. [Google Scholar] [CrossRef]

- Whatmough, P.N.; Das, S.; Bull, D.M. A low-power 1-GHz razor FIR accelerator with time-borrow tracking pipeline and approximate error correction in 65-nm CMOS. IEEE J. Solid-State Circuits 2013, 49, 84–94. [Google Scholar] [CrossRef]

- Hiienkari, M.; Teittinen, J.; Koskinen, L.; Turnquist, M.; Kaltiokallio, M. A 3.15 pJ/cyc 32-bit RISC CPU with timing-error prevention and adaptive clocking in 28 nm CMOS. In Proceedings of the IEEE 2014 Custom Integrated Circuits Conference, San Jose, CA, USA, 15–17 September 2014; pp. 1–4. [Google Scholar]

- Zhang, Y.; Khayatzadeh, M.; Yang, K.; Saligane, M.; Pinckney, N.; Alioto, M.; Blaauw, D.; Sylvester, D. irazor: Current-based error detection and correction scheme for pvt variation in 40-nm arm cortex-r4 processor. IEEE J. Solid-State Circuits 2017, 53, 619–631. [Google Scholar] [CrossRef]

- Fojtik, M.; Fick, D.; Kim, Y.; Pinckney, N.; Harris, D.M.; Blaauw, D.; Sylvester, D. Bubble razor: Eliminating timing margins in an ARM cortex-M3 processor in 45 nm CMOS using architecturally independent error detection and correction. IEEE J. Solid-State Circuits 2012, 48, 66–81. [Google Scholar] [CrossRef]

- Uytterhoeven, R.; Dehaene, W. Design Margin Reduction Through Completion Detection in a 28-nm Near-Threshold DSP Processor. IEEE J. Solid-State Circuits 2021, 57, 651–660. [Google Scholar] [CrossRef]

- Uytterhoeven, R.; Dehaene, W. Completion detection-based timing error detection and correction in a near-threshold RISC-V microprocessor in FDSOI 28 nm. IEEE Solid-State Circuits Lett. 2020, 3, 230–233. [Google Scholar] [CrossRef]

- Tadros, R.N.; Hua, W.; Moreira, M.T.; Calazans, N.L.; Beerel, P.A. A low-power low-area error-detecting latch for resilient architectures in 28-nm FDSOI. IEEE Trans. Circuits Syst. Ii Express Briefs 2016, 63, 858–862. [Google Scholar] [CrossRef]

- Hua, W.; Tadros, R.N.; Beerel, P.A. Low area, low power, robust, highly sensitive error detecting latch for resilient architectures. In Proceedings of the 2016 International Symposium on Low Power Electronics and Design, Airport, CA, USA, 8–10 August 2016; pp. 16–21. [Google Scholar]

- Cannizzaro, M.; Beer, S.; Cortadella, J.; Ginosar, R.; Lavagno, L. SafeRazor: Metastability-robust adaptive clocking in resilient circuits. IEEE Trans. Circuits Syst. I Regul. Pap. 2015, 62, 2238–2247. [Google Scholar] [CrossRef]

- Beer, S.; Cannizzaro, M.; Cortadella, J.; Ginosar, R.; Lavagno, L. Metastability in better-than-worst-case designs. In Proceedings of the 2014 20th IEEE International Symposium on Asynchronous Circuits and Systems, Potsdam, Germany, 12–14 May 2014; pp. 101–102. [Google Scholar]

- Wang, S.; Chen, C.; Xiang, X.Y.; Meng, J.Y. A variation-tolerant near-threshold processor with instruction-level error correction. IEEE Trans. Very Large Scale Integr. (VLSI) Syst. 2017, 25, 1993–2006. [Google Scholar] [CrossRef]

- Kong, W.; Venkatraman, R.; Castagnetti, R.; Duan, F.; Ramesh, S. High-density and high-performance 6T-SRAM for system-on-chip in 130 nm CMOS technology. In Proceedings of the 2001 Symposium on VLSI Technology, Digest of Technical Papers (IEEE Cat. No. 01 CH37184). Kyoto, Japan, 9–10 June 2001; pp. 105–106. [Google Scholar]

- Wen, L.; Cheng, X.; Zhou, K.; Tian, S.; Zeng, X. Bit-interleaving-enabled 8T SRAM with shared data-aware write and reference-based sense amplifier. IEEE Trans. Circuits Syst. II Express Briefs 2016, 63, 643–647. [Google Scholar] [CrossRef]

- Do, A.T.; Lee, Z.C.; Wang, B.; Chang, I.J.; Liu, X.; Kim, T.T.H. 0.2 V 8T SRAM with PVT-aware bitline sensing and column-based data randomization. IEEE J. Solid-State Circuits 2016, 51, 1487–1498. [Google Scholar] [CrossRef]

| TVLSI’17 [31] | JSSC’18 [18] | JSSC’17 [23] | JSSC’19 [20] | JSSC’22 [25] | This Work | |

|---|---|---|---|---|---|---|

| Method | EDFF | EDFF | Half path EP | EDL | CD TD | CD TD |

| DW(%TCLK) | - | 5% | 50% | 50% | 20% | 7% |

| Correction | Replay | Borrowing | Predictive clock gating | Borrowing + Replay | Clock gating/Clock stretching | Clock gating + replay |

| Low-voltage failures 1 | None | None | Failures | None | Failures | None |

| Area overhead | 8.70% | 7% | 3.10% | 4.17% | 4.90% | 6.84% |

| Technology | 40 nm | 40 nm | 40 nm | 28 nm | 28 nm | 55 nm |

| Gate count | 145 K | M0/12 K | 5 K | 12 K | 69 K | 12 K |

| F-range (MHz) | 27.4–286 | 5–30 | 40–750 | 18–68 | 1–200 | 1–100 |

| V-range | 0.6 V–1 V | 0.29V–0.47V | 0.44 V–1 V | 0.4 V–0.9 V | 0.25 V–0.65 V | 0.4 V–1 V |

| Vdecrease (wrt Vsign) (wrt Ecritical) 2 | 23.10% | 42% | 18% | 40% | 22% | 29.10% |

| Esave (wrt Esign) | 44% | 75% | 50% | 61% | 33% | 47.97% |

| Emargin remained (wrt Ecritical) 3 | - | 37% | - | - | 12% | −19.75% |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2023 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Yu, R.-Z.; Li, Z.-H.; Deng, X.; Liu, Z.-L. Negative Design Margin Realization through Deep Path Activity Detection Combined with Dynamic Voltage Scaling in a 55 nm Near-Threshold 32-Bit Microcontroller. Sensors 2023, 23, 7498. https://doi.org/10.3390/s23177498

Yu R-Z, Li Z-H, Deng X, Liu Z-L. Negative Design Margin Realization through Deep Path Activity Detection Combined with Dynamic Voltage Scaling in a 55 nm Near-Threshold 32-Bit Microcontroller. Sensors. 2023; 23(17):7498. https://doi.org/10.3390/s23177498

Chicago/Turabian StyleYu, Run-Ze, Zhen-Hao Li, Xi Deng, and Zheng-Lin Liu. 2023. "Negative Design Margin Realization through Deep Path Activity Detection Combined with Dynamic Voltage Scaling in a 55 nm Near-Threshold 32-Bit Microcontroller" Sensors 23, no. 17: 7498. https://doi.org/10.3390/s23177498

APA StyleYu, R.-Z., Li, Z.-H., Deng, X., & Liu, Z.-L. (2023). Negative Design Margin Realization through Deep Path Activity Detection Combined with Dynamic Voltage Scaling in a 55 nm Near-Threshold 32-Bit Microcontroller. Sensors, 23(17), 7498. https://doi.org/10.3390/s23177498