Analysis of Light Intensity and Charge Holding Time Dependence of Pinned Photodiode Full Well Capacity

Abstract

:1. Introduction

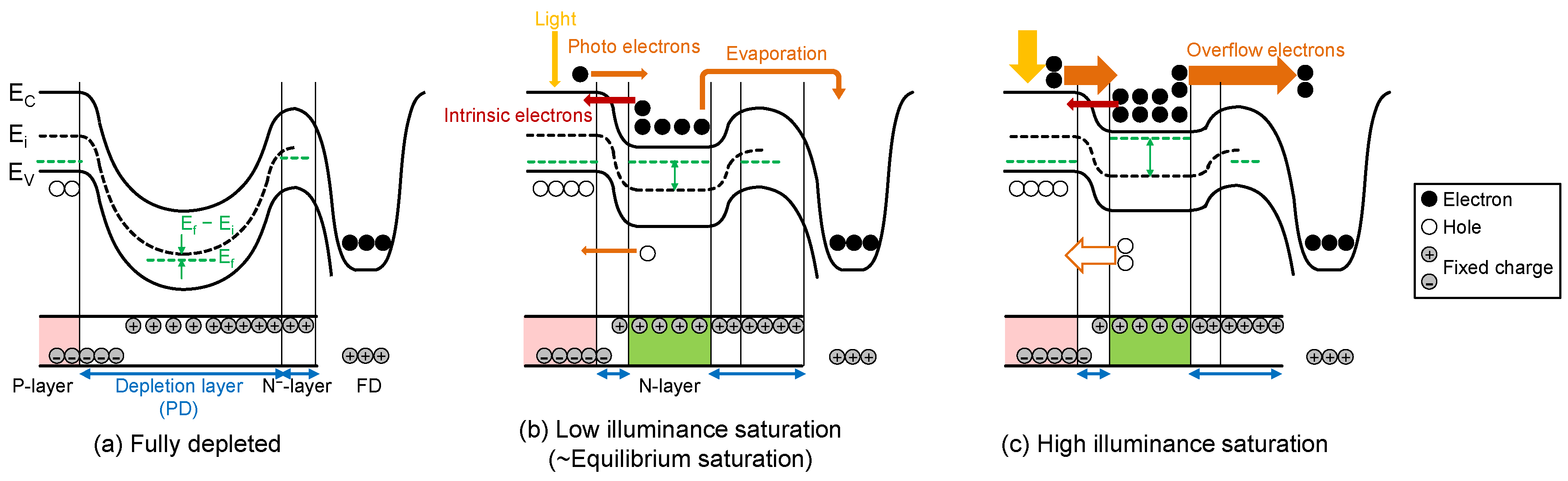

2. Analytical Model

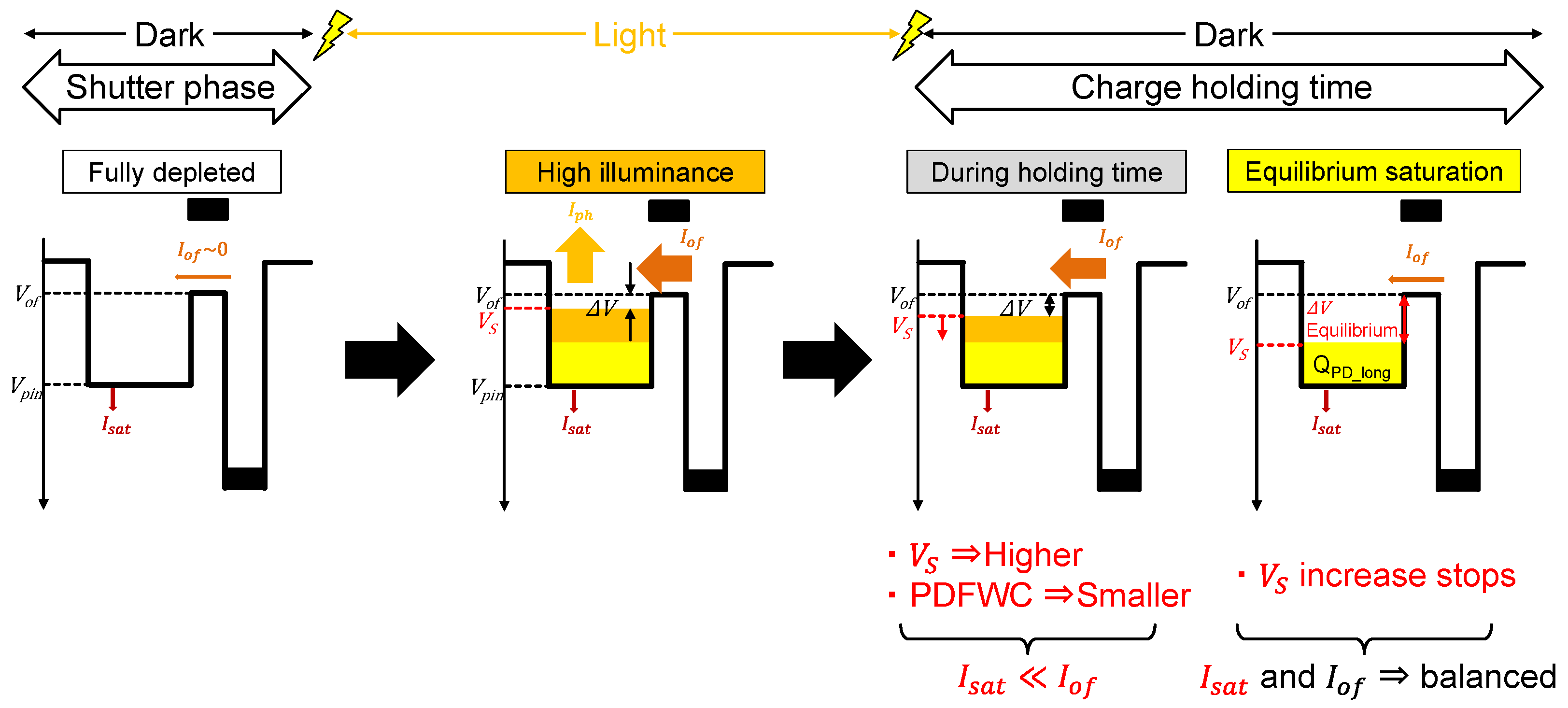

2.1. Light Intensity Dependence

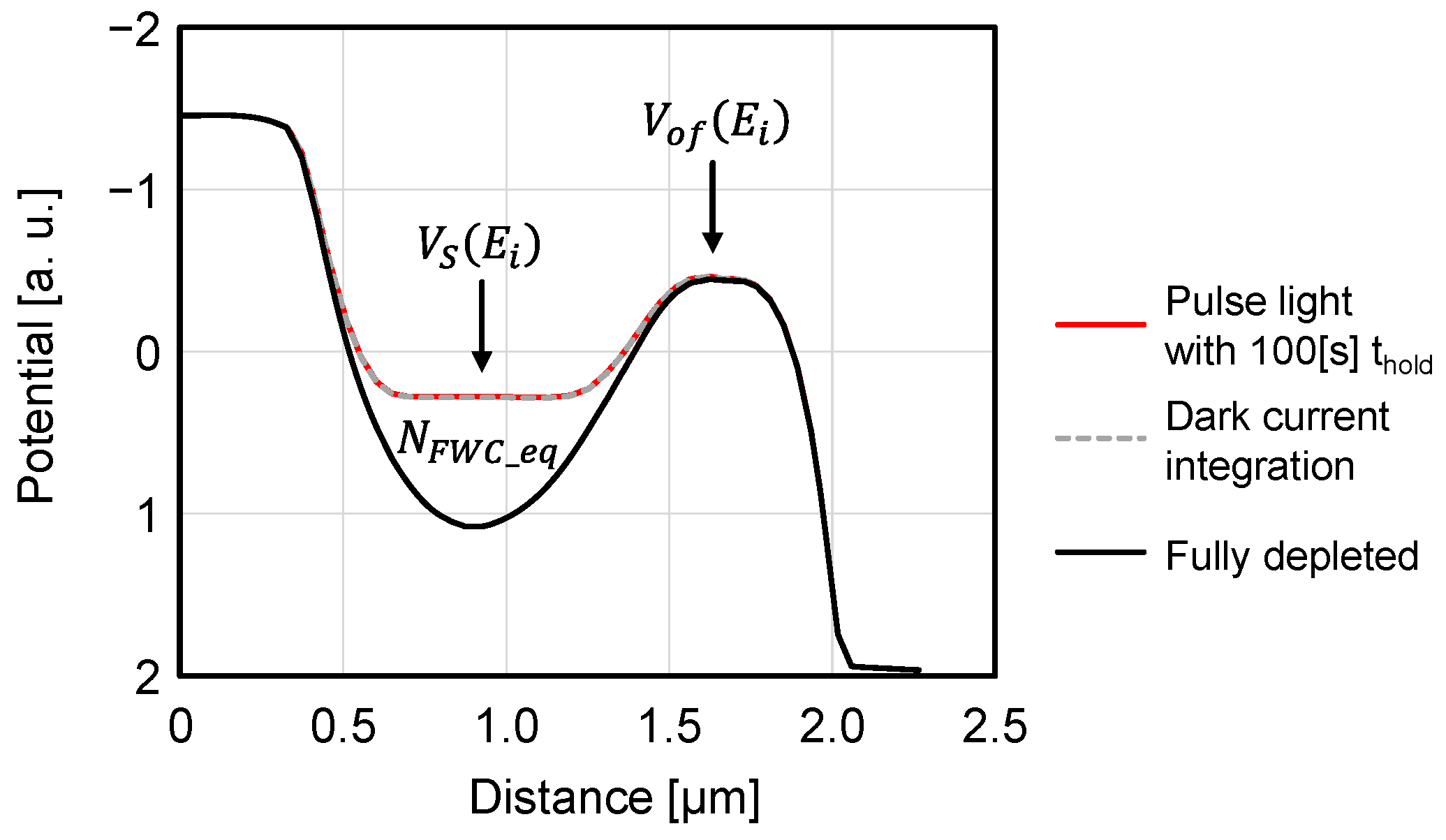

2.2. Charge Holding Time Dependence

2.3. Equilibrium PDFWC

3. Experimental Validation

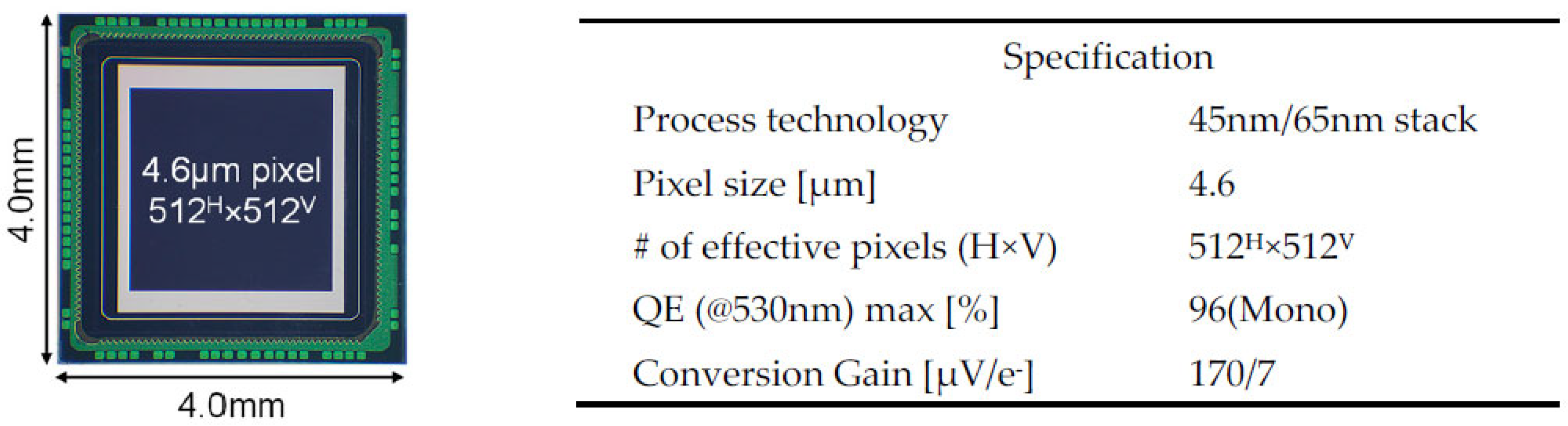

3.1. Device Information

3.2. Basic Characteristics of Transfer Gate Transistor

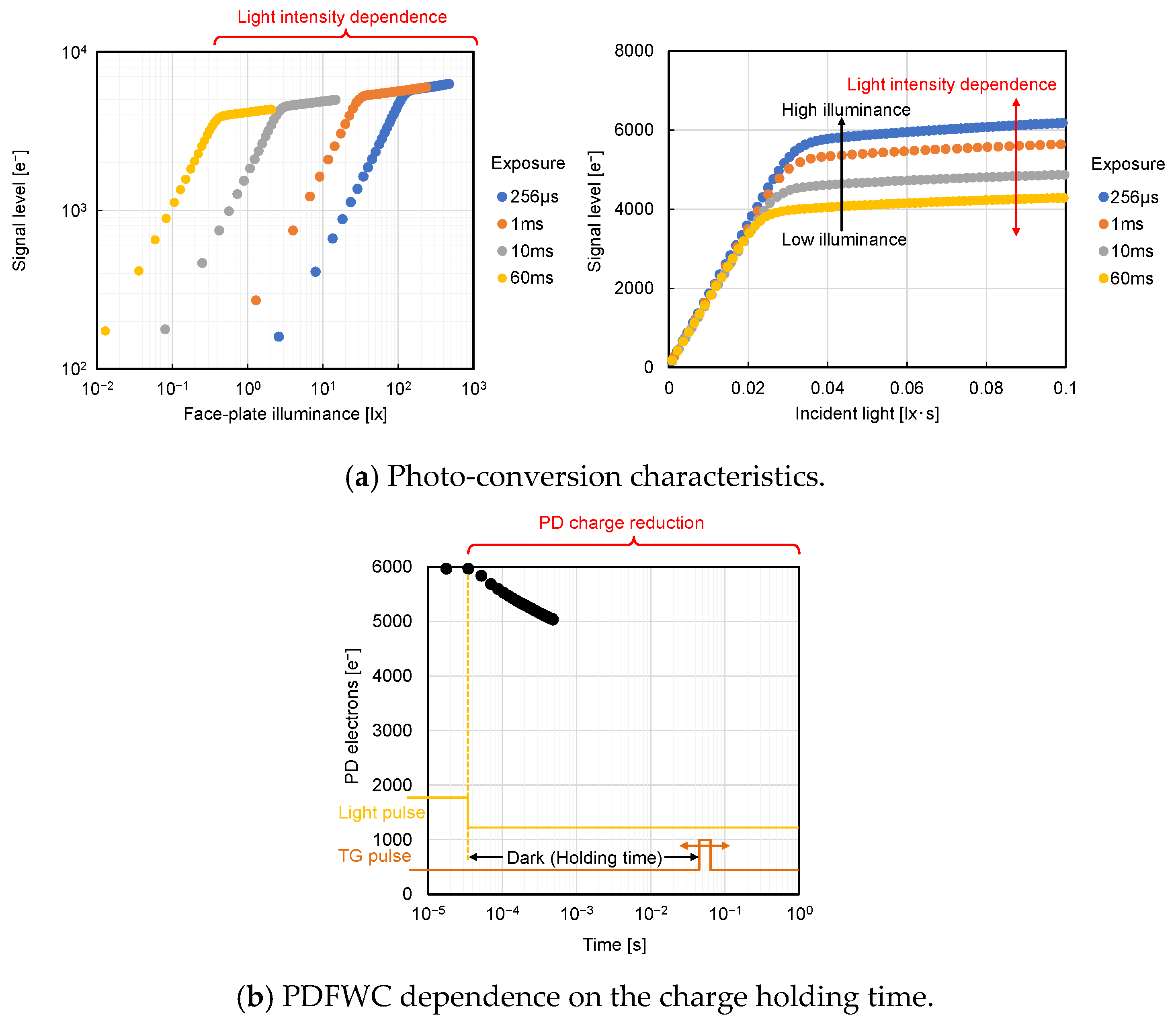

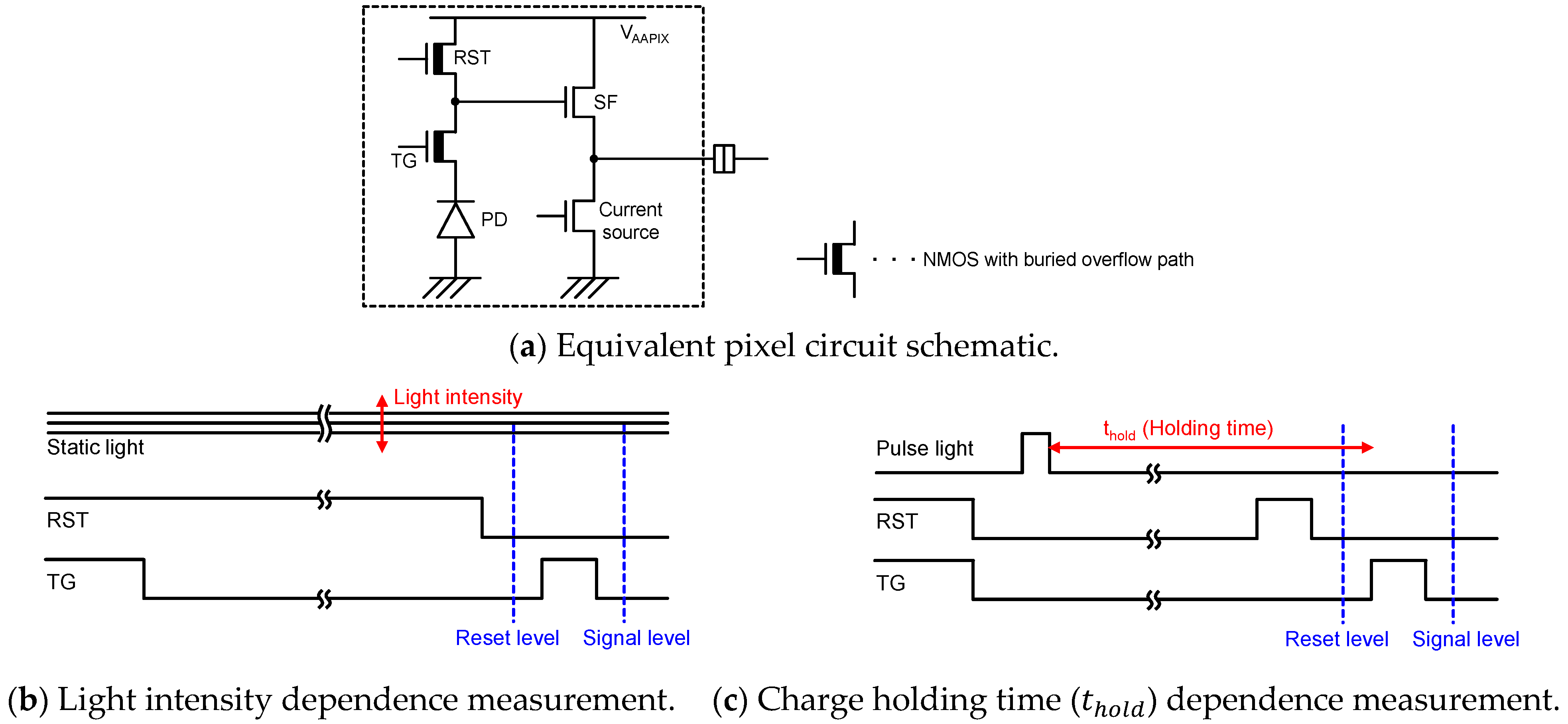

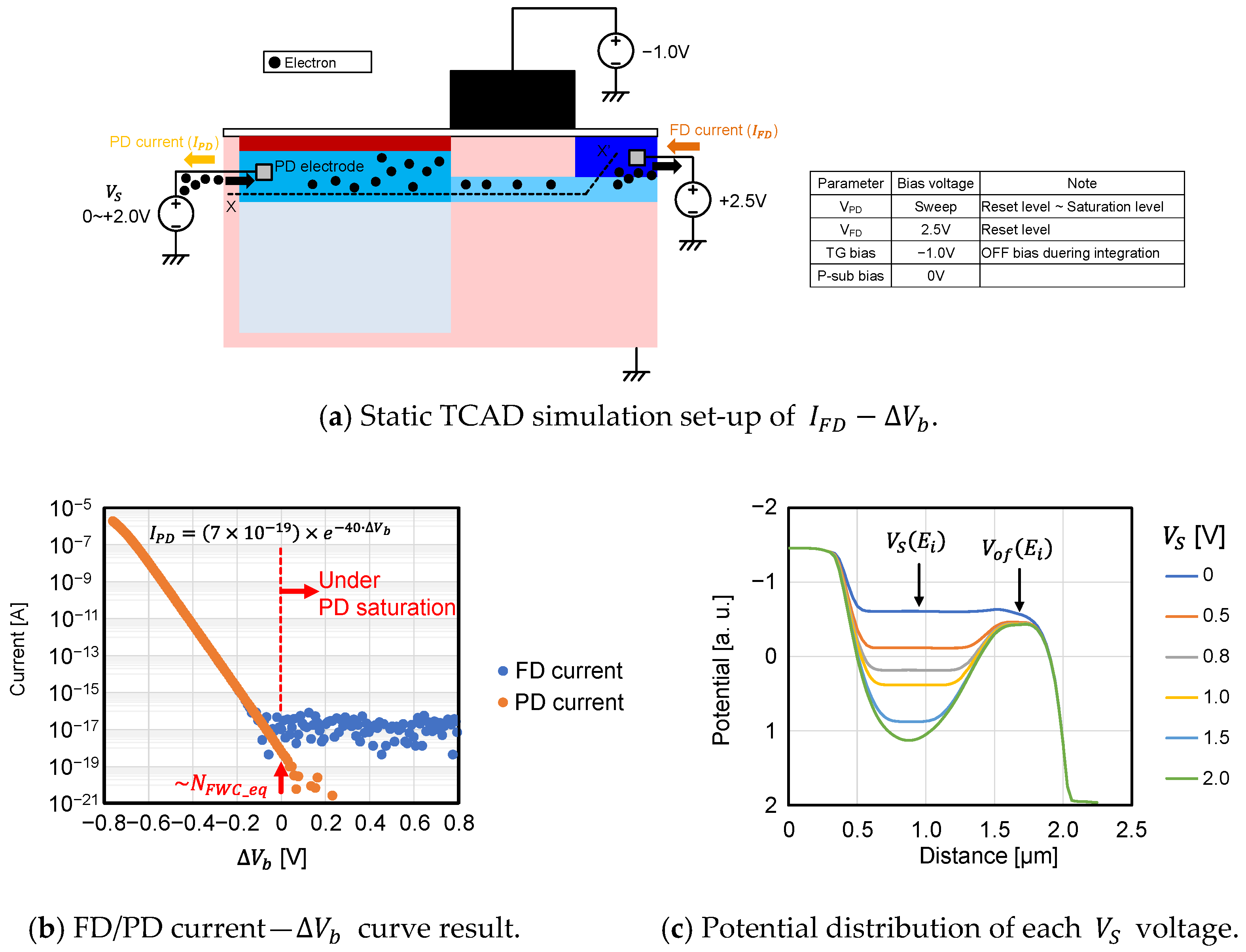

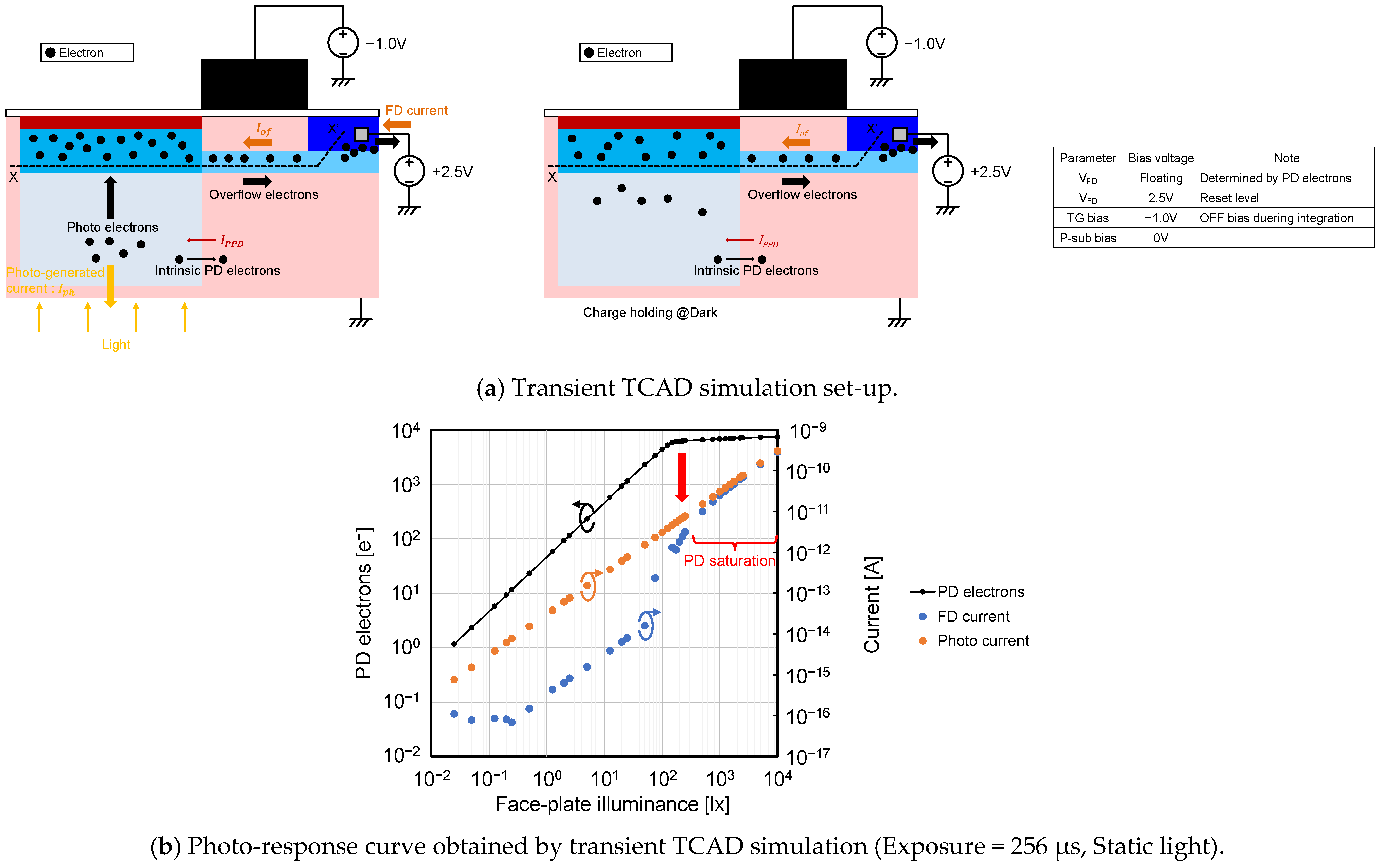

3.3. Simulation and Measurement Set-Up for Light Intensity and Charge Holding Time Dependence of PDFWC

3.4. Light Intensity Dependence Validation

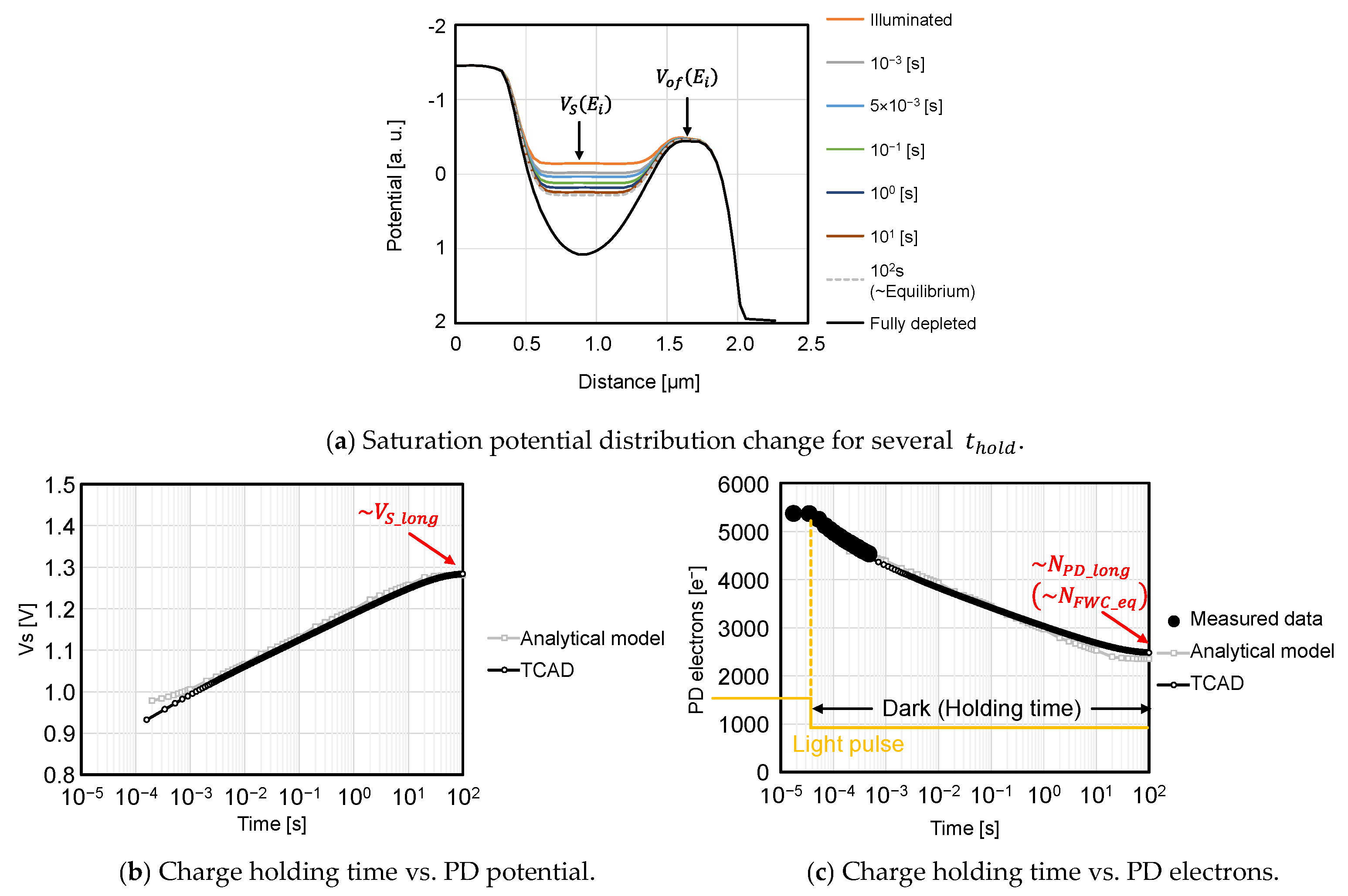

3.5. Charge Holding Time Dependence Validation

3.6. Equilibrium PDFWC Validation

4. Conclusions

Author Contributions

Funding

Institutional Review Board Statement

Informed Consent Statement

Data Availability Statement

Acknowledgments

Conflicts of Interest

Abbreviations

| Symbol | Parameter |

| Non-ideality factor | |

| Thermal voltage [V] | |

| Boltzmann constant [J/K] | |

| Temperature [K] | |

| Unit electron charge [C] | |

| Responsivity [e−/lx·s] | |

| Face-plate illuminance [lx] | |

| Constant integration | |

| Intrinsic fermi level [V] | |

| PD capacitance [F] | |

| PDFWC [e−] | |

| Equilibrium PDFWC [e−] | |

| PD electrons [e−] | |

| PD electrons after long [e−] | |

| Photo-generated current [A] | |

| Intrinsic PD current [A] (Current flowing from P-type Si to N-type Si) | |

| Overflow current [A] (Current flowing from FD to N-type PD) | |

| PN junction current at reverse bias condition [A] | |

| Overflow current at [A] | |

| PD potential [V] | |

| The minimum PD potential under PD saturation [V] | |

| PD potential after long [V] | |

| Overflow potential at the buried overflow path [V] | |

| The maximum PD fully depleted potential [V] | |

| Overflow barrier height [V] |

References

- Sugawa, S.; Akahane, N.; Adachi, S.; Mori, K.; Ishiuchi, T.; Mizobuchi, K. A 100 dB dynamic range CMOS image sensor using a lateral overflow integration capacitor. In Proceedings of the ISSCC. 2005 IEEE International Digest of Technical Papers. Solid-State Circuits Conference, San Francisco, CA, USA, 10 February 2005; pp. 352–353. [Google Scholar]

- Akahane, N.; Sugawa, S.; Adachi, S.; Mori, K.; Ishiuchi, T.; Mizobuchi, K. A Sensitivity and Linearity Improvement of a 100 dB Dynamic Range CMOS Image Sensor Using a Lateral Overflow Integration Capacitor. IEEE J. Solid State Circuits 2006, 41, 851–858. [Google Scholar] [CrossRef]

- Akahane, N.; Adachi, S.; Mizobuchi, K.; Sugawa, S. Optimum design of conversion gain and full well capacity in CMOS image sensor with lateral overflow integration capacitor. IEEE Trans. Electron Devices 2009, 56, 2429–2435. [Google Scholar] [CrossRef]

- Miyauchi, K.; Okura, S.; Mori, K.; Takayanagi, I.; Nakamura, J.; Sugawa, S. A high optical performance 2.8 µm BSI LOFIC pixel with 120ke- FWC and 160µV/e- conversion gain. In Proceedings of the International Image Sensor Workshop, Snowbird, UT, USA, 24–27 June 2019; pp. 246–249. [Google Scholar]

- Takayanagi, I.; Miyauchi, K.; Okura, S.; Mori, K.; Nakamura, J.; Sugawa, S. A 120-ke− Full-Well Capacity 160-µV/e− Conversion Gain 2.8-µm Backside-Illuminated Pixel with a Lateral Overflow Integration capacitor. Sensors 2019, 19, 5572. [Google Scholar] [CrossRef] [PubMed]

- Miyauchi, K.; Mori, K.; Isozaki, T.; Sawai, Y.; Yasuda, N.; Chien, H.-C.; Fu, K.-W.-C.; Takayanagi, I.; Nakamura, J. 4.0 μm Stacked Voltage Mode Global Shutter Pixels with Single Exposure High Dynamic Range and Phase Detection Auto Focus Capability. ITE Trans. Media Technol. Appl. 2022, 10, 234–242. [Google Scholar] [CrossRef]

- Ikeno, R.; Mori, K.; Uno, M.; Miyauchi, K.; Isozaki, T.; Takayanagi, I.; Nakamura, J.; Wuu, S.-G.; Bainbridge, L.; Berkovich, A.; et al. A 4.6-μm, 127-dB dynamic range, ultra-low power stacked digital pixel sensor with overlapped triple quantization. IEEE Trans. Electron Devices 2022, 69, 2943–2950. [Google Scholar] [CrossRef]

- Ikeno, R.; Mori, K.; Uno, M.; Miyauchi, K.; Isozaki, T.; Abe, H.; Nagamatsu, M.; Takayanagi, I.; Nakamura, J.; Wuu, S.-G.; et al. Evolution of a 4.6 μm, 512 × 512, ultra-low power stacked digital pixel sensor for performance and power efficiency improvement. In Proceedings of the 2023 International Image Sensor Workshop, Scotland, UK, 21–25 May 2023. P40. [Google Scholar]

- Isozaki, T.; Mori, K.; Miyauchi, K.; Uno, M.; Ikeno, R.; Takayanagi, I.; Nakamura, J.; Wuu, S.-G.; Berkovich, A.; Chen, S.; et al. 110dB high dynamic range continuous non-uniform TTS and linear ADC scheme using a 4.6 μm stacked digital pixel sensor. In Proceedings of the 2023 International Image Sensor Workshop, Scotland, UK, 21–25 May 2023. R4.4. [Google Scholar]

- Teranishi, N.; Kohono, A.; Ishihara, Y.; Oda, E.; Arai, K. No image lag photodiode structure in the interline CCD image sensor. In Proceedings of the 1982 IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 13–15 December 1982; pp. 324–327. [Google Scholar]

- Fossum, E.-R.; Hondongwa, D.-B. A review of the pinned photodiode for CCD and CMOS image sensors. J. Electron Devices Soc. 2014, 2, 33–43. [Google Scholar] [CrossRef]

- Teranishi, N. Effect and limitation of pinned photodiode. IEEE Trans. Electron Devices 2016, 63, 10–15. [Google Scholar] [CrossRef]

- Pelamatti, A.; Goiffon, V.; Estribeau, M.; Cervantes, P.; Magnan, P. Estimation and modeling of the full well capacity in pinned photodiode CMOS image sensors. IEEE Electron Devices Lett. 2013, 34, 900–902. [Google Scholar] [CrossRef]

- Pelamatti, A.; Belloir, J.-M.; Messien, C.; Goiffon, V.; Estribeau, M.; Magnan, P.; Virmontois, C.; Saint-Pé, O.; Paillet, P. Temperature dependence and dynamic behavior of full well capacity in pinned photodiode CMOS image sensors. IEEE Trans. Electron Devices 2015, 62, 1200–1207. [Google Scholar] [CrossRef]

- BenMoussa, A.; Giordanengo, B.; Gissot, S.; Meynants, G.; Wang, X.; Wolfs, B.; Bogaerts, J.; Schühle, U.; Berger, G.; Gottwald, A.; et al. Characterization of backside-illuminated CMOS APS prototypes for the extreme ultraviolet imager on-board solar orbiter. IEEE Trans. Electron Devices 2013, 60, 1701–1708. [Google Scholar] [CrossRef]

- Gao, Z.; Xu, J.; Zhou, Y.; Nie, K. Analysis and modeling of the light dependent full well capacity of the 4-T pixel in CMOS image sensors. IEEE Sens. J. 2016, 16, 2367–2373. [Google Scholar] [CrossRef]

- Gao, J.; Gong, Y.; Gao, Z.; Nie, K.; Xu, J. Analytical modeling of exposure process in pinned photodiode CMOS image sensors. J. Electron Devices Soc. 2020, 8, 1063–1071. [Google Scholar] [CrossRef]

- Xu, Y.; Ge, X.; Theuwissen, A.-J.P. Investigating Transfer Gate Potential Barrier by Feed-Forward Effect Measurement. In Proceeding of the 2015 International Image Sensor Workshop, Vaals, The Netherlands, 8–11 June 2015. P5-9. [Google Scholar]

- Sarkar, M.; Büttgen, M.; Albert, J.P.; Theuwissen, A.-J.P. Feedforward effect in standard CMOS pinned photodiodes. IEEE Trans. Electron Devices 2013, 60, 1154–1161. [Google Scholar] [CrossRef]

- Goiffon, V.; Estribeau, M.; Michelot, J.; Cervantes, P.; Pelamatti, A.; Marcelot, O.; Magnan, P. Pixel level characterization of pinned photodiode and transfer gate physical parameters in CMOS image sensors. J. Electron Devices Soc. 2014, 2, 65–76. [Google Scholar] [CrossRef]

- Kawai, S.; Mutoh, N.; Teranishi, N. Thermionic-emission based barrier height analysis for precise estimation of charge handling capacity in CCD registers. IEEE Trans. Electron Devices 1997, 44, 1588–1592. [Google Scholar] [CrossRef]

- Han, H.; Park, H.; Altice, P.; Choi, W.; Lim, Y.; Lee, S.; Kang, S.; Kim, J.; Yoon, K.; Hynecek, J. Evaluation of a small negative transfer gate bias on the performance of 4T CMOS image sensor pixels. In Proceeding of the 2007 International Image Sensor Workshop, Ogunquit, ME, USA, 6–10 June 2007; pp. 238–240. [Google Scholar]

- Watanabe, T.; Park, J.; Aoyama, S.; Isobe, K.; Kawahito, S. Effects of negative bias operation and optical stress on dark current. In Proceeding of the 2009 International Image Sensor Workshop, Bergen, Norway, 22–28 June 2009. P4. [Google Scholar]

- Watanabe, T.; Park, J.; Aoyama, S.; Isobe, K.; Kawahito, S. Effects of negative-bias operation and optical stress on dark current in CMOS image sensors. IEEE Trans. Electron Devices 2010, 57, 1512–1518. [Google Scholar] [CrossRef]

- Miyauchi, K.; Isozaki, T.; Ikeno, R.; Nakamura, J. Light intensity and charge holding time dependence of pinned photodiode full well capacity. In Proceeding of the 2023 International Image Sensor Workshop, Scotland, UK, 21–25 May 2023. R3.4. [Google Scholar]

- Alaibakhsh, H.; Karami, M.-A. Analytical modeling of pinning process in pinned photodiodes. IEEE Trans. Electron Devices 2018, 65, 4362–4368. [Google Scholar] [CrossRef]

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2023 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Miyauchi, K.; Isozaki, T.; Ikeno, R.; Nakamura, J. Analysis of Light Intensity and Charge Holding Time Dependence of Pinned Photodiode Full Well Capacity. Sensors 2023, 23, 8847. https://doi.org/10.3390/s23218847

Miyauchi K, Isozaki T, Ikeno R, Nakamura J. Analysis of Light Intensity and Charge Holding Time Dependence of Pinned Photodiode Full Well Capacity. Sensors. 2023; 23(21):8847. https://doi.org/10.3390/s23218847

Chicago/Turabian StyleMiyauchi, Ken, Toshiyuki Isozaki, Rimon Ikeno, and Junichi Nakamura. 2023. "Analysis of Light Intensity and Charge Holding Time Dependence of Pinned Photodiode Full Well Capacity" Sensors 23, no. 21: 8847. https://doi.org/10.3390/s23218847