A 4H-SiC CMOS Oscillator-Based Temperature Sensor Operating from 298 K up to 573 K

Abstract

:1. Introduction

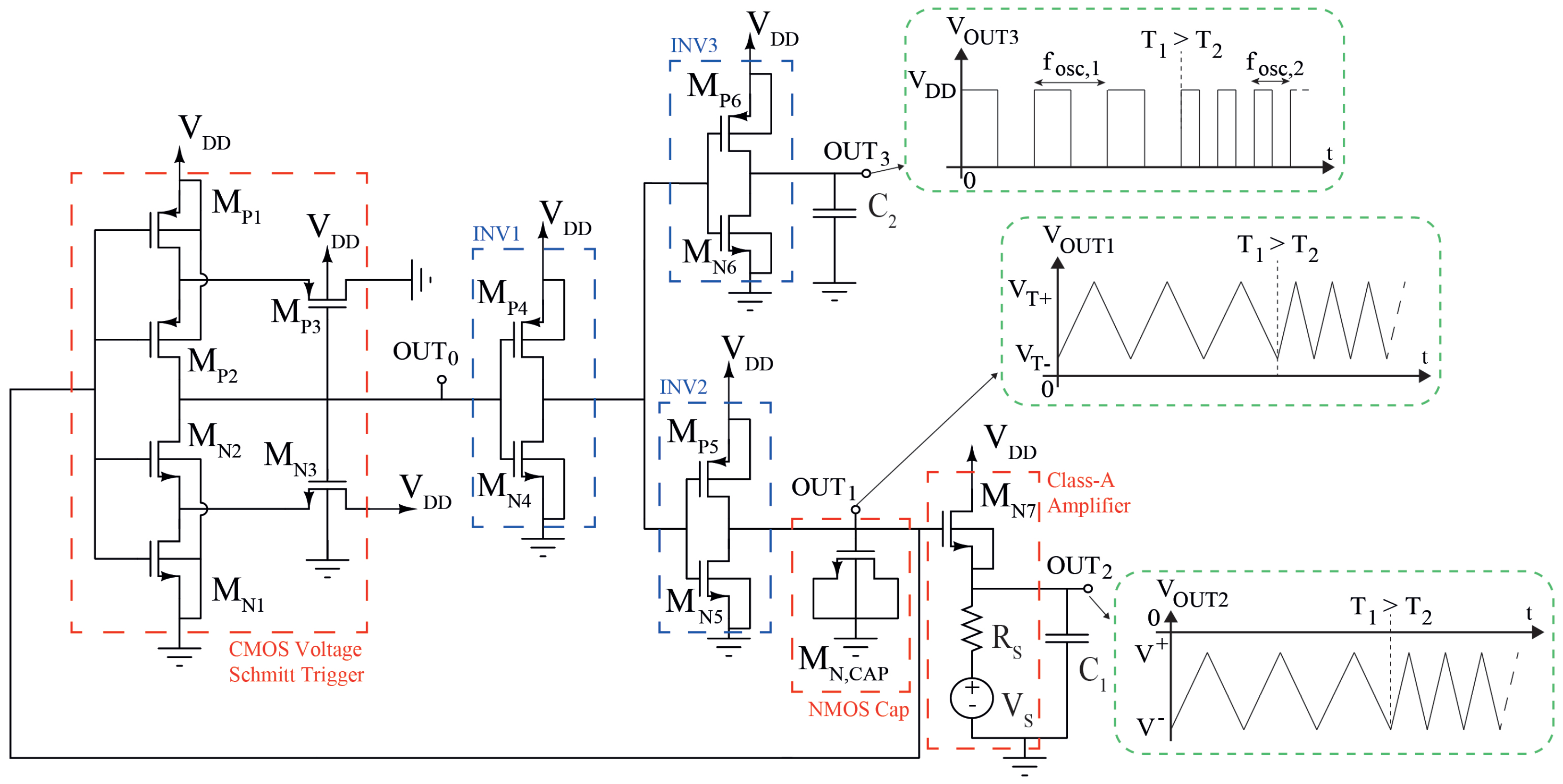

2. The Topology of the Temperature-Sensing Oscillator

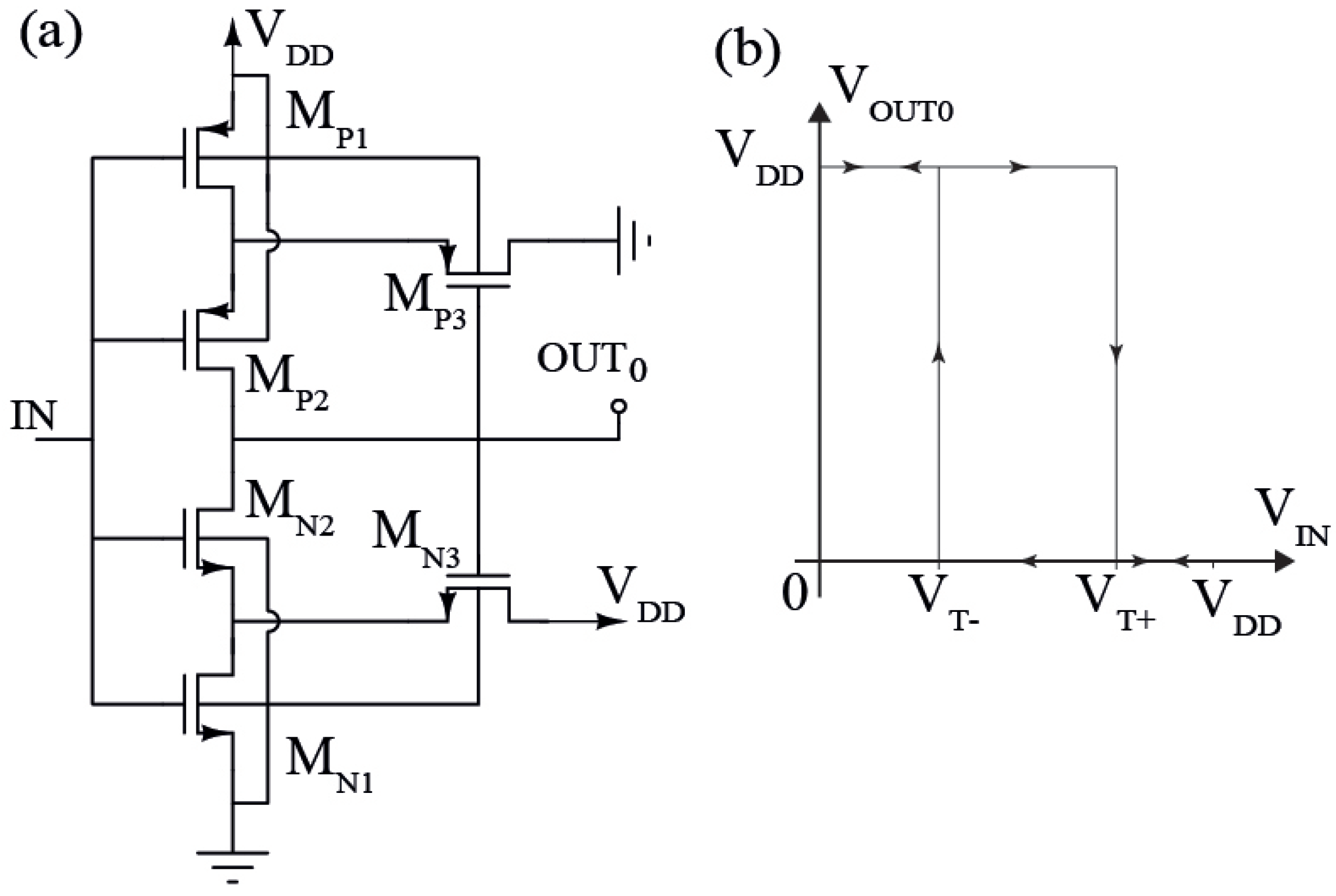

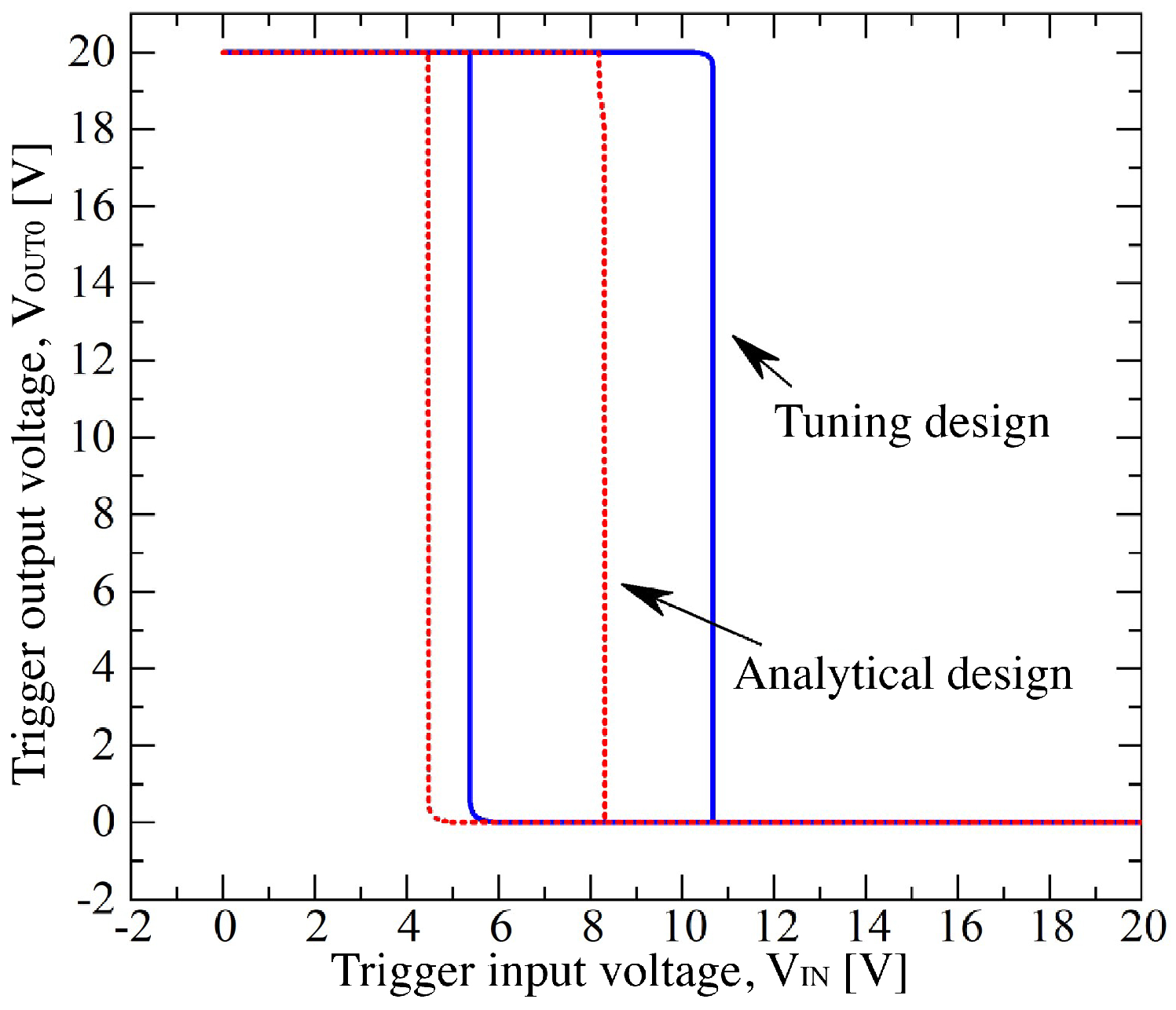

2.1. CMOS Voltage Schmitt Trigger

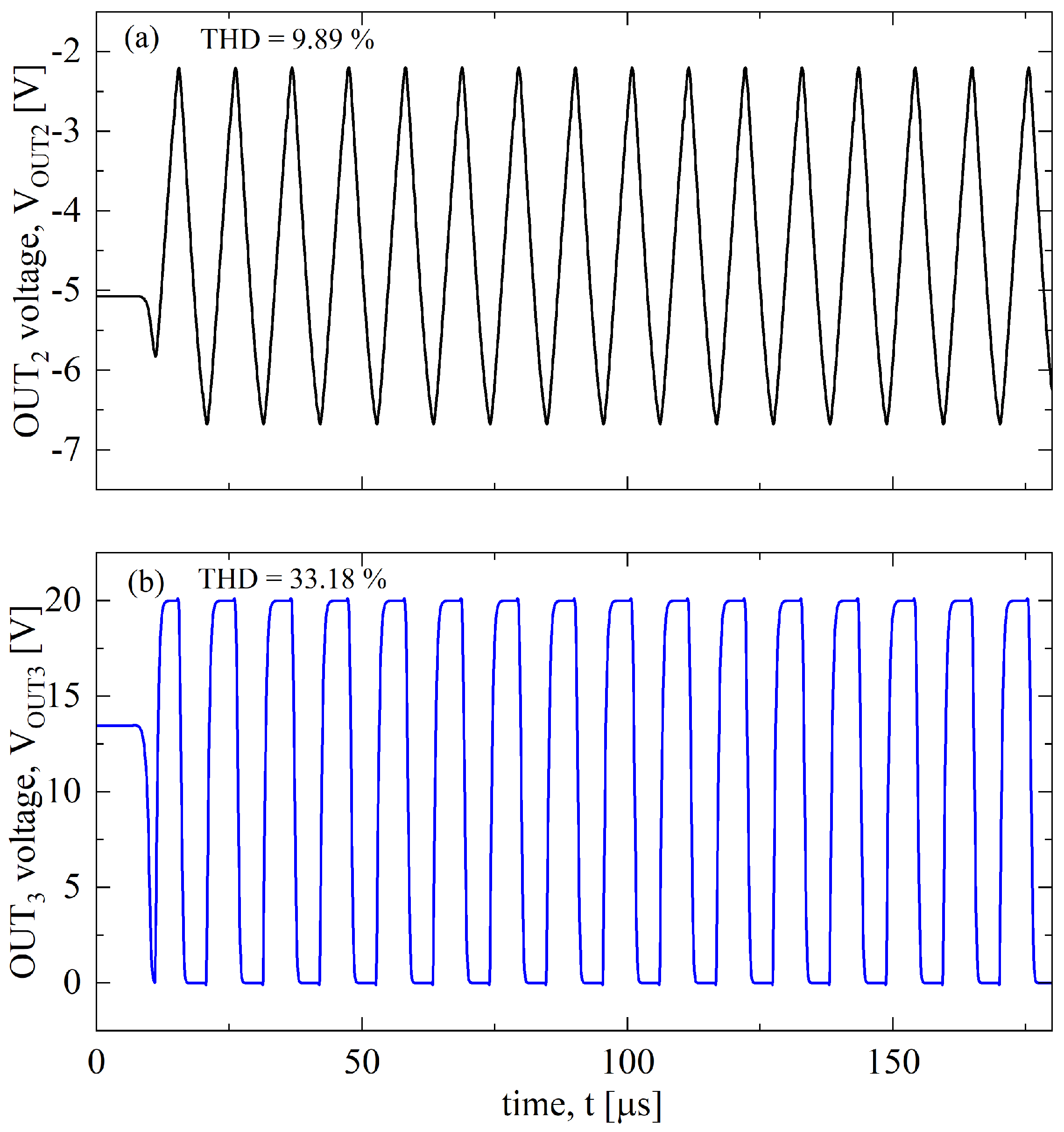

2.2. Integrator and Output Stages

2.3. Evaluation of the Oscillation Frequency

- for that is higher than other capacitances, one has ;

- for that is higher than the propagation delays, one obtains .

- fixing , one has ;

- fixing and , the channel widths of are calculated from (12);

- fixing , the channel widths of are calculated from (10);

2.4. Design of the Circuit

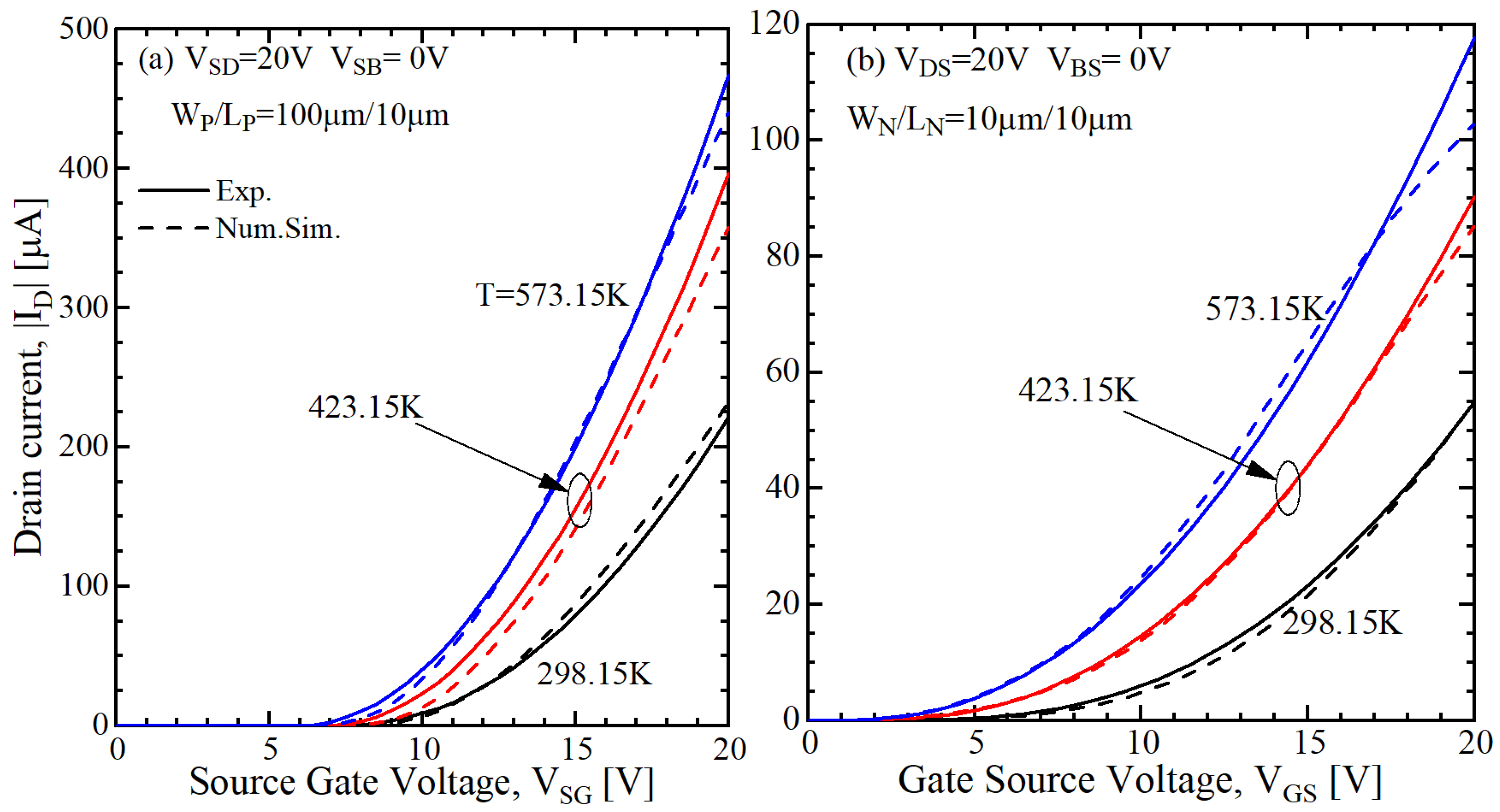

3. Numerical Simulation Results and Process Variability

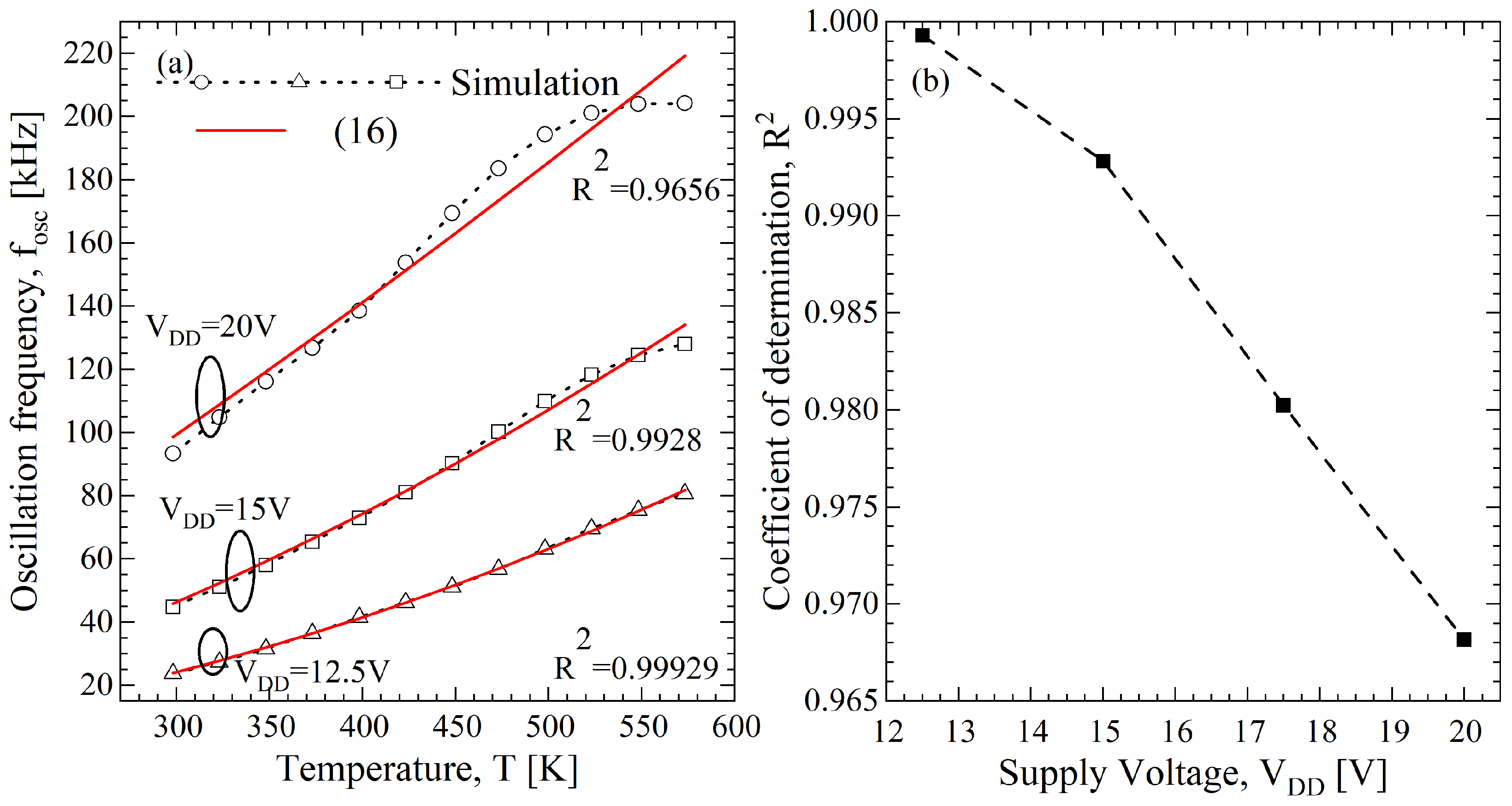

3.1. Oscillation Frequency Dependency on the Temperature

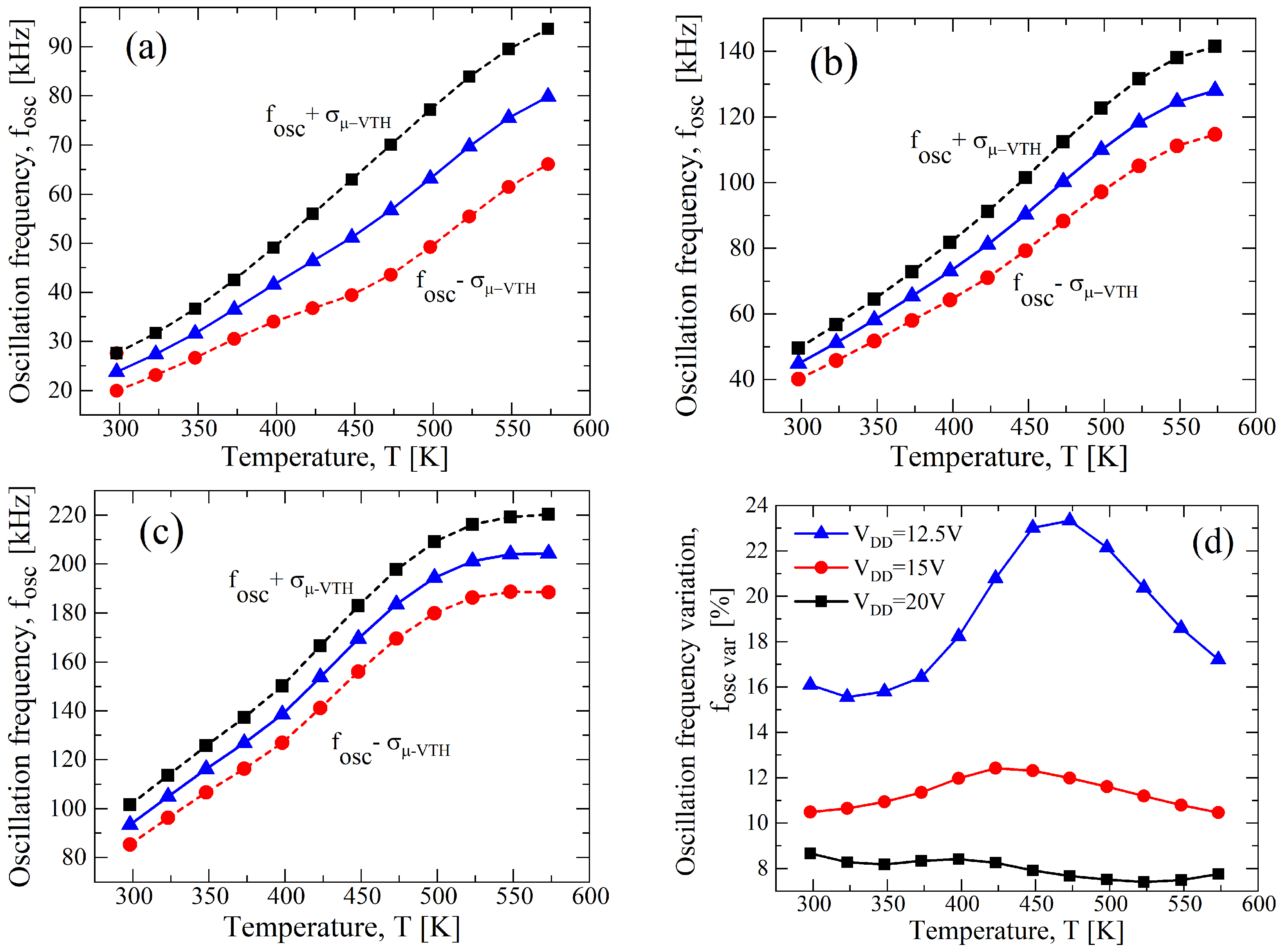

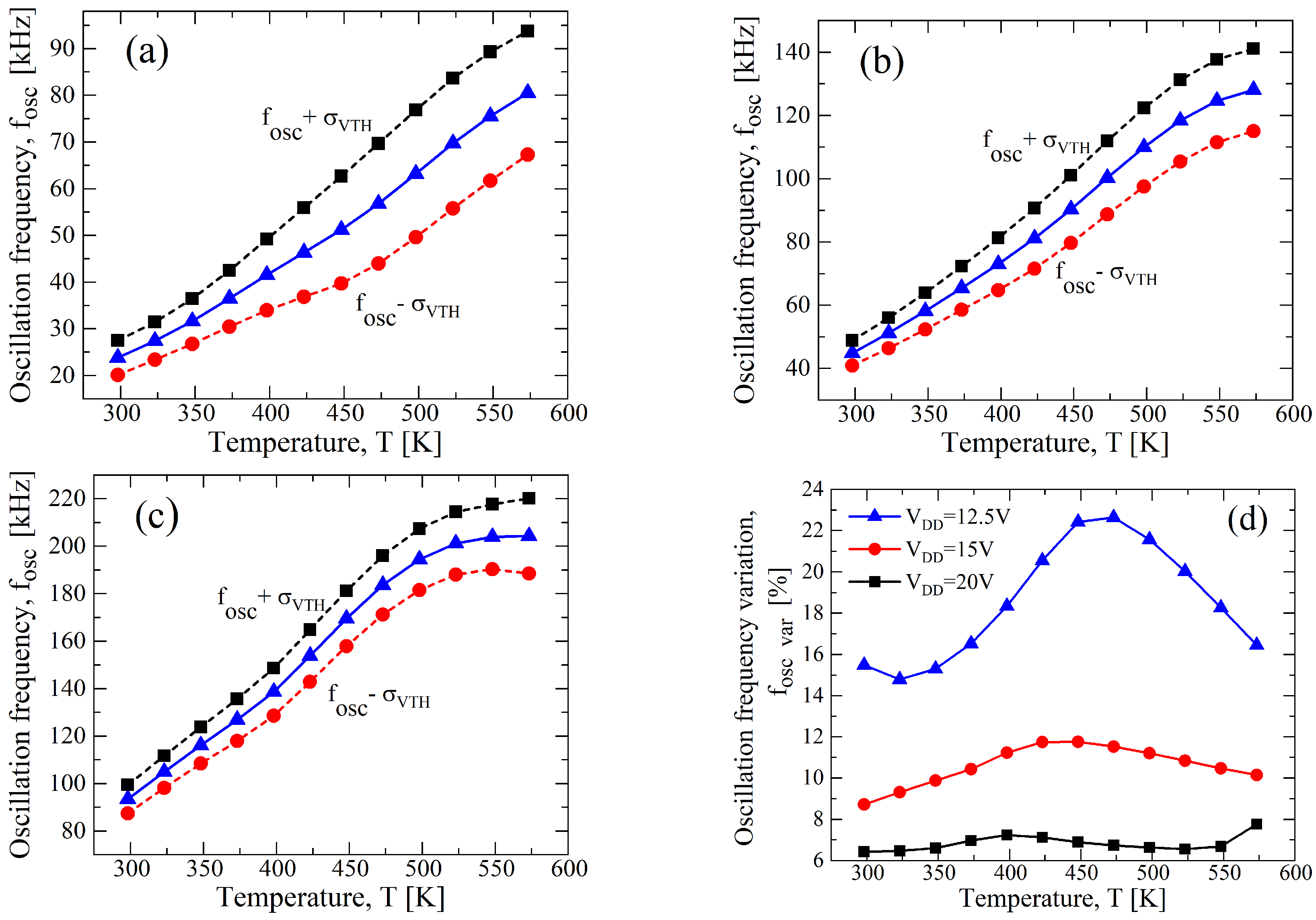

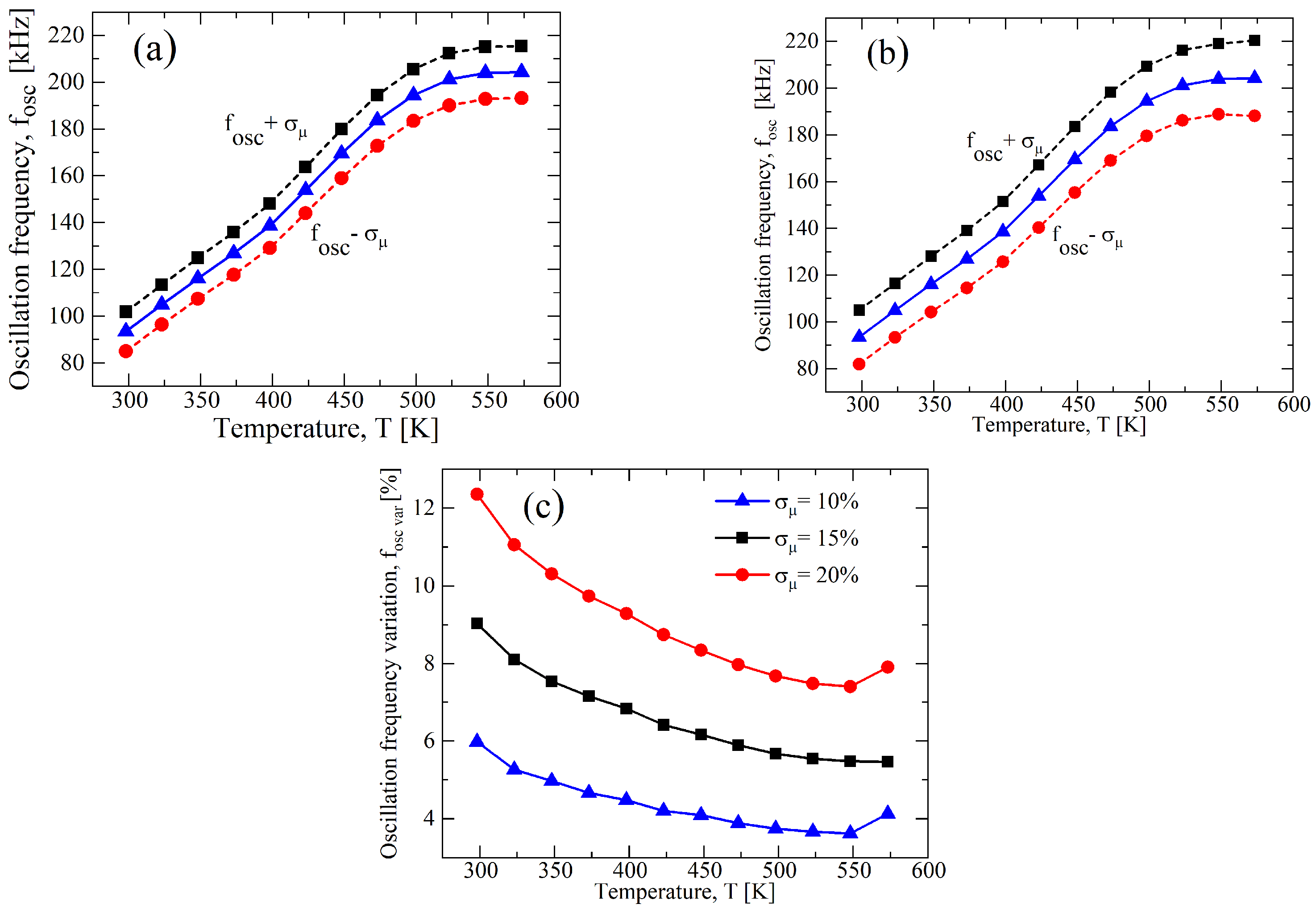

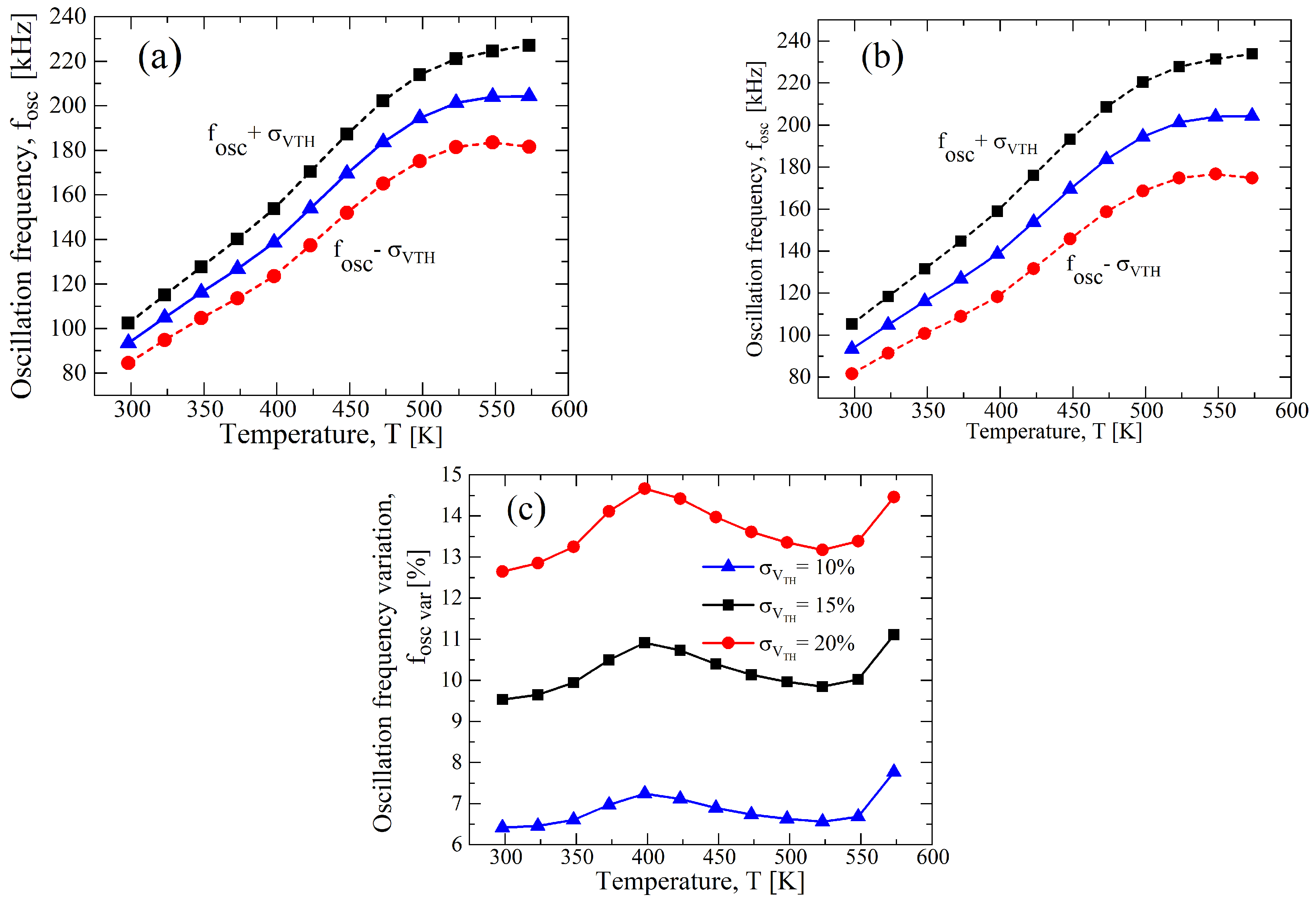

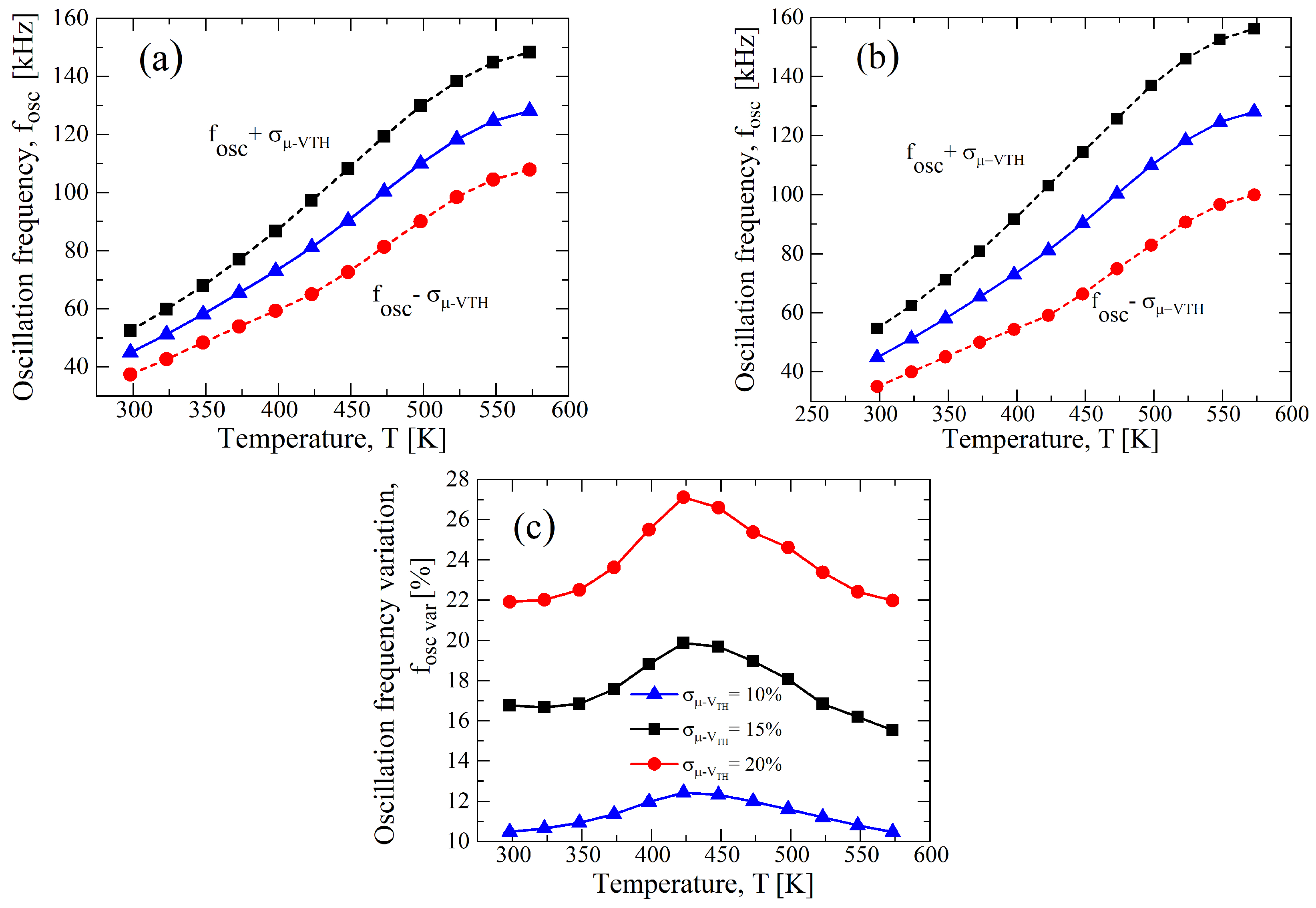

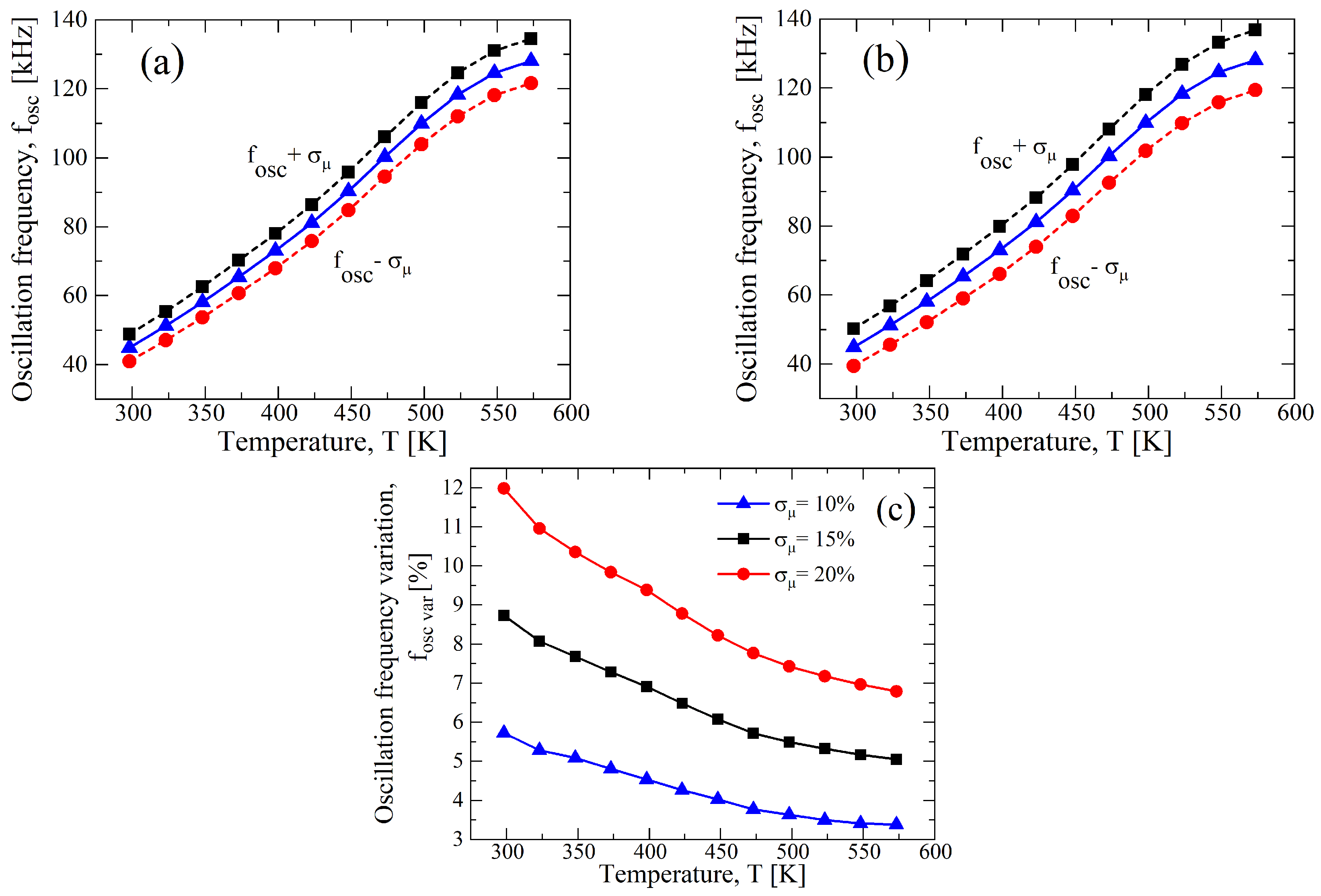

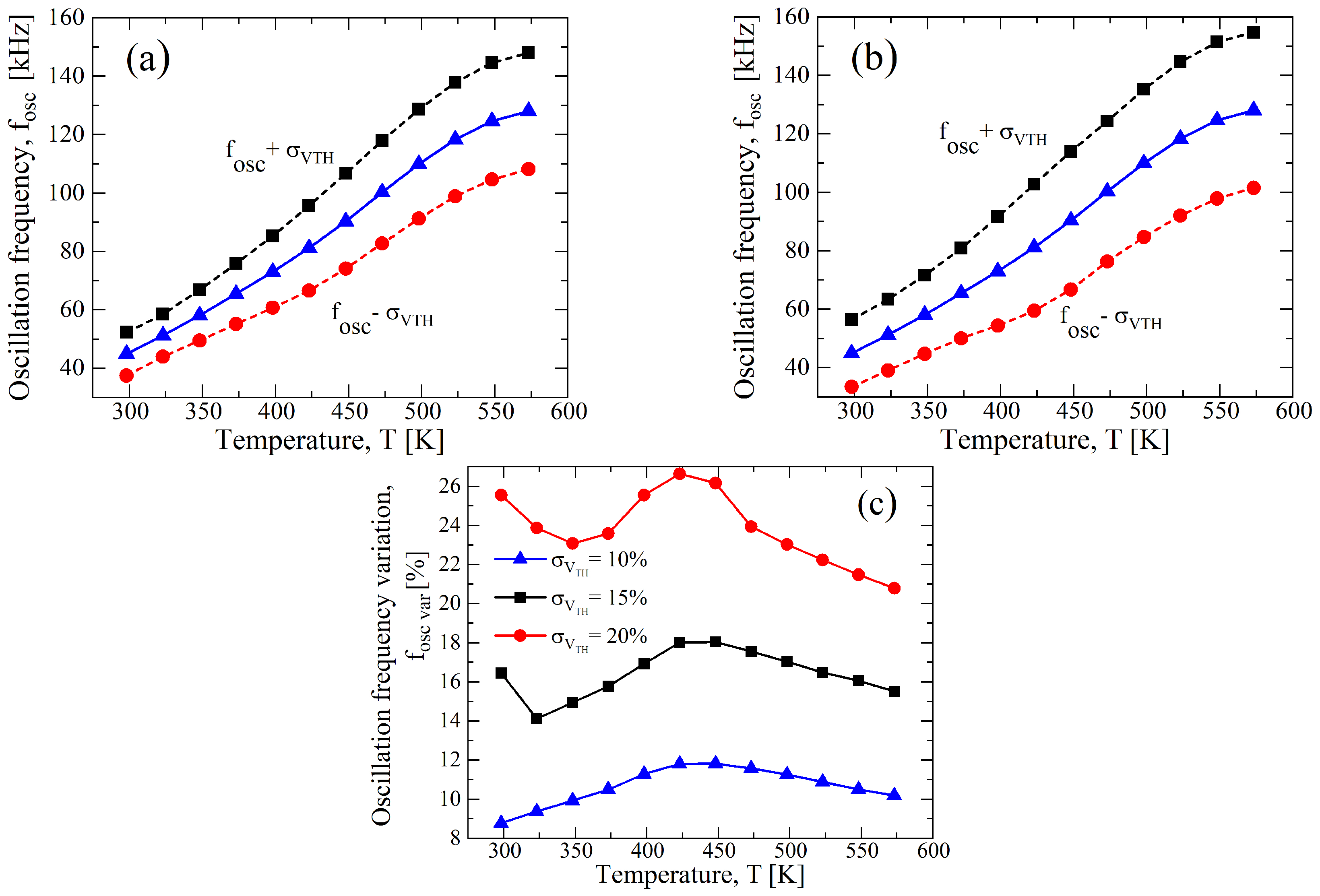

3.2. Effects of Process Parameters Variation

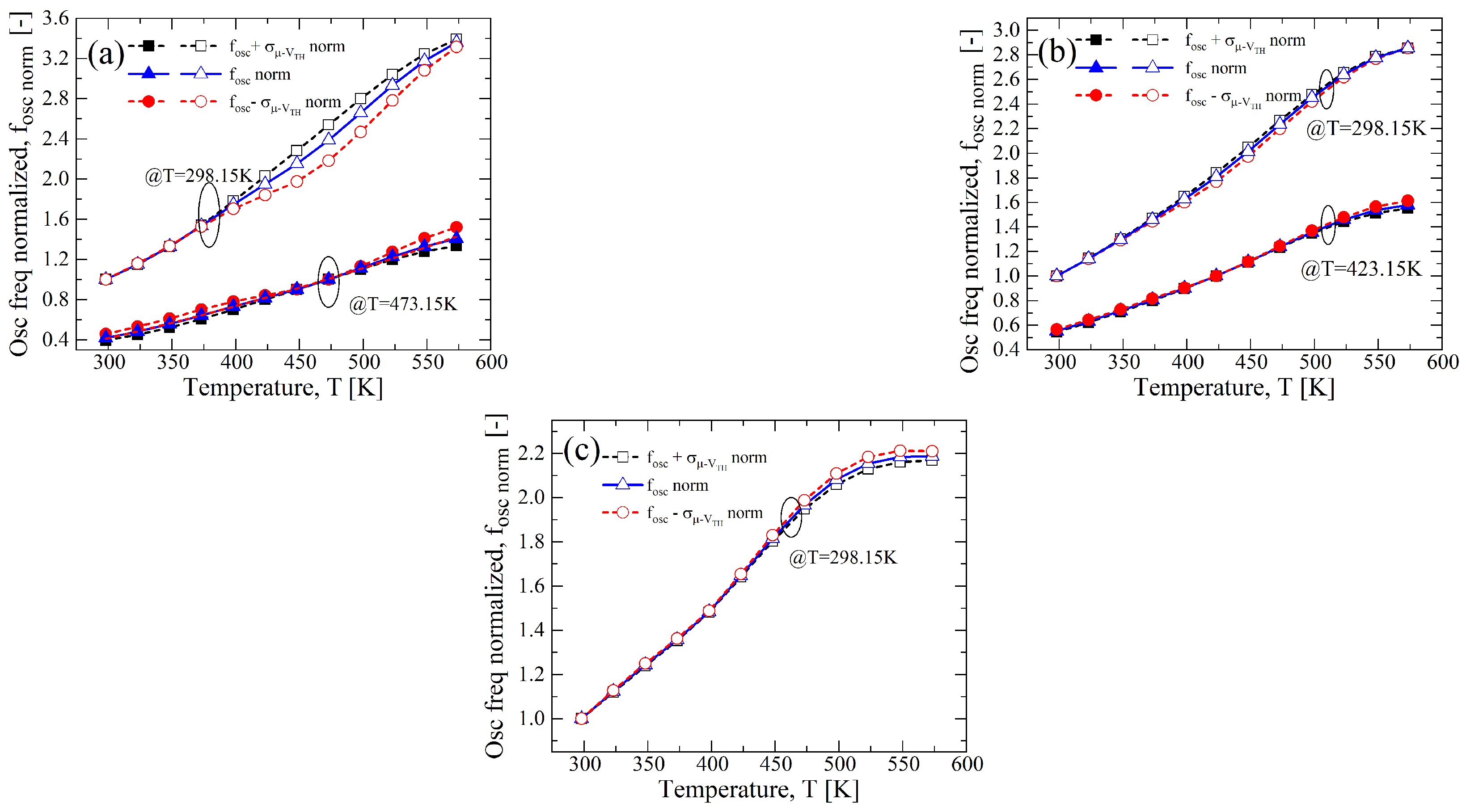

3.3. Results after Sensor Calibrations

3.4. Comparisons with the State-of-the-Art

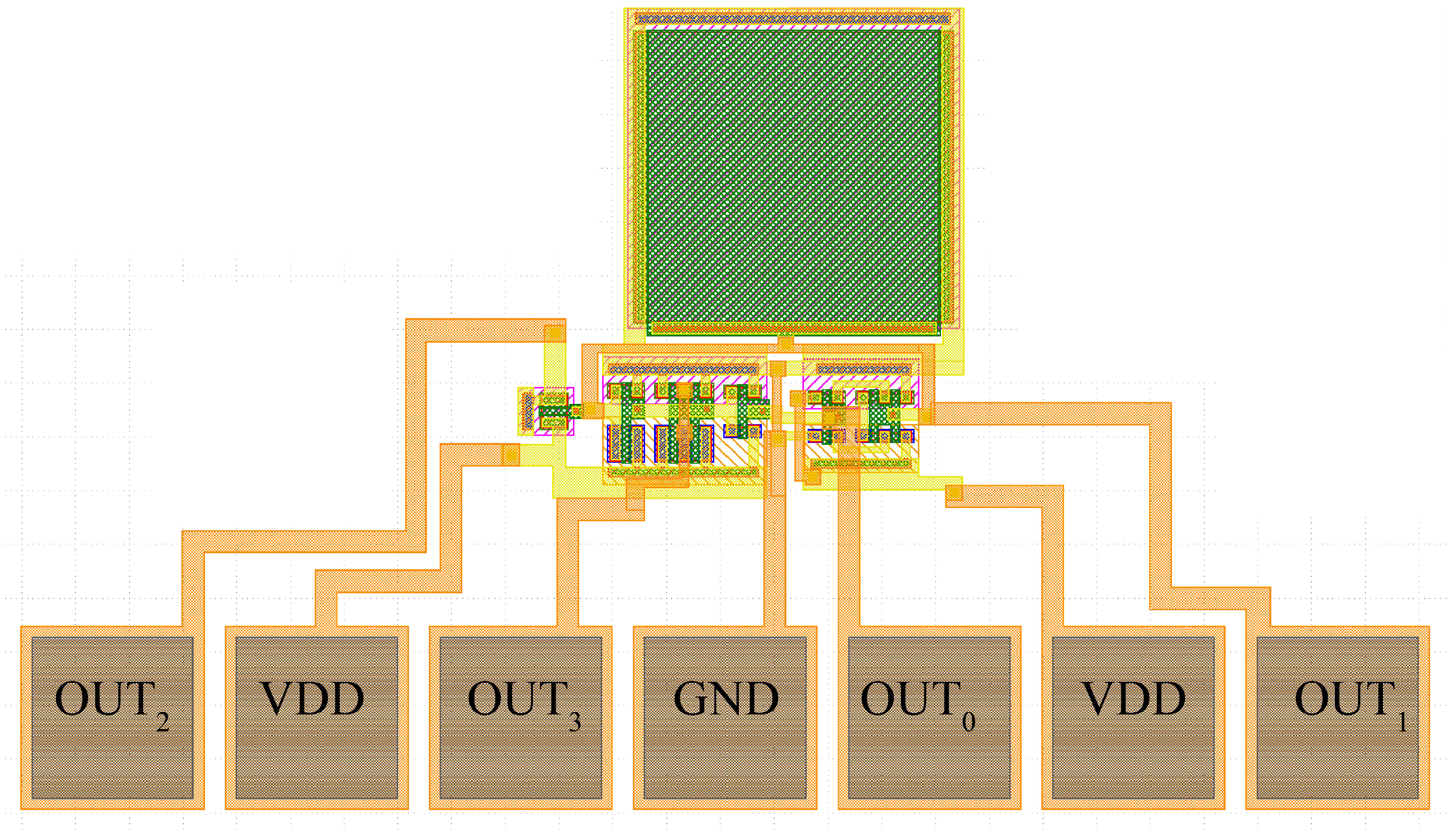

4. Layout

5. Conclusions

Author Contributions

Funding

Institutional Review Board Statement

Informed Consent Statement

Data Availability Statement

Conflicts of Interest

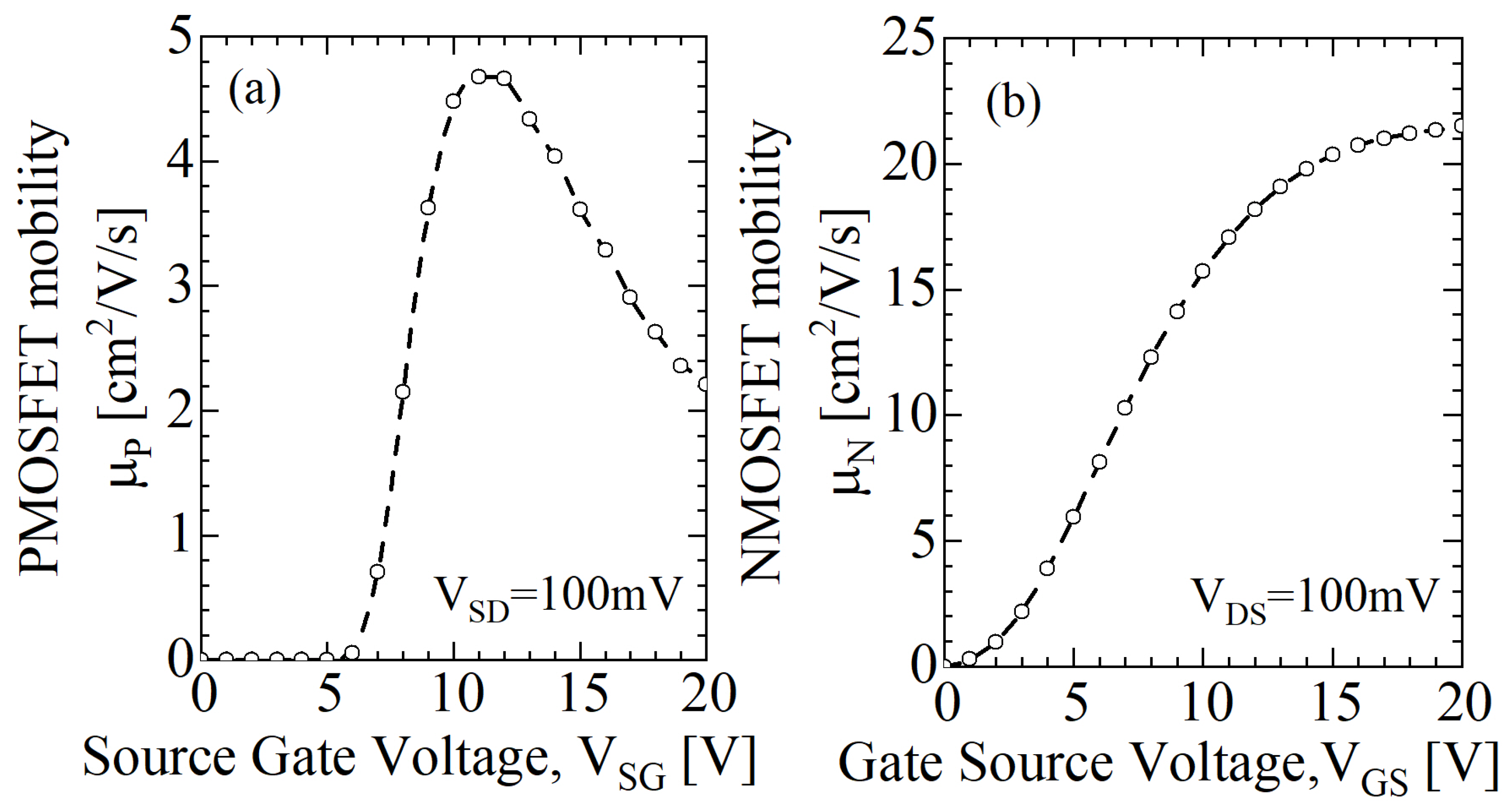

Appendix A

| Parameter | Unit | Value |

|---|---|---|

| [nm] | 55 | |

| [fFcm] | 345.31 | |

| [fFcm] | 855.30 | |

| [nFcm] | 62.78 | |

| [V] | 5.8 | |

| [V] | −8 | |

| [cmVs] | 17.14 | |

| [cmVs] | 3.52 |

References

- Kimoto, T.; Cooper, J.A. Fundamentals of Silicon Carbide Technology: Growth, Characterization, Devices and Applications; John Wiley & Sons Singapore Pte. Ltd.: Singapore, 2014. [Google Scholar]

- Zhang, N.; Lin, C.M.; Senesky, D.G.; Pisano, A.P. Temperature sensor based on 4H-silicon carbide pn diode operational from 20 °C to 600 °C. Appl. Phys. Lett. 2014, 104, 073504. [Google Scholar] [CrossRef]

- Matthus, C.D.; Di Benedetto, L.; Kocher, M.; Bauer, A.J.; Licciardo, G.D.; Rubino, A.; Erlbacher, T. Feasibility of 4H-SiC pin diode for sensitive temperature measurements between 20.5 K and 802 K. IEEE Sens. J. 2019, 19, 2871–2878. [Google Scholar] [CrossRef]

- Hussain, M.W.; Elahipanah, H.; Zumbro, J.E.; Rodriguez, S.; Malm, B.G.; Mantooth, H.A.; Rusu, A. A SiC BJT-based negative resistance oscillator for high-temperature applications. IEEE J. Electron Devices Soc. 2019, 7, 191–195. [Google Scholar] [CrossRef]

- Hedayati, R.; Lanni, L.; Rusu, A.; Zetterling, C.M. Wide temperature range integrated bandgap voltage references in 4H–SiC. IEEE Electron Device Lett. 2015, 37, 146–149. [Google Scholar] [CrossRef]

- Hedayati, R.; Lanni, L.; Rodriguez, S.; Malm, B.G.; Rusu, A.; Zetterling, C.M. A monolithic, 500 C operational amplifier in 4H-SiC bipolar technology. IEEE Electron Device Lett. 2014, 35, 693–695. [Google Scholar]

- Lanni, L.; Malm, B.G.; Östling, M.; Zetterling, C.M. ECL-based SiC logic circuits for extreme temperatures. Mater. Sci. Forum. 2015, 821–823, 910–913. [Google Scholar] [CrossRef]

- Rahman, A.; Shepherd, P.D.; Bhuyan, S.A.; Ahmed, S.; Akula, S.K.; Caley, L.; Mantooth, H.A.; Di, J.; Francis, A.M.; Holmes, J.A. A family of CMOS analog and mixed signal circuits in SiC for high temperature electronics. In Proceedings of the 2015 IEEE Aerospace Conference, Big Sky, MT, USA, 7–14 March 2015; IEEE: Piscataway, NJ, USA, 2015; pp. 1–10. [Google Scholar]

- Rahman, A.; Francis, A.M.; Ahmed, S.; Akula, S.K.; Holmes, J.; Mantooth, A. High-temperature voltage and current references in silicon carbide CMOS. IEEE Trans. Electron Devices 2016, 63, 2455–2461. [Google Scholar] [CrossRef]

- Fraunhofer Institute for Integrated Systems and Device Technology (IISB). Available online: https://www.iisb.fraunhofer.de/ (accessed on 30 September 2023).

- Romijn, J.; Middelburg, L.M.; Vollebregt, S.; El Mansouri, B.; van Zeijl, H.W.; May, A.; Erlbacher, T.; Zhang, G.; Sarro, P.M. Resistive and CTAT temperature sensors in a silicon carbide CMOS technology. In Proceedings of the 2021 IEEE Sensors, Sydney, Australia, 31 October–3 November 2021; IEEE: Piscataway, NJ, USA, 2021; pp. 1–4. [Google Scholar]

- Di Benedetto, L.; Licciardo, G.; Erlbacher, T.; Bauer, A.; Rubino, A. A 4H-SiC UV phototransistor with excellent optical gain based on controlled potential barrier. IEEE Trans. Electron Devices 2019, 67, 154–159. [Google Scholar] [CrossRef]

- Mo, J.; Li, J.; Zhang, Y.; Romijn, J.; May, A.; Erlbacher, T.; Zhang, G.; Vollebregt, S. A Highly Linear Temperature Sensor Operating up to 600 °C in a 4H-SiC CMOS Technology. IEEE Electron Device Lett. 2023, 44, 995–998. [Google Scholar] [CrossRef]

- Di Benedetto, L.; Licciardo, G.D.; Rao, S.; Pangallo, G.; Della Corte, F.G.; Alfredo, R. V2O5/4H-SiC Schottky diode temperature sensor: Experiments and model. IEEE Trans. Electron Devices 2018, 65, 687–694. [Google Scholar] [CrossRef]

- Tolić, I.P.; Mikulić, J.; Schatzberger, G.; Barić, A. Design of CMOS temperature sensors based on ring oscillators in 180-nm and 110-nm technology. In Proceedings of the 2020 43rd International Convention on Information, Communication and Electronic Technology (MIPRO), Opatija, Croatia, 28 September–2 October 2020; IEEE: Piscataway, NJ, USA, 2020; pp. 104–108. [Google Scholar]

- Ha, D.; Woo, K.; Meninger, S.; Xanthopoulos, T.; Crain, E.; Ham, D. Time-domain CMOS temperature sensors with dual delay-locked loops for microprocessor thermal monitoring. IEEE Trans. Very Large Scale Integr. (VLSI) Syst. 2011, 20, 1590–1601. [Google Scholar] [CrossRef]

- Dokic, B. CMOS Schmitt triggers. In Proceedings of the IEE Proceedings G. Electronic Circuits and Systems; 1984; Volume 131, pp. 197–202. Available online: https://digital-library.theiet.org/content/journals/10.1049/ip-g-1.1984.0037 (accessed on 5 September 2023).

- Jorgensen, J.M. CMOS Schmitt Trigger. U.S. Patent 3,984,703, 5 October 1976. [Google Scholar]

- Filanovsky, I.; Baltes, H. CMOS Schmitt trigger design. IEEE Trans. Circuits Syst. I Fundam. Theory Appl. 1994, 41, 46–49. [Google Scholar] [CrossRef]

- Rabaey, J.M.; Chandrakasan, A.P.; Nikolic, B. Digital Integrated Circuits; Prentice Hall: Englewood Cliffs, NJ, USA, 2002; Volume 2. [Google Scholar]

- Cadence Design Systems. Cadence Virtuoso. Available online: https://www.cadence.com/en_US/home.html (accessed on 30 September 2023).

- Ahmed, S.; Rashid, A.U.; Hossain, M.M.; Vrotsos, T.; Francis, A.M.; Mantooth, H.A. DC modeling and geometry scaling of SiC low-voltage MOSFETs for integrated circuit design. IEEE J. Emerg. Sel. Top. Power Electron. 2019, 7, 1574–1583. [Google Scholar] [CrossRef]

- Mudholkar, M.; Mantooth, H.A. Characterization and modeling of 4H-SiC lateral MOSFETs for integrated circuit design. IEEE Trans. Electron Devices 2013, 60, 1923–1930. [Google Scholar] [CrossRef]

- Arora, N. Mosfet Modeling for VLSI Simulation: Theory and Practice; World Scientific: Singapore, 2007. [Google Scholar]

- Blagouchine, I.V.; Moreau, E. Analytic method for the computation of the total harmonic distortion by the Cauchy method of residues. IEEE Trans. Commun. 2011, 59, 2478–2491. [Google Scholar] [CrossRef]

- Nipoti, R.; Di Benedetto, L.; Albonetti, C.; Bellone, S. Al+ implanted anode for 4H-SiC pin diodes. ECS Trans. 2013, 50, 391. [Google Scholar] [CrossRef]

- May, A.; Rommel, M.; Beuer, S.; Erlbacher, T. Via size-dependent properties of TiAl ohmic contacts on 4H-SiC. Mater. Sci. Forum 2022, 1062, 185–189. [Google Scholar] [CrossRef]

- Makinwa, K.A.; Snoeij, M.F. A CMOS Temperature-to-Frequency Converter with an Inaccuracy of Less than 0.5 °C (3σ) from −40 °C to 105 °C. IEee J. Solid-State Circuits 2006, 41, 2992–2997. [Google Scholar] [CrossRef]

- Anand, T.; Makinwa, K.A.; Hanumolu, P.K. A VCO based highly digital temperature sensor with 0.034 °C/mV supply sensitivity. IEEE J. Solid-State Circuits 2016, 51, 2651–2663. [Google Scholar] [CrossRef]

- Hwang, S.; Koo, J.; Kim, K.; Lee, H.; Kim, C. A 0.008 mm2 500 μW 469 kS/s Frequency-to-Digital Converter Based CMOS Temperature Sensor with Process Variation Compensation. IEEE Trans. Circuits Syst. I Regul. Pap. 2013, 60, 2241–2248. [Google Scholar] [CrossRef]

- Cochet, M.; Keller, B.; Clerc, S.; Abouzeid, F.; Cathelin, A.; Autran, J.L.; Roche, P.; Nikolić, B. A 225 μm2 Probe Single-Point Calibration Digital Temperature Sensor Using Body-Bias Adjustment in 28 nm FD-SOI CMOS. IEEE-Solid-State Circuits Lett. 2018, 1, 14–17. [Google Scholar] [CrossRef]

- Chowdhury, G.; Hassibi, A. An on-chip temperature sensor with a self-discharging diode in 32-nm SOI CMOS. IEEE Trans. Circuits Syst. II Express Briefs 2012, 59, 568–572. [Google Scholar] [CrossRef]

- Ortiz-Conde, A.; Sánchez, F.G.; Liou, J.J.; Cerdeira, A.; Estrada, M.; Yue, Y. A review of recent MOSFET threshold voltage extraction methods. Microelectron. Reliab. 2002, 42, 583–596. [Google Scholar] [CrossRef]

- Uhnevionak, V.; Burenkov, A.; Strenger, C.; Ortiz, G.; Bedel-Pereira, E.; Mortet, V.; Cristiano, F.; Bauer, A.J.; Pichler, P. Comprehensive study of the electron scattering mechanisms in 4H-SiC MOSFETs. IEEE Trans. Electron Devices 2015, 62, 2562–2570. [Google Scholar] [CrossRef]

- Rumyantsev, S.; Shur, M.; Levinshtein, M.; Ivanov, P.; Palmour, J.; Agarwal, A.; Hull, B.; Ryu, S.H. Channel mobility and on-resistance of vertical double implanted 4H-SiC MOSFETs at elevated temperatures. Semicond. Sci. Technol. 2009, 24, 075011. [Google Scholar] [CrossRef]

- Le-Huu, M.; Schmitt, H.; Noll, S.; Grieb, M.; Schrey, F.F.; Bauer, A.J.; Frey, L.; Ryssel, H. Investigation of the reliability of 4H–SiC MOS devices for high temperature applications. Microelectron. Reliab. 2011, 51, 1346–1350. [Google Scholar] [CrossRef]

- Di Benedetto, L.; Licciardo, G.D.; Nipoti, R.; Bellone, S. On the crossing-point of 4H-SiC power diodes characteristics. IEEE Electron Device Lett. 2013, 35, 244–246. [Google Scholar] [CrossRef]

- Li, X.; Luo, Y.; Fursin, L.; Zhao, J.; Pan, M.; Alexandrov, P.; Weiner, M. On the temperature coefficient of 4H-SiC BJT current gain. Solid-State Electron. 2003, 47, 233–239. [Google Scholar] [CrossRef]

| Parameter | Unit | Value |

|---|---|---|

| [V] | 20 | |

| [V] | −8 | |

| [kHz] | 90 | |

| [pF] | 8 | |

| [pF] | 8 | |

| [m] | 6 | |

| [V] | 10 | |

| [V] | 5 |

| Parameter | Device | Value | Unit |

|---|---|---|---|

| 94 | [] |

| Parameter | Device | Value | Unit |

|---|---|---|---|

| 6/6 | |||

| 12/6 | |||

| 32/6 | |||

| 24/6 | |||

| 64/6 | |||

| 24/6 | |||

| 60 | [] |

| V | |||

| 15 V | |||

| 20 V | |||

| V | |||||||||

| V | |||||||||

| Range | Error | Bias Volt. | Power | Area | Tech. | |

|---|---|---|---|---|---|---|

| [K] | [K] | [V] | [mW] | [mm2] | ||

| This work (Num.Sim.) | 298/573 | −5.8/8.8 | 15 | 0.89 | 0.163 | 4H-SiC 2 m-CMOS |

| [16] | 273/373 | −4/4 | 1.2 | 1.2 | 0.12 | Si 130 nm-CMOS |

| [28] | 233/378 | ± 0.5 | 5 | 2.5 | 2.3 | Si 0.7 m-CMOS |

| [29] | 273/373 | −3/3 | 1 | 0.154 | 0.004 | Si 65 nm-CMOS |

| [30] | 273/383 | −1.5/1.5 | 1 | 0.5 | 0.008 | Si 65 nm-CMOS |

| [31] | 272/385 | −2.5/1.2 ( = 0.6 V) −1.4/1.3 ( = 1.2 V) | 0.6 V/1.2 V | 0.056 | 0.001 | FD-SOI 28 nm-CMOS |

| [32] | 273/373 | ±1.95 (3 | 1.65V | 0.1 | 0.001 | SOI 32 nm-CMOS |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2023 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Rinaldi, N.; Liguori, R.; May, A.; Rossi, C.; Rommel, M.; Rubino, A.; Licciardo, G.D.; Di Benedetto, L. A 4H-SiC CMOS Oscillator-Based Temperature Sensor Operating from 298 K up to 573 K. Sensors 2023, 23, 9653. https://doi.org/10.3390/s23249653

Rinaldi N, Liguori R, May A, Rossi C, Rommel M, Rubino A, Licciardo GD, Di Benedetto L. A 4H-SiC CMOS Oscillator-Based Temperature Sensor Operating from 298 K up to 573 K. Sensors. 2023; 23(24):9653. https://doi.org/10.3390/s23249653

Chicago/Turabian StyleRinaldi, Nicola, Rosalba Liguori, Alexander May, Chiara Rossi, Mathias Rommel, Alfredo Rubino, Gian Domenico Licciardo, and Luigi Di Benedetto. 2023. "A 4H-SiC CMOS Oscillator-Based Temperature Sensor Operating from 298 K up to 573 K" Sensors 23, no. 24: 9653. https://doi.org/10.3390/s23249653

APA StyleRinaldi, N., Liguori, R., May, A., Rossi, C., Rommel, M., Rubino, A., Licciardo, G. D., & Di Benedetto, L. (2023). A 4H-SiC CMOS Oscillator-Based Temperature Sensor Operating from 298 K up to 573 K. Sensors, 23(24), 9653. https://doi.org/10.3390/s23249653