Influence of Parasitic Parameters on DC–DC Converters and Their Method of Suppression in High Frequency Link 35 kV PV Systems

Abstract

:1. Introduction

- The influence of the parasitic parameters of SiC devices in high-frequency LLC converters is analyzed step by step, which is more accurate.

- The mechanism of influence of parasitic parameters on the resonance process is discussed systematically. The paper reveals how different parameters can affect the resonance process with respect to the parasitic parameters.

- The proposed method is completely different from previous studies, and achieves better performance. Since the proposed method is able to achieve ZVS without a reduction in magnetic inductance and extension of the dead band, the efficiency can be further improved.

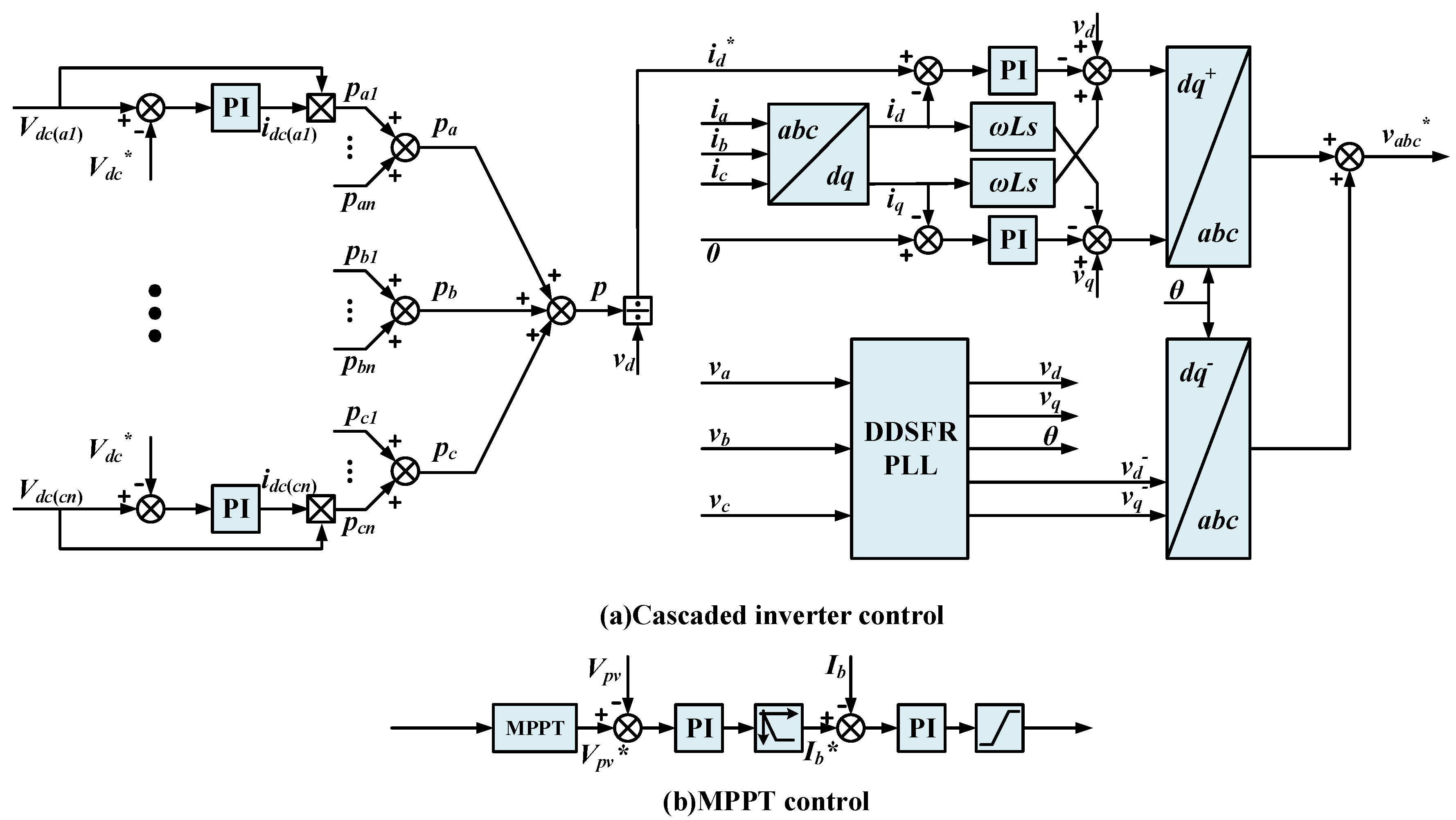

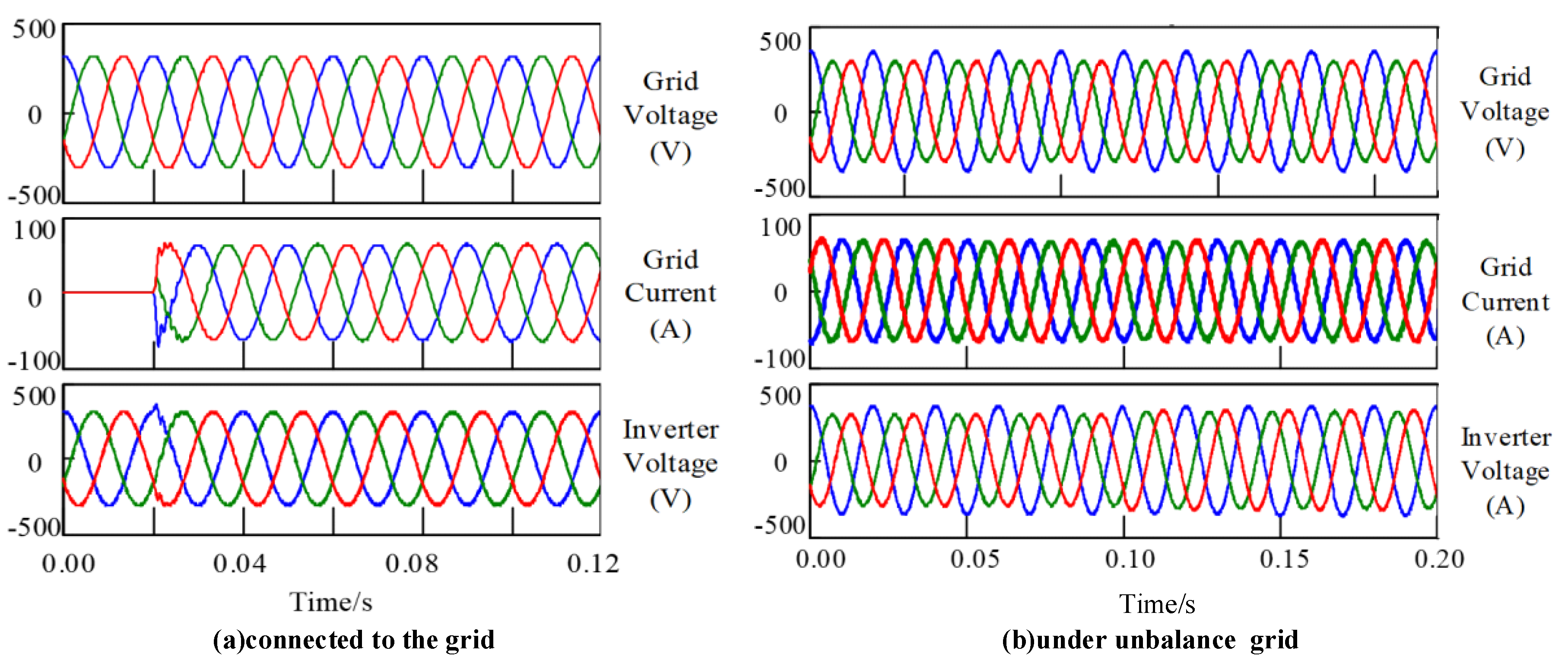

2. Architecture of High Frequency Link 35 kV PV System

3. Influences of Parasitic Parameters on the Resonance Process

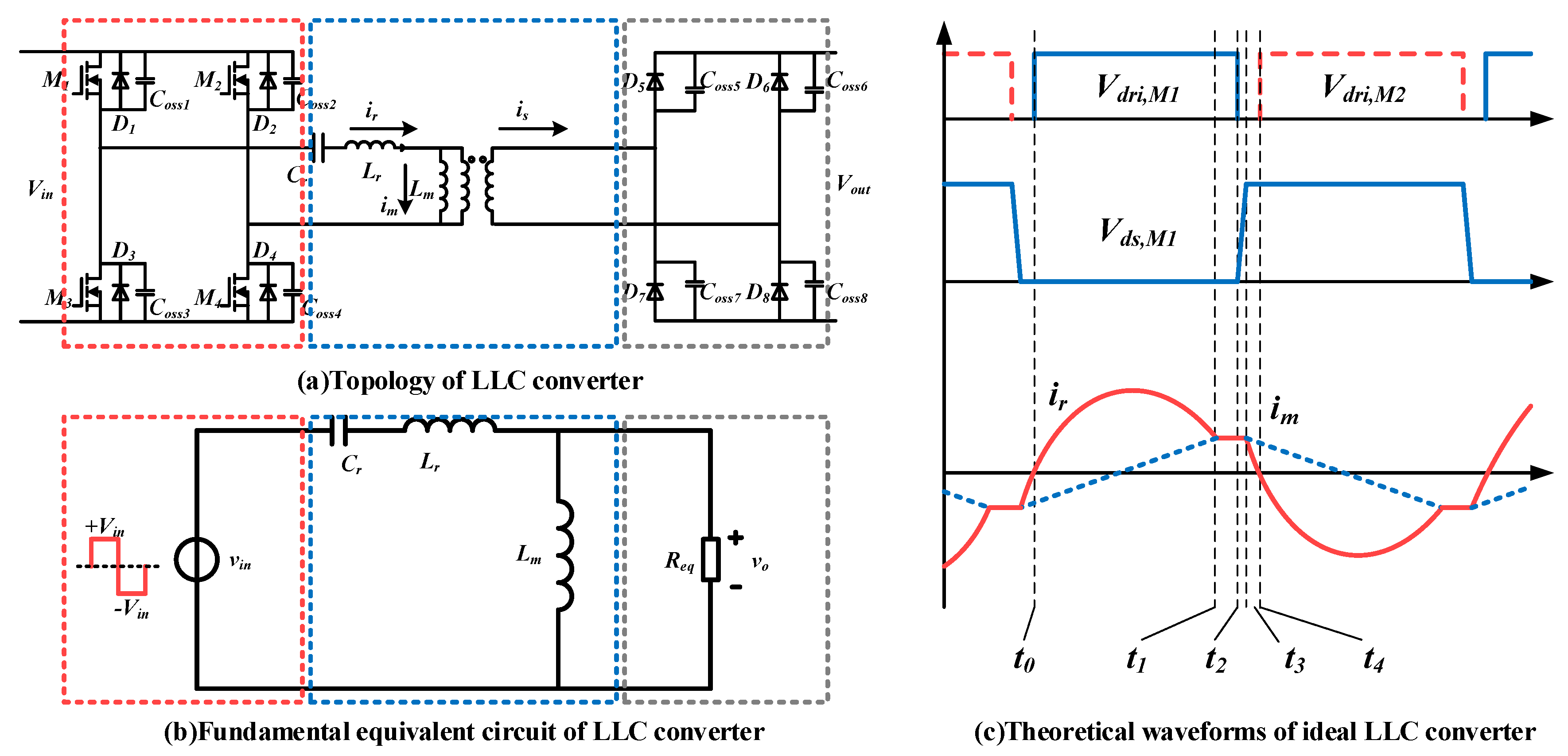

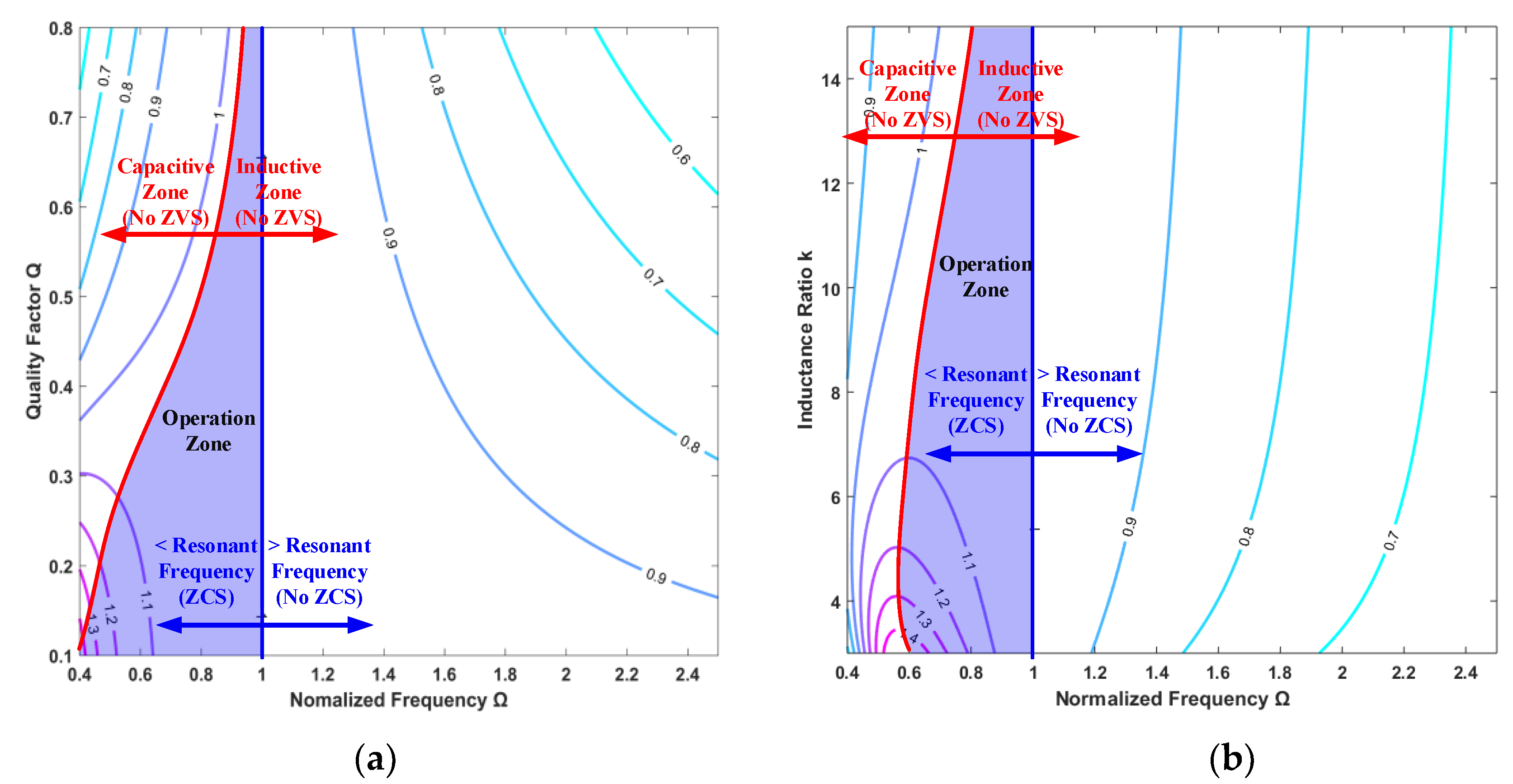

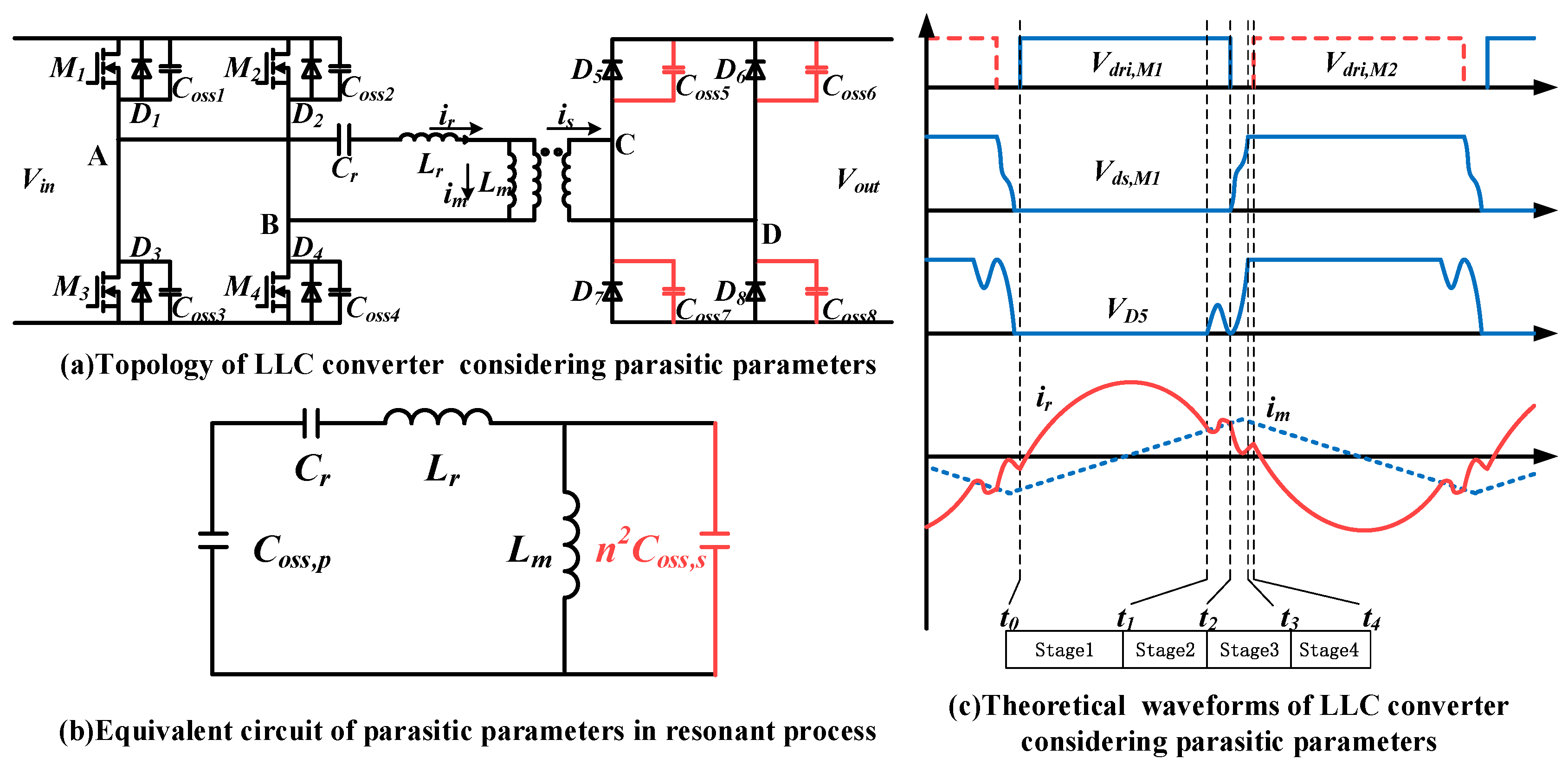

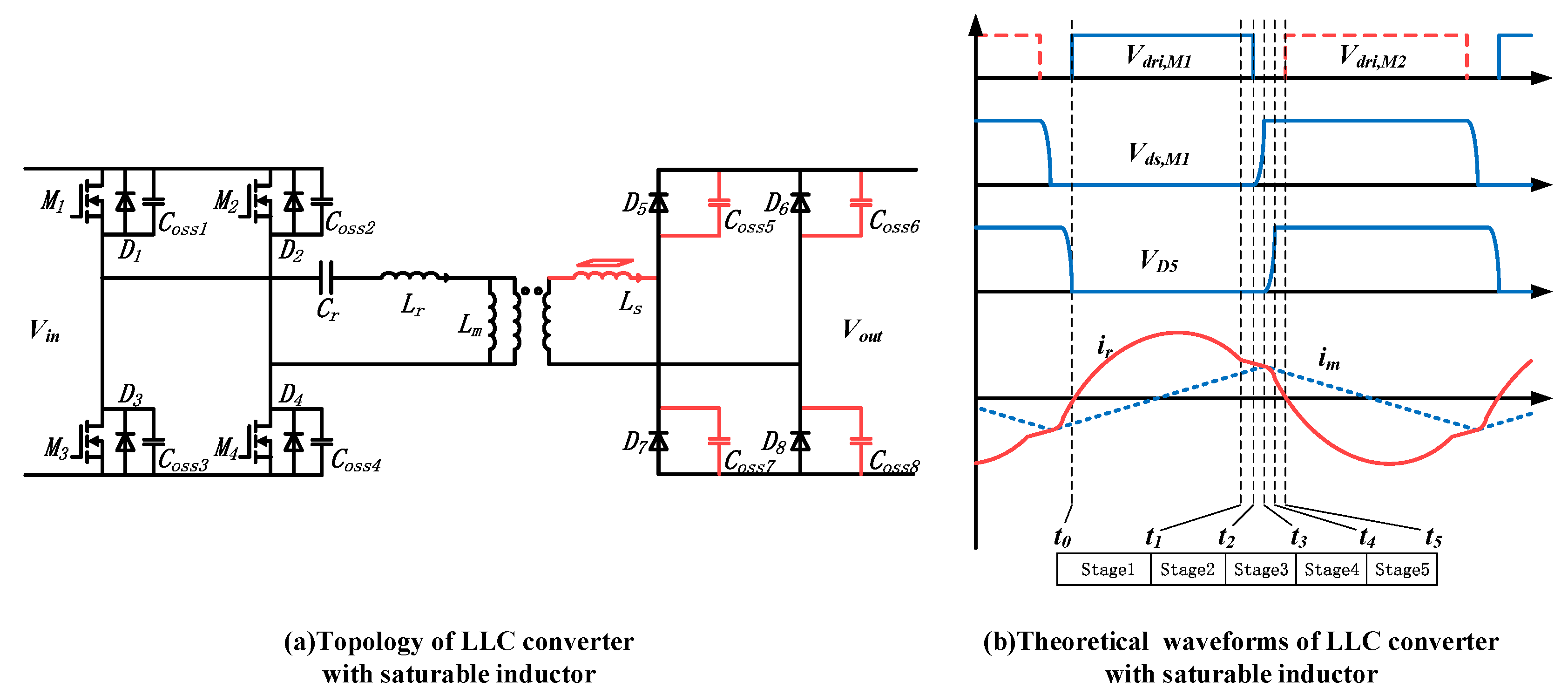

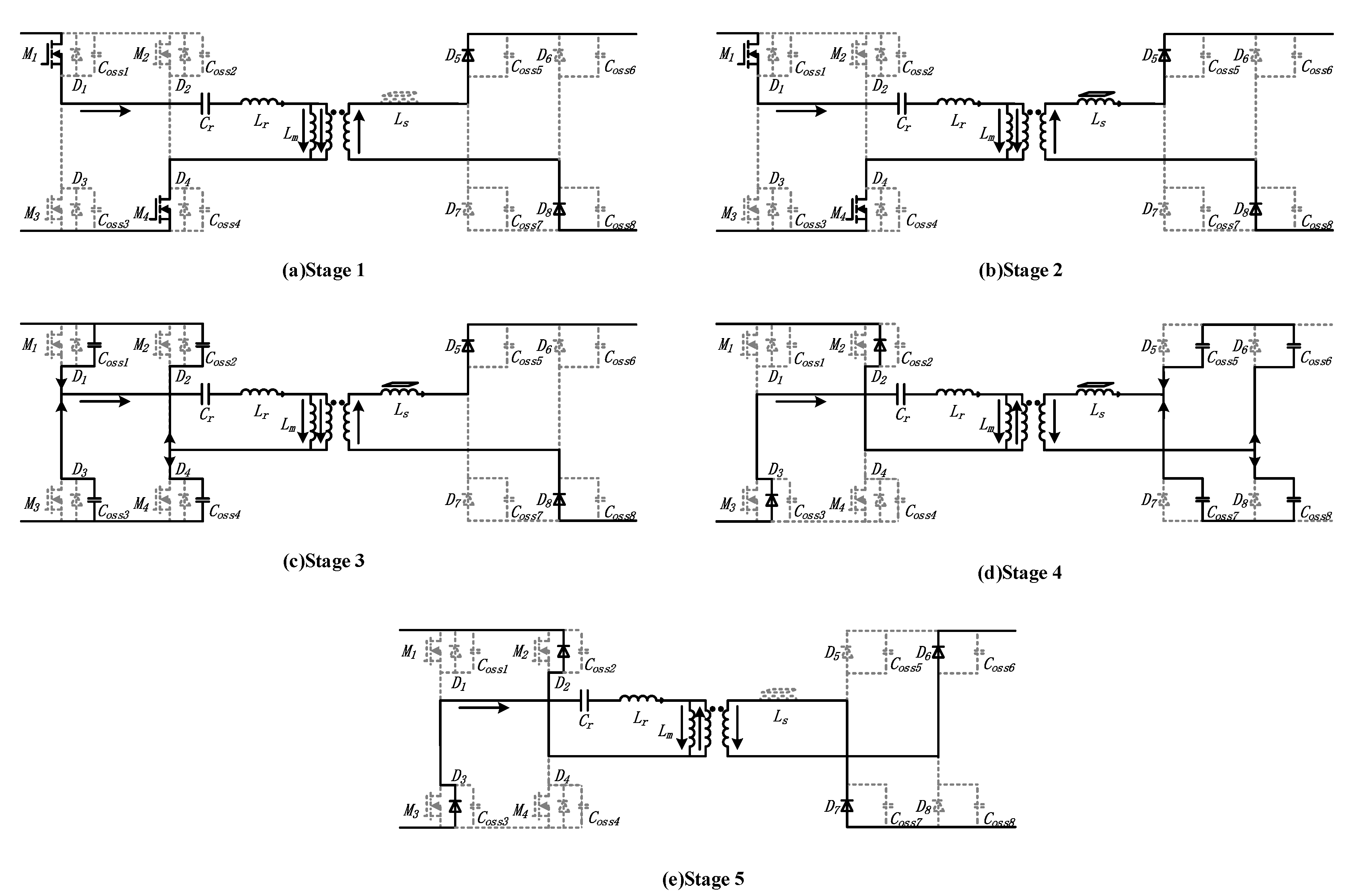

3.1. Operation Principle of the Ideal High-Frequency High Step-Up Ratio LLC Converter

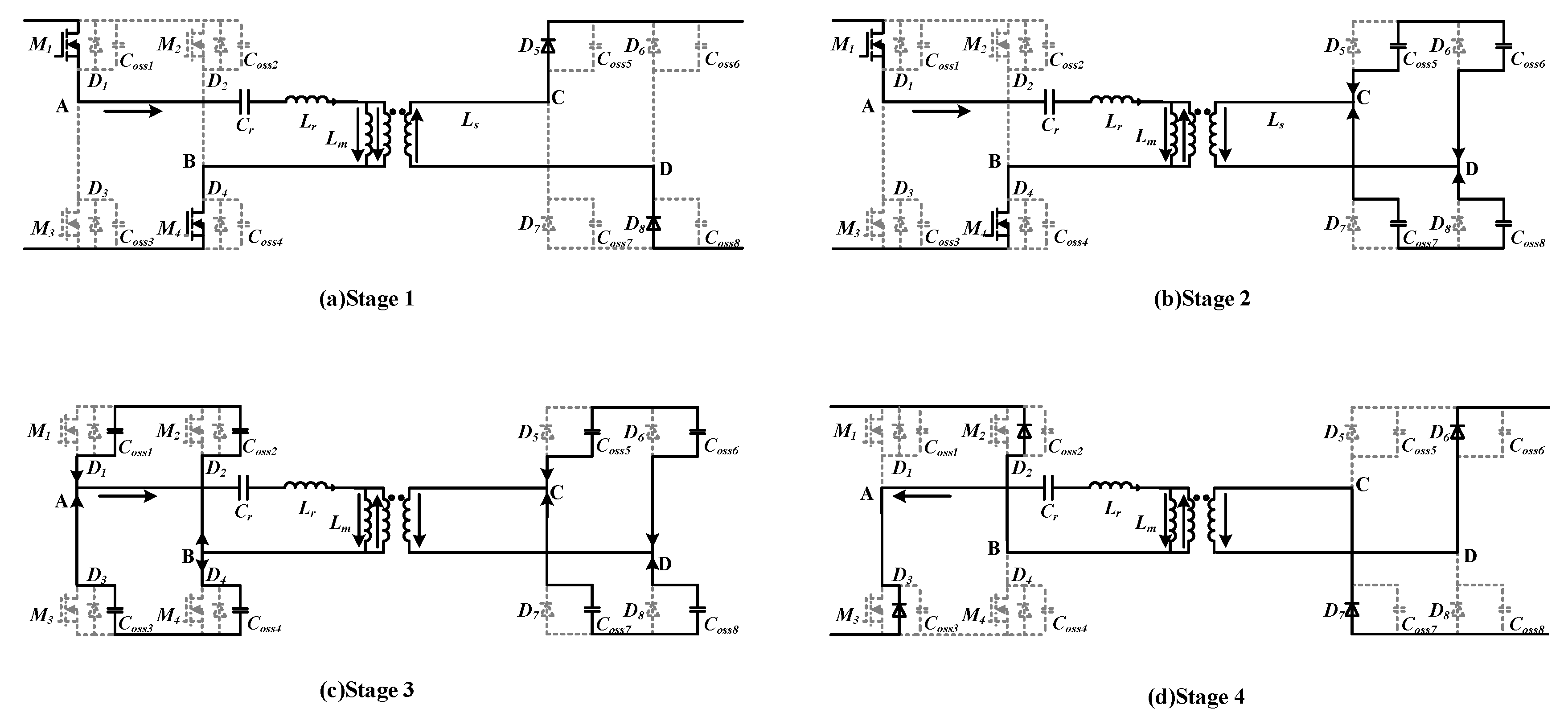

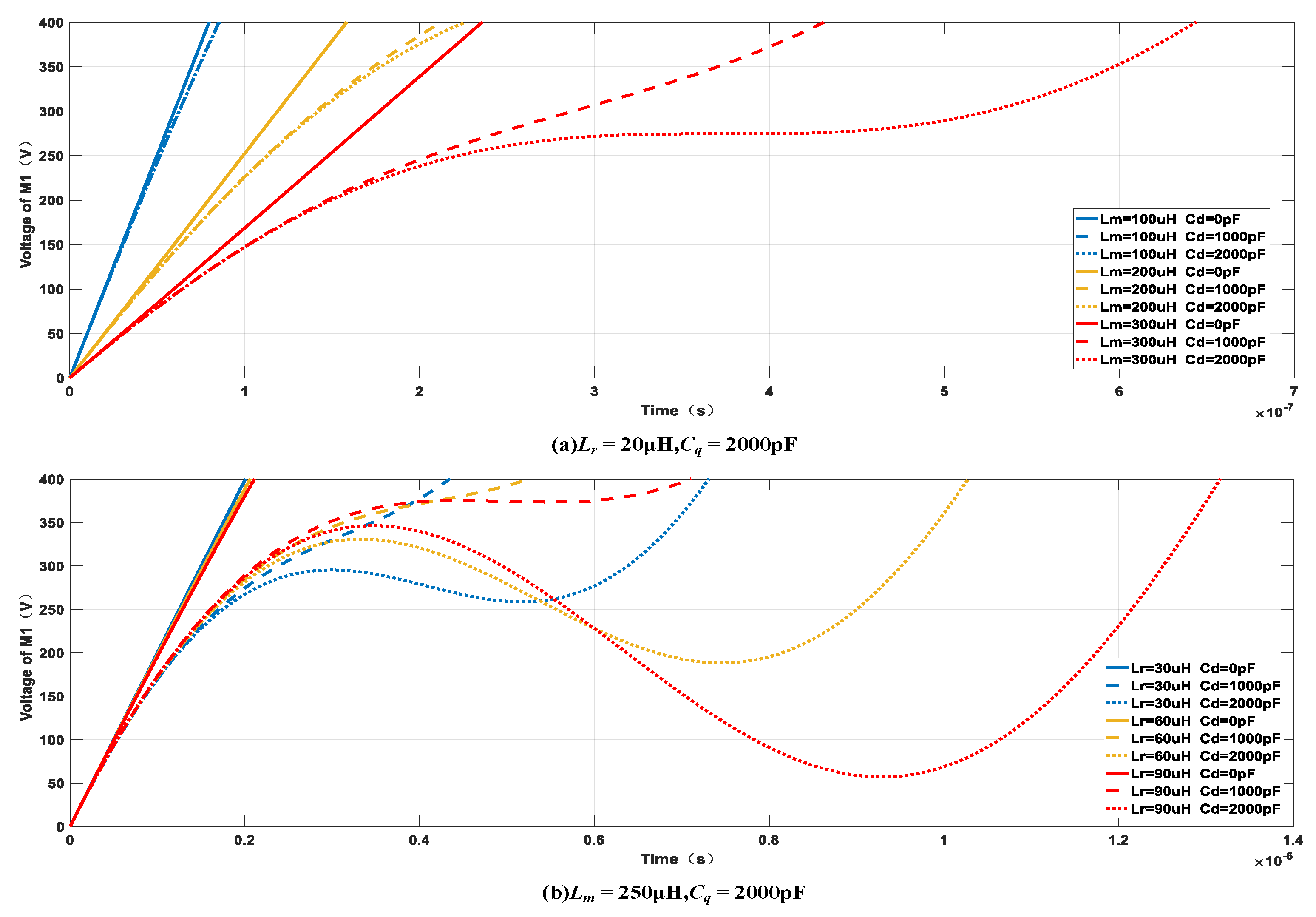

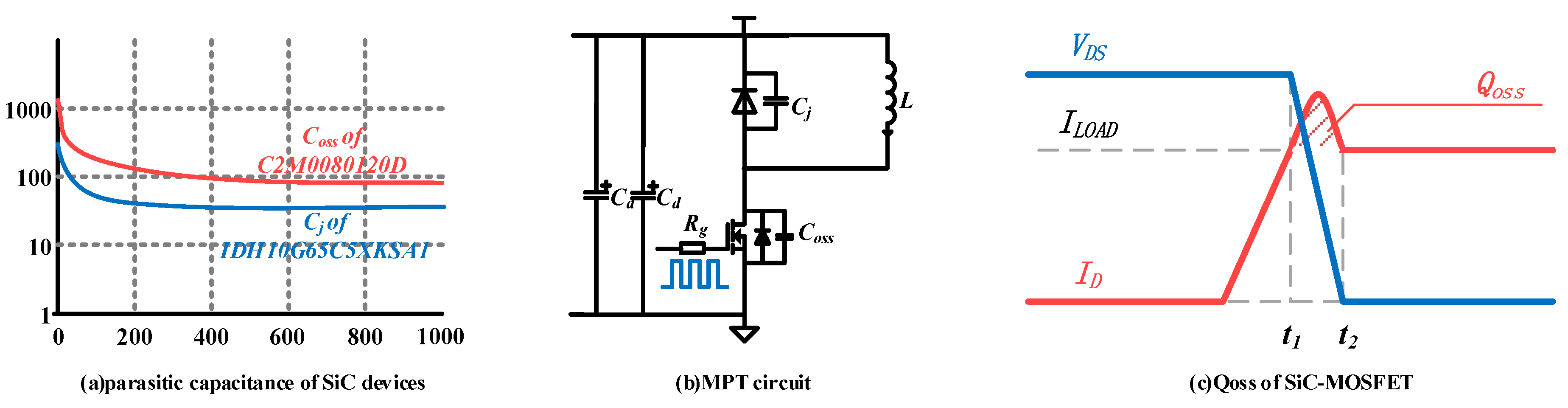

3.2. Analysis of the Operation Principle of the LLC Converter Considering Parasitic Parameters

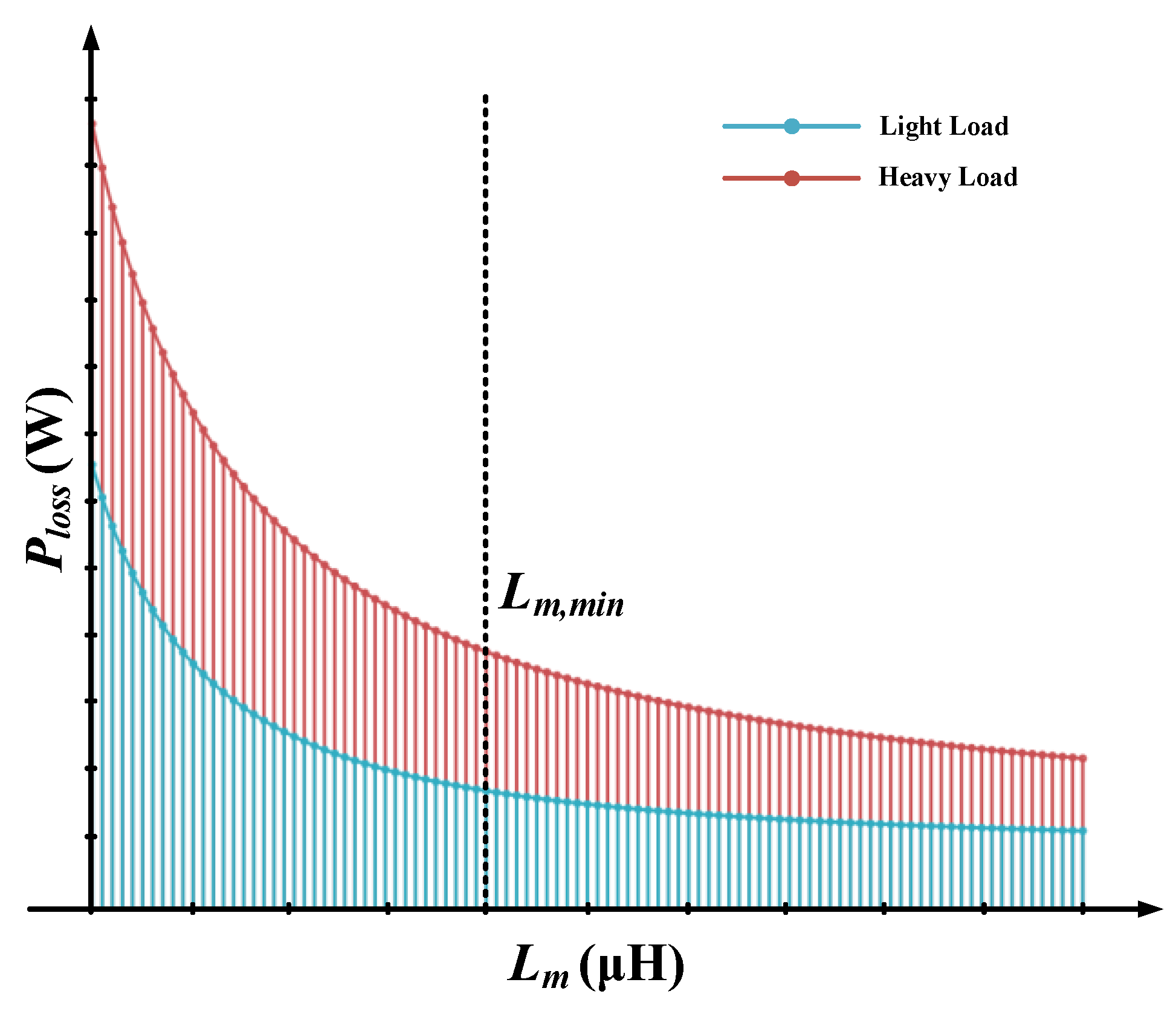

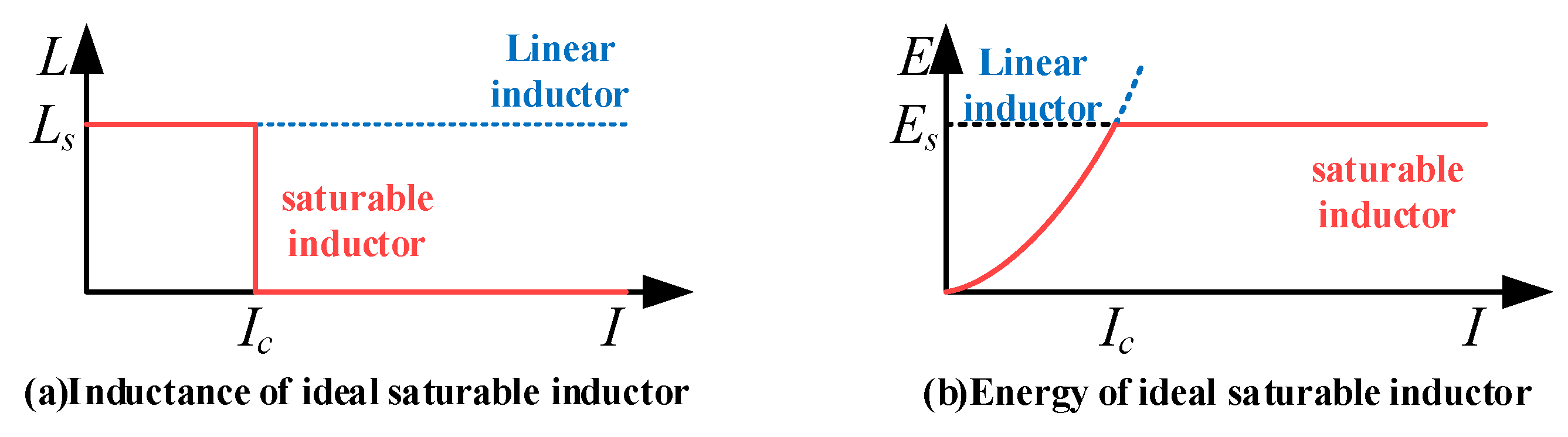

4. Suppression Method of the Influence of Parasitic Parameters Based on the Saturable Inductor

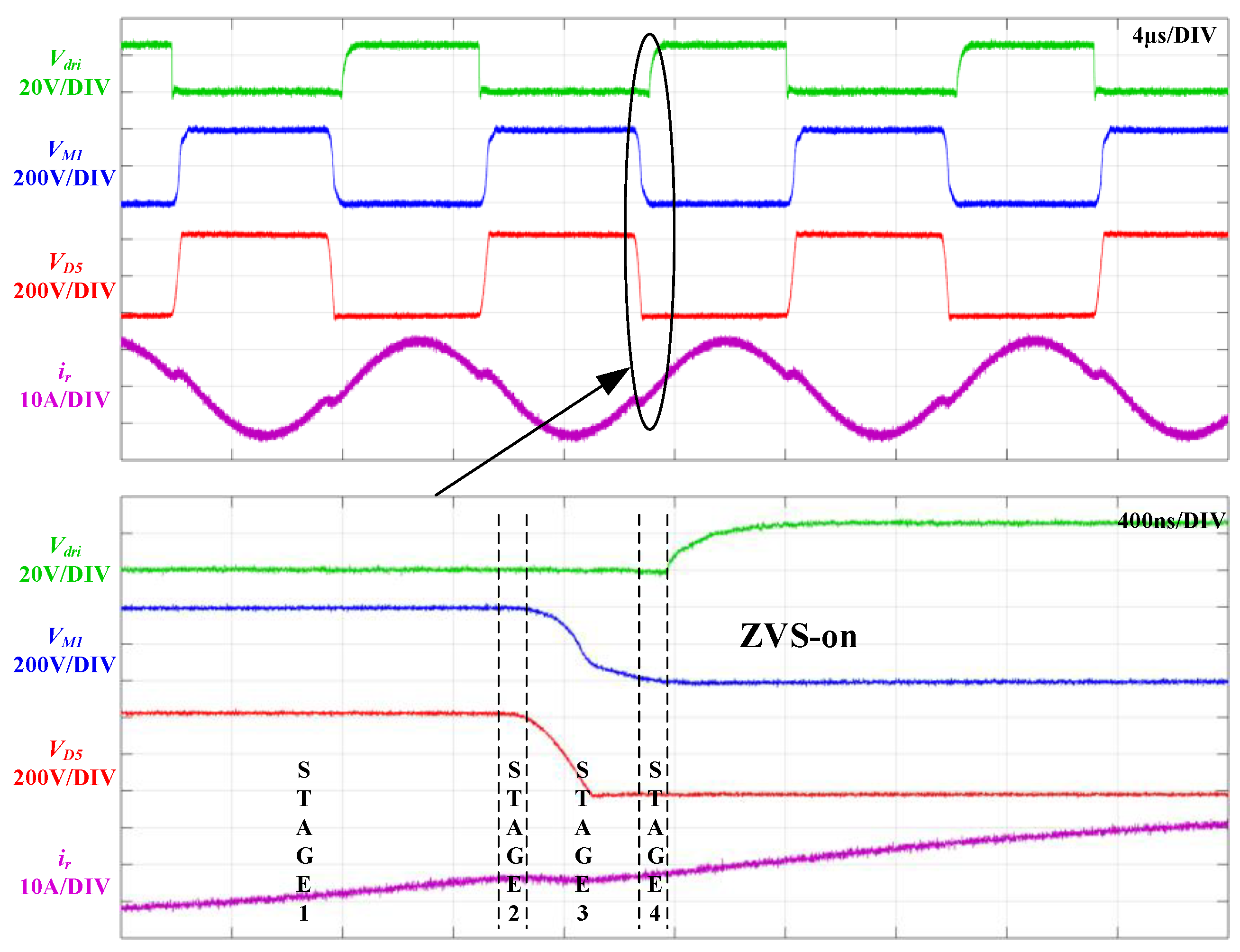

4.1. Analysis of the Operation Principle of the LLC Converter with the Saturable Inductor

4.2. Analysis and Design of the Saturable Inductor

5. Experimental Verification and Analysis

6. Conclusions

- The influence of the parasitic parameters of SiC devices on the high-frequency LLC converter is analyzed step by step, which is more accurate.

- The mechanism of influence of the parasitic parameters on the resonance process is discussed systematically. This paper reveals how different parameters are able to affect the resonance process with respect to parasitic parameters.

- Compared to the extended dead band, the proposed suppression method is able to cause ZVS to be realized and to eliminate the driving interference.

- Compared to the reduced magnetic inductance, the proposed suppression method can significantly decrease the power loss caused by magnetic inductance. The conduction loss can be reduced by 56.74% and the switching loss by 73%. The efficiency can be improved by 0.7%.

Author Contributions

Funding

Conflicts of Interest

Appendix A

Appendix B

Appendix C

| Symbol | Description |

|---|---|

| Vbus | DC bus voltage |

| Vgrid | Grid voltage |

| P | Power |

| NCHB | Number of CHB in one phase |

| Lg | Inductance of grid side |

| vdc(ki) (k = a, b, c and i = 1, 2, …, n) | DC side voltage of unit(i) in phase k |

| pki | Power reference of CHB of unit(i) in phase k |

| vdc* | DC side voltage reference |

| vd, vd-, vq, vq- | D-axis and q-axis components of positive and negative sequence of grid voltage |

| id, id-, iq, iq- | D-axis and q-axis components of positive and negative sequence of grid current |

| va,vb,vc | Grid voltage |

| ia,ib,ic | Grid current |

| θ | Phase angle of the grid |

| vabc* | Three phase voltage reference |

| M1~M4 | Channels of MOSFETs |

| D1~D4 | Body diodes of MOSFETs |

| D5~D8 | Secondary side rectifier diodes |

| Coss1~Coss8 | Parasitic capacitor of MOSFETs |

| Lr | Resonant inductance |

| Lm | Magnetic inductance |

| Cr | Resonant capacitance |

| Ls | Inductance of the saturable inductor |

| n | Turn ratio of transformer |

| Vdri,M1, Vdri,M2 | Drive signals of M1 and M2 |

| Vds,M1 | Drain-source voltage of M1 |

| VD5 | Voltage of secondary rectifier diode |

| ir | Resonant current |

| im | Magnetic current |

| G | DC voltage gain |

| Vout | Output voltage of LLC |

| Vin | Input voltage of LLC |

| k | Ratio of Lm to Lr |

| Ω | Normalized frequency |

| fs | Switching frequency |

| fr | Resonant frequency |

| Q | Quality factor |

| Coss5~Coss8 | Junction capacitors of rectifier diodes |

| Coss,p, Coss,s | Parasitic capacitance of primary and secondary devices |

| Cq, Cr, Cd | Capacitance of Coss1~Coss4, resonant capacitor and Coss5~Coss8 |

| ucq, ucr, ucd | Voltage of Cq, Cr, Cd |

| Tdead | Dead band of the converter |

| Vo | Equivalent output voltage |

| ip | Primary side current of transformer |

| is | Secondary side current of transformer |

| Im | The amplitude of magnetic current |

| Ir | The amplitude of resonant current |

| φ | Phase of resonant current |

| Ploss | Power loss of LLC |

| Lm.min | Demarcation point magnetic inductance |

| Ls | Initial inductance of the saturable inductor |

| Ic | Value of current when Ls becomes saturated |

| Vs | Secondary side voltage of transformer |

| Vc | Peak value of the resonant capacitor voltage |

| Coss(tr) | Time related equivalent parasitic capacitance |

| VDS | Drain-source voltage |

| ILOAD | Load current |

| ID | Drain current |

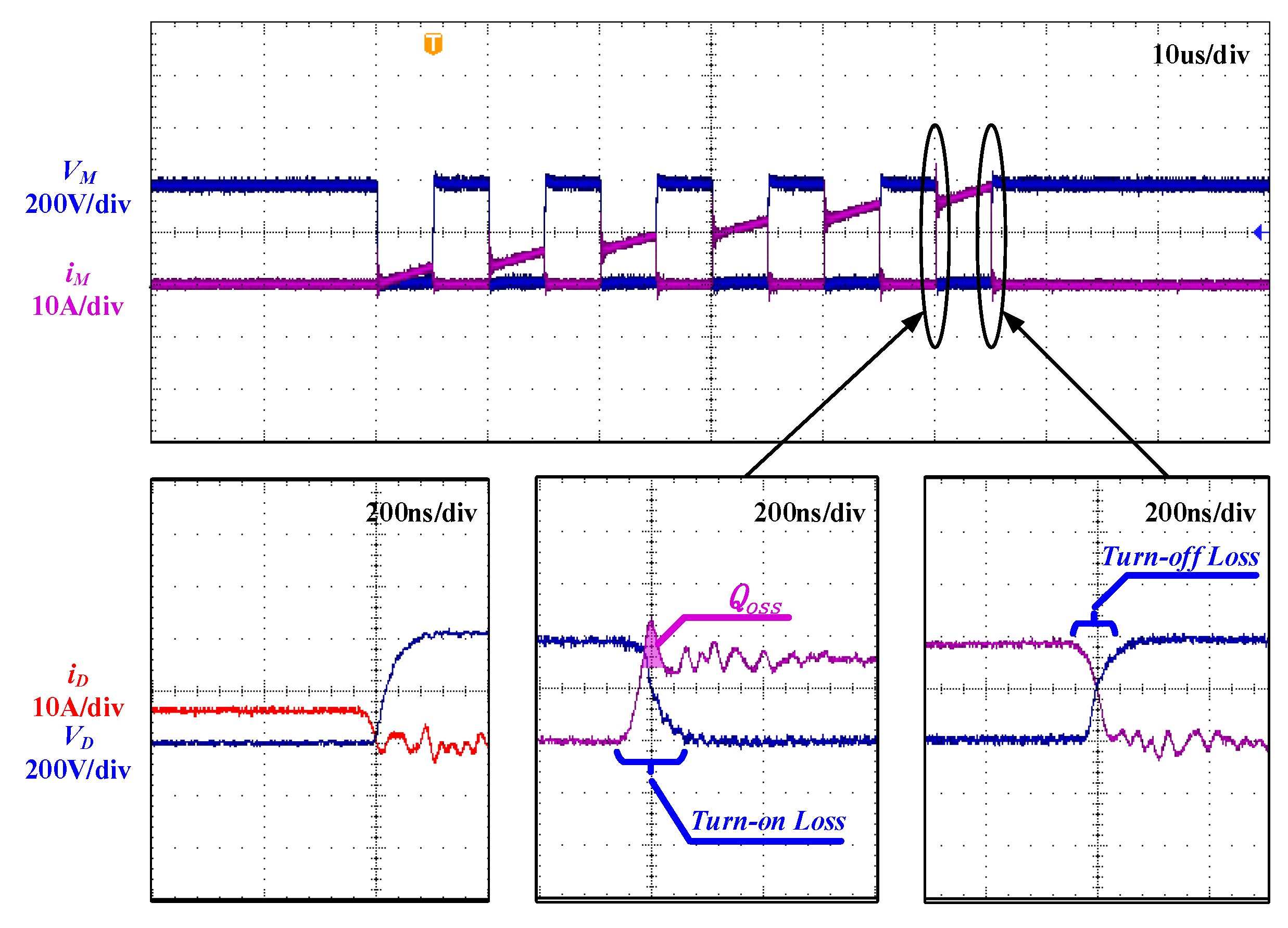

| Qoss | Charge caused by Coss |

| Pc | Conduction loss |

| Pon | Turn-on loss |

| Poff | Turn-off loss |

| Idrms | RMS value of the drain current |

| tr | Rise time of current |

| tf | Fall time of current |

| Bm | Maximum magnetic flux density |

| Pcore | Core loss |

| Pm | Loss of magnetic components |

References

- Wang, Y.; Lin, X.; Pedram, M. A near-optimal model-based control algorithm for households equipped with residential photovoltaic power generation and energy storage systems. IEEE Trans. Sustain. Energy 2016, 7, 77–86. [Google Scholar] [CrossRef]

- Xie, F.; Luo, Z.; Qiu, D.; Zhang, B.; Chen, Y.; Huang, L. Study on a Simplified Structure of a Two-Stage Grid-Connected Photovoltaic System for Parameter Design Optimization. Energies 2019, 12, 2193. [Google Scholar] [CrossRef]

- Van Sark, W. Photovoltaic System Design and Performance. Energies 2019, 12, 1826. [Google Scholar] [CrossRef]

- Karanayil, B.; Ceballos, S.; Pou, J. Maximum Power Point Controller for Large-Scale Photovoltaic Power Plants Using Central Inverters Under Partial Shading Conditions. IEEE Trans. Power Electron. 2019, 34, 3098–3109. [Google Scholar] [CrossRef]

- Choi, H.; Ciobotaru, M.; Jang, M.; Agelidis, V.G. Performance of Medium-Voltage DC-Bus PV System Architecture Utilizing High-Gain DC–DC Converter. IEEE Trans. Sustain. Energy 2015, 6, 464–473. [Google Scholar] [CrossRef]

- Naderipour, A.; Abdul-Malek, Z.; Miveh, M.R.; Hadidian Moghaddam, M.J.; Kalam, A.; Gandoman, F.H. A Harmonic Compensation Strategy in a Grid-Connected Photovoltaic System Using Zero-Sequence Control. Energies 2018, 11, 2629. [Google Scholar] [CrossRef]

- Kjaer, S.B.; Pedersen, J.K.; Blaabjerg, F. A review of single-phase grid-connected inverters for photovoltaic modules. IEEE Trans. Ind. Appl. 2005, 41, 1292–1306. [Google Scholar] [CrossRef]

- Yang, C.; Smedley, K.M. A cost-effective single-stage inverter with maximum power point tracking. IEEE Trans. Power Electron. 2004, 19, 1289–1294. [Google Scholar] [CrossRef]

- Siwakoti, Y.P.; Blaabjerg, F. Common-Ground-Type Transformerless Inverters for Single-Phase Solar Photovoltaic Systems. IEEE Trans. Ind. Electron. 2018, 65, 2100–2111. [Google Scholar] [CrossRef]

- Bratcu, A.I.; Munteanu, I.; Bacha, S.; Picault, D.; Raison, B. Cascaded DC–DC Converter Photovoltaic Systems: Power Optimization Issues. IEEE Trans. Ind. Electron. 2011, 58, 403–411. [Google Scholar] [CrossRef]

- McGrath, B.P.; Holmes, D.G.; Kong, W.Y. A decentralized controller architecture for a cascaded H-bridge multilevel converter. IEEE Trans. Ind. Electron. 2014, 61, 1169–1178. [Google Scholar] [CrossRef]

- Babaei, E.; Laali, S.; Alilu, S. Cascaded multilevel inverter with series connection of novel H-bridge basic units. IEEE Trans. Ind. Electron. 2014, 61, 6664–6671. [Google Scholar] [CrossRef]

- Liu, Y.; Abu-Rub, H.; Ge, B. Front-End Isolated Quasi-Z-Source DC–DC Converter Modules in Series for High-Power Photovoltaic Systems—Part I: Configuration, Operation, and Evaluation. IEEE Trans. Ind. Electron. 2017, 64, 347–358. [Google Scholar] [CrossRef]

- Yu, Y.; Konstantinou, G.; Hredzak, B.; Agelidis, V.G. Power Balance Optimization of Cascaded H-Bridge Multilevel Converters for Large-Scale Photovoltaic Integration. IEEE Trans. Power Electron. 2016, 31, 1108–1120. [Google Scholar] [CrossRef]

- Doncker, R.W.D. Power electronic technologies for flexible dc distribution grids. In Proceedings of the 2014 International Power Electronics Conference (IPEC-Hiroshima 2014—ECCE ASIA), Hiroshima, Japan, 18–21 May 2014. [Google Scholar] [CrossRef]

- Athab, H.; Yazdani, A.; Wu, B. A transformerless DC–DC converter with large voltage ratio for MVDC grids. IEEE Trans. Power Deliv. 2014, 29, 1877–1885. [Google Scholar] [CrossRef]

- Hu, J.; Joebges, P.; De Doncker, R.W. Maximum power point tracking control of a high power dc-dc converter for PV integration in MVDC distribution grids. In Proceedings of the 2017 IEEE Applied Power Electronics Conference and Exposition (APEC), San Antonio, TX, USA, 26–30 March 2017. [Google Scholar] [CrossRef]

- Zapata, J.W.; Meynard, T.A.; Kouro, S. Partial power dc-dc converter for large-scale photovoltaic systems. In Proceedings of the 2016 IEEE 2nd Annual Southern Power Electronics Conference (SPEC), Auckland, New Zealand, 5–8 December 2016. [Google Scholar] [CrossRef]

- Rojas, C.A.; Kouro, S.; Perez, M.A.; Echeverria, J. DC–DC MMC for HVdc Grid Interface of Utility-Scale Photovoltaic Conversion Systems. IEEE Trans. Ind. Electron. 2018, 65, 352–362. [Google Scholar] [CrossRef]

- Zhao, B.; Yu, Q.; Sun, W. Extended-phase-shift control of isolated bidirectional DC-DC converter for power distribution in microgrid. IEEE Trans. Power Electron. 2012, 27, 4667–4680. [Google Scholar] [CrossRef]

- Jain, A.K.; Ayyanar, R. PWM control of dual active bridge: Comprehensive analysis and experimental verification. IEEE Trans. Power Electron. 2011, 26, 1215–1227. [Google Scholar] [CrossRef]

- Zhu, Q.; Wang, L.; Chen, D.; Zhang, L.; Huang, A.Q. Design and implementation of a 7.2 kV single stage AC-AC solid state transformer based on current source series resonant converter and 15 kV SiC MOSFET. In Proceedings of the 2017 IEEE Energy Conversion Congress and Exposition (ECCE), Cincinnati, OH, USA, 1–5 October 2017. [Google Scholar] [CrossRef]

- Li, X.; Bhat, A.K.S. Analysis and design of high-frequency isolated dual-bridge series resonant DC/DC converter. IEEE Trans. Power Electron. 2010, 25, 850–862. [Google Scholar] [CrossRef]

- Yang, B. Topology Investigation for Front End DC/DC Power Conversion for Distributed Power System. Ph.D. Thesis, Virginia Polytechnic Institute and State University, Blacksburg, VA, USA, 2003. [Google Scholar]

- Ryu, M.H.; Kim, H.S.; Baek, J.W. Effective test bed of 380-V DC distribution system using isolated power converters. IEEE Trans. Ind. Electron. 2015, 62, 4525–4536. [Google Scholar] [CrossRef]

- Zixin, L.; Fanqiang, G.; Cong, Z.; Zhe, W.; Hang, Z.; Ping, W.; Yaohua, L. Research Review of Power Electronic Transformer Technologies. Proc. CSEE 2018, 38, 1593. [Google Scholar]

- Wang, L.; Zhu, Q.; Yu, W.; Huang, A.Q. A Medium-Voltage Medium-Frequency Isolated DC–DC Converter Based on 15-kV SiC MOSFETs. IEEE J. Emerg. Sel. Top. Power Electron. 2017, 5, 100–109. [Google Scholar] [CrossRef]

- Abbasi, M.; Lam, J. A Modular SiC-Based Step-Up Converter with Soft-Switching-Assisted Networks and Internally Coupled High-Voltage-Gain Modules for Wind Energy System with a Medium-Voltage DC-Grid. IEEE J. Emerg. Sel. Top. Power Electron. 2019, 7, 798–810. [Google Scholar] [CrossRef]

- Fernández, E.; Paredes, A.; Sala, V.; Romeral, L. A Simple Method for Reducing THD and Improving the Efficiency in CSI Topology Based on SiC Power Devices. Energies 2018, 11, 2798. [Google Scholar] [CrossRef]

- Parreiras, T.M.; Machado, A.P.; Amaral, F.V.; Lobato, G.C.; Brito, J.A.S.; Filho, B.C. Forward Dual-Active-Bridge Solid-State Transformer for a SiC-Based Cascaded Multilevel Converter Cell in Solar Applications. IEEE Trans. Ind. Appl. 2018, 54, 6353–6363. [Google Scholar] [CrossRef]

- Chen, H.; Wu, X. Analysis on the influence of the secondary parasitic capacitance to ZVS transient in LLC resonant converter. In Proceedings of the 2014 IEEE Energy Conversion Congress and Exposition (ECCE), Pittsburgh, PA, USA, 14–18 September 2014. [Google Scholar] [CrossRef]

- Stefan, D.; Thomas, H.; Martin, M. Influence of the junction capacitance of the secondary rectifier diodes on output characteristics in multi-resonant converters. In Proceedings of the 2016 IEEE Applied Power Electronics Conference and Exposition (APEC), Long Beach, CA, USA, 20–24 March 2016. [Google Scholar] [CrossRef]

- Beiranvand, R.; Rashidian, B.; Zolghadri, M.R.; Alavi, S.M.H. Optimizing the Normalized Dead-Time and Maximum Switching Frequency of a Wide-Adjustable-Range LLC Resonant Converter. IEEE Trans. Power Electron. 2011, 26, 462–472. [Google Scholar] [CrossRef]

- Kim, J.; Kim, C.; Kim, J.; Moon, G. Analysis for LLC resonant converter considering parasitic components at very light load condition. In Proceedings of the 8th International Conference on Power Electronics–ECCE Asia, Jeju, Korea, 30 May–3 June 2011. [Google Scholar] [CrossRef]

- Chen, C.; Zhao, X.; Yeh, C.; Lai, J. Analysis of the Zero-Voltage Switching Condition in LLC Series Resonant Converter with Secondary Parasitic Capacitors. In Proceedings of the 2019 IEEE Applied Power Electronics Conference and Exposition (APEC), Anaheim, CA, USA, 17–21 March 2019. [Google Scholar] [CrossRef]

- Ren, R.; Liu, B.; Edward, A.J.; Fred, W.; Zhang, Z.; Costinett, D. Accurate ZVS boundary in high switching frequency LLC converter. In Proceedings of the 2016 IEEE Energy Conversion Congress and Exposition (ECCE), Milwaukee, WI, USA, 18–22 September 2016. [Google Scholar] [CrossRef]

| Symbol | Description | Parameters |

|---|---|---|

| Vbus | DC bus voltage | 800 V |

| Vgrid | Grid voltage | 35 kV |

| P | Power | 6 MW |

| NCHB | Number of CHB in one phase | 40 |

| Lg | Inductance of grid side | 8 mH |

| Symbol | Description | Parameters | ||

|---|---|---|---|---|

| Dead Band Extended | Reduce Magnetic Inductance | Add Saturable Inductor | ||

| Vin | Input voltage | 400 V | 400 V | 400 V |

| Vo | Output voltage | 400 V | 400 V | 400 V |

| Po | Output Power | 2000 W | 2000 W | 2000 W |

| Lr | Resonant inductance | 20 μH | 20 μH | 20 μH |

| Lm | Magnetic inductance | 300 μH | 80 μH | 300 μH |

| Cr | Resonant capcitance | 156 nF | 156 nF | 156 nF |

| M | Primary side devices | C2M0080120D | C2M0080120D | C2M0080120D |

| D | Secondary side devices | IDH10G65C5XKSA1 (6 parallel) | IDH10G65C5XKSA1 (6 parallel) | IDH10G65C5XKSA1 (6 parallel) |

| Cossm | Capacitance of primary side devices | 1.6 nF | 1.6 nF | 1.6 nF |

| Cossd | Capacitance of secondary side devices | 6 × 40 pF | 6 × 40 pF | 6 × 40 pF |

| Ls | Inductance of the saturable inductor | 300 μH (Ic = 1 A) | ||

© 2019 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Li, R.; Shi, F.; Cai, X.; Xu, H. Influence of Parasitic Parameters on DC–DC Converters and Their Method of Suppression in High Frequency Link 35 kV PV Systems. Energies 2019, 12, 3743. https://doi.org/10.3390/en12193743

Li R, Shi F, Cai X, Xu H. Influence of Parasitic Parameters on DC–DC Converters and Their Method of Suppression in High Frequency Link 35 kV PV Systems. Energies. 2019; 12(19):3743. https://doi.org/10.3390/en12193743

Chicago/Turabian StyleLi, Rui, Fangyuan Shi, Xu Cai, and Haibo Xu. 2019. "Influence of Parasitic Parameters on DC–DC Converters and Their Method of Suppression in High Frequency Link 35 kV PV Systems" Energies 12, no. 19: 3743. https://doi.org/10.3390/en12193743

APA StyleLi, R., Shi, F., Cai, X., & Xu, H. (2019). Influence of Parasitic Parameters on DC–DC Converters and Their Method of Suppression in High Frequency Link 35 kV PV Systems. Energies, 12(19), 3743. https://doi.org/10.3390/en12193743