Comparative Study of Control Strategies for Stabilization and Performance Improvement of DC Microgrids with a CPL Connected

Abstract

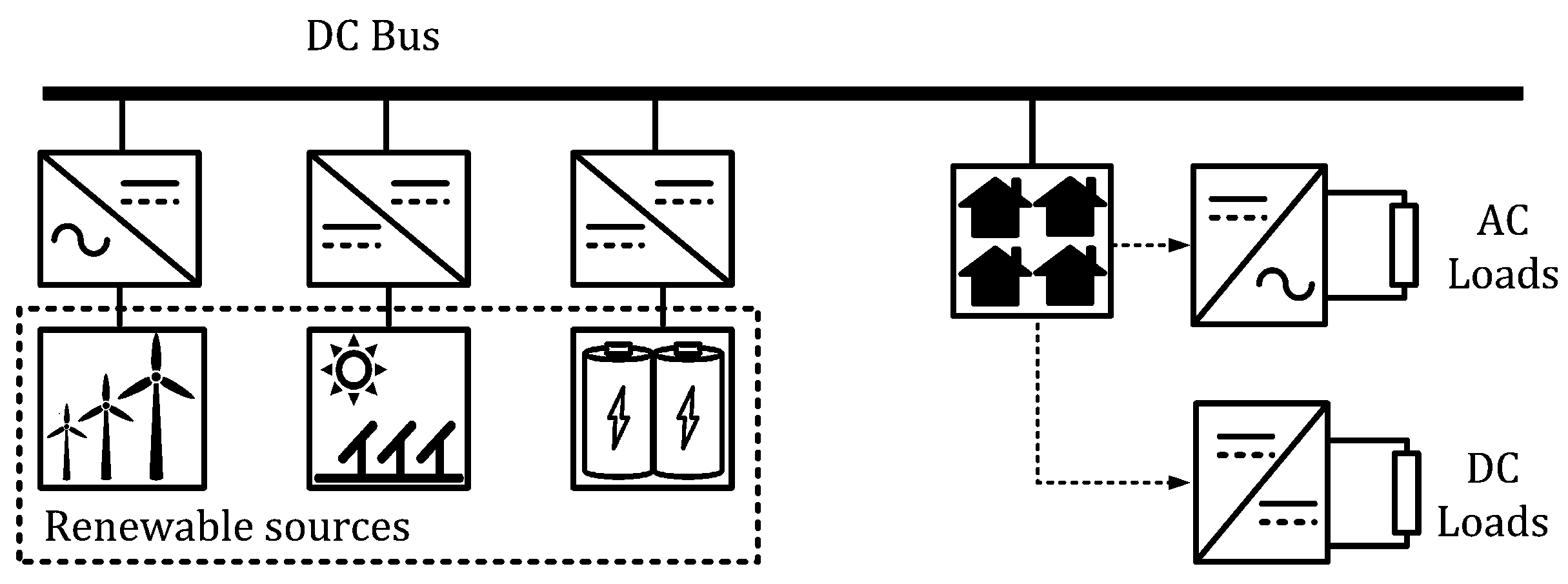

1. Introduction

- A novel relative stability analysis for microgrids with CPL is proposed based on the Middlebrook criterion. Such analysis provides a quantification of the stability margin for different control methodologies and by using two microgrid topologies;

- Experimental evaluation of different output and state feedback control techniques for stabilization and performance improvement of two different types of DC microgrid connected to a CPL;

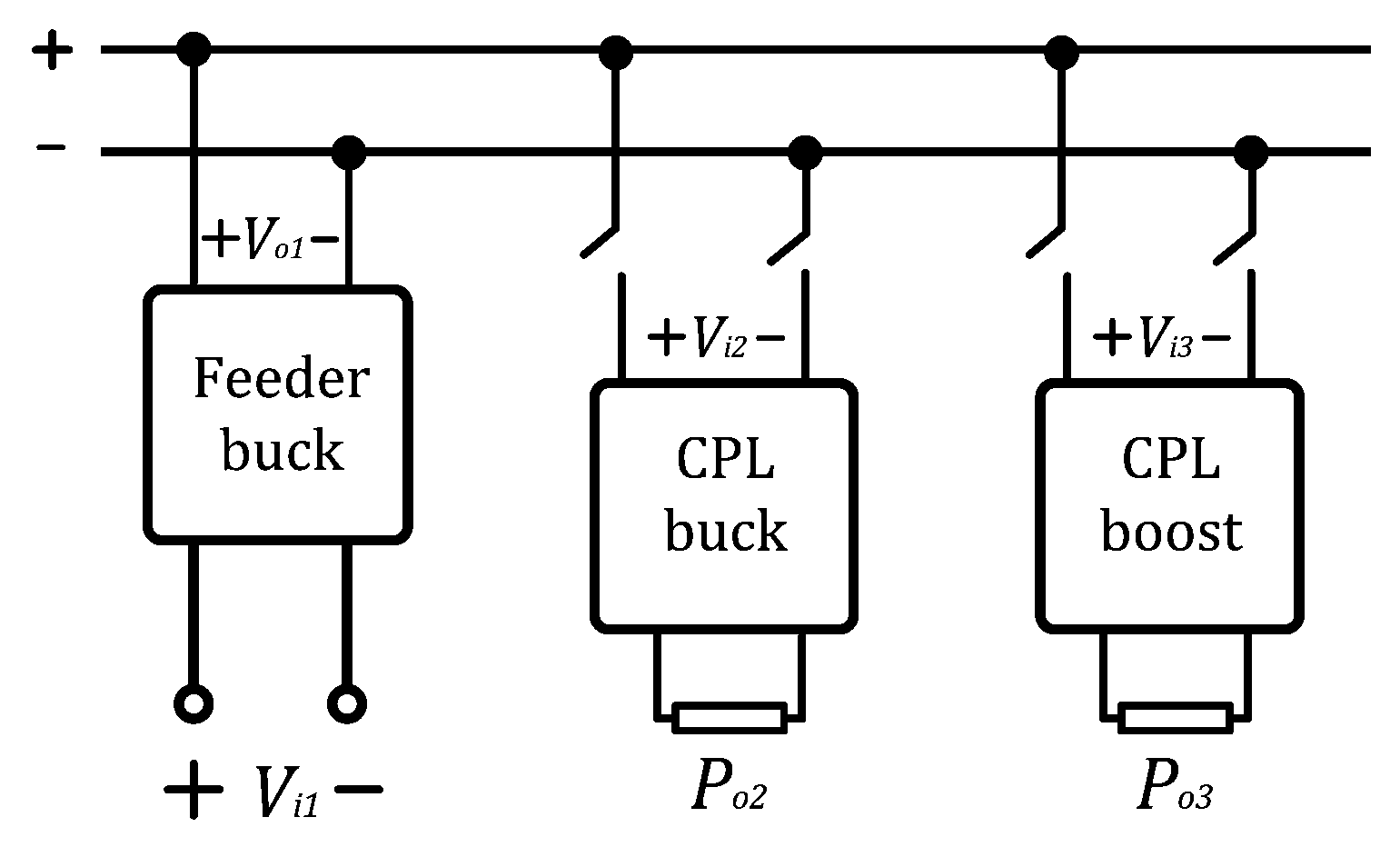

- Two DC microgrids topologies are used: buck-boost (buck feeder with boost CPL) and buck-buck;

- The performance of the control strategies under CPL power variation is evaluated by performance indices whose results are related to the stability margins based on Middlebrook criterion.

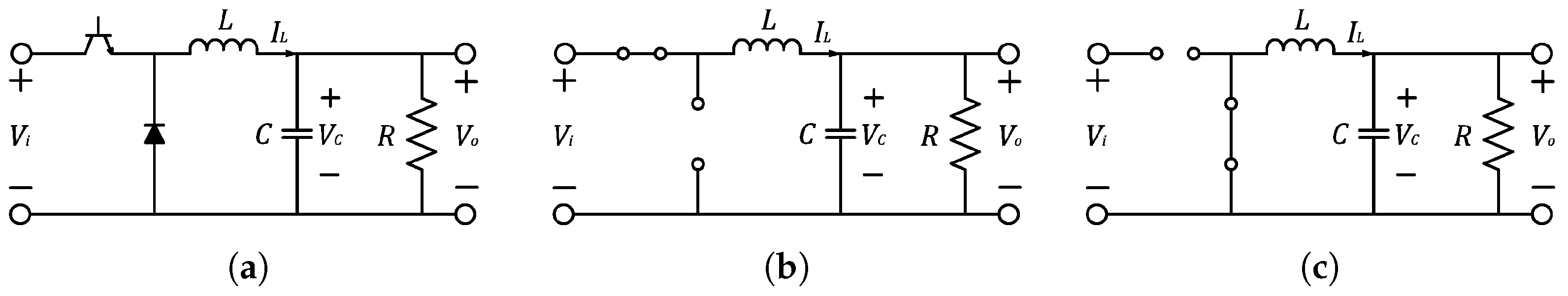

2. DC-DC Converters Modeling

2.1. Buck Converter Modeling

2.2. Boost Converter Modeling

3. DC Microgrids Stability

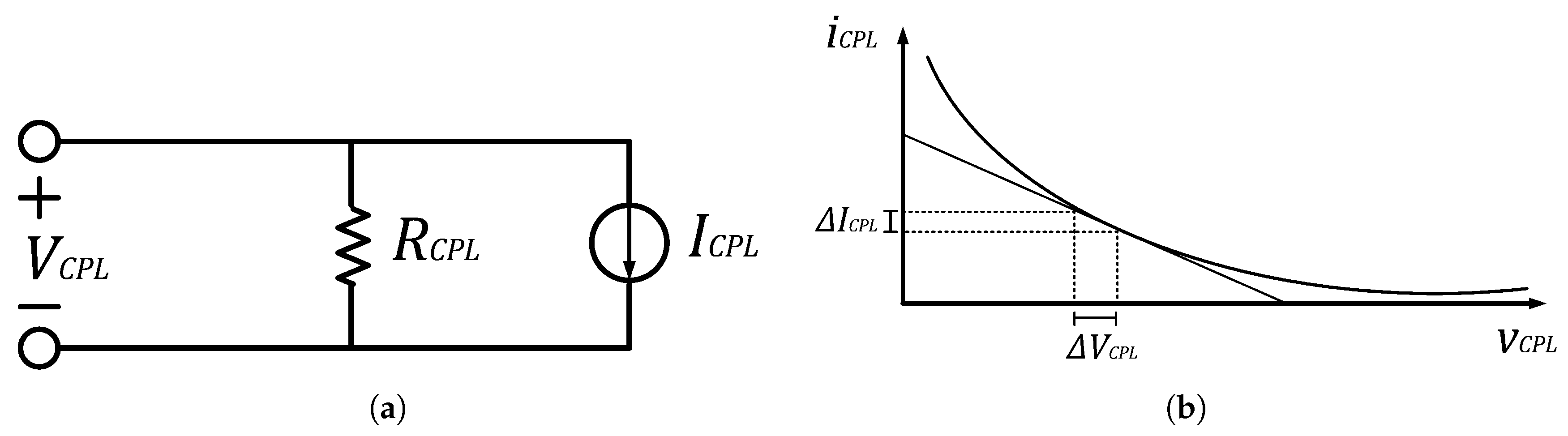

3.1. CPL Dynamic Behavior

3.2. DC-DC Converters Connected to CPL

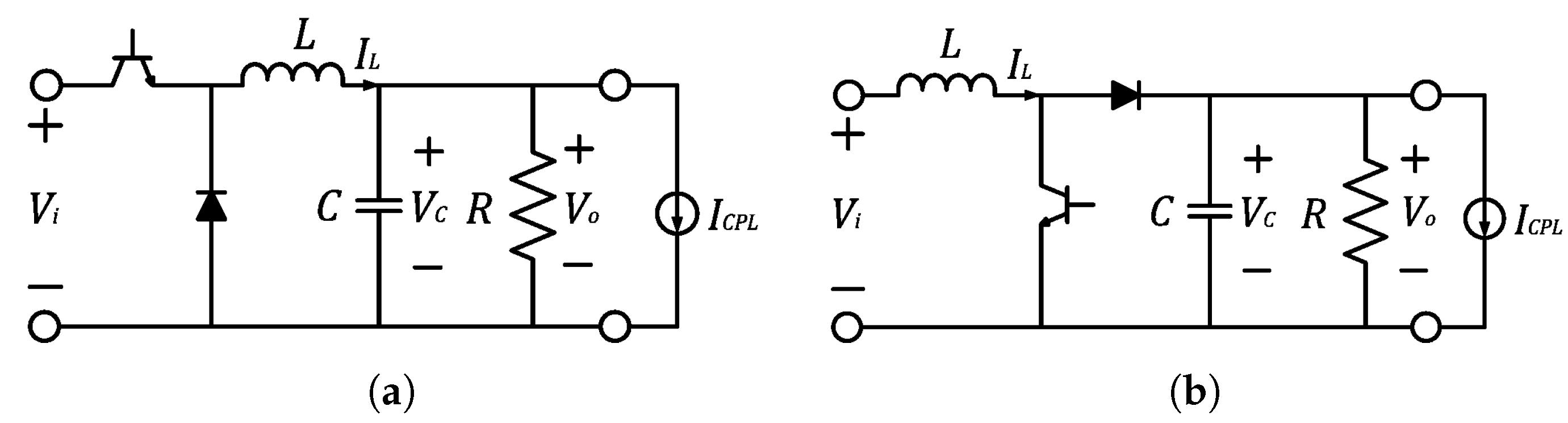

3.3. DC-DC Converters Operating as CPL

3.3.1. Buck Converter Operating as CPL

3.3.2. Boost Converter Operating as CPL

4. Microgrid Design

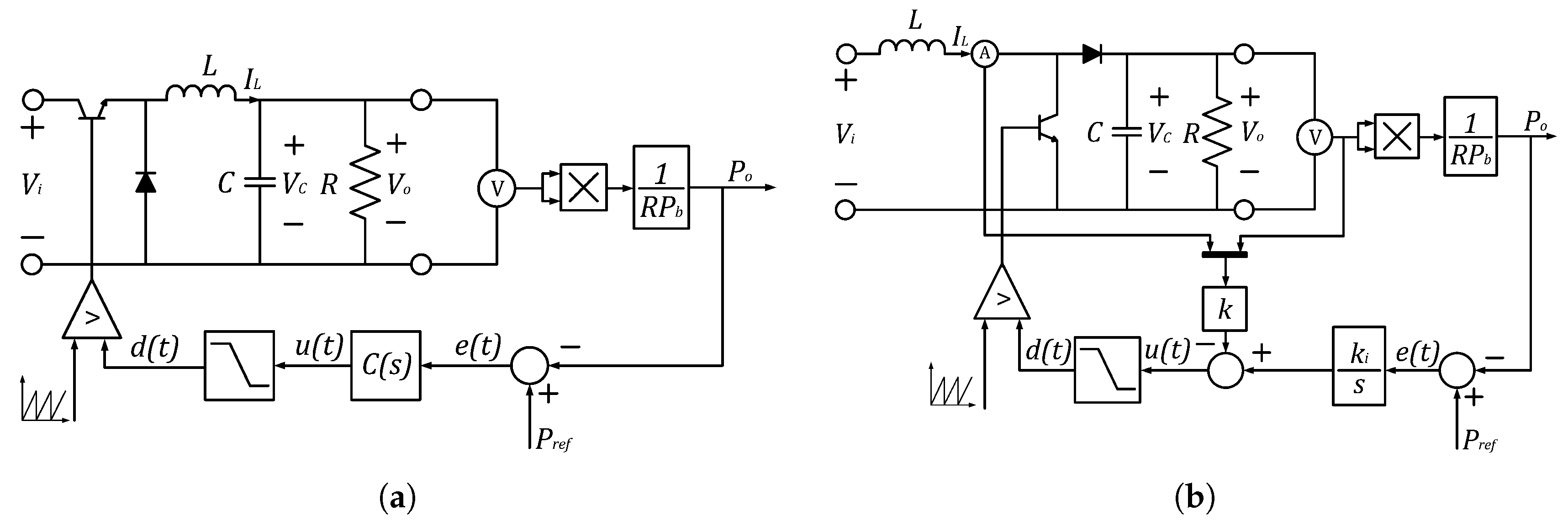

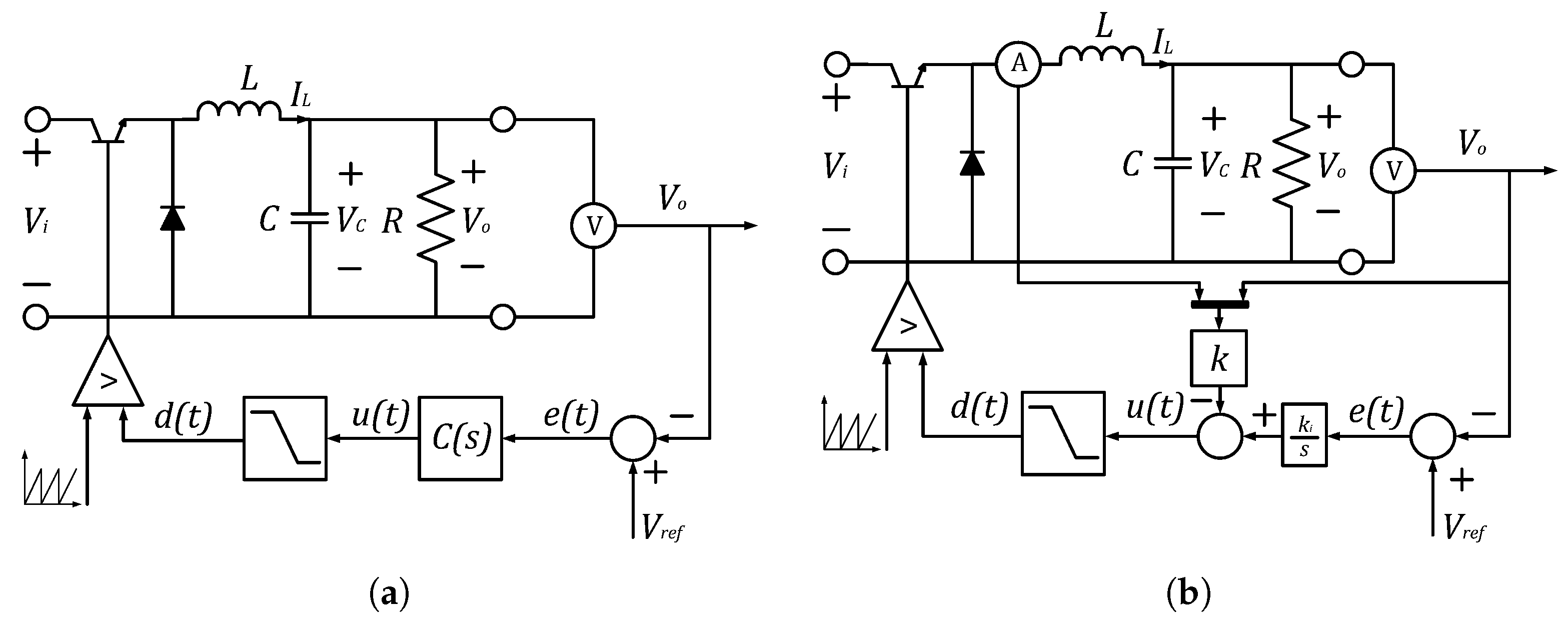

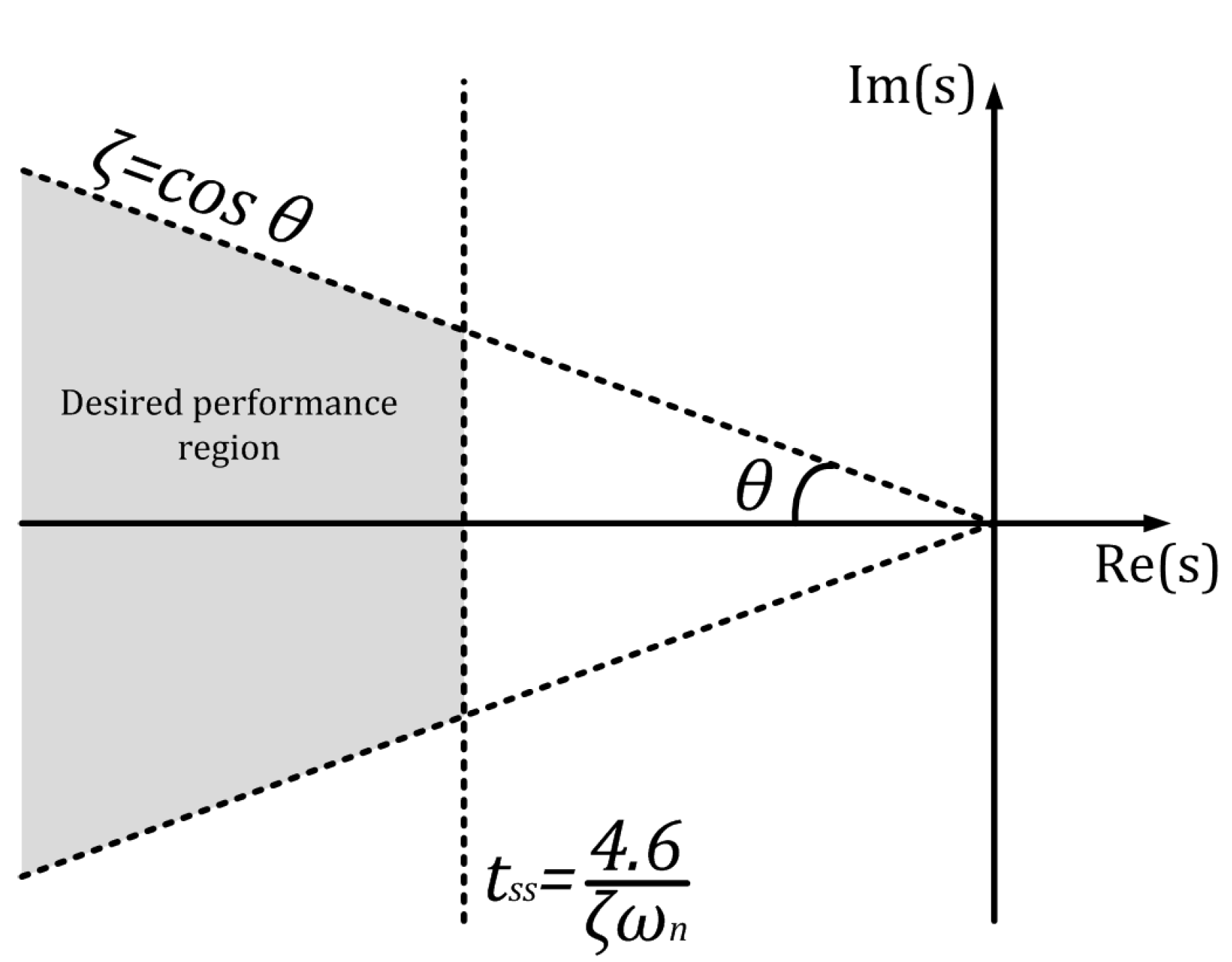

4.1. Feeder Controllers Design

4.2. CPL Design

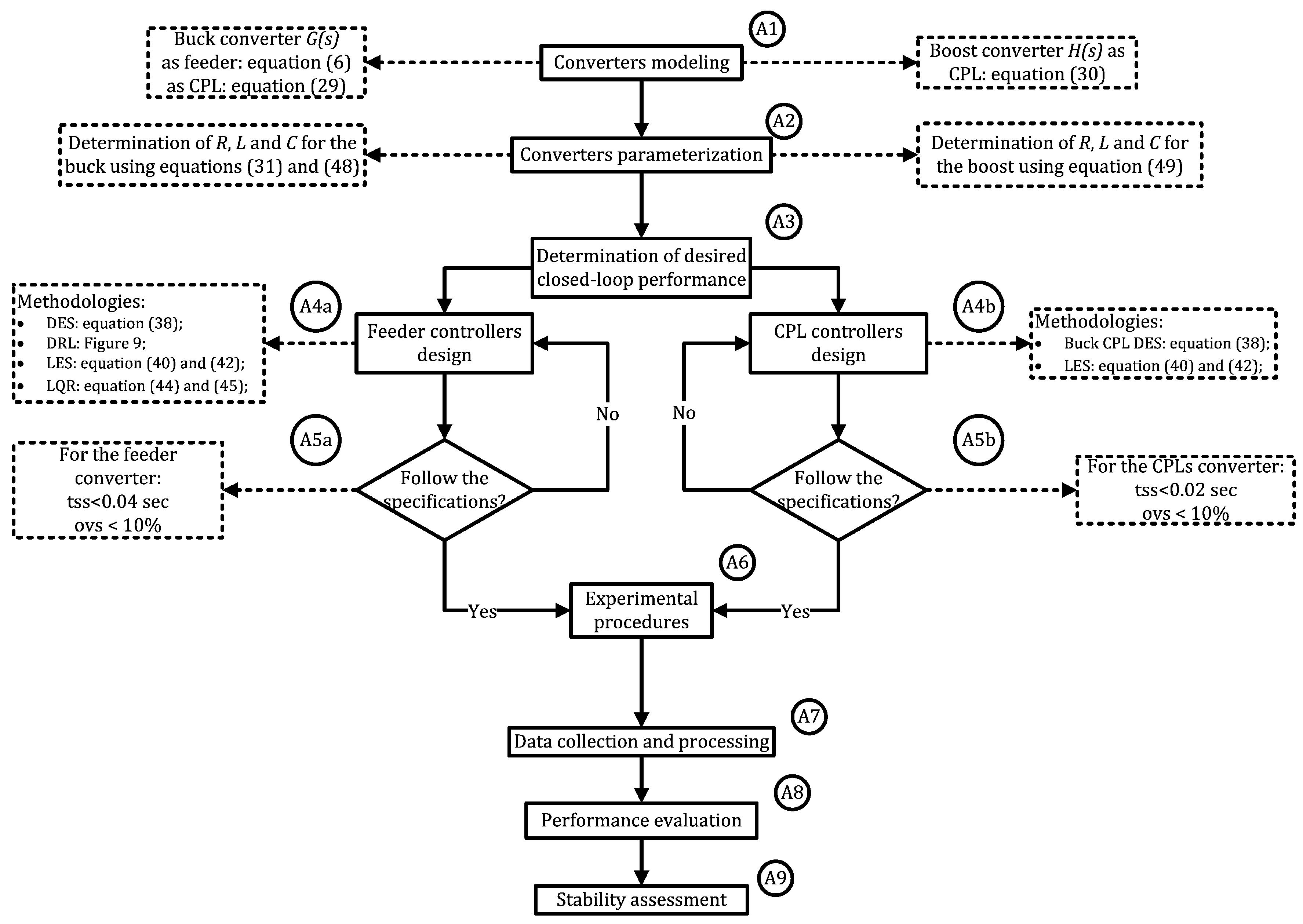

5. Methodological Procedures

5.1. Proposed Microgrids

Microgrid Implementation

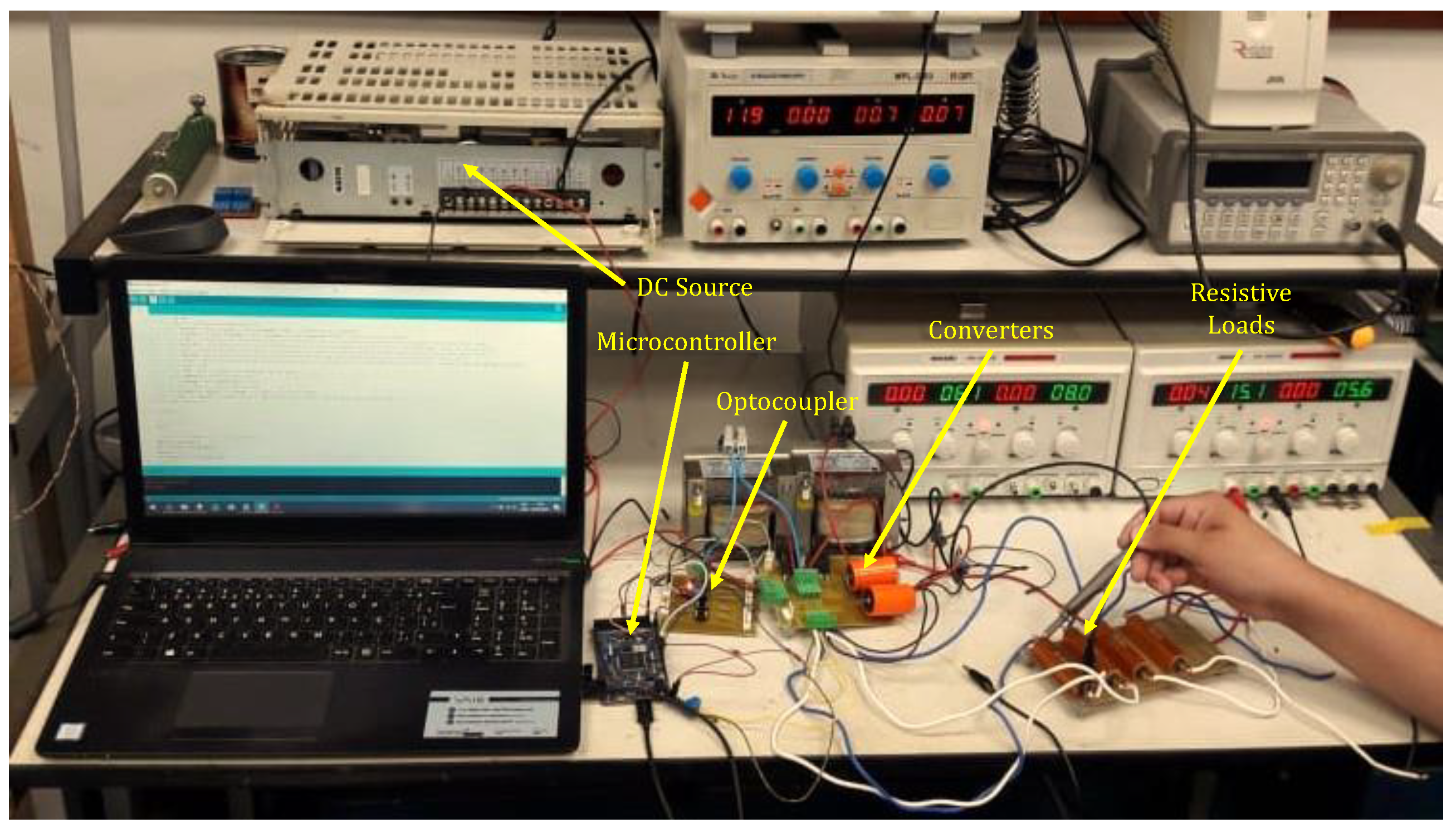

5.2. Experimental Procedures and Test Environment Description

- It leads the system to discontinuous conduction mode (DCM) causing the system collapse, since the controllers are not designed to deal with DCM.

- It modifies the feeder OP, losing the DC bus voltage regulation ability.

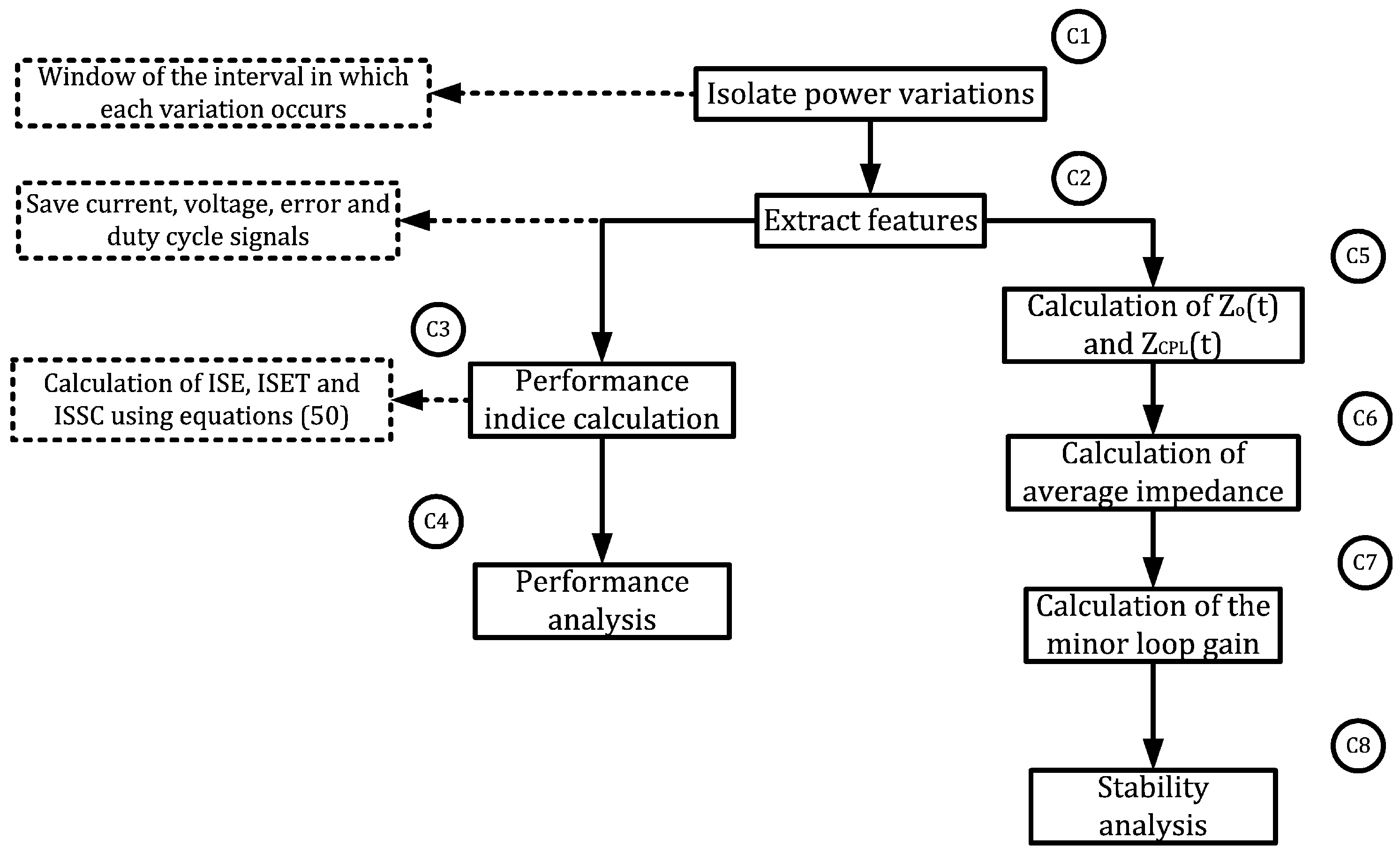

5.3. Data Processing

5.3.1. Perfomance Evaluation

5.3.2. Stability Assessment

6. Results and Discussions

6.1. Buck-Buck Microgrid Analysis

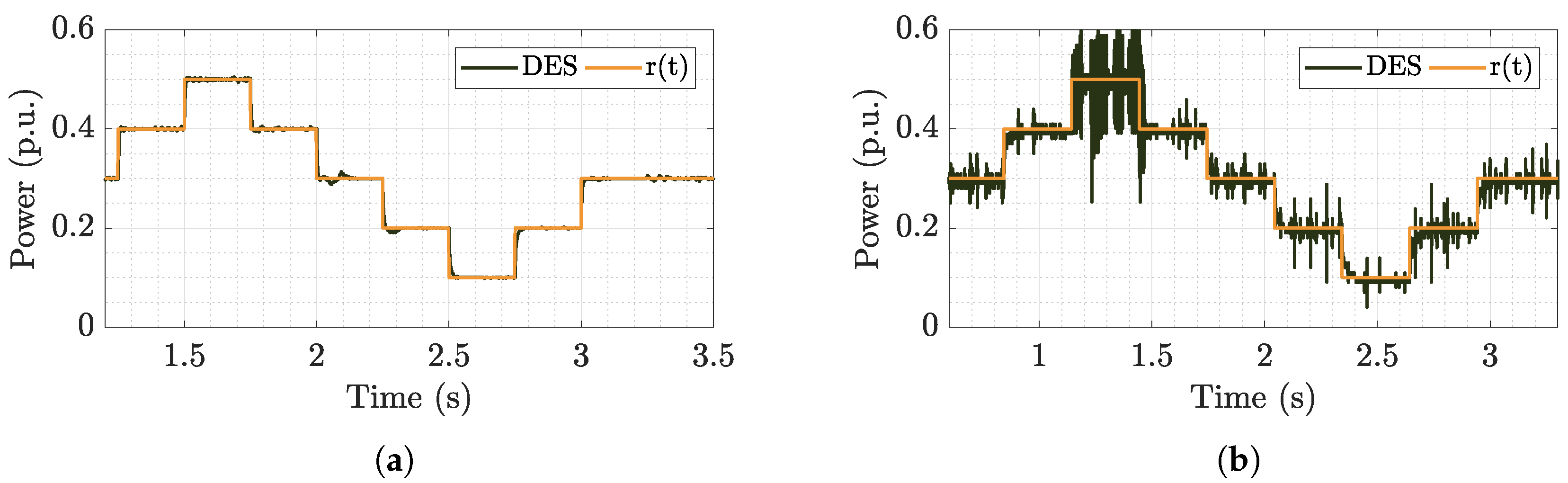

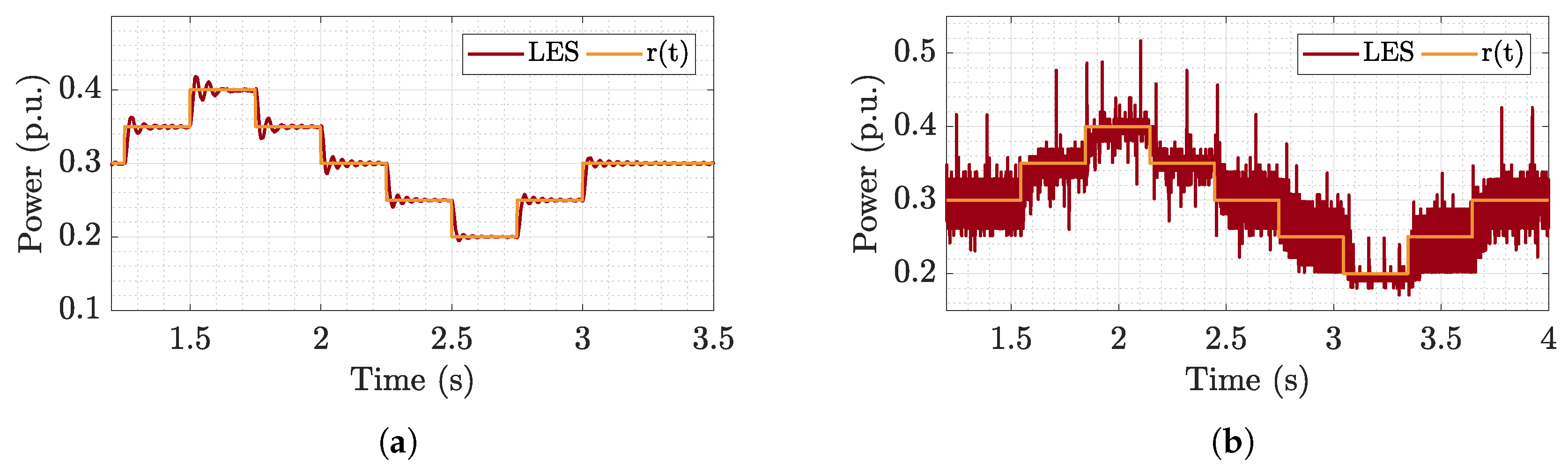

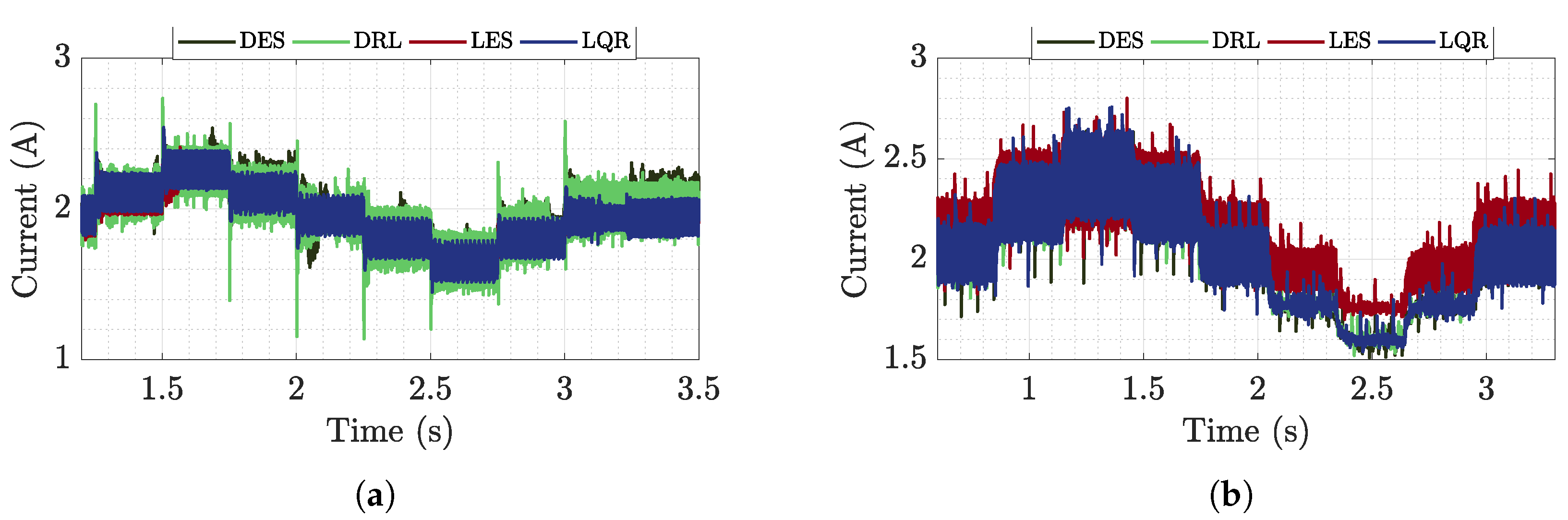

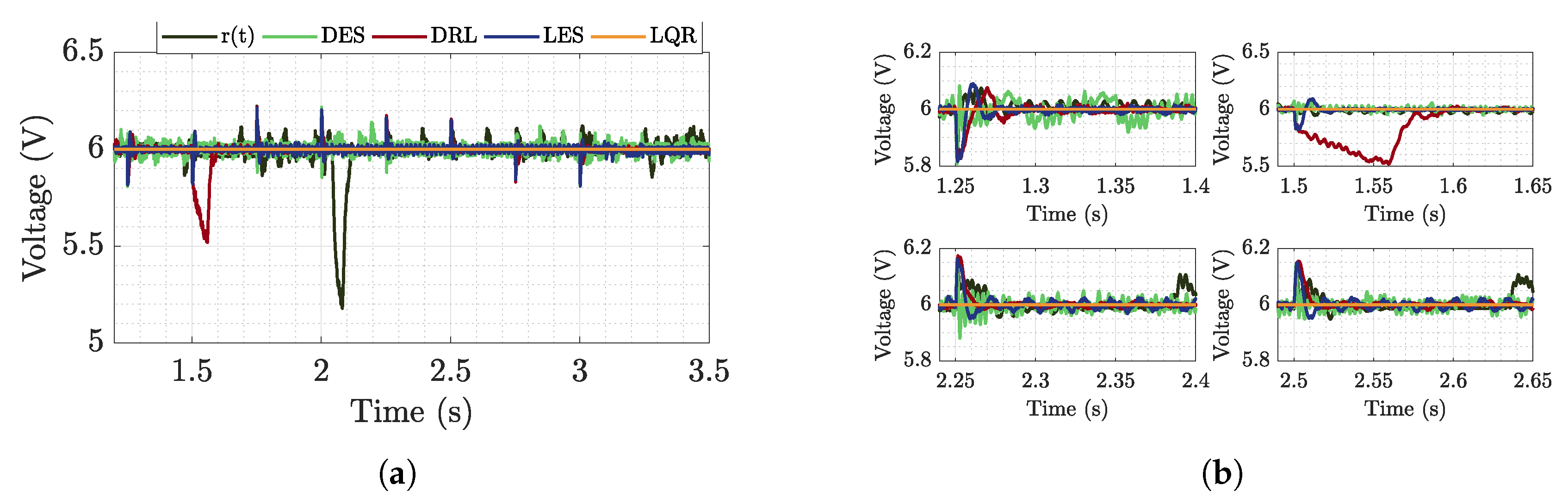

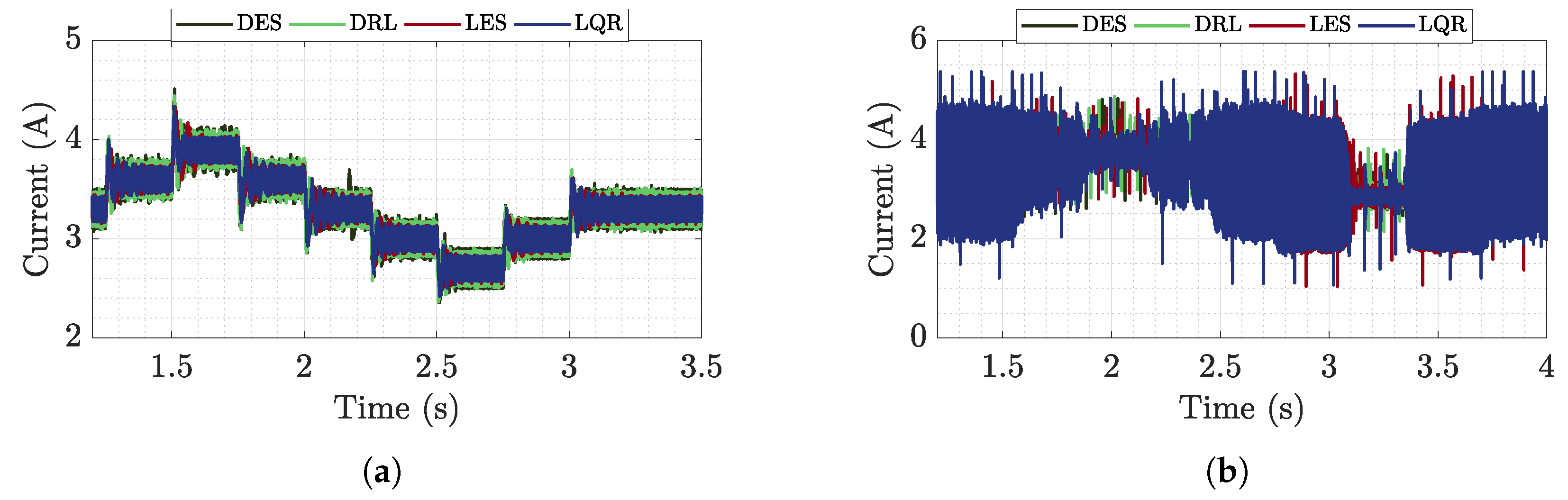

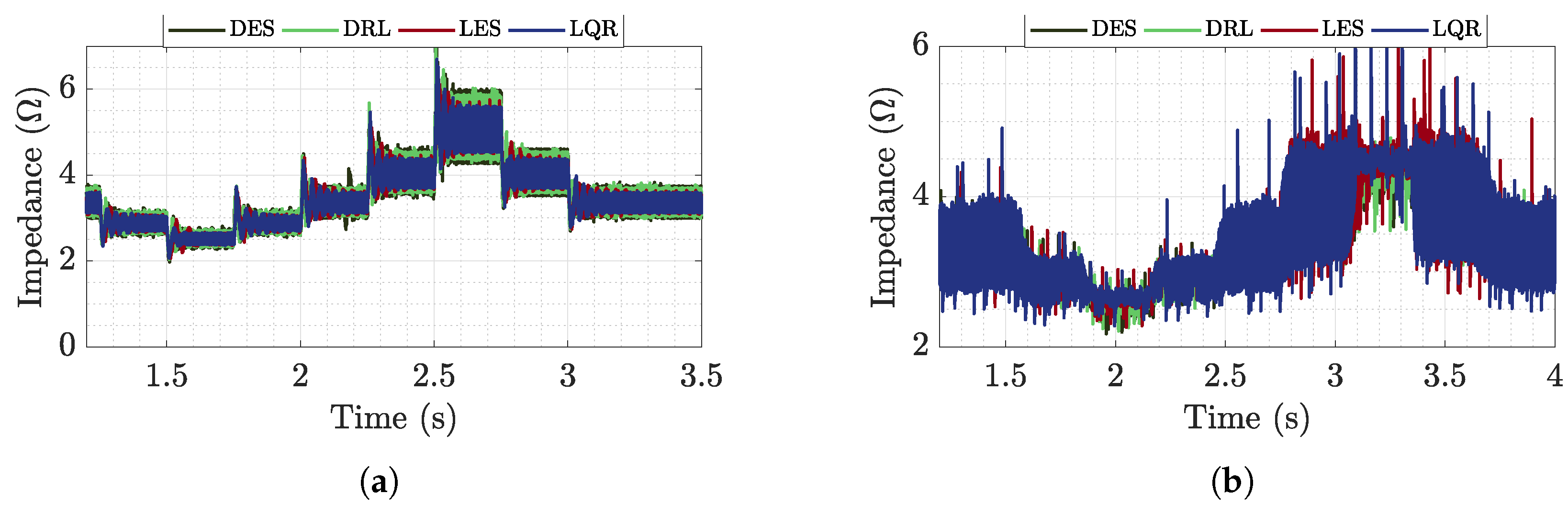

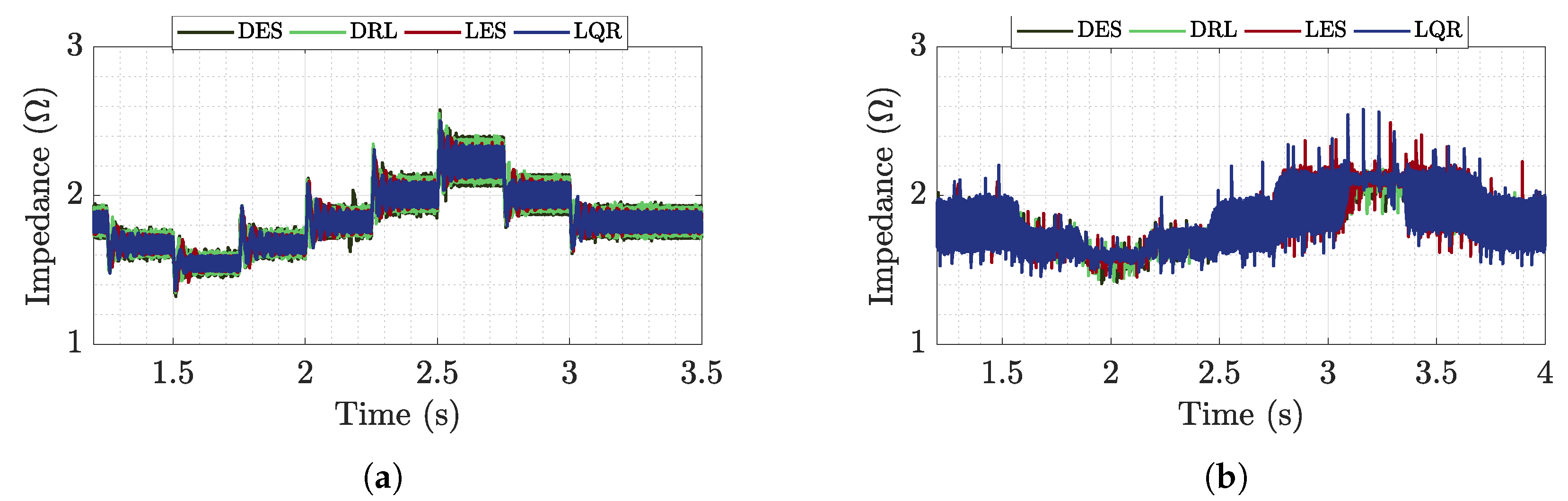

6.1.1. Time Analysis

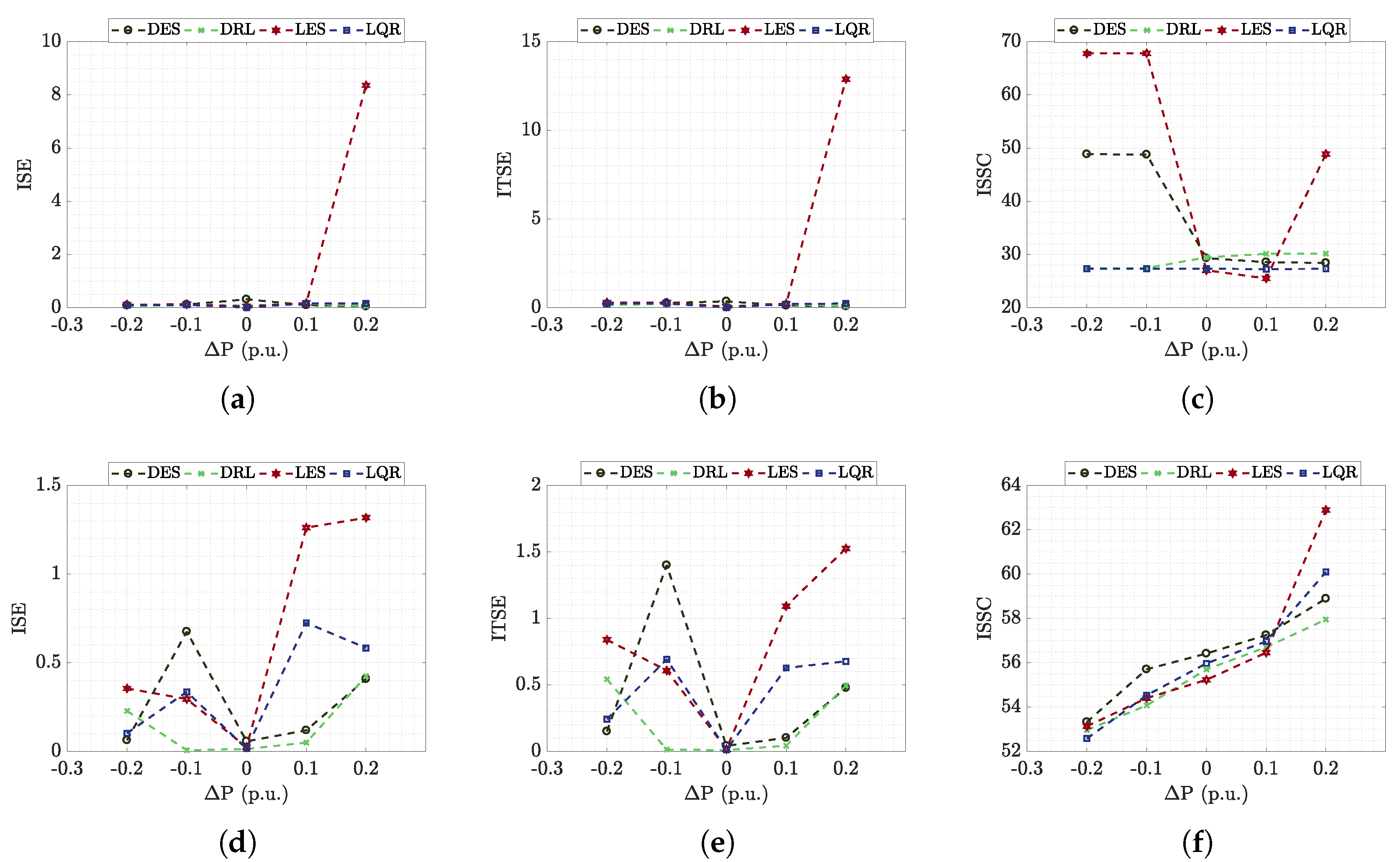

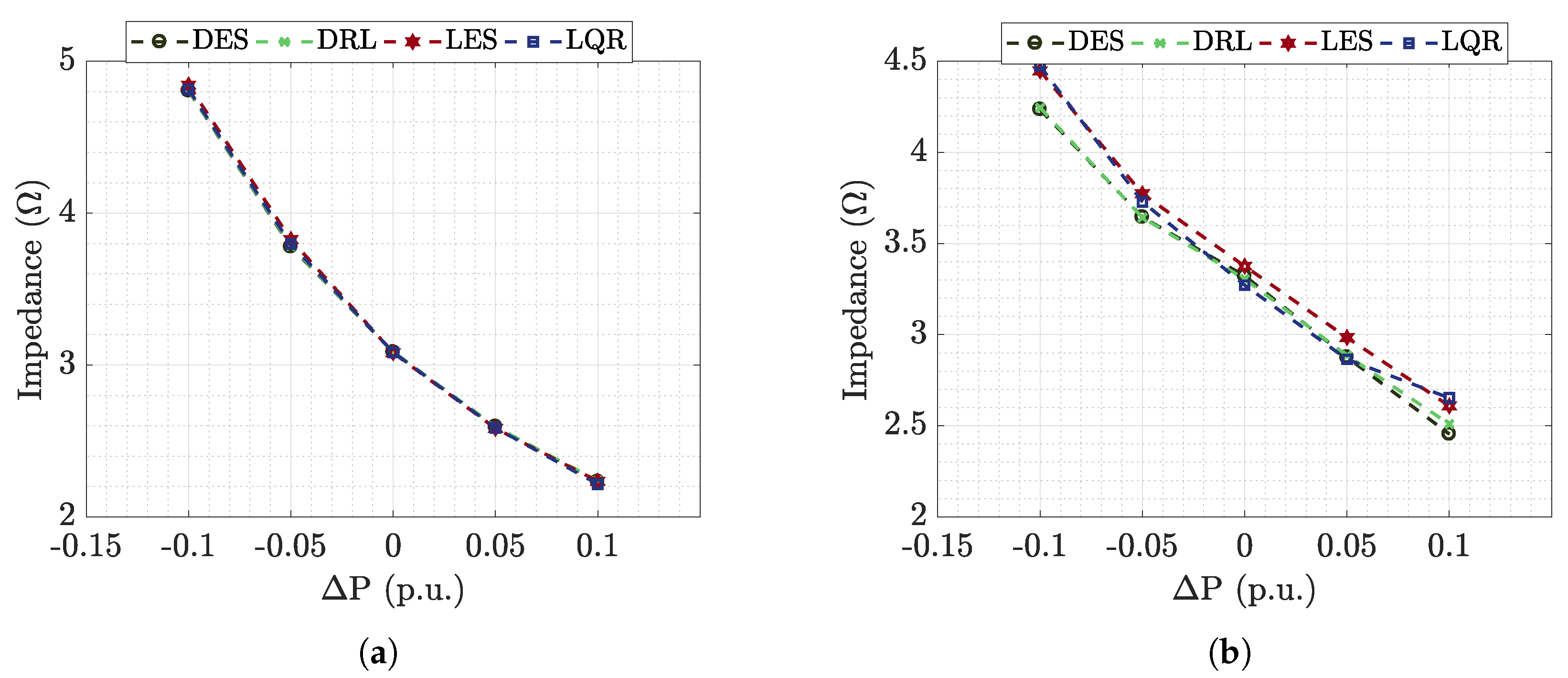

6.1.2. Performance Analysis

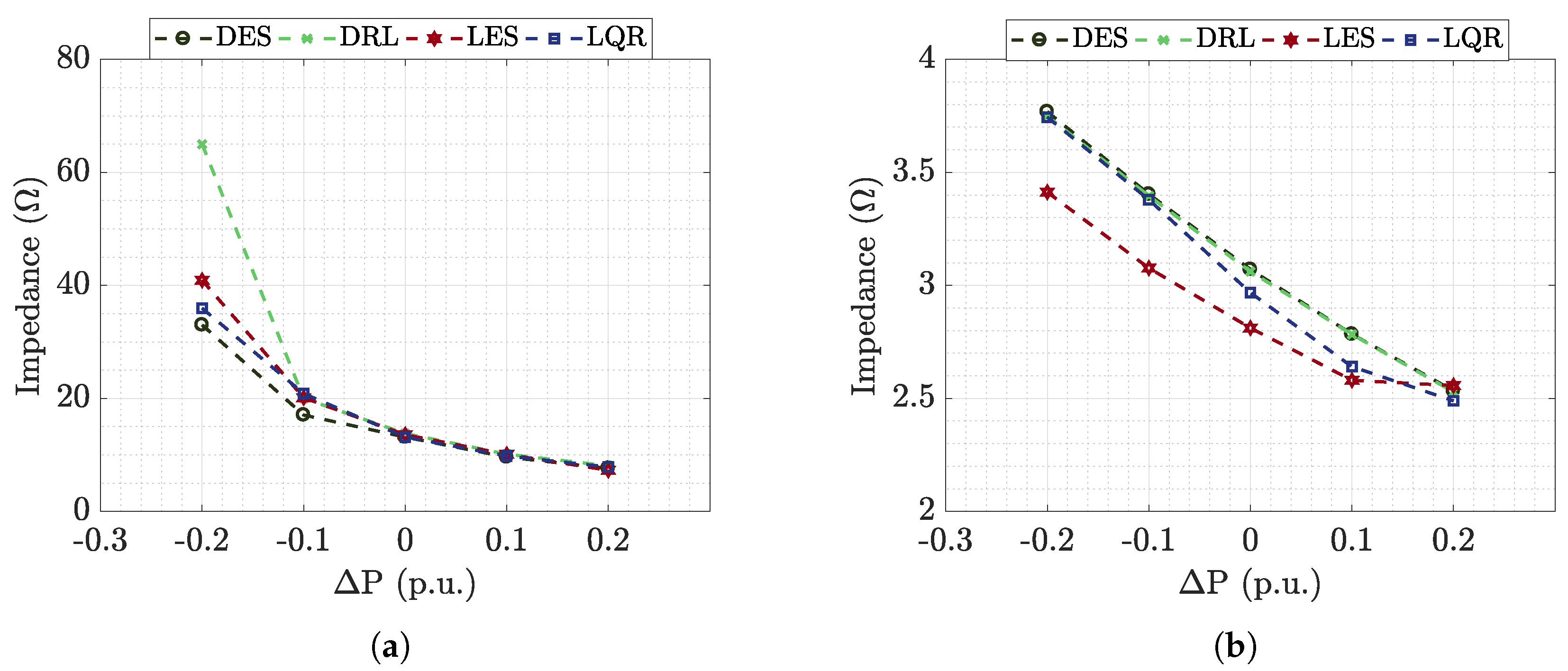

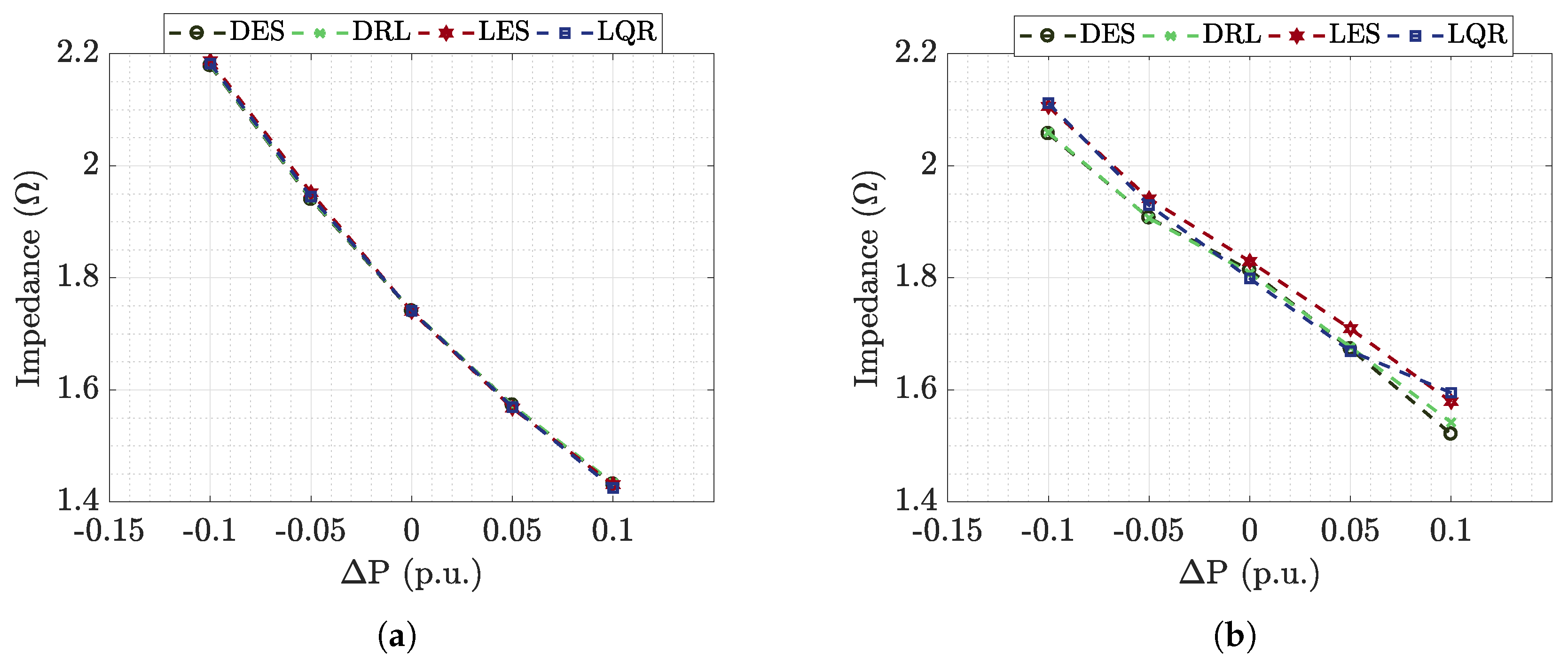

6.1.3. Stability Analysis

6.2. Buck-Boost Microgrid Analysis

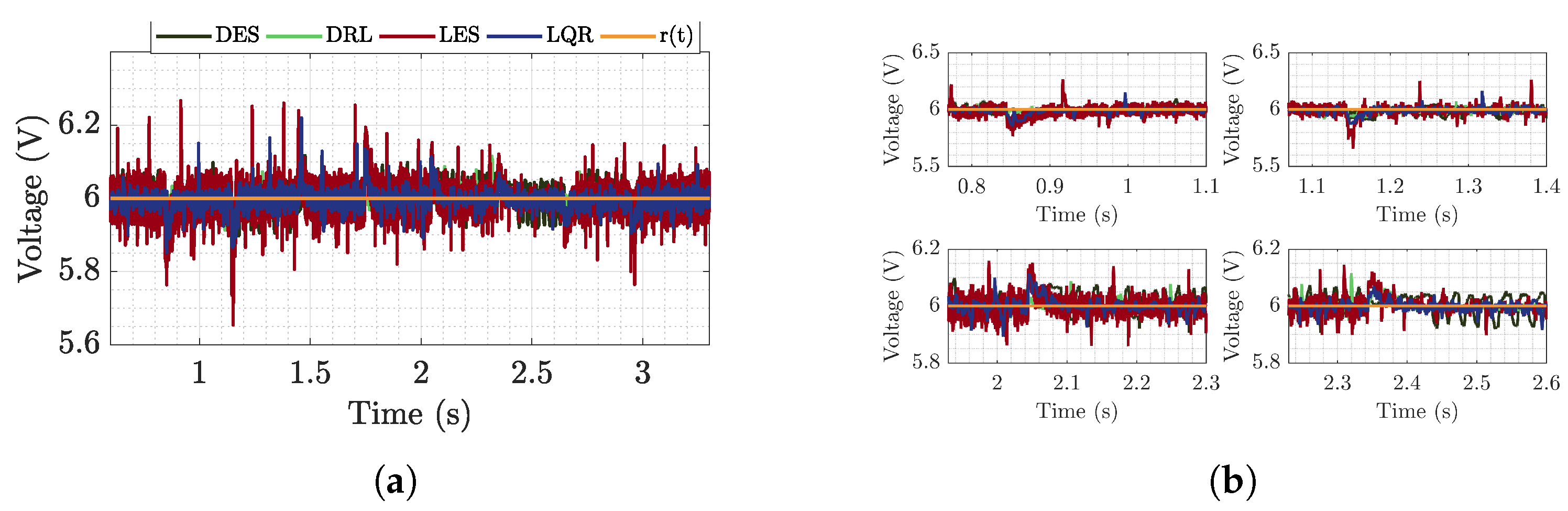

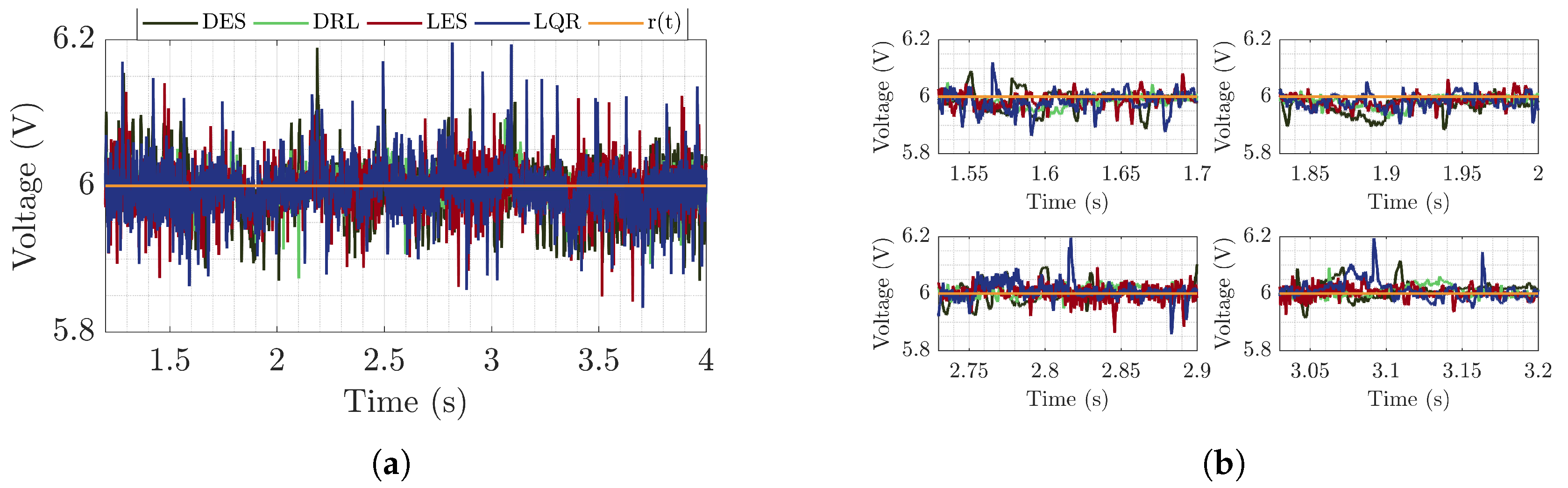

6.2.1. Time Analysis

- The boost converter causes greater voltage and current ripples in the system, thus the regulatory effect of CPL converter is spoiled;

- The boost converter dynamics during the test, for the same gains, is distinct from the simulation when it is connected to the DC bus due non-linearities found in a test, thus it is noticed that the effect of a CPL is better observed when the converter power regulation performance is closer to instantaneous, also indicating that the design of a fast feeder can help mitigate the effect of CPL.

6.2.2. Performance Analysis

6.2.3. Stability Analysis

7. Conclusions

Author Contributions

Funding

Acknowledgments

Conflicts of Interest

References

- Olalla, C.; Queinnec, I.; Leyva, R.; El Aroudi, A. Robust optimal control of bilinear DC-DC converters. Control. Eng. Pract. 2011, 19, 688–699. [Google Scholar] [CrossRef]

- Lu, Y.; Zhu, H.; Huang, X.; Lorenz, R.D. Inverse-System decoupling control of DC/DC converters. Energies 2019, 12, 179. [Google Scholar] [CrossRef]

- Marcillo, K.E.L.; Guingla, D.A.P.; Barra, W.; de Medeiros, R.L.P.; Rocha, E.M.; Benavides, D.A.V.; Nogueira, F.G. Interval Robust Controller to Minimize Oscillations Effects Caused by Constant Power Load in a DC Multi-Converter Buck-Buck System. IEEE Access 2019, 7. [Google Scholar] [CrossRef]

- Aldhaheri, A.; Etemadi, A. Adaptive stabilization and dynamic performance preservation of cascaded DC-DC systems by incorporating low pass filters. Energies 2018, 11, 440. [Google Scholar] [CrossRef]

- Bonfiglio, A.; Brignone, M.; Invernizzi, M.; Labella, A.; Mestriner, D.; Procopio, R. A Simplified Microgrid Model for the Validation of Islanded Control Logics. Energies 2017, 10, 1141. [Google Scholar] [CrossRef]

- Kwasinski, A.; Onwuchekwa, C.N. Dynamic behavior and stabilization of DC microgrids with instantaneous constant-power loads. IEEE Trans. Power Electron. 2011, 26, 822–834. [Google Scholar] [CrossRef]

- Dragicevic, T.; Lu, X.; Vasquez, J.C.; Guerrero, J.M. DC Microgrids-Part I: A Review of Control Strategies and Stabilization Techniques. IEEE Trans. Power Electron. 2016, 31, 4876–4891. [Google Scholar] [CrossRef]

- Elsayed, A.T.; Mohamed, A.A.; Mohammed, O.A. DC microgrids and distribution systems: An overview. Electr. Power Syst. Res. 2015, 119, 407–417. [Google Scholar] [CrossRef]

- Singh, S.; Gautam, A.R.; Fulwani, D. Constant power loads and their effects in DC distributed power systems: A review. Renew. Sustain. Energy Rev. 2017, 72, 407–421. [Google Scholar] [CrossRef]

- Wang, C.; Duan, J.; Fan, B.; Yang, Q.; Liu, W. Decentralized High-Performance Control of DC Microgrids. IEEE Trans. Smart Grid 2019, 10, 3355–3363. [Google Scholar] [CrossRef]

- Riccobono, A.; Santi, E. Comprehensive Review of Stability Criteria for DC Power Distribution Systems. IEEE Trans. Ind. Appl. 2014, 50, 3525–3535. [Google Scholar] [CrossRef]

- Dragičević, T. Dynamic Stabilization of DC Microgrids with Predictive Control of Point-of-Load Converters. IEEE Trans. Power Electron. 2018, 33, 10872–10884. [Google Scholar] [CrossRef]

- Liu, S.; Su, P.; Zhang, L. Article a nonlinear disturbance observer based virtual negative inductor stabilizing strategy for dc microgrid with constant power loads. Energies 2018, 11, 3174. [Google Scholar] [CrossRef]

- AL-Nussairi, M.K.; Bayindir, R.; Padmanaban, S.; Mihet-Popa, L.; Siano, P. Constant power loads (CPL) with Microgrids: Problem definition, stability analysis and compensation techniques. Energies 2017, 10, 1656. [Google Scholar] [CrossRef]

- Mosskull, H. Constant power load stabilization. Control. Eng. Pract. 2018, 72, 114–124. [Google Scholar] [CrossRef]

- Liu, Z.; Su, M.; Sun, Y.; Yuan, W.; Han, H.; Feng, J. Existence and stability of equilibrium of DC microgrid with constant power loads. IEEE Trans. Power Syst. 2018, 33, 6999–7010. [Google Scholar] [CrossRef]

- El Aroudi, A.; Martínez-Treviño, B.A.; Vidal-Idiarte, E.; Cid-Pastor, A. Fixed switching frequency digital sliding-mode control of DC-DC power supplies loaded by constant power loads with inrush current limitation capability. Energies 2019, 12, 1055. [Google Scholar] [CrossRef]

- Azzano, J.L.A.; Moré, J.J.; Puleston, P.F. Stability criteria for input filter design in converters with CPL: Applications in sliding mode controlled power systems. Energies 2019, 12, 4048. [Google Scholar] [CrossRef]

- Kabalan, M.; Singh, P.; Niebur, D. Large Signal Lyapunov-Based Stability Studies in Microgrids: A Review. IEEE Trans. Smart Grid 2017, 8, 2287–2295. [Google Scholar] [CrossRef]

- Hossain, E.; Perez, R.; Padmanaban, S.; Mihet-Popa, L.; Blaabjerg, F.; Ramachandaramurthy, V.K. Sliding mode controller and lyapunov redesign controller to improve microgrid stability: A comparative analysis with CPL power variation. Energies 2017, 10, 1959. [Google Scholar] [CrossRef]

- Liang, H.; Liu, Z.; Liu, H. Stabilization method considering disturbance mitigation for DC microgrids with constant power loads. Energies 2019, 12, 873. [Google Scholar] [CrossRef]

- Su, X.; Han, M.; Guerrero, J.M.; Sun, H. Microgrid stability controller based on adaptive robust total SMC. Energies 2015, 8, 1784–1801. [Google Scholar] [CrossRef]

- Rodríguez-Licea, M.A.; Pérez-Pinal, F.J.; Nuñez-Perez, J.C.; Herrera-Ramirez, C.A. Nonlinear robust control for low voltage direct-current residential microgrids with constant power loads. Energies 2018, 11, 1130. [Google Scholar] [CrossRef]

- Mardani, M.M.; Vafamand, N.; Khooban, M.H.; Dragičević, T.; Blaabjerg, F. Design of Quadratic D-Stable Fuzzy Controller for DC Microgrids With Multiple CPLs. IEEE Trans. Ind. Electron. 2019, 66, 4805–4812. [Google Scholar] [CrossRef]

- Haseltalab, A.; Botto, M.A.; Negenborn, R.R. Model Predictive DC Voltage Control for all-electric ships. Control. Eng. Pract. 2019, 90, 133–147. [Google Scholar] [CrossRef]

- Yousefizadeh, S.; Bendtsen, J.D.; Vafamand, N.; Khooban, M.H.; Dragicevic, T.; Blaabjerg, F. EKF-Based Predictive Stabilization of Shipboard DC Microgrids with Uncertain Time-Varying Load. IEEE J. Emerg. Sel. Top. Power Electron. 2019, 7, 901–909. [Google Scholar] [CrossRef]

- Saad, A.A.; Faddel, S.; Youssef, T.; Mohammed, O. Small-signal model predictive control based resilient energy storage management strategy for all electric ship MVDC voltage stabilization. J. Energy Storage 2019, 21, 370–382. [Google Scholar] [CrossRef]

- Lucas-Marcillo, K.E.; Plaza Guingla, D.A.; Barra, W.; De Medeiros, R.L.P.; Melo Rocha, E.; Vaca-Benavides, D.A.; Rios Orellana, S.J.; Herrera Muentes, E.V. Novel robust methodology for controller design aiming to ensure DC microgrid stability under CPL power variation. IEEE Access 2019, 7, 64206–64222. [Google Scholar] [CrossRef]

- Baranwal, M.; Askarian, A.; Salapaka, S.; Salapaka, M. A Distributed Architecture for Robust and Optimal Control of DC Microgrids. IEEE Trans. Ind. Electron. 2019, 66, 3082–3092. [Google Scholar] [CrossRef]

- Zhang, H.; Shi, Y.; Wang, J.; Chen, H. A New Delay-Compensation Scheme for Networked Control Systems in Controller Area Networks. IEEE Trans. Ind. Electron. 2018, 65, 7239–7247. [Google Scholar] [CrossRef]

- Ornelas-Tellez, F.; Rico-Melgoza, J.J.; Espinosa-Juarez, E.; Sanchez, E.N. Optimal and Robust Control in DC Microgrids. IEEE Trans. Smart Grid 2018, 9, 5543–5553. [Google Scholar] [CrossRef]

- Rahimi, A.M.; Emadi, A. An Analytical Investigation of DC/DC Power Electronic Converters With Constant Power Loads in Vehicular Power Systems. IEEE Trans. Veh. Technol. 2009, 58, 2689–2702. [Google Scholar] [CrossRef]

- Duarte-Mermoud, M.A.; Prieto, R.A. Performance index for quality response of dynamical systems. ISA Trans. 2007, 43, 133–151. [Google Scholar] [CrossRef]

| Feeder Parameters | |||||||

|---|---|---|---|---|---|---|---|

| Parameters | Symbol | Value | Unit | Parameters | Symbol | Value | Unit |

| Input voltage | 12.00 | V | Resistance | 4.00 | |||

| Output voltage | 6.00 | V | Inductor | 1.00 | mH | ||

| Duty cycle | 0.50 | - | Capacitor | 2.20 | mF | ||

| Frequency | 20.00 | kHz | |||||

| Method | Method | ||||||

|---|---|---|---|---|---|---|---|

| DES | 0.4481 | −0.9168 | 0.4706 | LES | 0.0817 | 0.0050 | 137.5 |

| DRL | 0.6190 | −1.2230 | 0.6068 | LQR | 0.0402 | 0.0081 | 142.5 |

| CPL Buck | CPL Boost | ||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| Parameters | Symbol | Value | Unit | Parameters | Symbol | Value | Unit | Parameters | Symbol | Value | Unit | Parameters | Symbol | Value | Unit |

| Input voltage | 6.00 | V | Frequency | 20.0 | kHz | Input voltage | 6.00 | V | Frequency | 20.0 | kHz | ||||

| Base power | 9.00 | W | Resistance | 4.00 | Base power | 36.0 | W | Resistance | 8.00 | ||||||

| Output power | 0.30 | p.u. | Inductor | 1.00 | mH | Output power | 0.30 | p.u. | Inductor | 1 | mH | ||||

| Duty cyle | 0.55 | - | Capacitor | 2.20 | mF | Duty cyle | 0.65 | - | Capacitor | 2.20 | mF | ||||

| Method | Method | ||||||

|---|---|---|---|---|---|---|---|

| DES-buck | 19.6381 | −37.8491 | 18.2812 | LES-boost | 0.0722 | 0.0032 | 212.5 |

| Simulation | Test | ||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| −0.2 | −0.1 | 0.0 | 0.1 | 0.2 | −0.2 | −0.1 | 0.0 | 0.1 | 0.2 | ||||

| DES | 0.1070 | 0.1889 | 0.2321 | 0.2929 | 0.3434 | 0.2329 | DES | 0.0568 | 0.1487 | 0.2323 | 0.3039 | 0.3664 | 0.2216 |

| DRL | 0.0559 | 0.1668 | 0.2235 | 0.2817 | 0.3298 | 0.2115 | DRL | 0.0619 | 0.1510 | 0.2347 | 0.3042 | 0.3677 | 0.2239 |

| LES | 0.0888 | 0.1655 | 0.2270 | 0.2831 | 0.3539 | 0.2237 | LES | 0.1468 | 0.2308 | 0.2974 | 0.3553 | 0.3611 | 0.2783 |

| LQR | 0.1014 | 0.1600 | 0.2326 | 0.2888 | 0.3366 | 0.2239 | LQR | 0.0627 | 0.1549 | 0.2577 | 0.3403 | 0.3783 | 0.2388 |

| Simulation | Test | ||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| −0.2 | −0.1 | 0.0 | 0.1 | 0.2 | −0.2 | −0.1 | 0.0 | 0.1 | 0.2 | ||||

| DES | 0.4536 | 0.5131 | 0.5640 | 0.6060 | 0.6414 | 0.5556 | DES | 0.4854 | 0.5230 | 0.5492 | 0.5816 | 0.6197 | 0.5518 |

| DRL | 0.4532 | 0.5132 | 0.5642 | 0.6063 | 0.6408 | 0.5556 | DRL | 0.4847 | 0.5229 | 0.5507 | 0.5805 | 0.6145 | 0.5507 |

| LES | 0.4509 | 0.5083 | 0.5647 | 0.6068 | 0.6392 | 0.5540 | LES | 0.4725 | 0.5115 | 0.5446 | 0.5725 | 0.6051 | 0.5412 |

| LQR | 0.4610 | 0.5236 | 0.5647 | 0.6072 | 0.6482 | 0.5610 | LQR | 0.4715 | 0.5146 | 0.5504 | 0.5818 | 0.6010 | 0.5438 |

© 2020 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

de Bessa, I.V.; de Medeiros, R.L.P.; Bessa, I.; Ayres Junior, F.A.C.; de Menezes, A.R.; Torres, G.M.; Chaves Filho, J.E. Comparative Study of Control Strategies for Stabilization and Performance Improvement of DC Microgrids with a CPL Connected. Energies 2020, 13, 2663. https://doi.org/10.3390/en13102663

de Bessa IV, de Medeiros RLP, Bessa I, Ayres Junior FAC, de Menezes AR, Torres GM, Chaves Filho JE. Comparative Study of Control Strategies for Stabilization and Performance Improvement of DC Microgrids with a CPL Connected. Energies. 2020; 13(10):2663. https://doi.org/10.3390/en13102663

Chicago/Turabian Stylede Bessa, Isaías V., Renan L. P. de Medeiros, Iury Bessa, Florindo A. C. Ayres Junior, Alessandra R. de Menezes, Gustavo M. Torres, and João Edgar Chaves Filho. 2020. "Comparative Study of Control Strategies for Stabilization and Performance Improvement of DC Microgrids with a CPL Connected" Energies 13, no. 10: 2663. https://doi.org/10.3390/en13102663

APA Stylede Bessa, I. V., de Medeiros, R. L. P., Bessa, I., Ayres Junior, F. A. C., de Menezes, A. R., Torres, G. M., & Chaves Filho, J. E. (2020). Comparative Study of Control Strategies for Stabilization and Performance Improvement of DC Microgrids with a CPL Connected. Energies, 13(10), 2663. https://doi.org/10.3390/en13102663