Understanding Turn-On Transients of SiC High-Power Modules: Drain-Source Voltage Plateau Characteristics

Abstract

1. Introduction

2. Experiment Setup

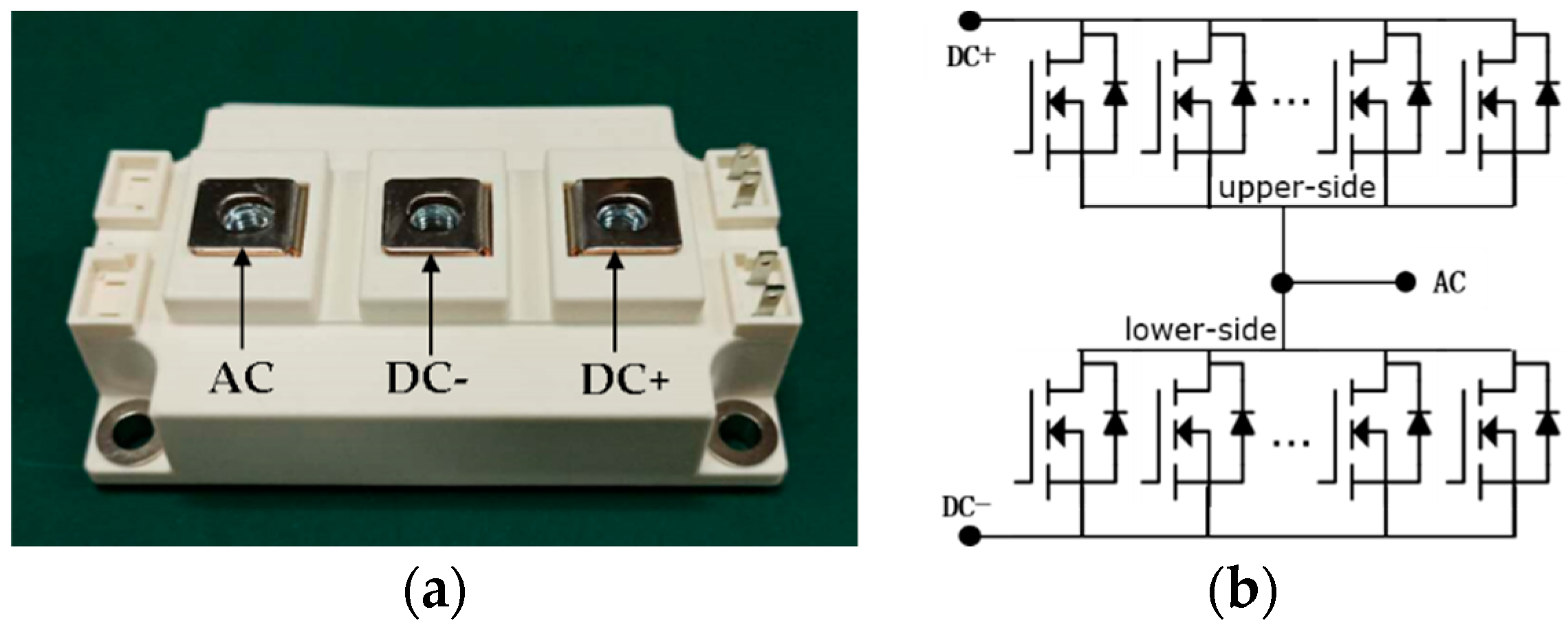

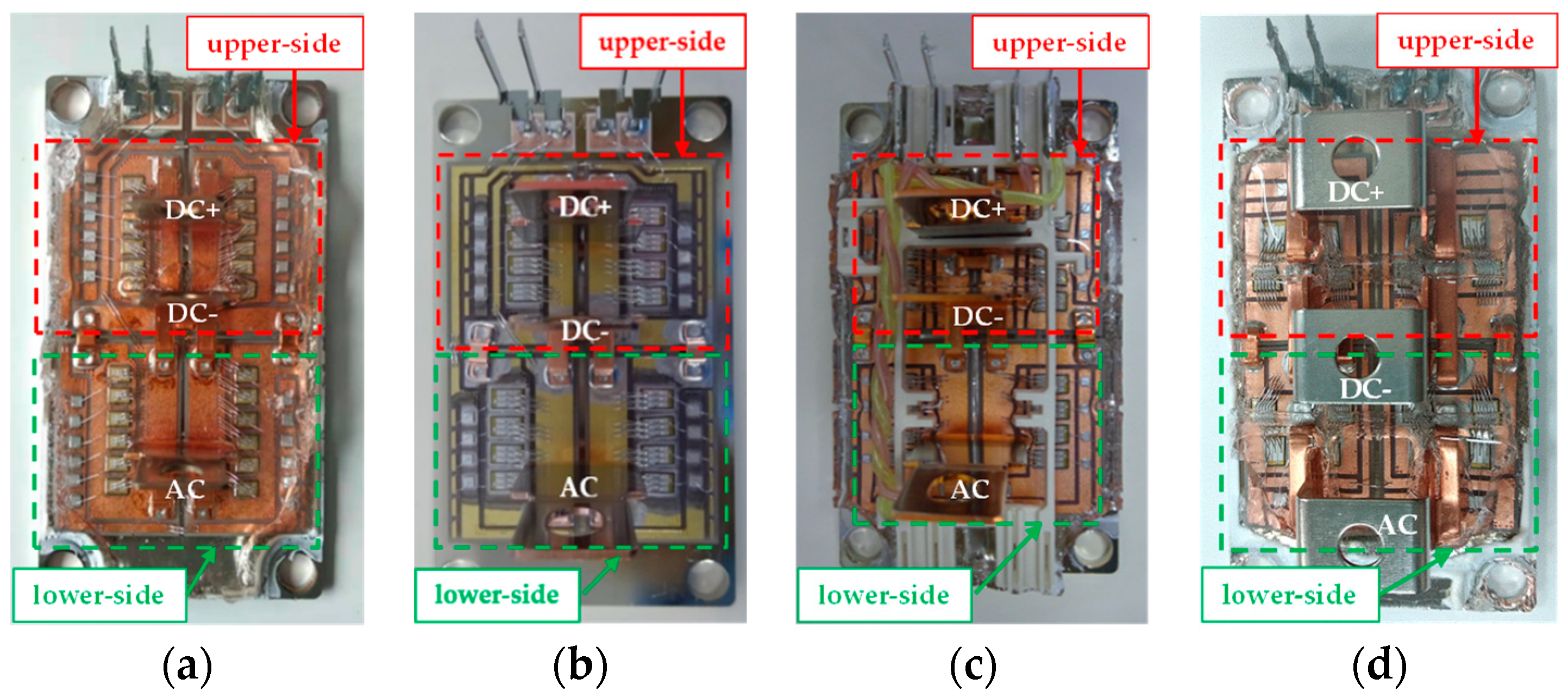

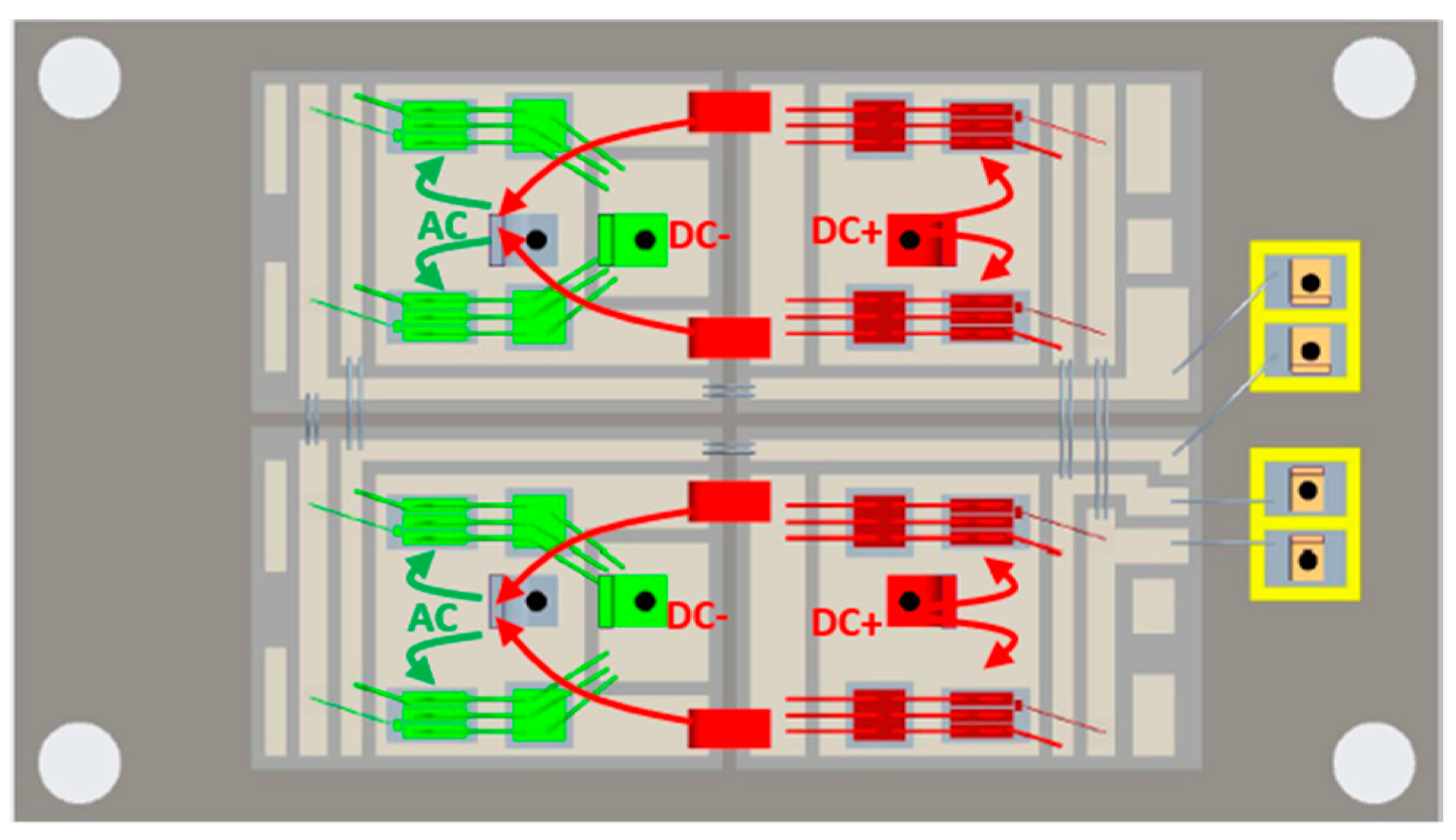

2.1. Introduction of the Developed SiC High-Power Module

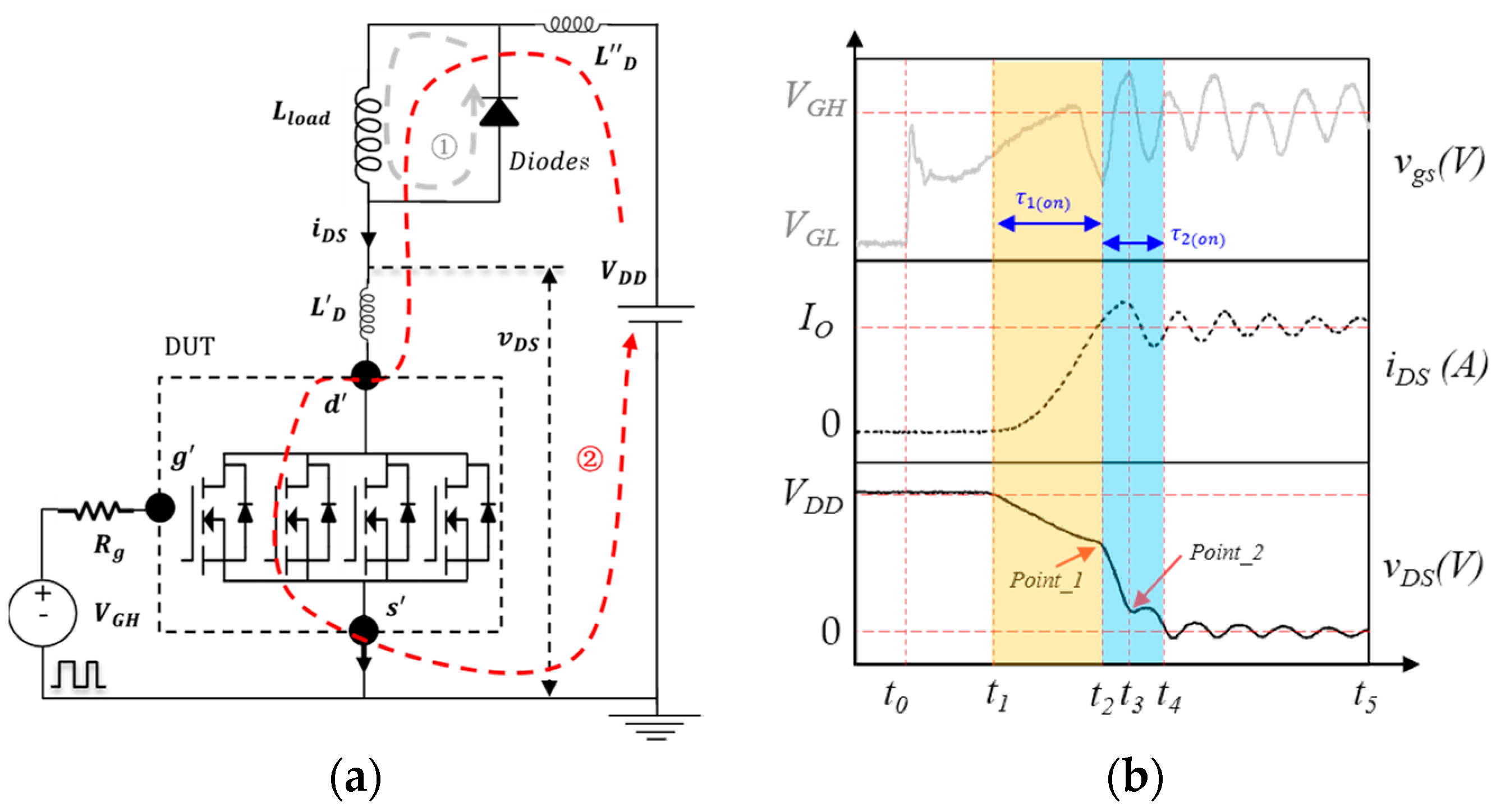

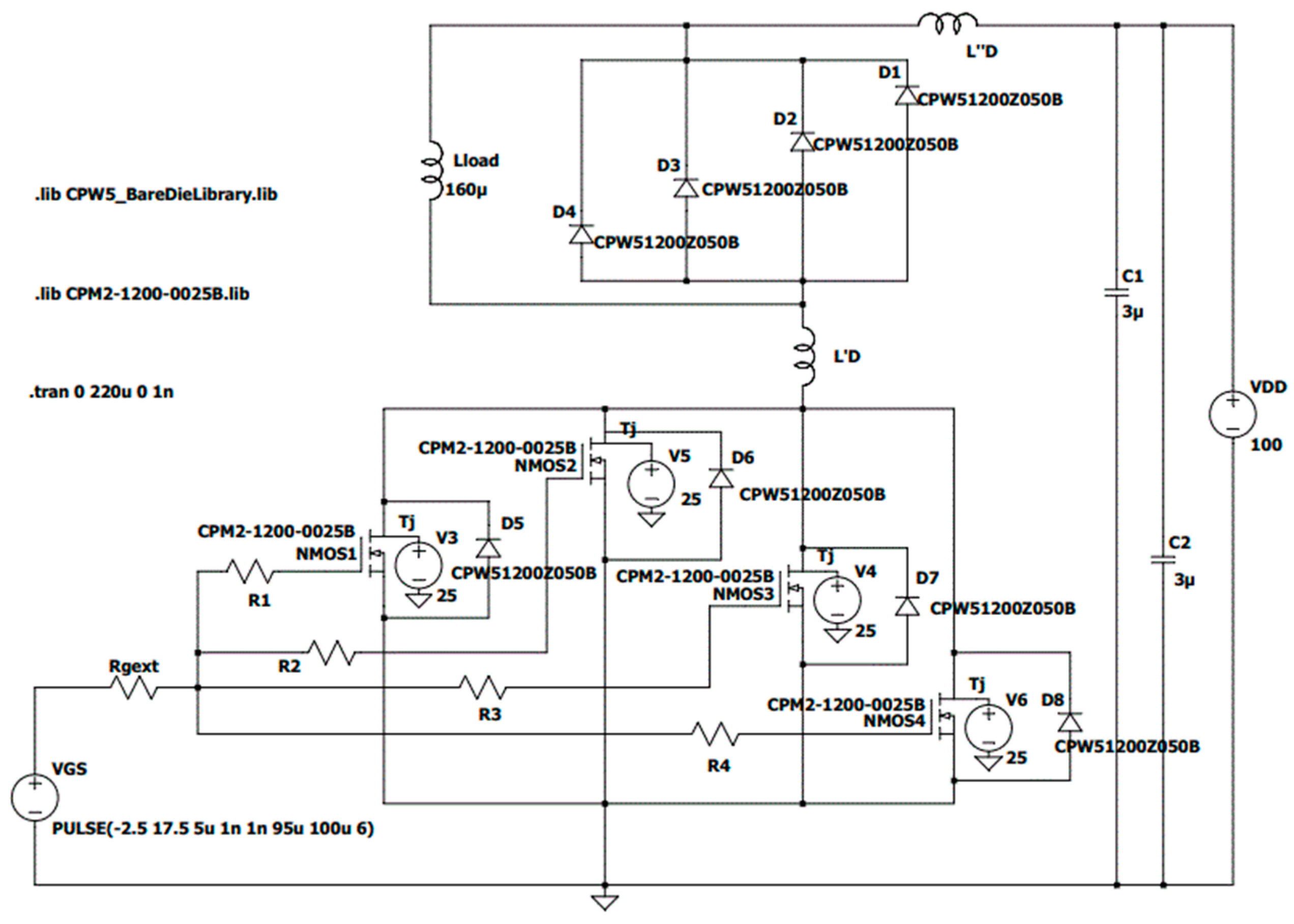

2.2. Introduction of the Double Pulse Test Platform

2.3. Introduction of the Turn-On Transient Process for SiC High-Power Module

3. Experimental Results

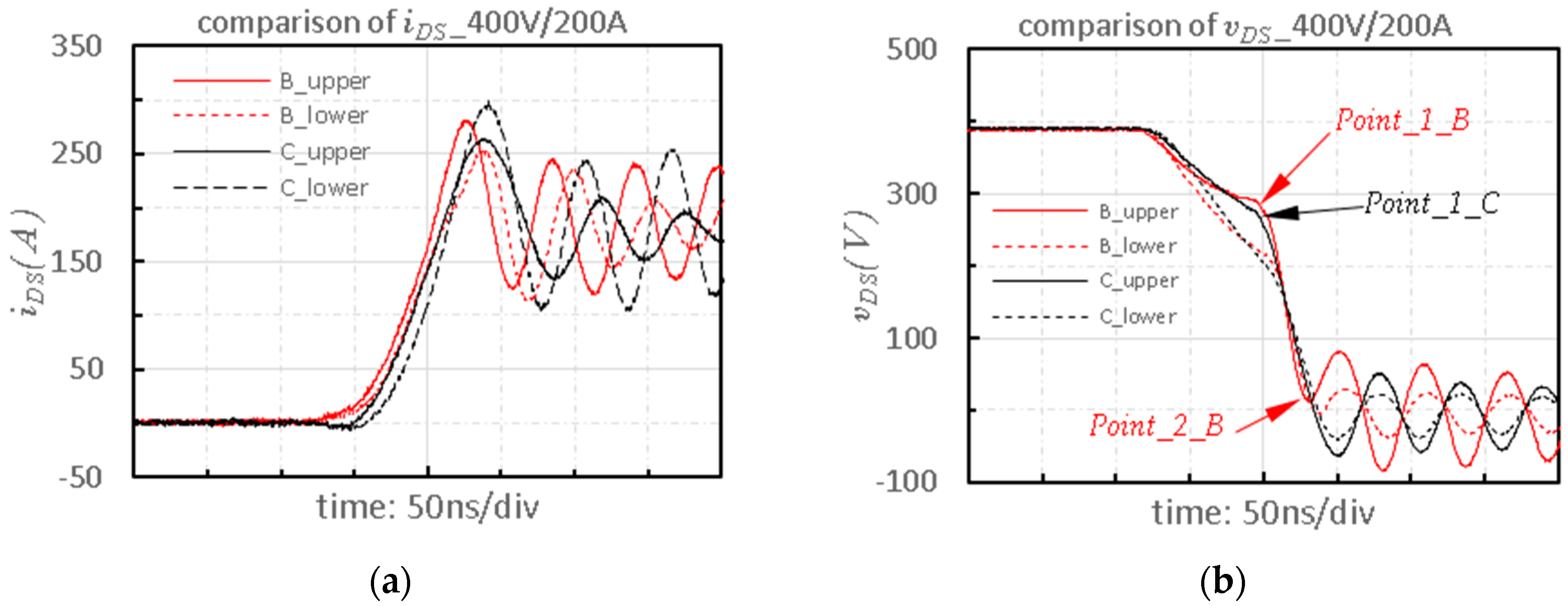

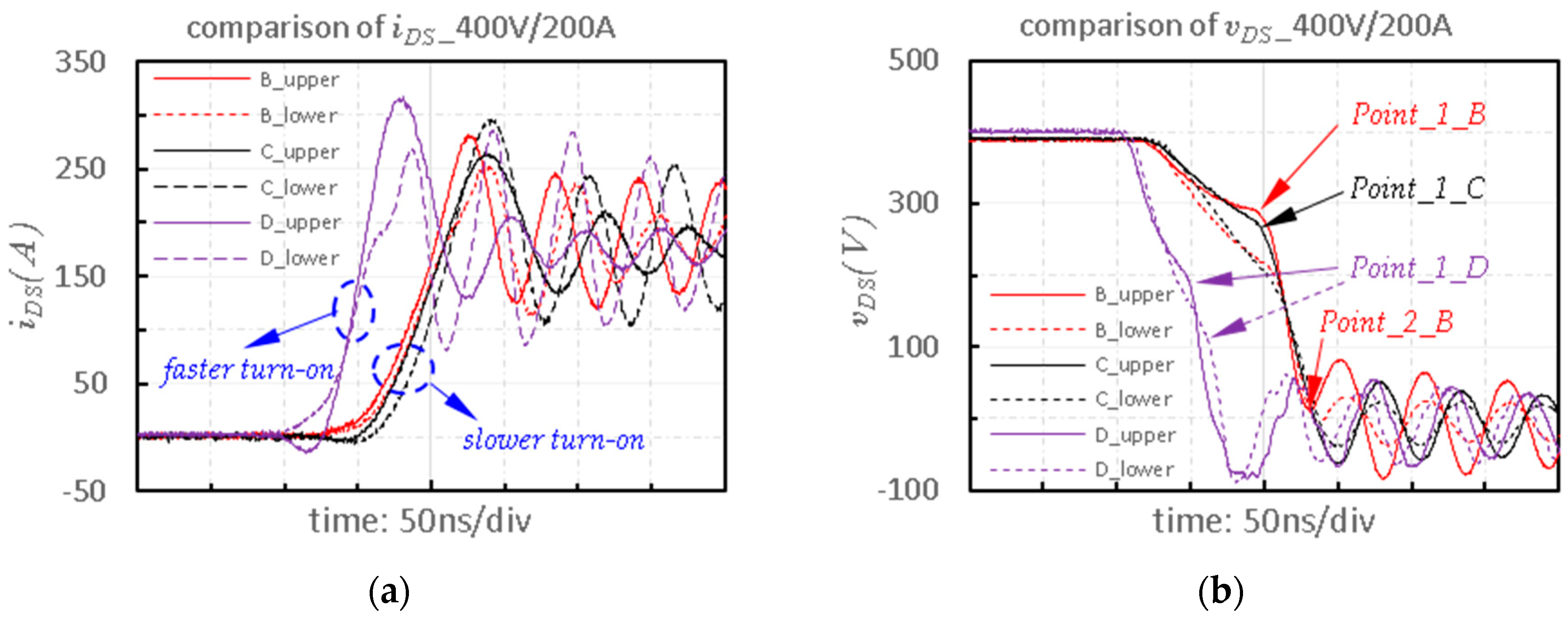

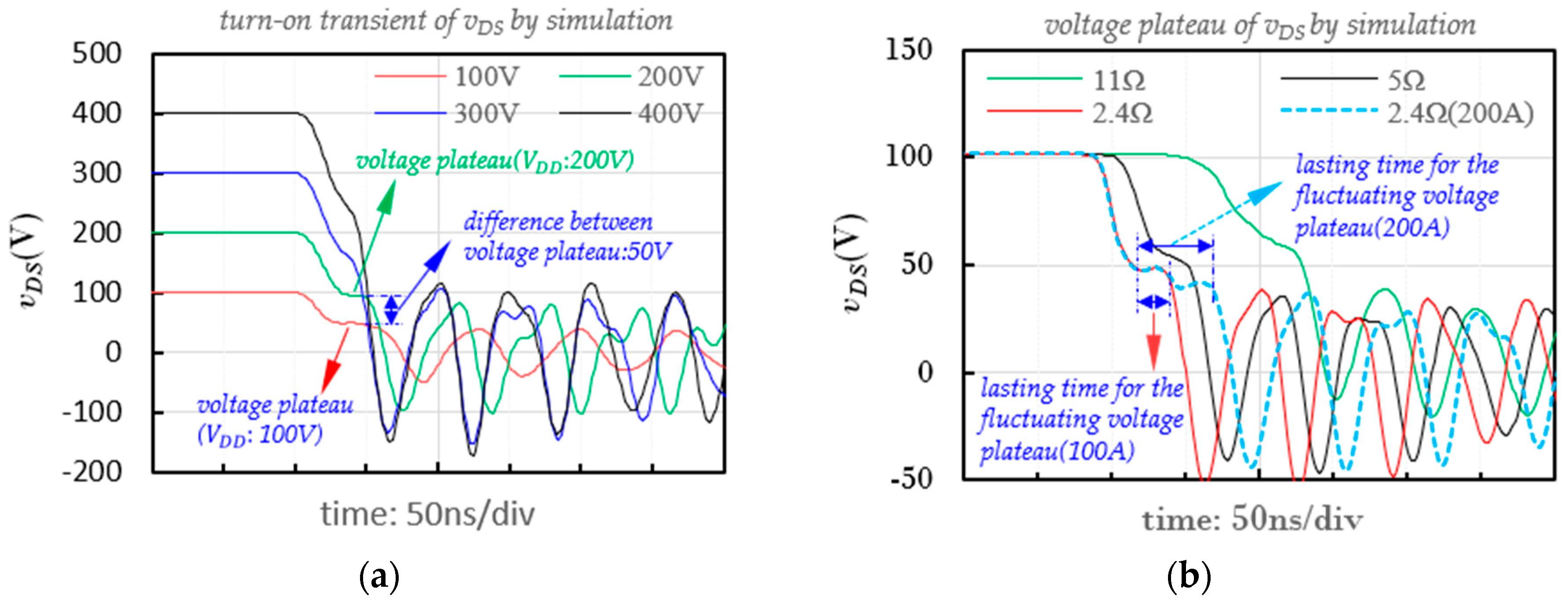

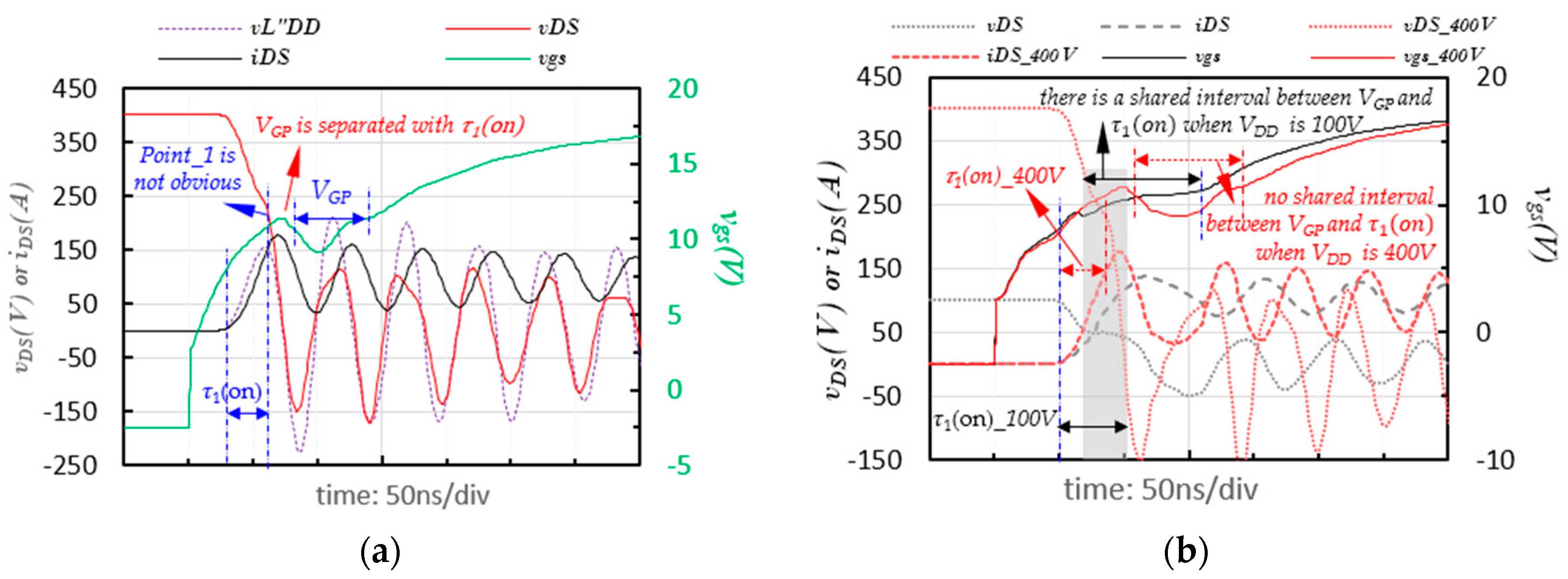

3.1. Turn-On Transient at Condition of Relatively High

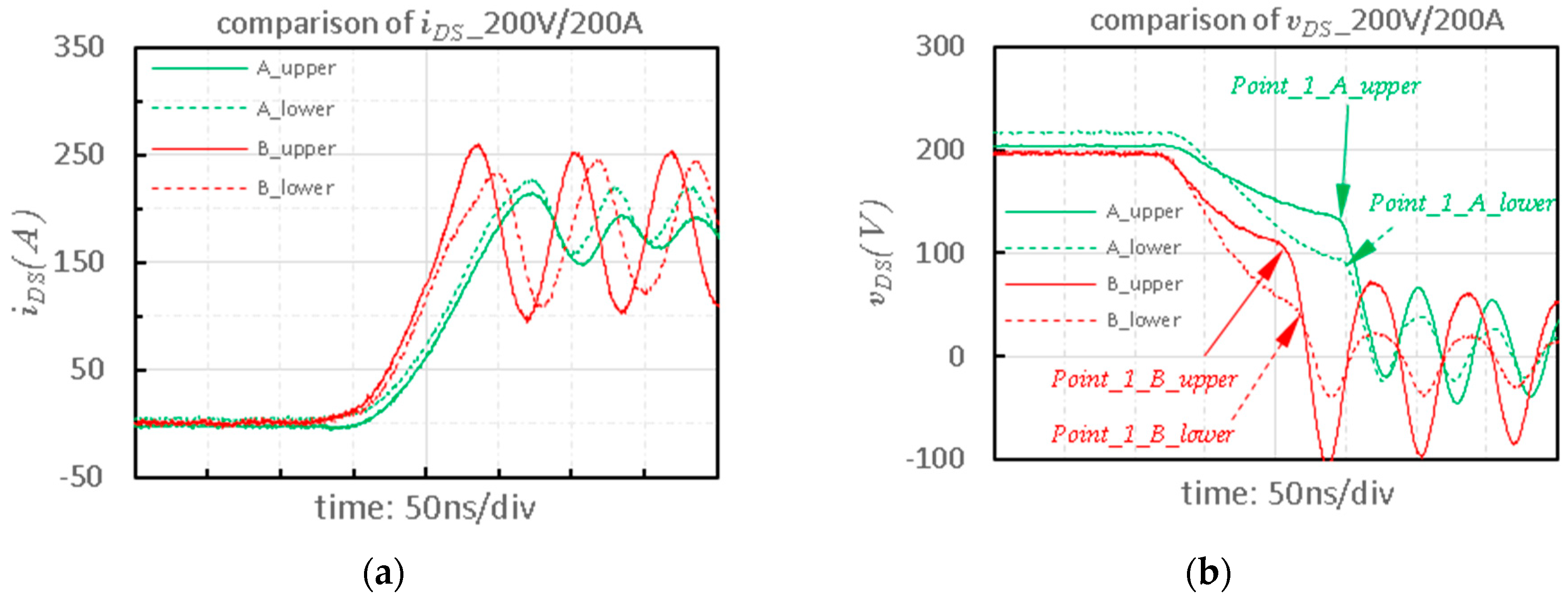

3.2. Turn-On Transient at Condition of Low

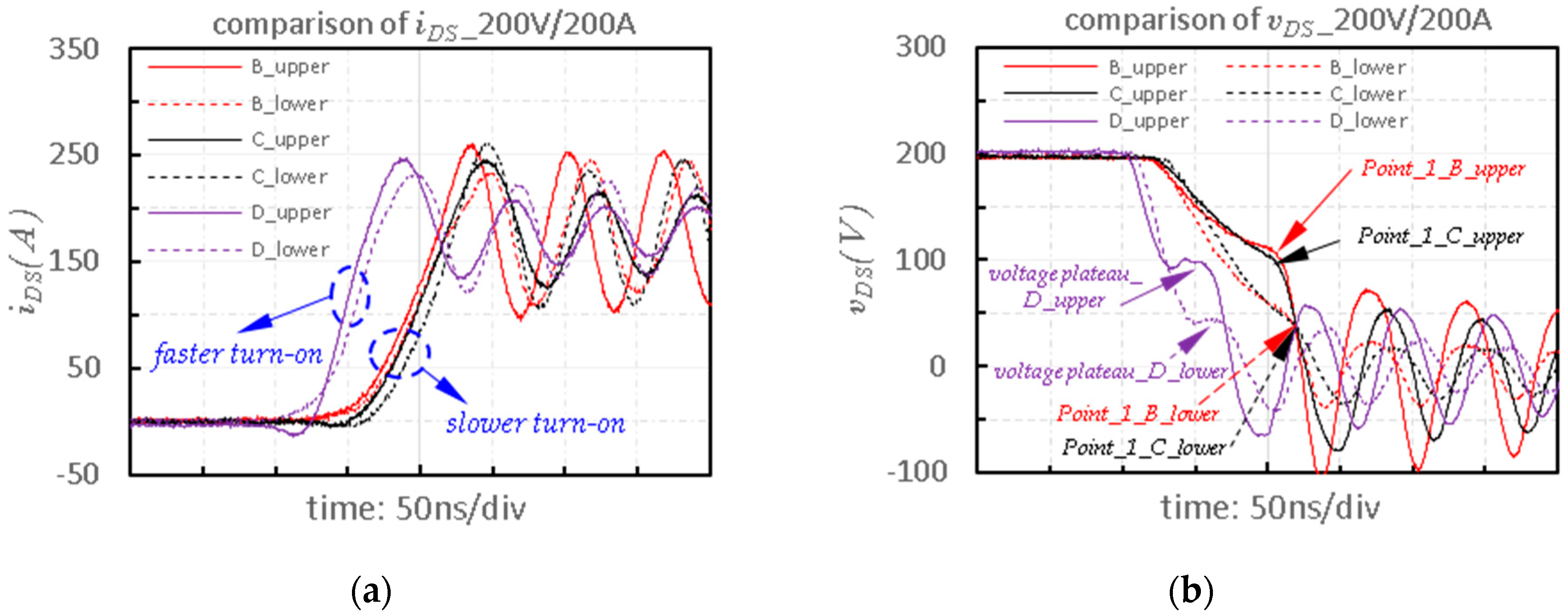

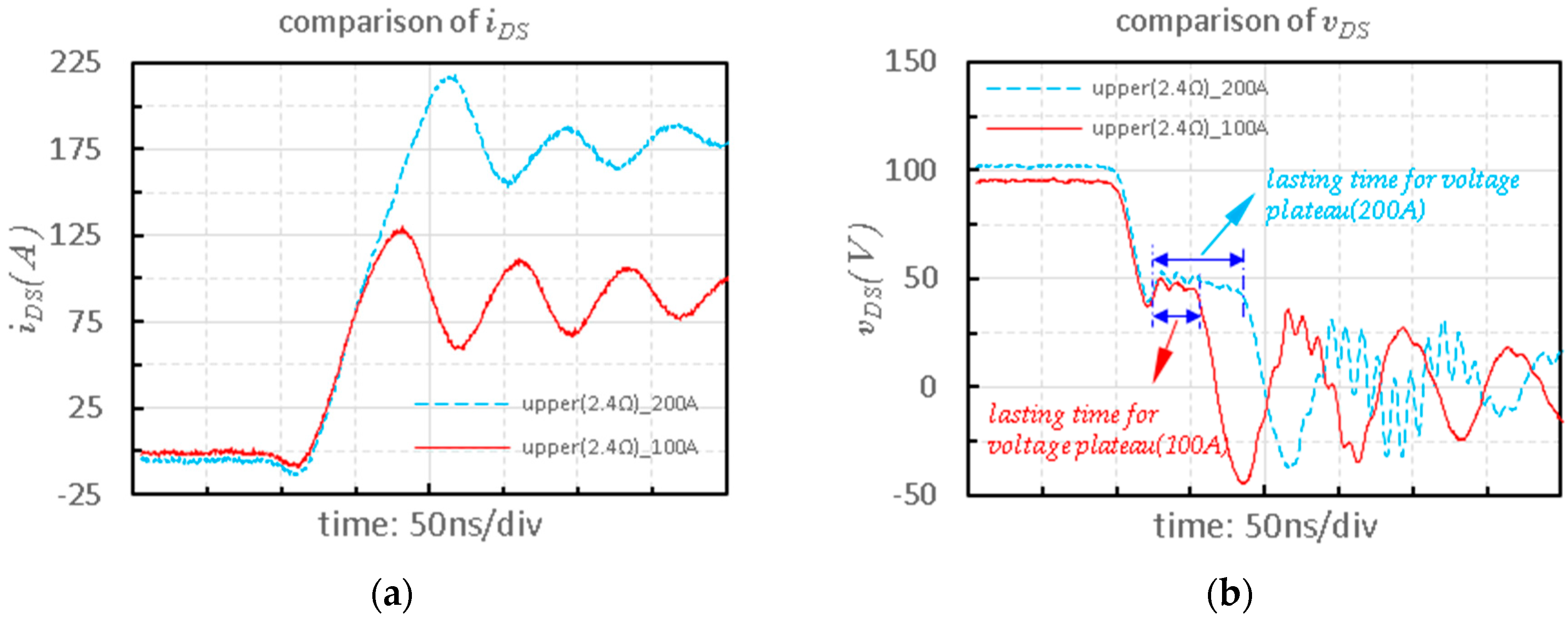

3.3. Turn-On Transient at Conditions of a Lower and Various Turn-On Speed

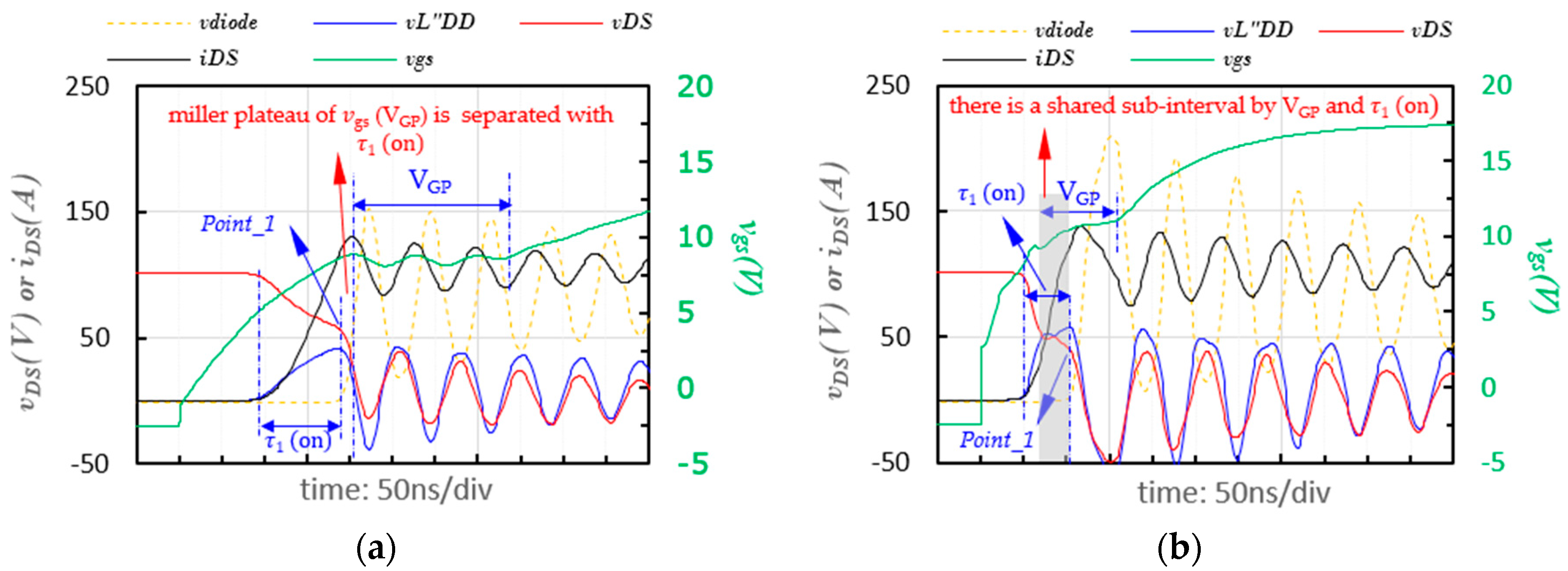

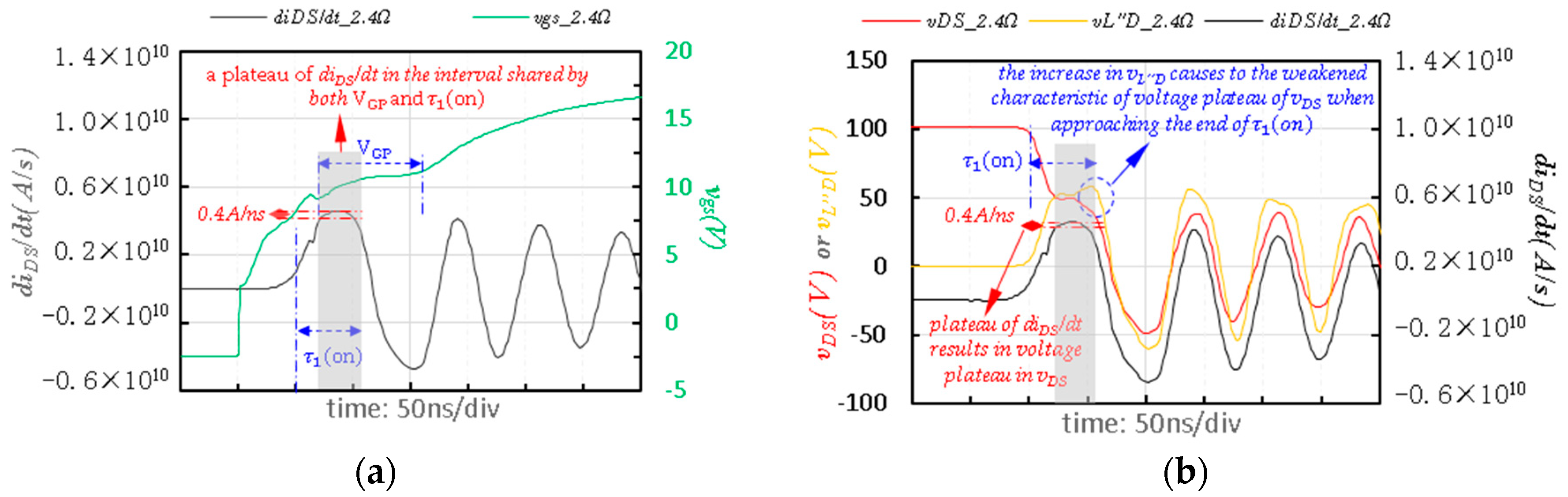

4. Simulation Study for Mechanism of Drain-Source Voltage Plateau

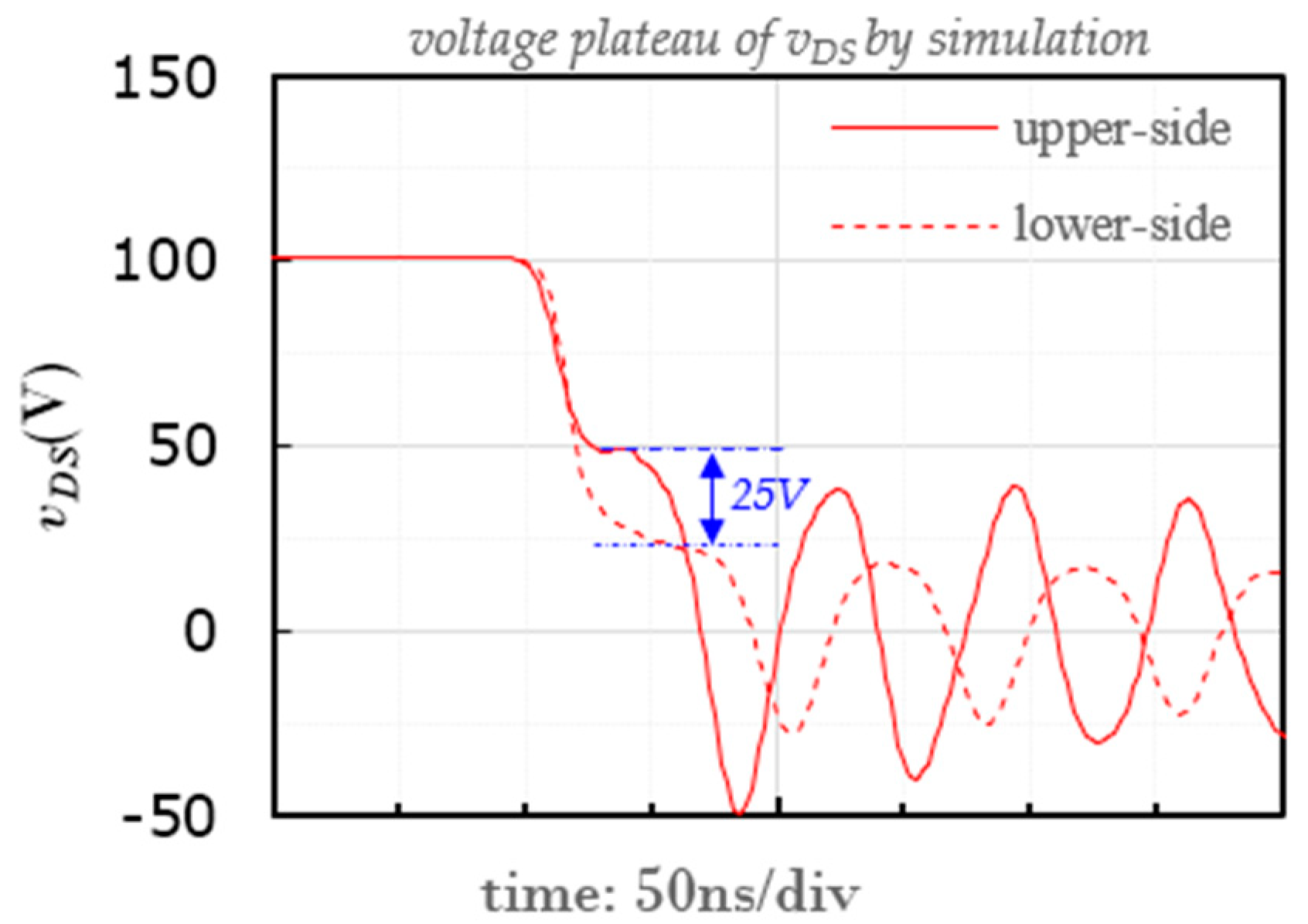

4.1. Mechanism for Characteristic of Drain-Source Voltage Plateau

4.2. Mechanism for Difference of Drain-Source Voltage Plateau between Upper-Side and Lower-Side

5. Conclusions

Author Contributions

Funding

Conflicts of Interest

References

- Xiao, Y.; Shah, H.; Chow, T.P.; Gutmann, R.J. Analytical modeling and experimental evaluation of interconnect parasitic inductance on MOSFET switching characteristics. In Proceedings of the 19th annual IEEE Applied Power Electronics Conference and Exposition, Anaheim, CA, USA, 22–26 February 2004; Volume 1, pp. 516–521. [Google Scholar]

- Teulings, W.; Schanen, J.L.; Roudet, J. MOSFET switching behavior under influence of PCB stray inductance. In Proceedings of the 1996 IEEE Industry Applications Conference Thirty-First IAS Annual Meeting, San Diego, CA, USA, 6–10 October 1996; Volume 3, pp. 1449–1453. [Google Scholar]

- Chen, Z.; Boroyevich, D.; Burgos, R. Experimental parametric study of the parasitic inductance influence on MOSFET switching characteristics. In Proceedings of the 2010 International Power Electronics Conference (ECCE ASIA), Sapporo, Japan, 21–24 June 2010; pp. 164–169. [Google Scholar]

- Merienne, F.; Roudet, J.; Schanen, J.L. Switching disturbance due to source inductance for a power MOSFET: Analysis and solutions. In Proceedings of the 1996 IEEE Power Electronics Specialists Conference, Baveno, Italy, 23–27 June 1996; Volume 2, pp. 1743–1747. [Google Scholar]

- Tiwari, S.; Midtgård, O.-M.; Undeland, T.M.; Lund, R. Parasitic capacitances and inductances hindering utilization of the fast switching potential of SiC power modules. Simulation model verified by experiment. In Proceedings of the 2017 19th European Conference on Power Electronics and Applications (EPE’17 ECCE Europe), Warsaw, Poland, 11–14 September 2017; pp. P.1–P.10. [Google Scholar]

- Wang, J.; Chung, H.S.; Li, R.T. Characterization and experimental assessment of the effects of parasitic elements on the MOSFET switching performance. IEEE Trans. Power Electron. 2013, 28, 573–590. [Google Scholar] [CrossRef]

- Incau, B.I.; Trintis, I.; Munk-Nielsen, S. Switching speed limitations of high power IGBT modules. In Proceedings of the 2015 17th European Conference on Power Electronics and Applications (EPE’15 ECCE-Europe), Geneva, Switzerland, 8–10 September 2015; pp. 1–8. [Google Scholar]

- Zhu, H.; Hefner, A.R.; Lai, J.S. Characterization of power electronics system interconnect parasitics using time domain reflectomentry. IEEE Trans. Power Electron. 1999, 14, 622–628. [Google Scholar]

- Dalal, D.N.; Christensen, N.; Jørgensen, A.B.; Jørgensen, J.K.; Bęczkowski, S.; Munk-Nielsen, S. Impact of power module parasitic capacitances on medium-voltage SiC MOSFETs switching transients. IEEE J. Emerg. Sel. Top. Power Electron. 2020, 8, 298–310. [Google Scholar] [CrossRef]

- Huang, X.; Ji, S.; Palmer, J.; Zhang, L.; Tolbert, L.M.; Wang, F. Parasitic Capacitors’ Impact on Switching Performance in a 10 kV SiC MOSFET Based Converter. In Proceedings of the 6th IEEE Workshop on Wide Bandgap Power Devices and Applications (WiPDA), Atlanta, GA, USA, 31 October–2 November 2018; pp. 311–318. [Google Scholar]

- Ji, S.; Zheng, S.; Wang, F.; Tolbert, L.M. Temperature-dependent characterization, modeling and switching speed limitation analysis of latest generation 10 kV SiC MOSFET. IEEE Trans. Power Electron. 2018, 33, 4317–4326. [Google Scholar] [CrossRef]

- Zhang, Z.; Wang, F.; Tolbert, L.M.; Blalock, B.J.; Costinett, D.J. Evaluation of switching performance of SiC devices in PWM inverter fed induction motor drives. IEEE Trans. Power Electron. 2015, 30, 5701–5711. [Google Scholar] [CrossRef]

- Fuentes, C.D.; Kouro, S.; Bernet, S. Comparison of 1700-V SiC-MOSFET and Si-IGBT modules under identical test setup conditions. IEEE Trans. Ind. Appl. 2019, 55, 7765–7775. [Google Scholar] [CrossRef]

- Zhang, Z.; Zhang, W.; Wang, F.; Tolbert, L.M.; Blalock, B.J. Analysis of the switching speed limitation of wide band-gap devices in a phase-leg configuration. In Proceedings of the 2012 IEEE Energy Conversion Congress and Exposition (ECCE), Raleigh, NC, USA, 15–20 September 2012; pp. 3950–3955. [Google Scholar]

- Zhang, M.; Ren, N.; Guo, Q.; Zhu, X.; Zhang, J.; Sheng, K. Modeling and analysis of vgs characteristics for upper-side and lower-side switches at turn-on transients for a 1200V/200A full-SiC power module. Micromachines 2020, 11, 5. [Google Scholar] [CrossRef] [PubMed]

- Khanna, R.; Amrhein, A.; Stanchina, W.; Reed, G.; Mao, Z. An analytical model for evaluating the influence of device parasitics on Cdv/dt induced false turn-on in SiC MOSFETs. In Proceedings of the 28th Annual IEEE Applied Power Electronics Conference and Exposition (APEC), Long Beach, CA, USA, 17–21 March 2013; pp. 518–525. [Google Scholar]

- Zhang, Z.; Wang, F.; Tolbert, L.M.; Blalock, B.J. Active gate driver for crosstalk suppression of SiC devices in a phase-leg configuration. IEEE Trans. Power Electron. 2014, 29, 1986–1997. [Google Scholar] [CrossRef]

- Xu, S.; Sun, W.; Sun, D. Analysis and design optimization of brushless DC motor’s driving circuit considering the Cdv/dt induced effect. In Proceedings of the 2010 IEEE Energy Conversion Congress and Exposition, Atlanta, GA, USA, 12–16 September 2010; pp. 2091–2095. [Google Scholar]

- Burra, R.K.; Mazumder, S.K.; Huang, R. DV/DT related spurious gate turn-on of bidirectional switches in a high-frequency cycloconverter. IEEE Trans. Power Electron. 2005, 20, 1237–1243. [Google Scholar] [CrossRef]

| Modules 1 | Module_A | Module_B | Modue_C | Module_D |

|---|---|---|---|---|

| SiC-MOSFET dies | S2301TCST | CPM2-1200-0025B | CPM2-1200-0025B | CPM2-1200-0025B |

| Parallel number of dies | 12 | 8 | 8 | 4 |

| Supplier of dies | ROHM | CREE | CREE | CREE |

| Input capacitance | 24.12 nF | 22.30 nF | 22.30 nF | 12.15 nF |

| Voltage/Current ratings | 1200 V/300 A | 1200 V/400 A | 1200 V/400 A | 1200 V/200 A |

| Components | Names | Value |

|---|---|---|

| DC-bus capacitor | C1 | 1000 μF |

| Decoupling capacitor | C2 | 3 μF |

| Decoupling capacitor | C3 | 3 μF |

| Load inductor | 160 μH |

| Number of Turning Points | Module_A | Module_B | Module_C | Module_D |

|---|---|---|---|---|

| High | 2 | 2 | 1 | 1 |

| Low | 1 | 1 | 1 | 1 1 |

| Parasitic Inductance of Paths or Routings | Symbol | Upper-Side | Lower-Side |

|---|---|---|---|

| Routings from terminals of DC+ and DC- inside module | (nH) | 16.46 | 16.46 |

| Paths of drain circuit loop outside module in DPT | (nH) | 12.56 | 12.56 |

| Common part of the routings, and | (nH) | 7.95 | 5.14 |

© 2020 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Zhang, M.; Ren, N.; Guo, Q.; Sheng, K. Understanding Turn-On Transients of SiC High-Power Modules: Drain-Source Voltage Plateau Characteristics. Energies 2020, 13, 3802. https://doi.org/10.3390/en13153802

Zhang M, Ren N, Guo Q, Sheng K. Understanding Turn-On Transients of SiC High-Power Modules: Drain-Source Voltage Plateau Characteristics. Energies. 2020; 13(15):3802. https://doi.org/10.3390/en13153802

Chicago/Turabian StyleZhang, Maosheng, Na Ren, Qing Guo, and Kuang Sheng. 2020. "Understanding Turn-On Transients of SiC High-Power Modules: Drain-Source Voltage Plateau Characteristics" Energies 13, no. 15: 3802. https://doi.org/10.3390/en13153802

APA StyleZhang, M., Ren, N., Guo, Q., & Sheng, K. (2020). Understanding Turn-On Transients of SiC High-Power Modules: Drain-Source Voltage Plateau Characteristics. Energies, 13(15), 3802. https://doi.org/10.3390/en13153802