Research on the Equivalent Virtual Space Vector Modulation Output of Diode Clamped N-level Converter under Multi-Modulation Carrier Modulation

Abstract

:1. Introduction

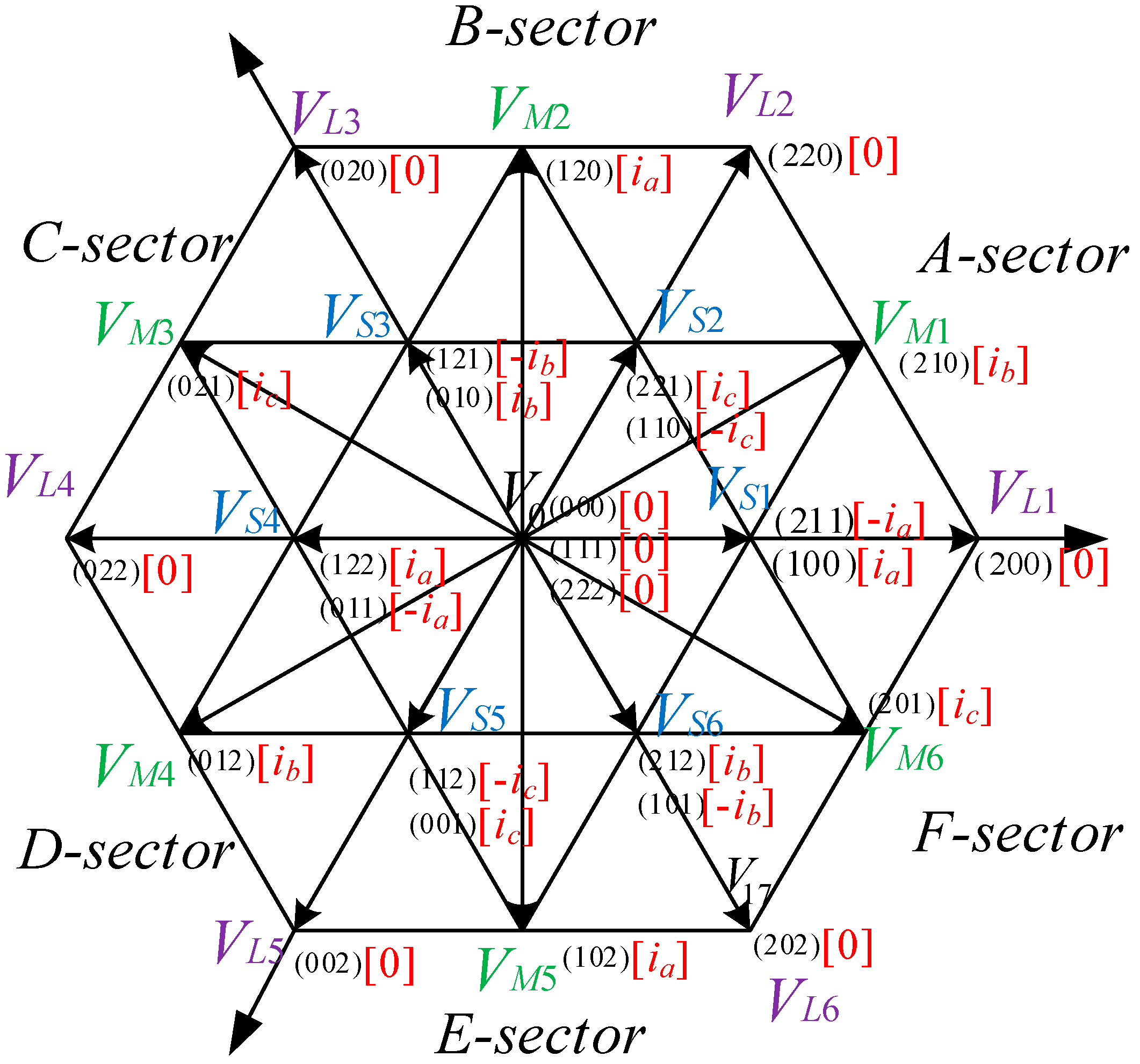

2. VSVPWM Modulation Principle of Diode Clamped Multi-Level Converter

3. The Essential Relationship between Diode Clamp Multi-Level Converter VSVPWM and MCBPWM

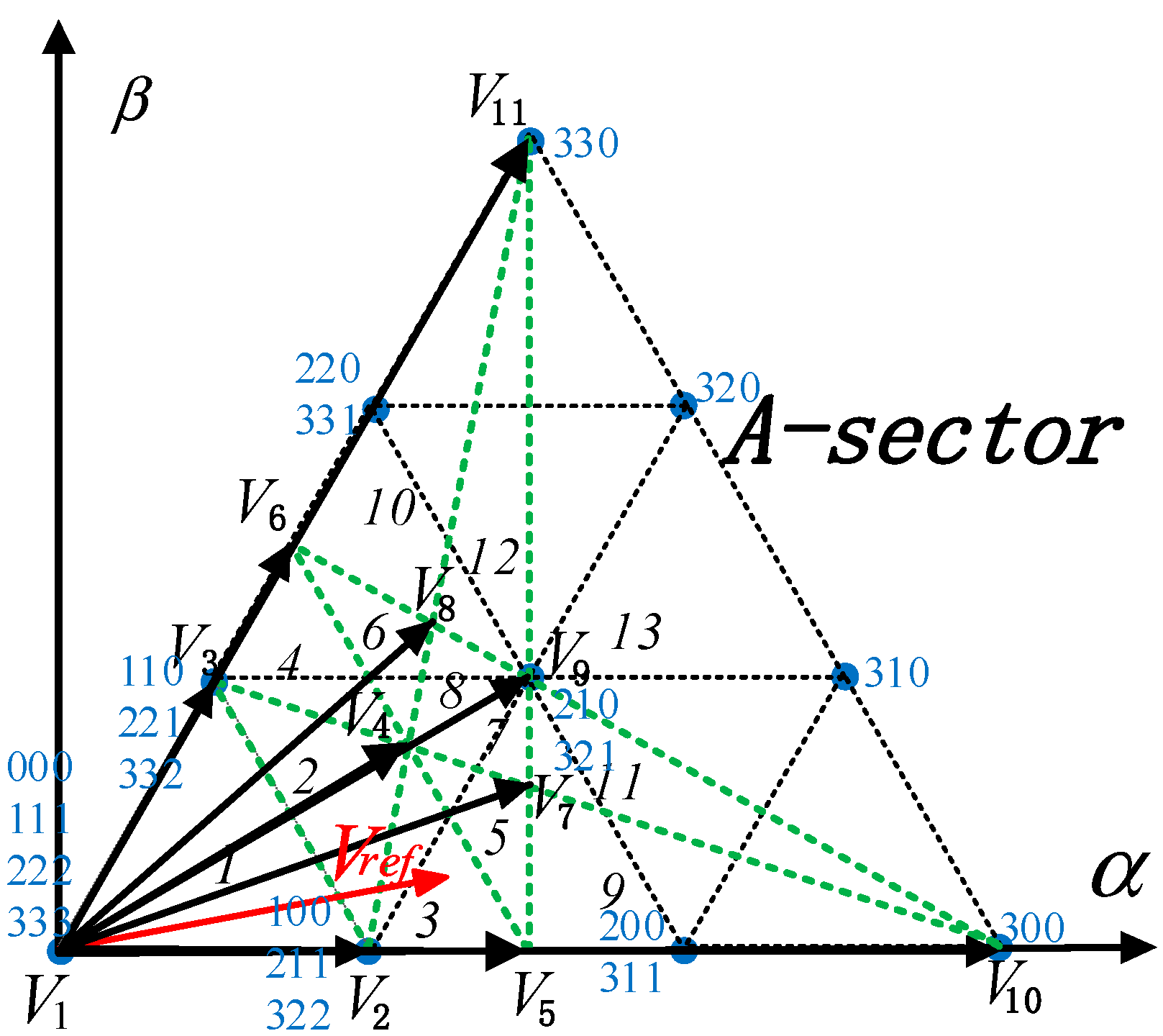

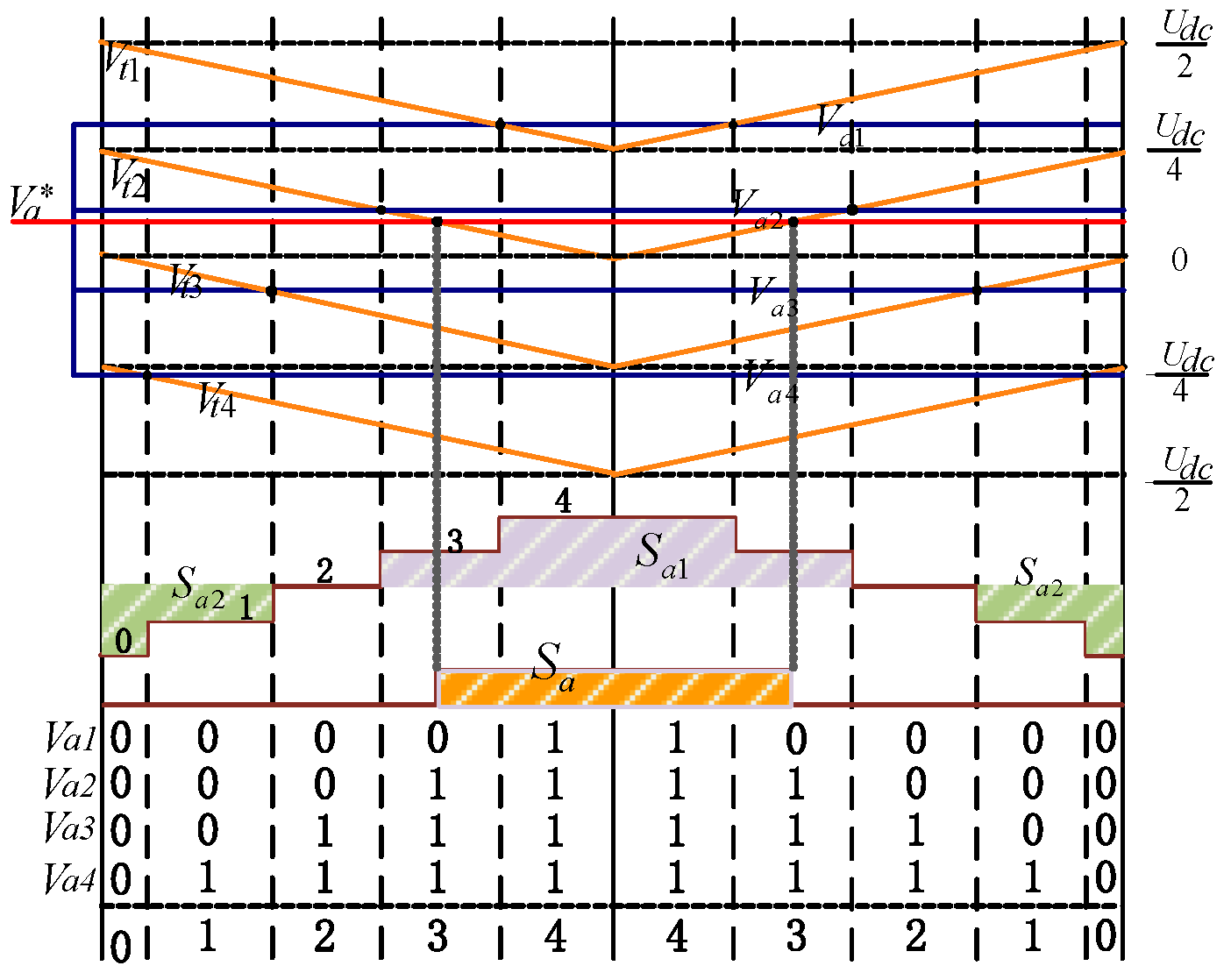

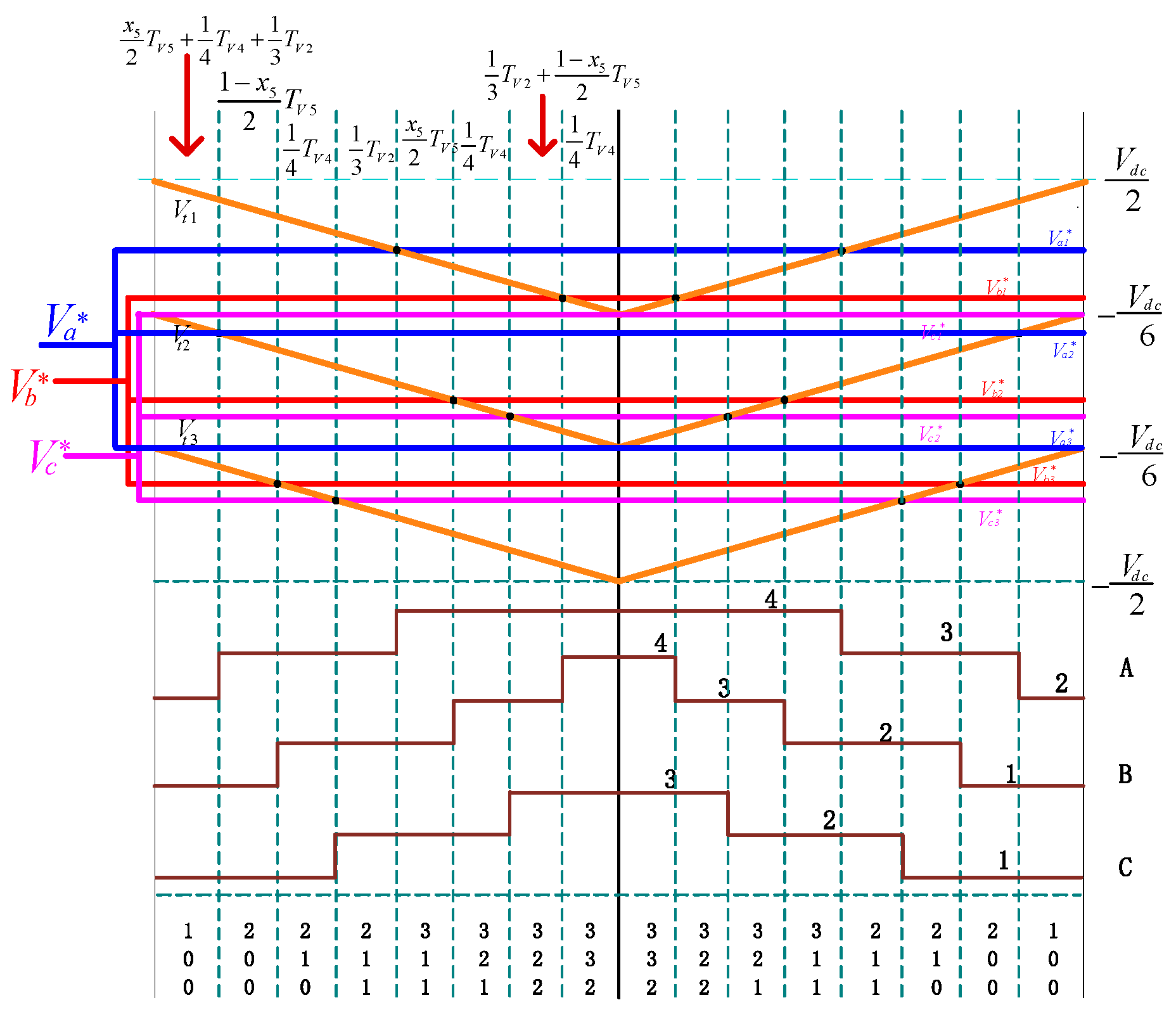

3.1. The Equivalent of Three-Level VSVPWM Modulation and MCBPWM Modulation

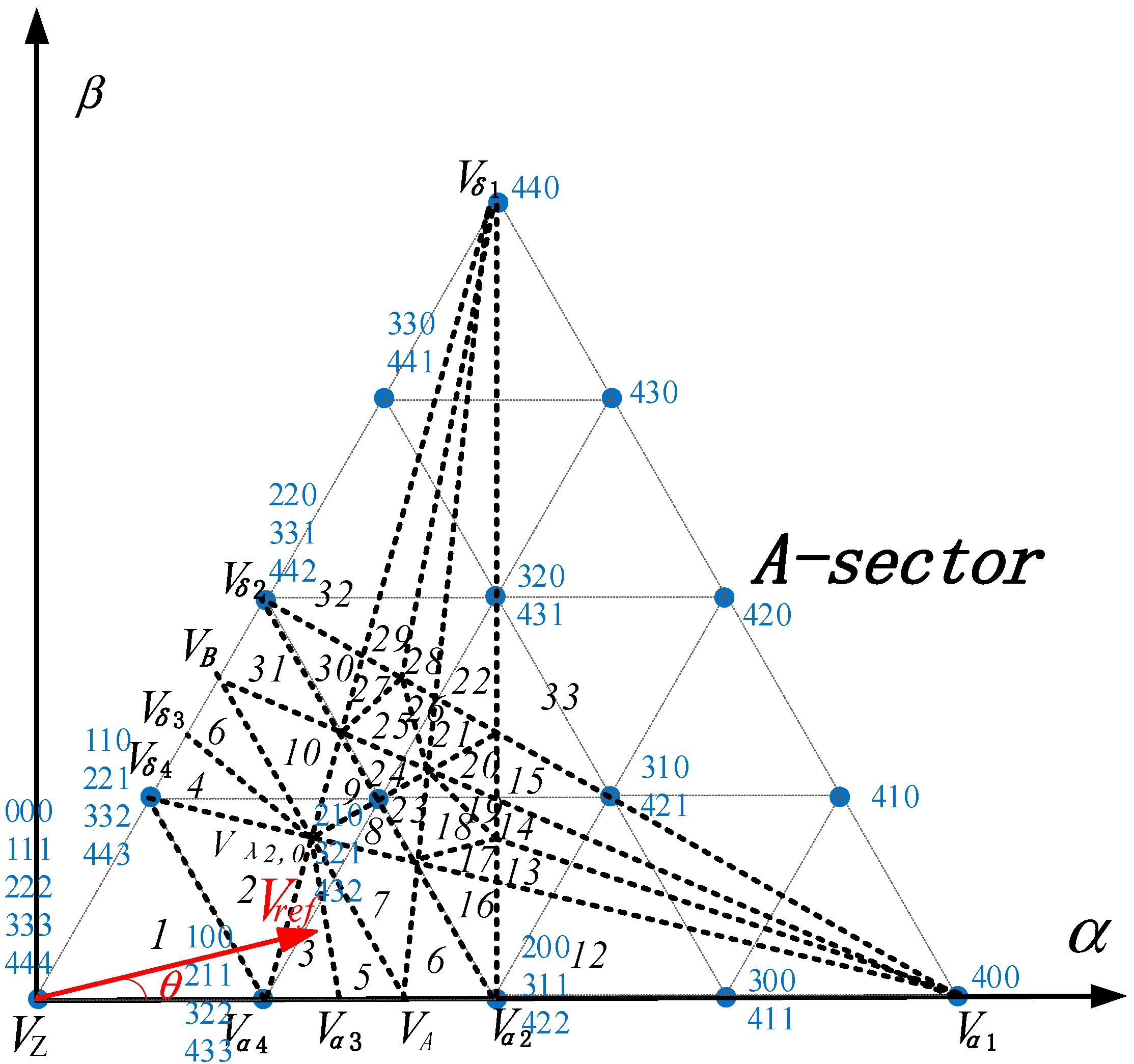

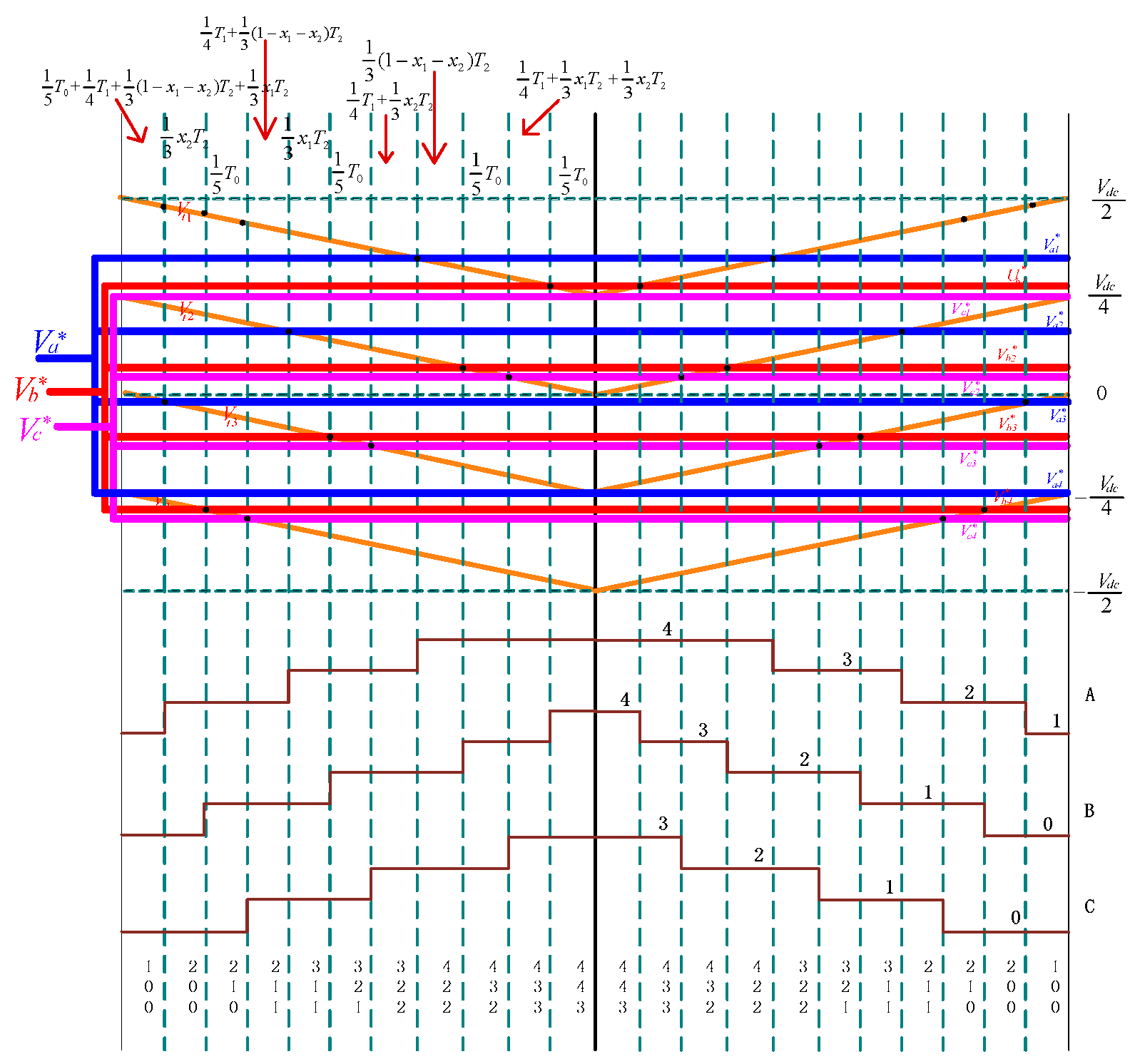

3.2. The Equivalent of Four-Level VSVPWM Modulation and MCBPWM Modulation

3.3. Equivalence of N-Level VSVPWM Modulation and MCBPWM Modulation

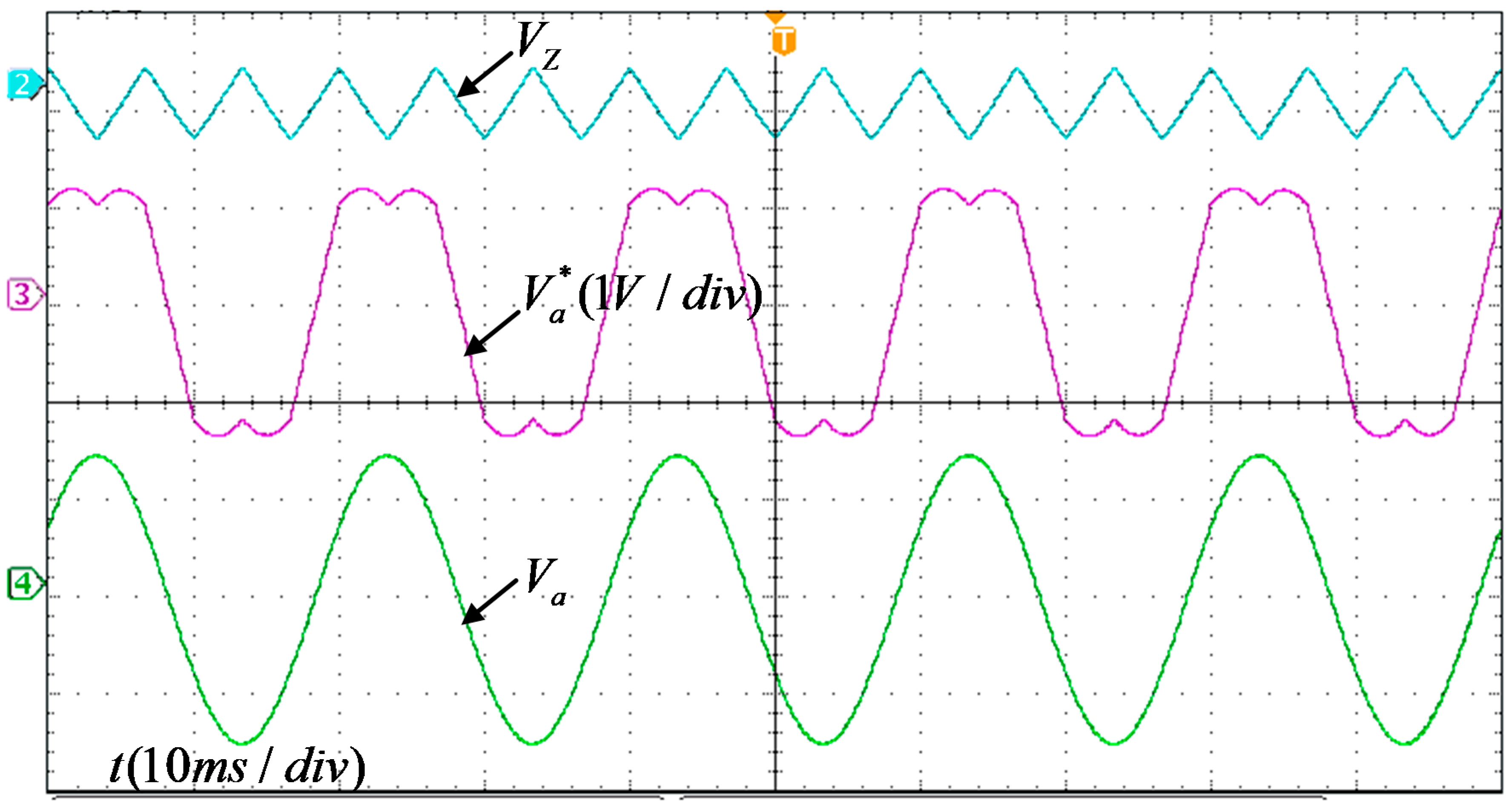

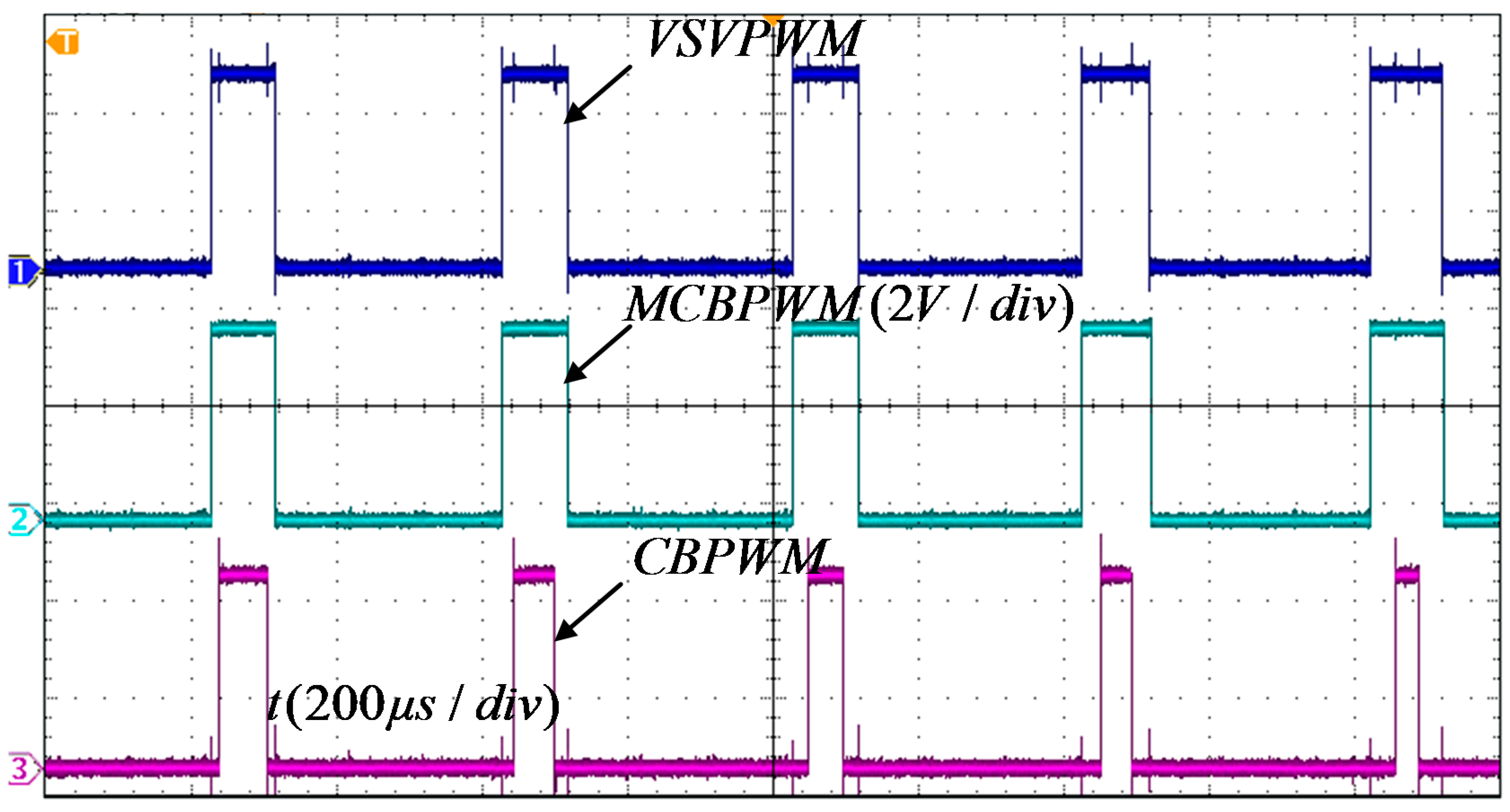

4. Experiment and Result Analysis

5. Discussion

Author Contributions

Funding

Conflicts of Interest

Abbreviations

| Abbreviation | Full Name |

| THD | Total harmonic distortion |

| PWM | Pulse-width modulation |

| VSVPWM | Virtual space vector pulse-width modulation |

| CBPWM | Carrier-based pulse-width modulation |

| SVPWM | Space vector pulse-width modulation |

| MCBPWM | Multi-modulation carrier CBPWM |

| NPC | Neutral-point-clamped |

| DSP | Digital signal processing |

| FPGA | Field programmable gate array |

Appendix A

References

- Jiang, W.; Wang, P.; Ma, M.; Wang, J.; Li, J.; Li, L.; Chen, K.; Weidong, J. A Novel Virtual Space Vector Modulation With Reduced Common-Mode Voltage and Eliminated Neutral Point Voltage Oscillation for Neutral Point Clamped Three-Level Inverter. IEEE Trans. Ind. Electron. 2019, 67, 884–894. [Google Scholar] [CrossRef]

- Wu, X.; Tan, G.; Ye, Z.; Yao, G.; Liu, Z.; Liu, G. Virtual-Space-Vector PWM for a Three-Level Neutral-Point-Clamped Inverter With Unbalanced DC-Links. IEEE Trans. Power Electron. 2018, 33, 2630–2642. [Google Scholar] [CrossRef]

- Alhosaini, W.; Wu, Y.; Zhao, Y. An Enhanced Model Predictive Control Using Virtual Space Vectors for Grid-Connected Three-Level Neutral-Point Clamped Inverters. IEEE Trans. Energy Convers. 2019, 34, 1963–1972. [Google Scholar] [CrossRef]

- Liu, G.; Wang, D.; Wang, M.; Zhu, C.; Wang, M. Neutral-Point Voltage Balancing in Three-Level Inverters Using an Optimized Virtual Space Vector PWM with Reduced Commutations. IEEE Trans. Ind. Electron. 2018, 65, 6959–6969. [Google Scholar] [CrossRef]

- Xiang, C.-Q.; Shu, C.; Han, D.; Mao, B.-K.; Wu, X.; Yu, T.-J.; Chao-Qun, X.; Cheng, S.; Ding, H.; Bing-Kui, M.; et al. Improved Virtual Space Vector Modulation for Three-Level Neutral-Point-Clamped Converter With Feedback of Neutral-Point Voltage. IEEE Trans. Power Electron. 2018, 33, 5452–5464. [Google Scholar] [CrossRef]

- Tan, L.; Wu, B.; Narimani, M.; Xu, D.; Liu, J.; Cheng, Z.; Zargari, N.R. A Space Virtual-Vector Modulation With Voltage Balance Control for Nested Neutral-Point Clamped Converter Under Low Output Frequency Conditions. IEEE Trans. Power Electron. 2017, 32, 3458–3466. [Google Scholar] [CrossRef]

- Hu, C.; Yu, X.; Holmes, D.G.; Shen, W.; Wang, Q.; Luo, F.; Liu, N. An Improved Virtual Space Vector Modulation Scheme for Three-Level Active Neutral-Point-Clamped Inverter. IEEE Trans. Power Electron. 2016, 32, 7419–7434. [Google Scholar] [CrossRef]

- Tian, K.; Wang, J.; Wu, B.; Cheng, Z.; Zargari, N.R. A Virtual Space Vector Modulation Technique for the Reduction of Common-Mode Voltages in Both Magnitude and Third-Order Component. IEEE Trans. Power Electron. 2015, 31, 839–848. [Google Scholar] [CrossRef]

- Song, W.; Wang, S.; Ge, X.; Xiong, C.; Feng, X. Single-phase three-level space vector pulse width modulation algorithm for grid-side railway traction converter and its relationship of carrier-based pulse width modulation. IET Electr. Syst. Transp. 2014, 4, 78–87. [Google Scholar] [CrossRef]

- Busquets-Monge, S.; Somavilla, S.; Bordonau, J.; Boroyevich, D. A novel modulation for the comprehensive neutral-point balancing in the three-level NPC inverter with minimum output switching-frequency ripple. In Proceedings of the 2004 IEEE 35th Annual Power Electronics Specialists Conference (IEEE Cat. No.04CH37551), Aachen, Germany, 20–25 June 2004; Institute of Electrical and Electronics Engineers (IEEE): Piscataway, NJ, USA, 2004; Volume 1–6, pp. 4226–4232. [Google Scholar]

- Busquets-Monge, S.; Bordonau, J.; Rocabert, J. A Virtual-Vector Pulsewidth Modulation for theFour-Level Diode-Clamped DC–AC Converter. IEEE Trans. Power Electron. 2008, 23, 1964–1972. [Google Scholar] [CrossRef]

- Busquets-Monge, S.; Alepuz, S.; Rocabert, J.; Bordonau, J. Pulsewidth Modulations for the Comprehensive Capacitor Voltage Balance of n-Level Three-Leg Diode-Clamped Converters. IEEE Trans. Power Electron. 2009, 24, 1364–1375. [Google Scholar] [CrossRef] [Green Version]

- Fang, H.; Ge, X.; Song, W.; Ding, R.; Feng, X. Relationship between two-level space-vector pulse-width modulation and carrier-based pulse-width modulation in the over-modulation region. IET Power Electron. 2014, 7, 189–199. [Google Scholar] [CrossRef]

- Yao, W.X.; Hu, H.B.; Lu, Z.Y. Comparisons of space-vector modulation and carrier-based modulation of multi-level inverter. IEEE Trans. Power Electron. 2008, 23, 45–51. [Google Scholar]

- Song, W.; Feng, X.; Smedley, K.M. A Carrier-Based PWM Strategy With the Offset Voltage Injection for Single-Phase Three-Level Neutral-Point-Clamped Converters. IEEE Trans. Power Electron. 2012, 28, 1083–1095. [Google Scholar] [CrossRef]

- Chen, J.; He, Y.; Hasan, S.U.; Liu, J.J. A Comprehensive Study on Equivalent Modulation Waveforms of the SVM Sequence for Three-Level Inverters. IEEE Trans. Power Electron. 2015, 30, 7149–7158. [Google Scholar] [CrossRef]

- He, Y.; Liu, Y.; Lei, C.; Liu, J. Equivalent Space Vector Output of Diode Clamped Multilevel Inverters Through Modulation Wave Decomposition Under Carrier-Based PWM Strategy. IEEE Access 2020, 8, 104918–104932. [Google Scholar] [CrossRef]

- Wang, J.; Gao, Y.; Jiang, W.; Weidong, J. A Carrier-Based Implementation of Virtual Space Vector Modulation for Neutral-Point-Clamped Three-Level Inverter. IEEE Trans. Ind. Electron. 2017, 64, 9580–9586. [Google Scholar] [CrossRef]

- Weidong, J.; Wang, L.; Wang, J.; Zhang, X.; Wang, P. A Carrier-Based Virtual Space Vector Modulation With Active Neutral-Point Voltage Control for a Neutral-Point-Clamped Three-Level Inverter. IEEE Trans. Ind. Electron. 2018, 65, 8687–8696. [Google Scholar] [CrossRef]

- Deng, Y.; Harley, R.G. Space-Vector Versus Nearest-Level Pulse Width Modulation for Multi-level Converters. IEEE Trans. Ind. Electron. 2015, 30, 2962–2974. [Google Scholar]

- Deng, Y.; Wang, Y.B.; Teo, K.H.; Harley, R.G. A Simplified Space Vector Modulation Scheme for Multi-level Converters. IEEE Trans. Ind. Electron. 2016, 31, 1873–1886. [Google Scholar]

| Sector | Modulation Sequence |

|---|---|

| A1 | 100→110→111→211→221→221→211→111→110→100 |

| A2 | 100→110→210→211→221→221→211→210→110→100 |

| A3 | 100→200→210→211→221→221→211→210→200→100 |

| A4 | 100→110→210→220→221→221→220→210→110→100 |

| A5 | 100→200→210→220→221→221→220→210→200→100 |

© 2020 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

He, Y.; Lei, C.; Liu, Y.; Liu, J. Research on the Equivalent Virtual Space Vector Modulation Output of Diode Clamped N-level Converter under Multi-Modulation Carrier Modulation. Energies 2020, 13, 3803. https://doi.org/10.3390/en13153803

He Y, Lei C, Liu Y, Liu J. Research on the Equivalent Virtual Space Vector Modulation Output of Diode Clamped N-level Converter under Multi-Modulation Carrier Modulation. Energies. 2020; 13(15):3803. https://doi.org/10.3390/en13153803

Chicago/Turabian StyleHe, Yingjie, Chao Lei, Yunfeng Liu, and Jinjun Liu. 2020. "Research on the Equivalent Virtual Space Vector Modulation Output of Diode Clamped N-level Converter under Multi-Modulation Carrier Modulation" Energies 13, no. 15: 3803. https://doi.org/10.3390/en13153803