Optimal Design of Multi-Output LLC Resonant Converter with Independently Regulated Synchronous Single-Switched Power-Regulator †

Abstract

:1. Introduction

2. Technical Work Preparation

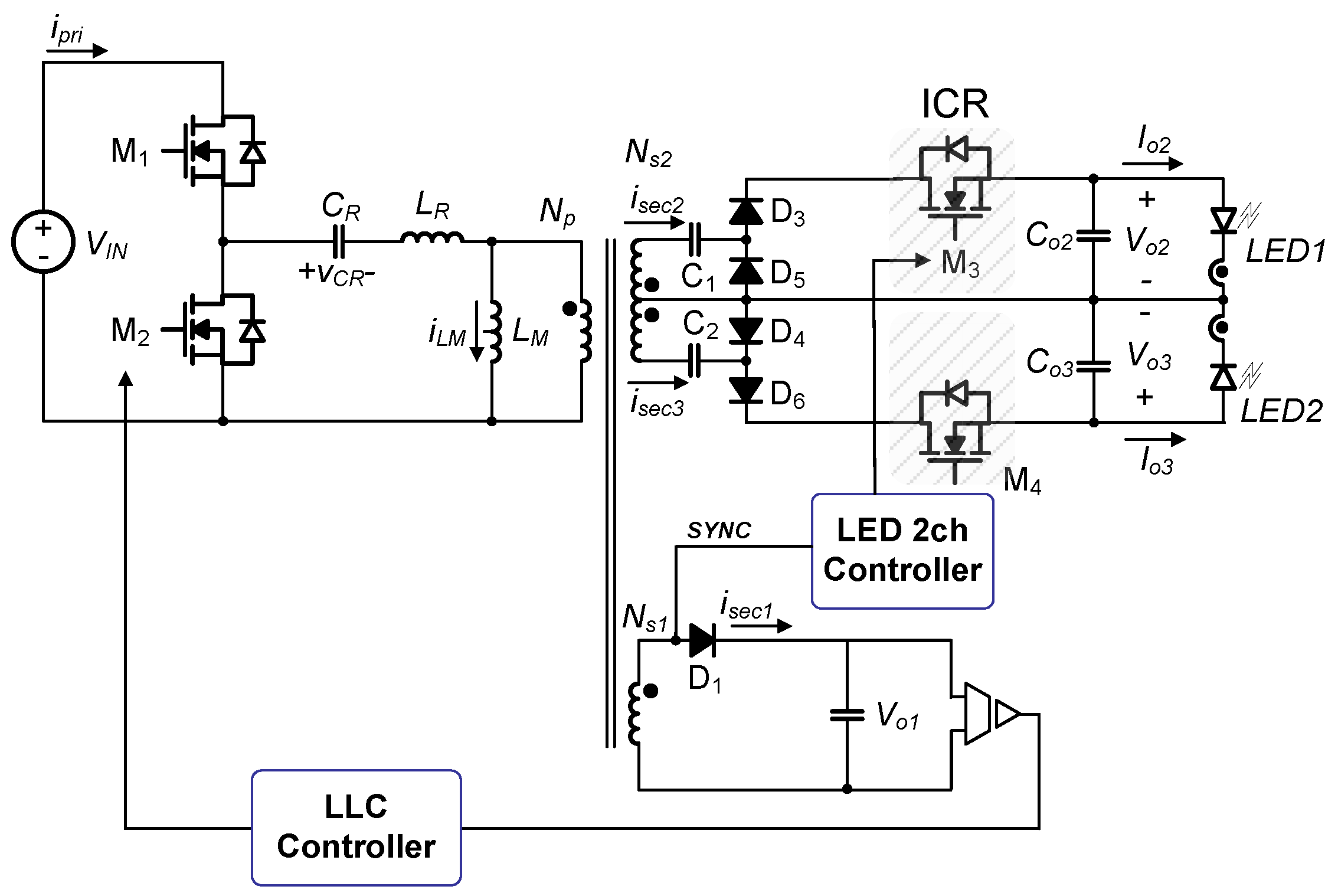

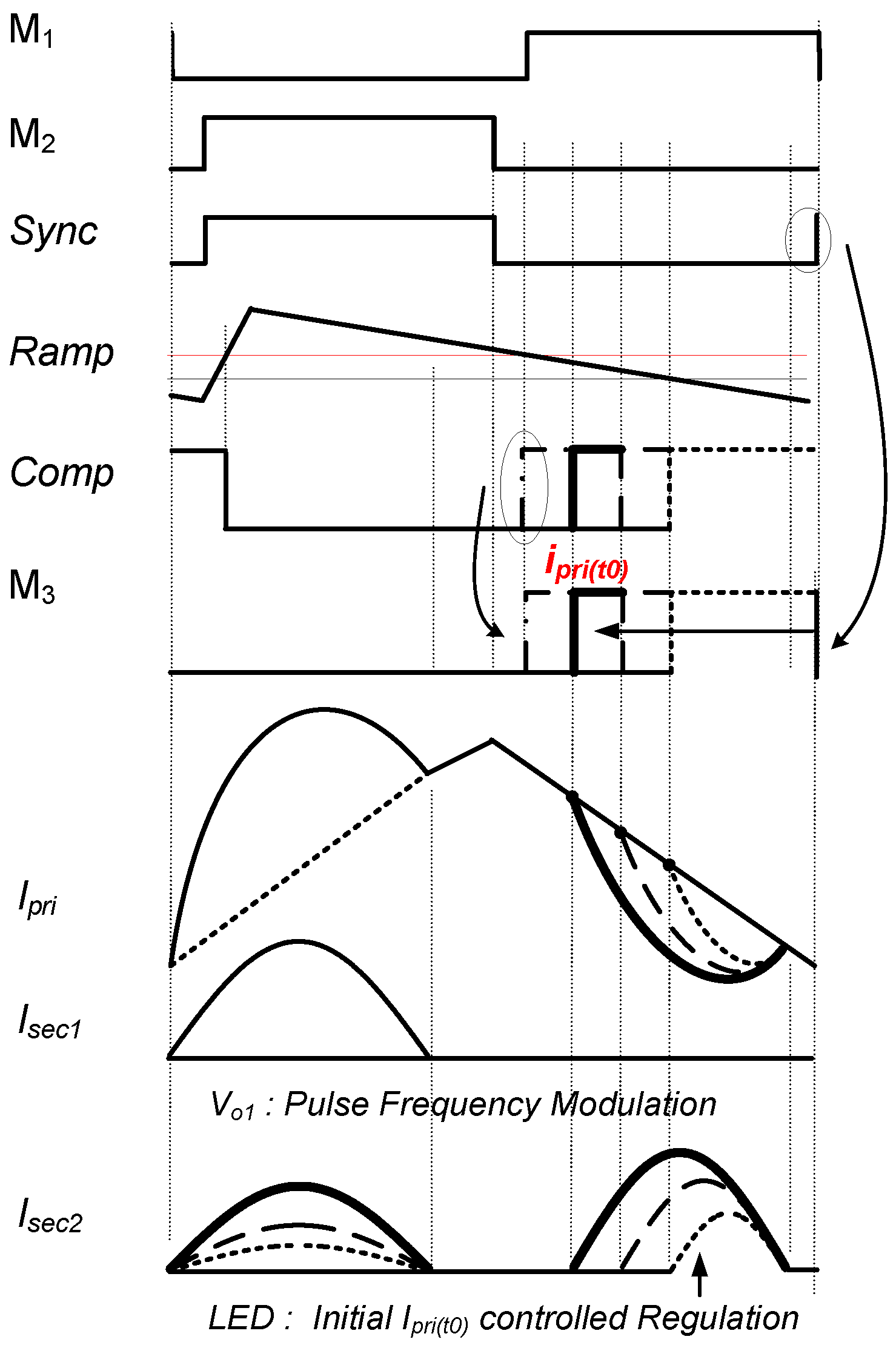

2.1. Control Method for Proposed Converter

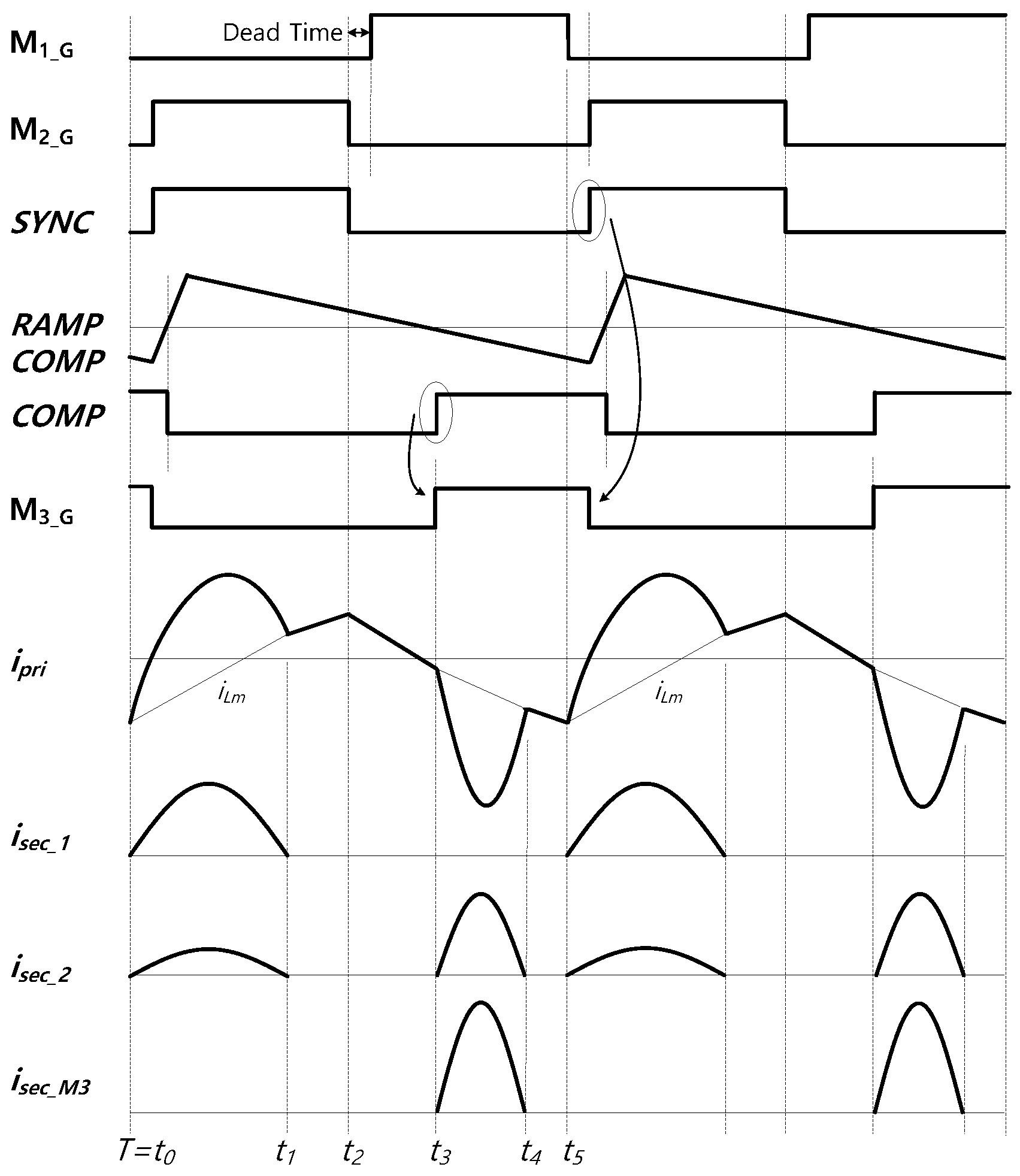

2.2. Analysis of Operational Modes

- (1)

- The switch is ideal, except for the internal diode.

- (2)

- The transformer is ideal, except for the magnetizing inductance Lm and leakage inductance LR.

- (3)

- The output capacitors Co1 and Co2 are large enough to be considered as constant DC voltage sources Vo1 and Vo2, respectively.

- (4)

- The switching transition interval between M1 and M2 is small enough to be ignored.

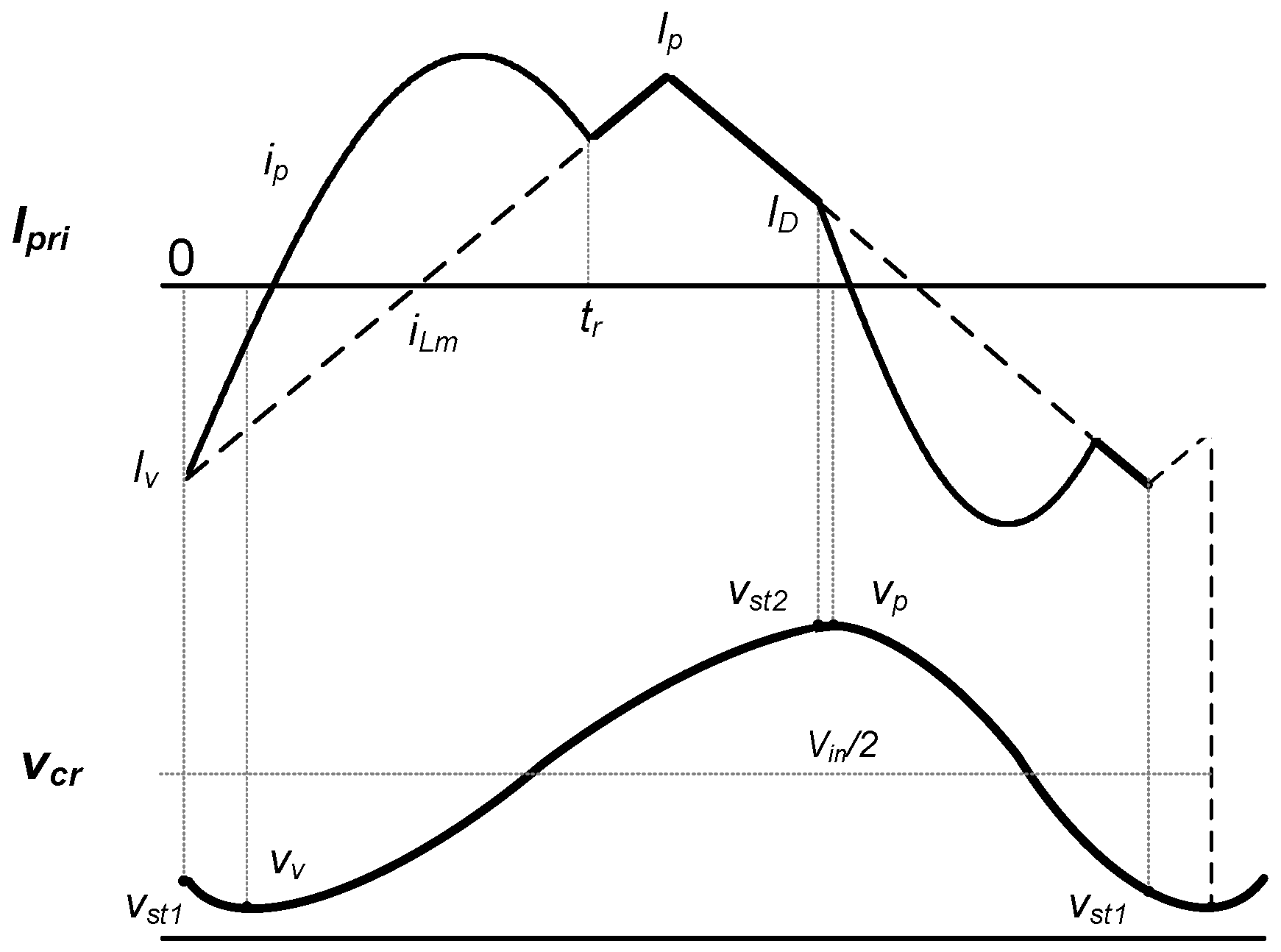

- Mode 1 [t0–t1]: This mode starts when M1 is turned off at t0. At this moment, the current of the resonant inductor LR is negative; it will flow through the body diode of M2, creating a zero-voltage switching (ZVS) condition for M2. The gating signal of M2 should be applied during this mode.When the current of the resonant inductor LR flows through the body diode of M2, Ipri starts to rise. As the voltage VIN–vCR across the primary side of the transformer is higher than the reflected output voltage (NP/NS1)Vo1, D1 is turned on.Concurrently, the transformer primary current ipri starts to increase, based on the resonance between CR and LR. The magnetic current iLm increases linearly as the reflected output voltage (NP/NS1)Vo1 is applied to Lm. Therefore, it does not participate in the resonance during this period. In this mode, the circuit operates as a series resonant converter (SRC), with a resonant inductor LR and resonant capacitor CR. This mode is terminated when the LR current is the same as the Lm current.

- Mode 2 [t1–t2]: When the transformer primary current ipri becomes equal to iLM and isec1 reaches zero at t1, Mode 2 begins. At this moment, D1 is blocked, and VIN–vCR is applied to LM + LR. The value of ipri is still increasing owing to the resonance between CR and LM + LR, as shown in Figure 5c, and the primary current ipri is still increasing, based on the resonance between CR and Lm + LR.

- Mode 3 [t2–t3]: When M2 is turned off and M1 is turned on at t2, Mode 3 begins. Although M1 is conducting and −vCR is applied to the primary side of the transformer, the turned off M3 prevents the input power from being transferred to the output side. Therefore, resonance does not occur between CR and LR, isec2 is maintained at zero, and the initial current Iini decreases with the slope of −vCR/(LR + Lm). The primary current ipri decreases in the same manner as the resonance between CR and LM + LR.

- Mode 4 [t3–t4]: When M3 is turned on at t3, Mode 4 starts, as shown in Figure 4. D3 is turned on because the voltage vCR is higher than the reflected output voltage (NP/NS2)Vo2. Concurrently, the primary current begins to decrease owing to the resonance between CR and LR. In addition, the reflected output voltage −(NP/NS2)Vo2 is applied to LM, causing the magnetizing current iLM to decrease linearly.

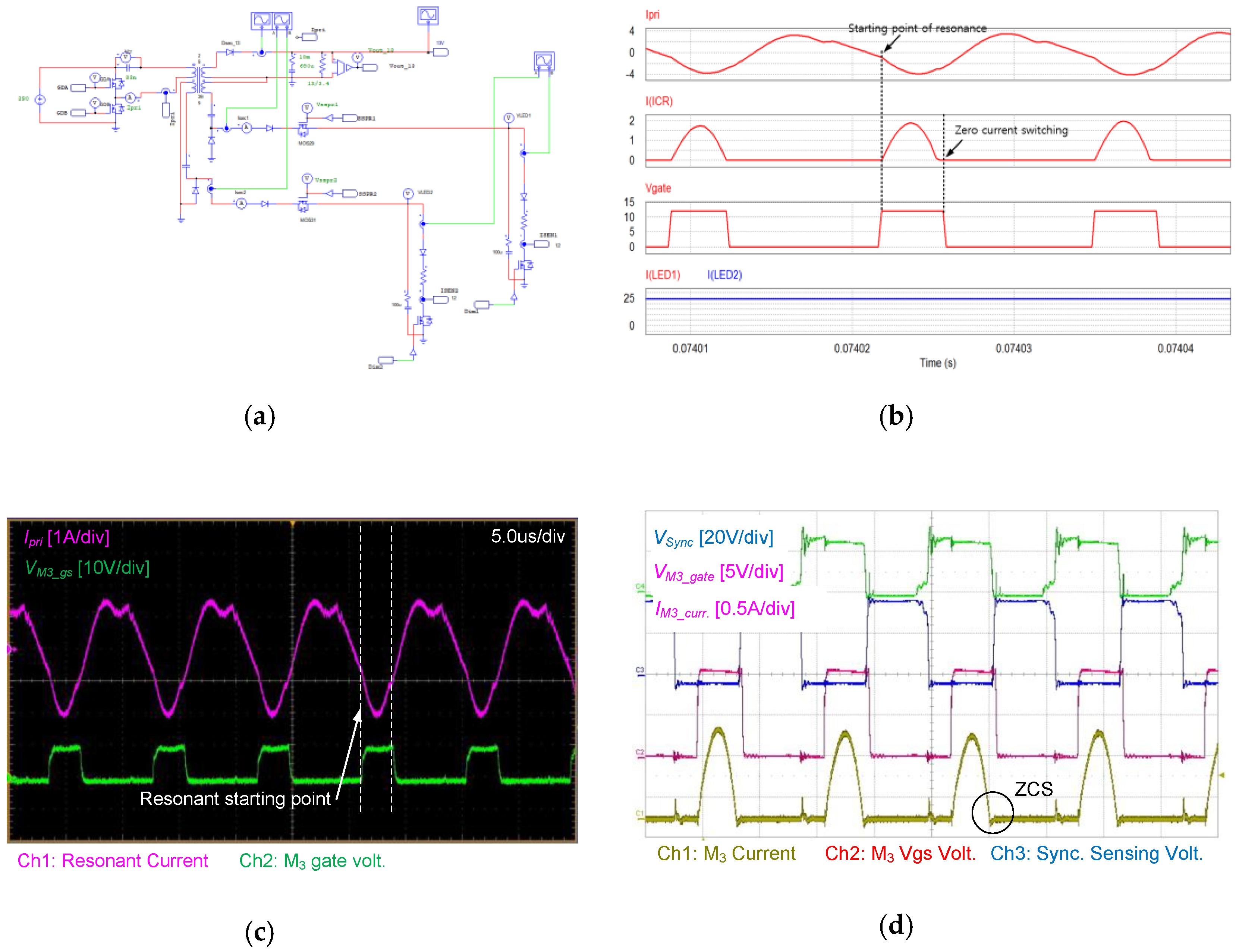

- Mode 5 [t4–t5]: Mode 5 begins when the primary current ipri becomes equal to the magnetizing current iLM, and the secondary current of the transformer, isec2, reaches zero at t4. At this moment, the primary current ipri is still decreasing owing to the resonance between CR and LM + LR, because D3 and D6 are blocked and −vCR is applied to LM + LR, as shown in Figure 5e. If only M3 and M4 are turned off after t5, M3 and M4 can be turned off to the Sync signal under the ZCS operation. This mode is terminated when M1 is switched off at t5. Then, the operations from t0 to t5 are repeated.

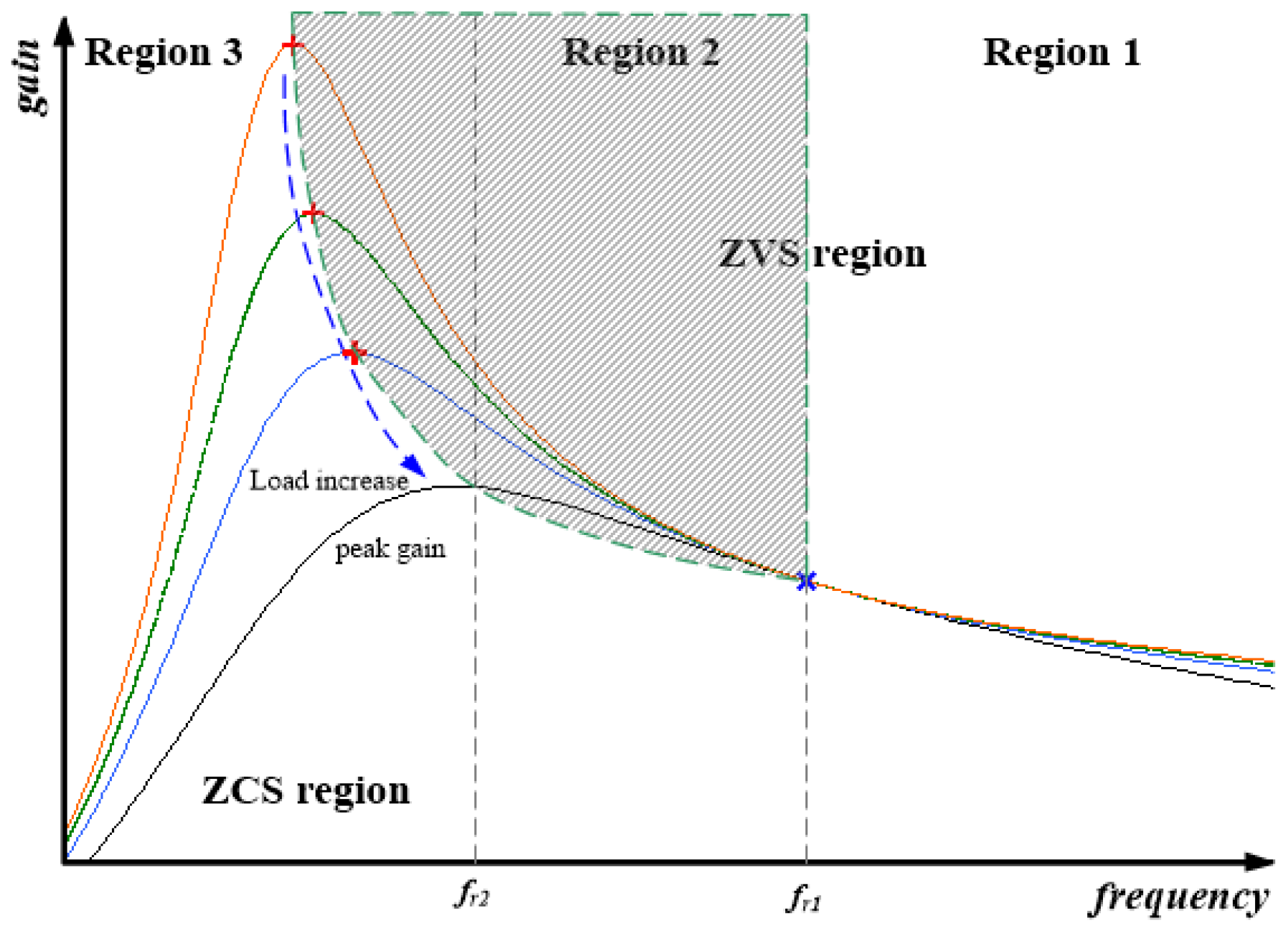

3. Analysis and Simplified Design Guidelines

3.1. Output Voltage Analysis

3.2. Simplified Design Guidelines

- (1)

- Switching frequency (fs)

- (2)

- Resonant tank frequency (fn)

- (3)

- Magnetizing inductance of the transformer (LM)

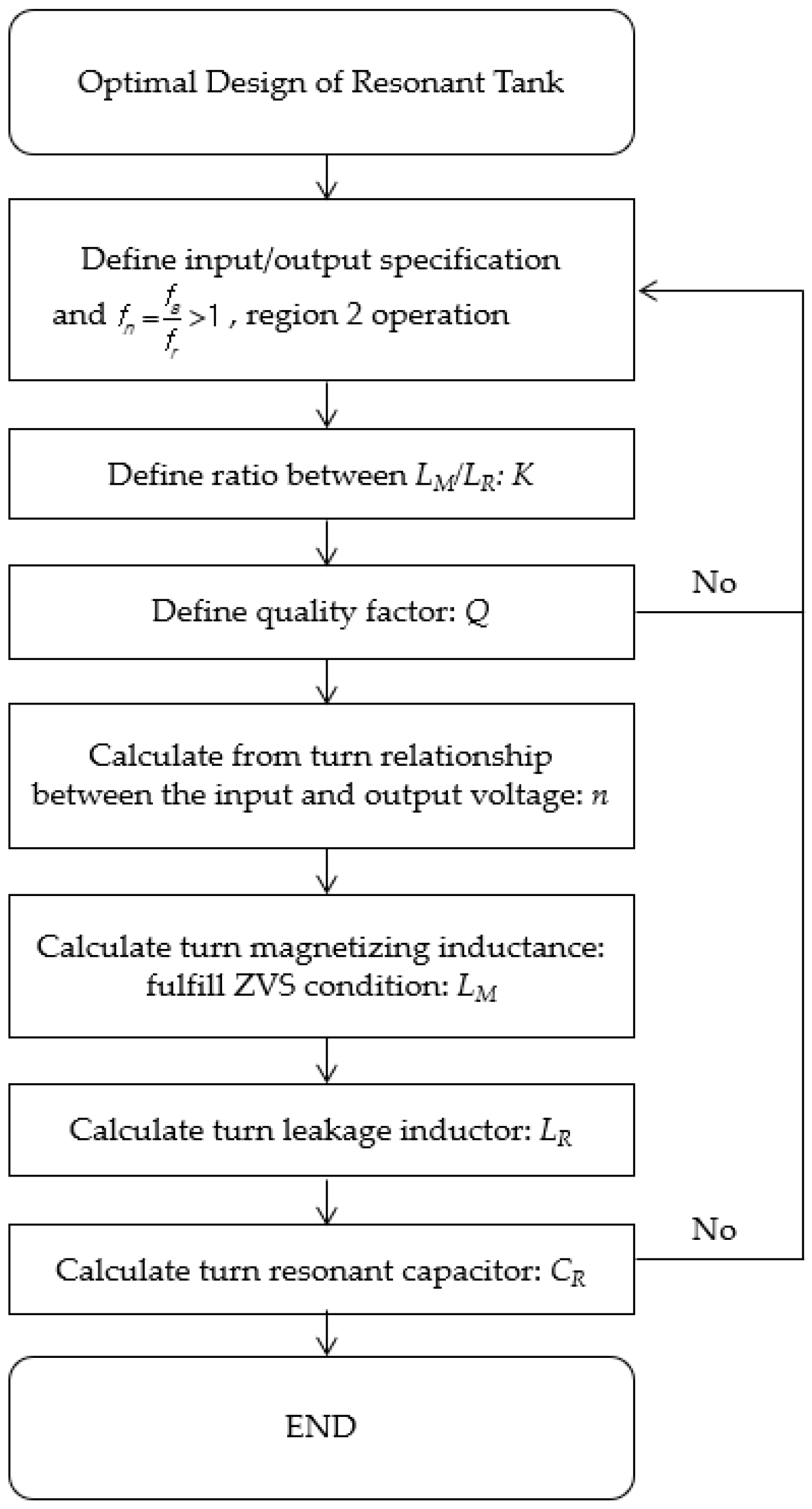

3.3. Optimal Design of the LLC Resonant Converter

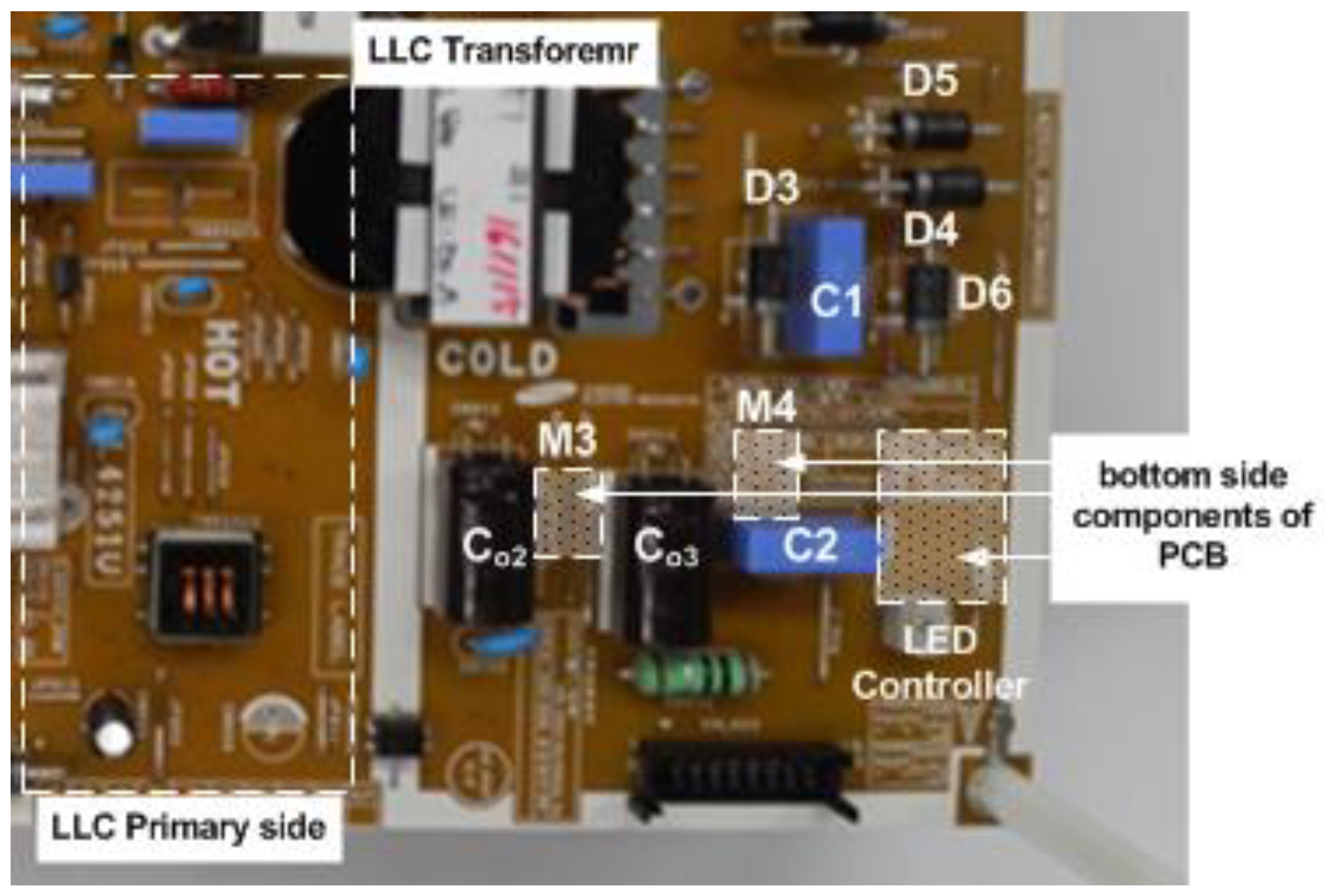

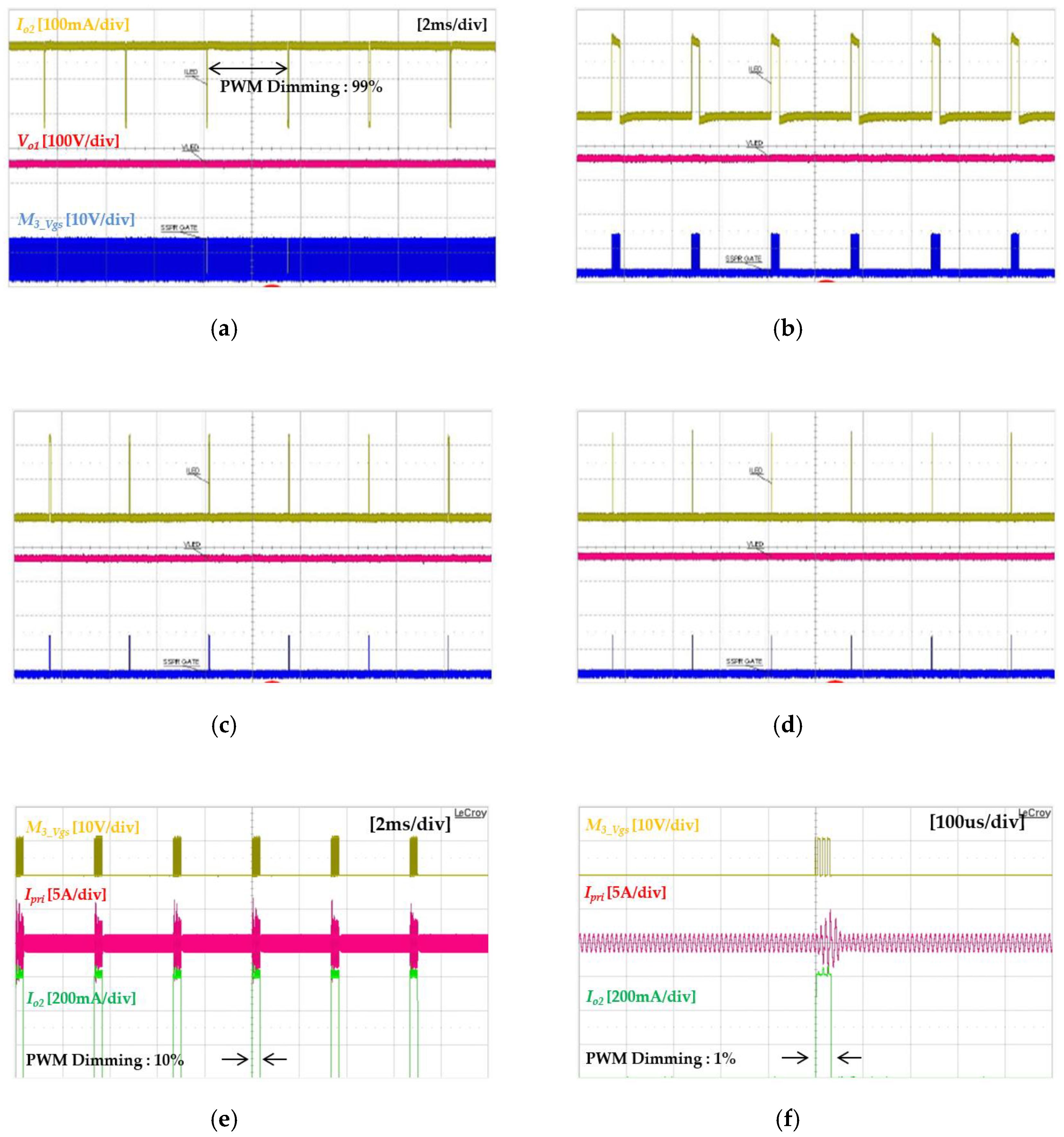

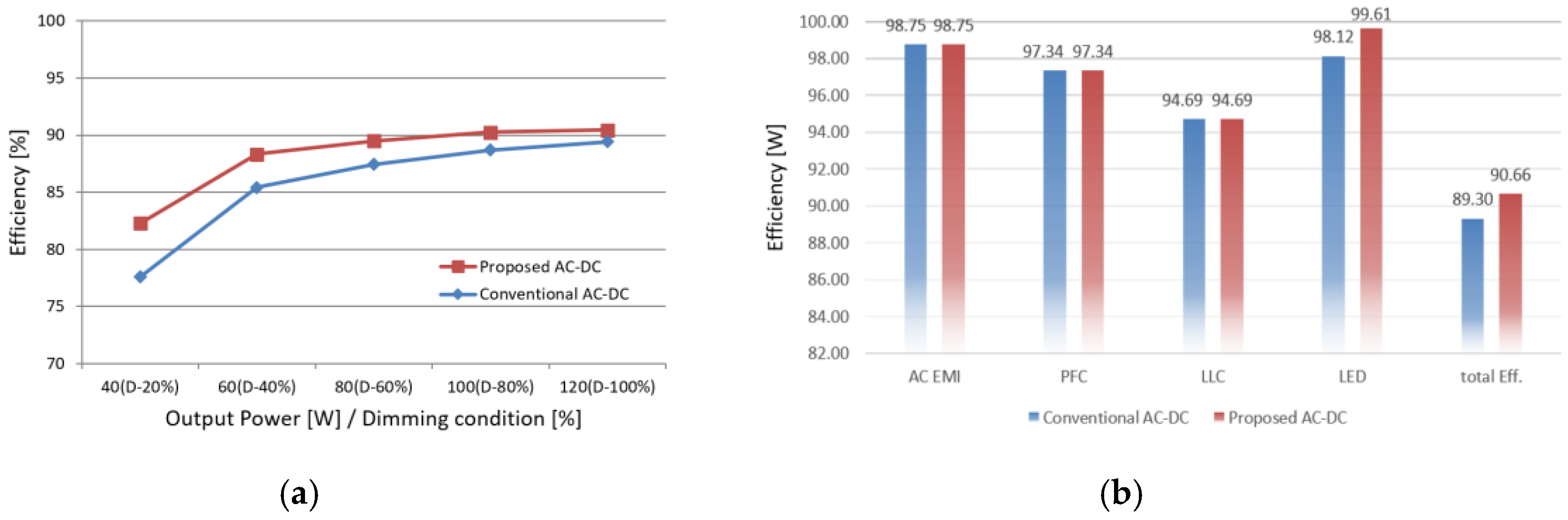

4. Experimental Results

5. Conclusions

Author Contributions

Funding

Conflicts of Interest

References

- Qu, X.; Wong, S.-C.; Tse, C.K. A current balancing scheme with high luminous efficiency for high power LED lighting. In Proceedings of the IECON 2013-39th Annual Conference of the IEEE Industrial Electronics Society, Vienna, Austria, 10–13 November 2013. [Google Scholar]

- Liu, J.; Sun, W.; Zeng, J. Precise current sharing control for multi-channel LED driver based on switch-controlled capacitor. IET Power Electron. 2017, 10, 357–367. [Google Scholar] [CrossRef]

- Chen, Y.; Wu, X.; Qian, Z. Analysis and design considerations of LLCC resonant dc–dc converter with precise current sharing for two-channel LED driver. In Proceedings of the 2011 IEEE Energy Conversion Congress and Exposition, Phoenix, AZ, USA, 17–22 September 2011; pp. 2771–2776. [Google Scholar]

- Raghavendra, K.V.G.; Zeb, K.; Muthusamy, A.; Krishna, T.N.V.; Prabhudeva Kumar, S.V.S.V.; Kim, D.-H.; Kim, M.-S.; Cho, H.-G.; Kim, H.-J. A comprehensive review of DC–DC converter topologies and modulation strategies with recent advances in solar photovoltaic systems. Electronics 2019, 9, 31. [Google Scholar] [CrossRef] [Green Version]

- Park, S.-G.; Ryu, S.-H.; Cho, K.-S.; Lee, B.-K. An improved single switched post regulator for multiple output isolated converters. In Proceedings of the 2015 9th International Conference on Power Electronics and ECCE Asia (ICPE-ECCE Asia), Seoul, Korea, 1–5 June 2015; pp. 2403–2408. [Google Scholar]

- Vinoth Kumar, K.; Shankar, A.; Renius, J.S.; Guru, R.; Nair, S.L.; Viswanathan, K. The FHA analysis of dual-bridge LLC type resonant converter arnold fredderics. Int. J. Power Electron. Drive Syst. (IJPEDS) 2014, 4, 538–546. [Google Scholar]

- Lo, Y.K.; Yen, S.C.; Song, T.H. Analysis and design of a double-output series- resonant DC-DC converter. IEEE Trans. Power Electron. 2007, 22, 952–959. [Google Scholar] [CrossRef]

- Gu, Y.; Hang, L.; Chen, U.; Lu, Z.; Qian, Z.; Li, J. A simple structure of LLC resonant DC-DC converter for multi-output applications. In Proceedings of the 2005 20th Annual Meeting of Applied Power Electronics Conference, Austin, TX, USA, 6–10 March 2005; Volume 3, pp. 1485–1490. [Google Scholar]

- Jovanović, M.M.; Irving, B.T. Efficiency optimization of LLC resonant converters operating in wide input-and/or output-voltage range by on-the-fly topology-morphing control. In Proceedings of the IEEE Applied Power Electronics Conference (APEC), Charlotte, NC, USA, 15–19 March 2015. [Google Scholar]

- Chandrasekar, B.; Samuel Rajesh Babu, R. A review on LLC resonant converter. In Proceedings of the International Conference on Computation of Power, Energy Information and Communication (ICCPEIC), Chennai, India, 20–21 April 2016. [Google Scholar]

- Kim, C.-E.; Moon, G.-W.; Lee, J.-Y.; Park, K.-B. New Multi-output LLC resonant converter for high efficiency and low cost PDP power module. In Proceedings of the 2006 37th IEEE Power Electronics Specialists Conference, Jeju, Korea, 18–22 June 2006; pp. 1–7. [Google Scholar]

- Hang, L.-J.; Gu, Y.-L.; Lu, Z.-Y.; Qian, Z.-M. Multi-output LLC resonant converter with symmetrical auxiliary output structure. In Proceedings of the INTELEC 06-Twenty-Eighth International Telecommunications Energy Conference, Providence, RI, USA, 10–14 September 2006; pp. 1–5. [Google Scholar]

- Lin, Y.-L.; Liu, K.H. A new synchronous-switch post regulator for multi-output forward converters. In Proceedings of the Fifth Annual Proceedings on Applied Power Electronics Conference and Exposition, Los Angeles, CA, USA, 11–16 March 1990; pp. 693–696. [Google Scholar]

- Zhang, J.; Liao, J.; Wang, J.; Qian, Z. A current-driving synchronous rectifier for an LLC resonant converter with voltage-doubler rectifier structure. IEEE Trans. Power Electron. 2012, 27, 1894–1904. [Google Scholar] [CrossRef]

- Qian, Q.; Yu, J.; Su, C.; Sun, W.; Lu, W. A LLC resonant converter with dual resonant frequency for high light load efficiency. Int. J. Electron. 2017, 104, 2033–2047. [Google Scholar] [CrossRef]

- Luo, J.; Wang, J.; Fang, Z.; Shao, J.; Li, J. Optimal design of a high efficiency LLC resonant converter with a narrow frequency range for voltage regulation. Energies 2018, 11, 1124. [Google Scholar] [CrossRef] [Green Version]

- Park, H.P.; Jung, J.H. PWM and PFM hybrid control method for LLC resonant converters in high switching frequency operation. IEEE Trans. Ind. Electron. 2017, 64, 253–263. [Google Scholar] [CrossRef]

- Su, B.; Wen, H.; Zhang, J.; Lu, Z. A soft-switching post regulator for multi-outputs dual forward dc/dc converter with tight output voltage regulation. IET Power Electron. 2013, 6, 1067–1077. [Google Scholar] [CrossRef]

- Fang, X.; Hu, H.; John Shen, Z.; Batarseh, I. Operation mode analysis and peak gain approximation of the LLC resonant converter. IEEE Trans. Power Electron. 2012, 27, 1985–1995. [Google Scholar] [CrossRef]

| Input Voltage, VIN | AC90–264V |

| Vvisual and Vamp | 12.8 V/5.4 A |

| LED Output (2CH) | 2D Mode_100V/240 mA |

| 3D Mode_122V/630 mA | |

| Output Power, Po,max | 120 W |

| Trans Turn Ratio, NP:NS1:NS2 | 39:2:32 |

| Resonant Capacitor, Cr | 33 nF |

| Leakage Inductance, Lr | 94 uH |

| Magnetizing inductance, LM | 470 uH |

| LLC Resonant Controller | FA6A00N, Fuji Electric, Japan |

| Item | Conventional Circuit | Proposed Circuit | ||

|---|---|---|---|---|

| Rectifier Diode | 4EA | SDURF1030 (TO-220) | 4EA | SF38G (DO-201A) |

| Heat Sink | 1EA | 60 mm × 30 mm × 9 mm | − | − |

| Power Switch | 2EA | AOD9N25 (D-PAK) | 2EA | AOD5N40 (D-PAK) |

| Freewheeling Diode | 2EA | MUR460 (DO-201A) | − | − |

| Elec. Capacitor | 2EA | 68 uF/160 V | − | − |

| 2EA | 33 uF/200 V | 2EA | 47 uF/200 V | |

| Film Capacitor | − | − | 2EA | 100 nF/330 V |

| Inductor | 2EA | EFD2020 | − | − |

© 2020 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Park, S.G.; Lee, B.K.; Kim, J.S. Optimal Design of Multi-Output LLC Resonant Converter with Independently Regulated Synchronous Single-Switched Power-Regulator. Energies 2020, 13, 4341. https://doi.org/10.3390/en13174341

Park SG, Lee BK, Kim JS. Optimal Design of Multi-Output LLC Resonant Converter with Independently Regulated Synchronous Single-Switched Power-Regulator. Energies. 2020; 13(17):4341. https://doi.org/10.3390/en13174341

Chicago/Turabian StylePark, Sang Gab, Byoung Kuk Lee, and Jong Soo Kim. 2020. "Optimal Design of Multi-Output LLC Resonant Converter with Independently Regulated Synchronous Single-Switched Power-Regulator" Energies 13, no. 17: 4341. https://doi.org/10.3390/en13174341